Page 1 of 11

# **RADIOGRAPHIC INSPECTION OF**

# **INTEGRATED CIRCUITS**

ESCC Basic Specification No. 2099000

| Issue 2 | March 2014 |

|---------|------------|

Document Custodian: European Space Agency - see https://escies.org

PAGE 2

### LEGAL DISCLAIMER AND COPYRIGHT

European Space Agency, Copyright © 2014. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

PAGE 3

## **DOCUMENTATION CHANGE NOTICE**

(Refer to https://escies.org for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION                                               |

|---------|------------------------------------------------------------------|

| 838     | Specification upissued to incorporate editorial changes per DCR. |

PAGE 4

## No. 2099000

## TABLE OF CONTENTS

| 1   | SCOPE                                                            | 5  |

|-----|------------------------------------------------------------------|----|

| 2   | GENERAL REQUIREMENTS                                             | 5  |

| 2.1 | APPLICABILITY                                                    | 5  |

| 2.2 | PROCEDURE                                                        | 5  |

| 3   | X-RAY PHOTOGRAPHS                                                | 5  |

| 4   | DETAILED REQUIREMENTS                                            | 5  |

| 4.1 | REJECT CRITERIA                                                  | 5  |

| 4.2 | PRESENCE OF EXTRANEOUS MATTER                                    | 5  |

| 4.3 | UNACCEPTABLE CONSTRUCTION                                        | 6  |

| 5   | FIGURES                                                          | 7  |

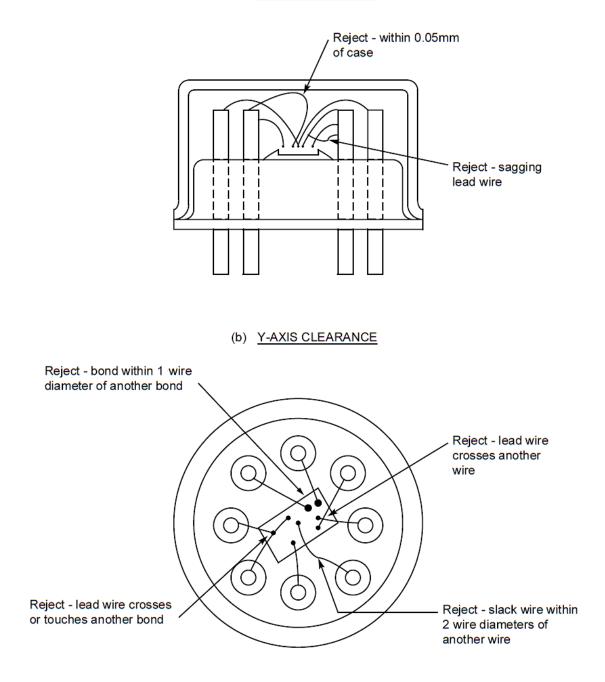

| 5.1 | FIGURE 1: PARTICLE LOCATIONS, PIGTAILS, TRIMMING WIRES AND VOIDS | 7  |

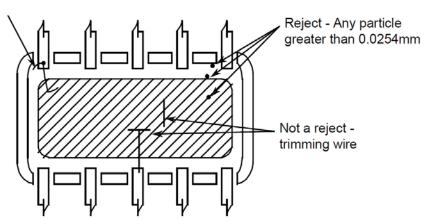

| 5.2 | FIGURE 2: ACCEPTABLE AND UNACCEPTABLE BONDING MATERIAL BUILD-UP  | 8  |

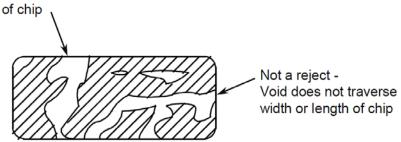

| 5.3 | FIGURE 3: EXTRANEOUS BONDING MATERIAL BUILD-UP                   | 9  |

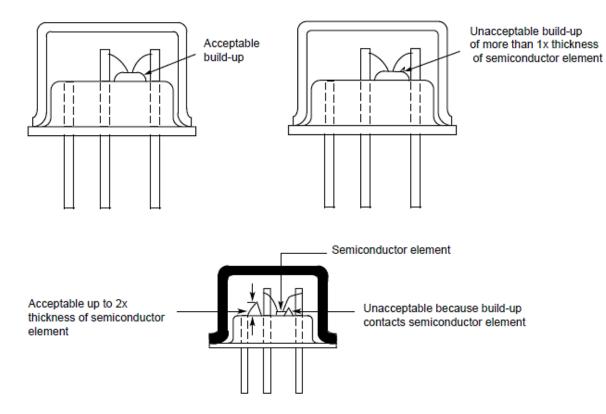

| 5.4 | FIGURE 4: CLEARANCE IN DUAL-IN-LINE OR FLAT PACK TYPE DEVICE     | 10 |

| 5.5 | FIGURE 5: CLEARANCE IN ROUND TRANSISTOR TYPE DEVICE              | 11 |

PAGE 5

No. 2099000

**ISSUE 2**

## 1 <u>SCOPE</u>

This specification, to be read in conjunction with ESCC Basic Specification No. 20900, Radiographic Inspection, contains additional requirements to be applied to Integrated Circuits.

### 2 GENERAL REQUIREMENTS

#### 2.1 <u>APPLICABILITY</u>

The following criteria may not be varied or modified after commencement of any inspection stage. Any ambiguity or proposed minor deviation shall be referred to the ESCC Executive for resolution and approval.

#### 2.2 PROCEDURE

All items shall be examined in such a manner that a minimum of handling and movement of the components is involved.

#### 3 <u>X-RAY PHOTOGRAPHS</u>

Each component shall be radiographed once along one axis.

#### 4 DETAILED REQUIREMENTS

#### 4.1 <u>REJECT CRITERIA</u>

The individual device examination shall include, but not be limited to, inspection for foreign particles, build-up of bonding material, placement of lead wires, bond of lead to semiconductor element and lead to terminal post, and mounting of semiconductor element. Any device for which the radiograph reveals any of the following defects shall be rejected.

#### 4.2 PRESENCE OF EXTRANEOUS MATTER

Extraneous matter (foreign particles) shall include, but not be limited to:

- (a) Any foreign particle, loose or attached, greater than 0.0254mm (see Figure 1), or of any lesser size which is sufficient to bridge non-connected conducting elements of the device.

- (b) Any wire tail extending beyond its normal end by more than two diameters at the semiconductor die pad or by more than four wire diameters at the package post (see Figure 1).

- (c) Any burr on a post (header lead) greater than 0.08mm in its major dimension or of such configuration that it may break away.

- (d) Excessive semiconductor element bonding material build-up:

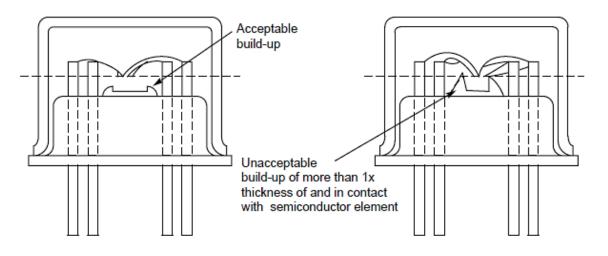

- A semiconductor element shall be mounted and bonded so that it is not tilted more than 10 degrees from the normal mounting surface. The bonding agent that accumulates around the perimeter of the semiconductor element and touches the side of the semiconductor element shall not accumulate to a thickness greater than that of the semiconductor element (see Figures 2 and 3). Where the bonding agent is built up, but is not touching the semiconductor element, the build-up shall not be greater than twice the thickness of the semiconductor element.

- There shall be no visible extraneous material of 0.0254mm or larger in the major dimension. Loose bonding material will be considered extraneous material. Excessive (but not loose) bonding material will not be considered extraneous unless it fails to meet the thickness requirements or the accumulation of bonding material is in the pedestal form (see Figures 2 and 3).

- (e) Gold flaking on the header or posts or anywhere inside the case.

- (f) Extraneous ball bonds anywhere inside the case, except for attached residue when rebonding is allowed.

#### 4.3 UNACCEPTABLE CONSTRUCTION

In the examination of devices, the following aspects shall be considered unacceptable construction and devices that exhibit the following defects shall be rejected:

- (a) Voids When radiographing devices, certain types of mounting do not give true representations of voids. When such devices are inspected, the mounting shall be noted on the inspection report (see Figure 1).

- 1. Contact area voids in excess of one-half of the total contact area.

- 2. A single void equal to the length of the semiconductor element.

- 3. A single void that traverses the width of the semiconductor element.

- (b) Wires present other than those connecting specific areas of the semiconductor element to the external leads. Device designs calling for the use of such wires, including jumping wires, are acceptable (see Figure 1).

- (c) Cracks, splits or chips of the electrical elements.

- (d) Defective seal Any device wherein the integral lid seal is not continuous or is reduced from its designed sealing width by more than 75%. Expulsion resulting from the final sealing operation is not considered extraneous material as long as it can be established that it is attached to the parent material and does not exhibit a tear-drop configuration (i.e. where the base support's least dimension is smaller than the dimension it is supposed to support).

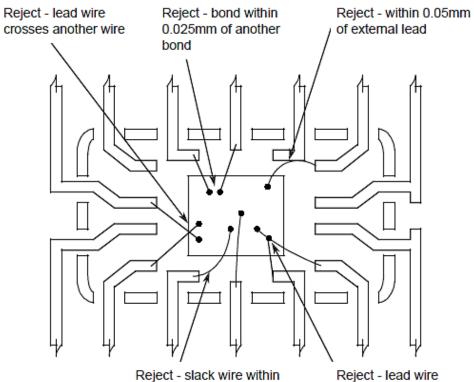

- (e) Inadequate clearance Acceptable devices shall have adequate internal clearance to ensure that the elements cannot contact one another or the case. No cross-overs shall be allowed. Depending upon the case type, devices shall be rejected for the following conditions:

- (1) Flat pack and dual-in-line (see Figure 4).

- (a) Any lead wire that appears to touch or cross another lead wire or bond (Y plane only).

- (b) Any lead wire that deviates from a straight line from bond to external lead and appears to be within 0.05mm of another wire or bond (Y plane only).

- (c) Lead wires that do not deviate from a straight line from bond to external lead and appear to touch another wire or bond (Y plane only).

- (d) Any lead wire that touches or comes within 0.05mm of the case or external lead to which it is not attached (X and Y planes).

- (e) Any bond that is less than 0.025mm (excluding bonds connected by a common conductor from another bond (Y plane only).

- (f) Any wire making a straight line run from die bonding pad to package post that has no arc.

**ISSUE 2**

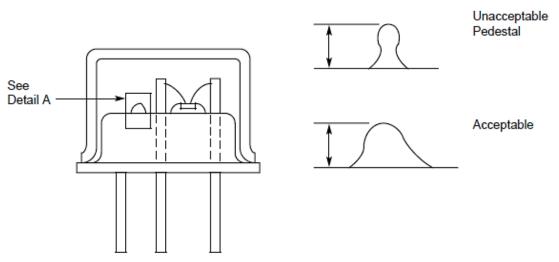

- (2) Round Transistor Type (see Figure 5).

- (a) Any lead wire that touches or comes within 0.05mm of the case or external lead to which it is not attached (X and Y planes).

- (b) Lead wires that sag below an imaginary plane across the top of the bond (X plane only).

- (c) Any lead wire that appears to touch or cross another lead wire or bond (Y plane only).

- (d) Any lead wire that deviates from a straight line from bond to external lead and appears to touch or be within 0.05mm of another wire or bond (Y plane only).

- (e) Any bond that is less than 0.025mm (excluding bonds connected by a common conductor) from another bond (Y plane only).

- (f) Any wire making a straight line run from die bonding pad to package post that has no arc.

### 5 <u>FIGURES</u>

## 5.1 FIGURE 1: PARTICLE LOCATIONS, PIGTAILS, TRIMMING WIRES AND VOIDS

(a) Particle Locations, Pigtails and Trimming Wires

Reject - Wire tail longer than

- 2 wire diameters at pad or

- 4 wire diameters at post

(b) Voids

Reject -Void traverse width

**ISSUE 2**

## 5.2 FIGURE 2: ACCEPTABLE AND UNACCEPTABLE BONDING MATERIAL BUILD-UP

PAGE 9

**ISSUE 2**

## 5.3 FIGURE 3: EXTRANEOUS BONDING MATERIAL BUILD-UP

DETAIL A 2x semiconductor element height maximum

ISSUE 2

### 5.4 FIGURE 4: CLEARANCE IN DUAL-IN-LINE OR FLAT PACK TYPE DEVICE

0.05mm of another wire

Reject - lead wire crosses over a bond

## 5.5 FIGURE 5: CLEARANCE IN ROUND TRANSISTOR TYPE DEVICE

#### (a) X-AXIS CLEARANCE