Page 1 of 47

## **ESCC QUALIFIED MANUFACTURERS LIST (QML)**

Issue 31

December 2025

Document Custodian: European Space Agency – see <https://escies.org>

### **LEGAL DISCLAIMER AND COPYRIGHT**

European Space Agency, Copyright © 2025. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without prior permission of the European Space Agency and provided it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

**DOCUMENTATION CHANGE NOTICE**

(Refer to <https://escies.org> for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1786    | <p><b>Extension:</b><br/>356C Exxelia SAS, France<br/>357C Microchip Technology, France<br/>359C Microchip Technology, France</p> <p><b>New:</b><br/>394 ST Microelectronics, France<br/>The ST ASIC platform 28nm FDSOI has been qualified. The first ESCC-qualified product based on this technology is the NG-ULTRA NX2H540TSC, a radiation-hardened-by-design SoC FPGA supplied by NanoXplore.</p> |

## **FOREWORD**

This document contains a list of qualified manufacturers that have been certified by the European Space Agency for technology flows to the rules of the ESCC system with principle reference to ESCC Basic Specification no. [25400](#).

The qualified electronic components produced from the technology flows are intended for use in ESA and other spacecraft and associated equipment in accordance with the requirements of the ECSS standard ECSS-Q-ST-60.

Each technology flow qualification and its subsequent maintenance is monitored and overseen by the ESCC executive. ESA certifies the qualification upon receipt of a formal application from the executive stating that all applicable ESCC requirements have been met by the pertinent manufacturer. The qualified status of a technology flow is noted by an entry in this document, a corresponding entry in the European space components information exchange system, ESCIES, and the issue of a certificate to the qualified manufacturer.

## TABLE OF CONTENTS

|          |                                                                 |           |

|----------|-----------------------------------------------------------------|-----------|

| <b>1</b> | <b>PROMOTION</b>                                                | <b>6</b>  |

| <b>2</b> | <b>PROCURER'S RESPONSIBILITY</b>                                | <b>6</b>  |

| <b>3</b> | <b>QML ORGANISATION</b>                                         | <b>6</b>  |

| 3.1      | TECHNOLOGY FLOWS AND PROCESS CAPABILITY APPROVALS (PCA)         | 6         |

| 3.2      | QUALIFIED COMPONENTS                                            | 6         |

| 3.3      | TYPE DESIGNATION                                                | 6         |

| 3.4      | COMPONENT CHARACTERISTICS                                       | 6         |

| 3.5      | MANUFACTURER                                                    | 6         |

| <b>4</b> | <b>TABLE OF QUALIFIED COMPONENT TECHNOLOGY</b>                  | <b>7</b>  |

| <b>5</b> | <b>QUALIFIED TECHNOLOGY FLOWS</b>                               | <b>8</b>  |

| 5.1      | <b>FILTERS (05)</b>                                             | <b>8</b>  |

| 5.1.1    | KONSBERG DEFENCE & AEROSPACE, Norway: SAW FILTERS               | 8         |

| 5.2      | <b>MICROCIRCUITS (08)</b>                                       | <b>13</b> |

| 5.2.1    | Microchip Technology, France: ATC18RHA                          | 13        |

| 5.2.2    | Microchip Technology, France: ATMX150RHA                        | 17        |

| 5.2.3    | ST Microelectronics, France: ASIC platform C65Space             | 24        |

| 5.2.4    | ST Microelectronics, France: ASIC platform FDSOI 28nm           | 29        |

| 5.2.5    | United Monolithic Semiconductors, France : GaN HEMT             | 35        |

| 5.3      | <b>RESISTORS (10)</b>                                           | <b>40</b> |

| 5.3.1    | VISHAY S.A. Fance: Chip resistors                               | 40        |

| 5.4      | <b>TRANSFORMERS (08)</b>                                        | <b>46</b> |

| 5.4.1    | Exxelia SAS: Custom magnetics: linear and toroidal technology   | 46        |

| 5.4.2    | Flux A/S: Custom Magnetics (Inductors, Chokes and Transformers) | 48        |

**1 PROMOTION**

It is permitted to advertise the ESCC qualification status of a component provided such publicity or advertisement does not state or imply that the component is the only qualified one of that particular type, range or family.

**2 PROCURER'S RESPONSIBILITY**

When procuring ESCC qualified components, the procurer is responsible for ensuring that the qualification status is valid and that delivered components fulfil the specified requirements of the applicable ESCC specifications. The procurer is advised to utilise the ESCC non- conformance system, per ESCC Basic Specification No. [22800](#), in the event that a qualified manufacturer delivers non-conforming components.

**3 QML ORGANISATION****3.1 TECHNOLOGY FLOWS AND PROCESS CAPABILITY APPROVALS (PCA)**

The individual Technology Flows and PCA and are listed in this document by manufacturer in alphabetical order. They may also be found on the ESCIES web site, <https://escies.org>. A Technology Flow Abstract is provided to describe the main features of the qualified Technology Flow.

**3.2 QUALIFIED COMPONENTS**

Under each technology flow a list of the qualified components is provided.

**3.3 TYPE DESIGNATION**

Wherever possible the referenced type (style) designations are derived from industrial standards. Where no standardised type designation is applicable the manufacturer's designation is referenced.

**3.4 COMPONENT CHARACTERISTICS**

The precise characteristics of the qualified component are defined in the referenced ESCC Detail specifications.

**3.5 MANUFACTURER**

Contact information and plant locations are indicated in the individual Technology Flow listings. Contact information may also be found in the ESCC QML section of the ESCIES web site, <https://escies.org>.

4

**TABLE OF QUALIFIED COMPONENT TECHNOLOGY**

| Components          | Sub-section                                           | Manufacturers                    | Certificates |

|---------------------|-------------------------------------------------------|----------------------------------|--------------|

| 05<br>Filters       | SAW                                                   | Kongsberg Defence & Aerospace    | 313F         |

| 08<br>Microcircuits | Digital C-MOS: ATC18RHA                               | Microchip Technology Nantes      | 357C         |

|                     | Digital C-MOS: ATMX150RHA                             | Microchip Technology Nantes      | 359C         |

|                     | ASIC platform C65Space                                | STMicroelectronics               | 381A         |

|                     | ASIC platform 28nm FDSOI                              | STMicroelectronics               | 394          |

|                     | GaN HEMT                                              | United Monolithic Semiconductors | 388          |

| 10<br>Resistors     | Chip                                                  | Vishay SA, Sfernice              | 287J         |

| 14<br>Transformers  | Custom magnetics: linear or toroidal technology       | Exxelia Magnetics                | 356C         |

|                     | Custom Magnetics (Inductors, Chokes and Transformers) | Flux A/S                         | 364A         |

## 5 QUALIFIED TECHNOLOGY FLOWS

The following technology flows are qualified.

### 5.1 FILTERS (05)

#### 5.1.1 KONSBERG DEFENCE & AEROSPACE, Norway: SAW FILTERS

##### 5.1.1.1 *Contact Information*

| Address                                                                     | ESCC Chief Inspector                                                                                |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Kongsberg Defence & Aerospace<br>Knutsrødveien 7<br>N-3189 Horten<br>Norway | Mrs Cecilie Berg<br>Tel: (+47) 3303 2700<br>Fax: (+47) 3303 2800<br>email: cecilie.berg@norspace.no |

##### 5.1.1.2 *Qualification*

| Current Qualification<br>Certificate No. | In QML since: | Type Designation                                                               |

|------------------------------------------|---------------|--------------------------------------------------------------------------------|

| 313F                                     | Aug. 2011     | SAW filters (transversal band pass/resonator/notch/low loss impedance element) |

### APPLICABLE ESCC DOCUMENTS:

ESCC Generic Specification No. [3502](#)

ESCC Detail Specification Nos. [3502/002](#)

### NORSPACE PROCESS IDENTIFICATION DOCUMENTS:

PID534\_9 SAW Device Assembly with flow NORSF-A1

PID630\_9 SAW Crystal Manufacturing with flow NORSF-C1

##### 5.1.1.3 *List of Qualified Components*

For each design, a detail specification is produced by Kongsberg Space Electronics. Where the SAW component is not proprietary to the customer the detail specification is published in ESCIES as a supporting document. Available detail specifications are found in the table below.

| Detail Specification     | Component Type                                                                  |

|--------------------------|---------------------------------------------------------------------------------|

| <a href="#">3502/002</a> | SAW Filters, Hermetically Sealed, Surface Mount, Frequency Range 10 MHz - 4 GHz |

#### 5.1.1.4 Technology Flow Abstract

##### General features

The Technology Flow covers the design, fabrication, assembly, screening, in-process control and testing of the Norspace SAW filters manufactured within the NORSF-C1 and NORSF-A1 processes. The design, crystal manufacturing, assembly, screening and testing is performed in Kongsberg Space Electronics facility at Knudsrødveien 7 in Horten, Norway.

| Technology Flow       | Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design                | Norspace specification Ko 03.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Crystal manufacturing | <p>Process flow NORSF-C1 on purchased SAW-grade surface polished wafers.</p> <p><u>Wafer materials:</u><br/>Quartz (<math>\text{SiO}_2</math>), Lithium niobate (<math>\text{LiNbO}_3</math>), Lithium tantalate (<math>\text{LiTaO}_3</math>), Langasite (<math>\text{La}_3\text{Ga}_5\text{SiO}_{14}</math>)</p> <p><u>Wafer dimensions:</u></p> <p>3" diameter 0.5 mm thick</p> <p>3" diameter 1.0 mm thick</p> <p>4" diameter 1.5 mm thick</p>                                                                                                                                                                                                            |

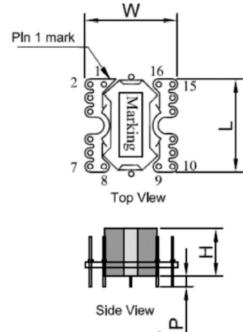

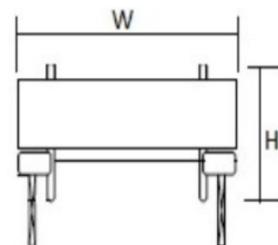

| Assembly              | <p>Process flow NORSF-A1.</p> <p>Crystal dimensions:<br/>from 1.7 mm x 3.1 mm up to 8 mm x 76 mm.</p> <p>Packages:</p> <p>-Gold plated Fe-Ni-Co-alloy flat packs.<br/>From 4 up to 50 leads with ceramic or glass feedthroughs. External wings for screw attach on some types<br/><u>Package dimensions:</u> From 8 mm x 8 mm up to 85 mm x 12 mm.</p> <p>-Gold plated Fe-Ni-Co-alloy flat packs with Cu-W base, 4 or 6 leads and ceramic feedthroughs.<br/><u>Package dimensions:</u> From 11 mm x 11 mm up to 7 mm x 21 mm.</p> <p>-Gold plated ceramic Leadless Chip Carrier (LCC) package, 10 solder pads.<br/><u>Package dimension:</u> 5 mm x 7 mm.</p> |

| Screening and Test    | <p>Process flow NORSF-A1.</p> <ul style="list-style-type: none"><li>-Incoming inspection</li><li>-In-process inspection</li><li>-100% Wafer probe electrical test</li><li>-100% Visual inspection</li><li>-Final production tests</li><li>-Customer Source Inspection</li><li>-Screening</li><li>-Burn-in and electrical measurements</li><li>-Test procedures</li><li>-External visual inspection</li><li>-Qualification testing</li></ul>                                                                                                                                                                                                                   |

## Basic Information

The SAW devices are passive devices and typically require external tuning. Frequency range: From 10 MHz up to 4 GHz.

Max operating temperature range: -30 / +85 °C (maximum), -20 / +70 °C (typical).

Input power: design sensitive.

## Component Types

- Transversal band pass SAW filters with frequencies up to 4 GHz.

- SAW Resonator filters

- SAW Notch filters

- Impedance element filters with low loss

### 5.1.1.5 Technology Flow definition

#### 1. Design

The design programs are in-house developed procedures and libraries. Each new design is custom made for the application by Kongsberg Space Electronics design engineers. The design centre is in Horten, Norway.

#### Transversal band pass SAW filters

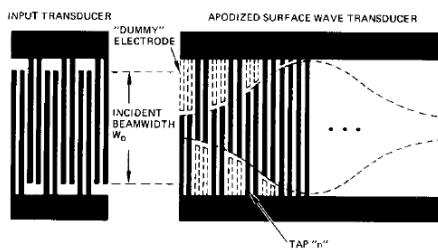

The transversal filters consist of one input transducer and one output transducer, see figure below. The transducers are interdigital transducers formed by a metal pattern on a piezoelectric material (wafer). The transducers can be withdrawal weighted and/or length (apodization) weighted. The detailed weighting functions are calculated in a dedicated filter synthesis software and used as input to the mask layout software. The simulation of the filter response is performed by a dedicated SAW Analysis software.

## Resonator filters

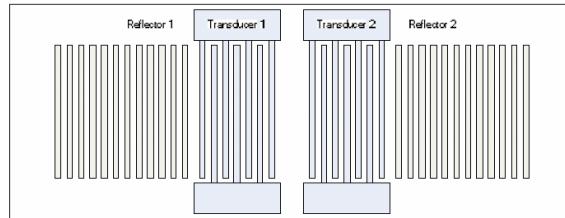

The resonator filter consists of input and output transducers as described above. These are normally unweighted. The transducers are backed by reflectors, see figure below. The reflectors are  $1/4$  wide etched grooves or metal fingers. The same software is used for simulation of the transducers and reflectors.

## SAW Notch filters

The notch are based on single port resonator elements, so called impedance elements (see below).

### Impedance element filters with low loss

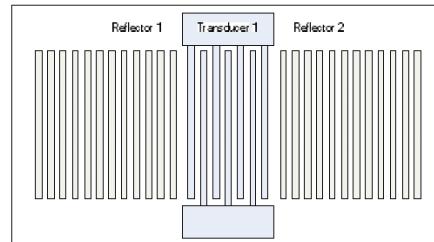

Impedance element filters are constructed from one port SAW resonators. The one port SAW resonators consist of one interdigital transducer backed by one reflector on each side, as shown in the figure below.

## 2. Fabrication

The NORSF-C1 process at Kongsberg Space Electronics comprises:

- SAW crystal manufacturing on SAW grade polished single crystal wafers from quartz, LiNbO<sub>3</sub>, LiTaO<sub>3</sub> and La<sub>3</sub>Ga<sub>5</sub>SiO<sub>14</sub> (langasite)

- Externally purchased SAW wafers

- SAW wafer thickness between 0.5 mm and 1.5 mm

- Photolithography with line widths down to 0.3  $\mu$ m. No upper limit. Metallization performed with Al or Cr/Al. Metal thickness 400 to 10 000  $\text{\AA}$ .

The process can manufacture SAW elements of band pass, resonator or notch type with centre frequencies in the range 10 MHz to 4 GHz.

## 3. Assembly

Norspace assembly flow NORSF-A1 technology flow covers the following capabilities:

| Package                                                                                    | Die Attach      | Wire Bond                             | Lid Seal                                | Leads     |

|--------------------------------------------------------------------------------------------|-----------------|---------------------------------------|-----------------------------------------|-----------|

| Flatpack/LCC. Au plated. CuW base/Fe-Ni-Co alloy or ceramic with Fe-Ni-Co alloy seal ring. | Silicone rubber | Ultrasonic ball- wedge, 25 µm Au wire | Resistance seam sealing. N2 atmosphere. | Au plated |

#### 4. Test

Measurements are performed using a Vector Network Analyzer (VNA).

All equipment in the electrical test set-up shall have the same characteristic impedance. The S-parameters are measured on the VNA and transferred to a PC for post-processing and analysis. Before testing the VNA and its test cables must be calibrated as specified in the manual for the instrument (full 2-port calibration).

Test vehicles used for qualification: SQF-3800, SLC-4320.

Test vehicles used for maintenance: SQF-3800, SLC-3900, or similar devices.

#### 5. Radiation

The devices are regarded as radiation insensitive within a small drift in centre frequency and phase allowed for in the design margins.

Radiation testing has been performed successfully up to 50 MRad(Si) for quartz and 1 MRad(Si) for LiNbO<sub>3</sub>, LiTaO<sub>3</sub> and Langasite.

Qualified wafer materials: Quartz, LiNbO<sub>3</sub>, LiTaO<sub>3</sub>, Langasite (La<sub>3</sub>Ga<sub>5</sub>SiO<sub>12</sub>)

5.2 MICROCIRCUITS (08)

5.2.1 Microchip Technology, France: ATC18RHA

5.2.1.1 *Contact Information*

| Address                                                                  | ESCC Chief Inspector                                                                                  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Microchip Technology Nantes<br>Route de Gachet<br>44300 Nantes<br>France | Ms V. Lepaludier<br>Tel. +33 2 40 18 1633<br>FAX +33 2 40 18 1946<br>Valerie.Lepaludier@microchip.com |

5.2.1.2 *Qualification*

| Current Qualification Certificate No. | In QML since: | Type Designation                                                                         |

|---------------------------------------|---------------|------------------------------------------------------------------------------------------|

| 357C                                  | May 2019      | Integrated Circuits, Silicon, Monolithic, CMOS, Cell-Based Array, based on Type ATC18RHA |

**Remarks:**

Certificate 357 supersedes previous certificate 312B Rev1. New certificate reflects significant changes in the supply chain.

An End-Of-Life of the ATC18RHA ASIC offer for new design has been announced by Microchip in January 2021. Detail is available in Microchip Notification CRS20-0158 (information added in QML issue 22, published in March 2021). ATMX150RHA ASICs is to be used as replacement for any new design. Microchip will stop wafer manufacturing launch by December 2021. Microchip commits to maintain the wafer/die stock, based on customer needs. Microchip will continue Flight Models manufacturing from this wafer/die stock.

**Applicable documents:**

ESCC Generic Specification No. [9000](#); ESCC Detail Specification No. [9202/080](#)

ATC18RHA Process Identification Document PID 0032 Rev G, MMT assembly PID 1G-QM-0105 and HCM columns manufacturing and assembly PID 11 issue F.

5.2.1.3 *List of Qualified Components*

For each ASIC design an ASIC Sheet is produced by Microchip for use in conjunction with the ESCC Detail Specification No. [9202/080](#). Where the ASIC is not proprietary to the customer the ASIC sheet is published in ESCIES as a supporting document.

| ASIC Sheet | Component Type |

|------------|----------------|

|            |                |

In the case of ATC18RHA, standard components are also available. These are listed below with their full ESCC Detail Specification:

| Detail Specification | Component Type                                                                         |

|----------------------|----------------------------------------------------------------------------------------|

| 9512/004             | Integrated Circuits, Silicon, 32-bit SPARC Processor, based on Type AT697F             |

| 9512/005             | Integrated circuits, silicon monolithic, SPARC V8 GNSS controller based on type AT7991 |

#### 5.2.1.4 Technology Flow Abstract

#### GENERAL FEATURES

ATC18RHA standard cells family is designed with a 0.18µm radiation hard CMOS technology. This offering is based on 6 metal layers at 1.8V +/-0.15V for the core and 3.3V +/-0.3V for the periphery. This family features arrays with up to 7 Mgates and 544 pads. With its high speed performance, its low supply current and its radiation hard level, the ATC18RHA is suitable for digital applications working in radiation intensive environment.

#### BASIC INFORMATION

- CMOS technology AT58KRHA

- 40 to 70 kgates per mm<sup>2</sup>

- Periphery power supply 3.3V and 2.5V

- Core power supply 1.8V

- Low supply current :

- Operating maximum value: 85nW/gate/MHz with a duty cycle at 20%

- I/O Interfaces:

- Cold sparing

- High speed LVDS (655 Mps) and LVPECL

- PCI

- 544 pads (+ 8 pads power only)

- Embedded memories: Compiled and Synthesized

- EDAC library

- Radiation :

- No Single Event Latch-Up below a LET Threshold of 80 MeV/mg/cm<sup>2</sup> at high temperature

- SEU hardened DFF's to 30 MeV/mg/cm<sup>2</sup>

- Tested up to 300 krad (Si), Radiation Level is 100 krads (Si).

#### COMPONENT TYPES

Device Types as per ESCC Detail Specification 9202/080 and individual custom ESCC ASIC Sheets.

| Die          | Supply Voltage I/O / core | Max programmable I/O's | Case      | Typical Routable gates |

|--------------|---------------------------|------------------------|-----------|------------------------|

| ATC18RHA_216 | 2.5V or 3.3V/1.8V         | 216                    | CQFP-F256 | 1M                     |

| ATC18RHA_216 | 2.5V or 3.3V/1.8V         | 216                    | CQFP-F196 | 1M                     |

| Die          | Supply Voltage<br>I/O / core | Max<br>programmable<br>I/O's | Case      | Typical<br>Routable gates |

|--------------|------------------------------|------------------------------|-----------|---------------------------|

| ATC18RHA_216 | 2.5V or 3.3V/1.8V            | 216                          | CQFP-F160 | 1M                        |

| AT697F       | 3.3V/1.8V                    | -                            | CQFP-F256 | 0.85M                     |

| ATC18RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CQFP-F352 | 2.2M                      |

| ATC18RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CQFP-F256 | 2.2M                      |

| ATC18RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CQFP-F196 | 2.2M                      |

| ATC18RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CQFP-F160 | 2.2M                      |

| ATC18RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CLGA-349  | 2.2M                      |

| ATC18RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CCGA-349  | 2.2M                      |

| ATC18RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CQFP-T352 | 3.5M                      |

| ATC18RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CQFP-T256 | 3.5M                      |

| ATC18RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CLGA-472  | 3.5M                      |

| ATC18RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CLGA-349  | 3.5M                      |

| ATC18RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CCGA-472  | 3.5M                      |

| ATC18RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CCGA-349  | 3.5M                      |

| ATC18RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CQFP-T352 | 5.5M                      |

| ATC18RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CQFP-F256 | 5.5M                      |

| ATC18RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CLGA-625  | 5.5M                      |

| ATC18RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CLGA-472  | 5.5M                      |

| ATC18RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CLGA-349  | 5.5M                      |

| ATC18RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CCGA-625  | 5.5M                      |

| ATC18RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CCGA-472  | 5.5M                      |

| ATC18RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CCGA-349  | 5.5M                      |

| AT7991       | 3.3V/1.8V                    | -                            | CQFP-352  | 7.6M                      |

| ATC18RHA_544 | 2.5V or 3.3V/1.8V            | 544                          | CLGA-625  | 7M                        |

| ATC18RHA_544 | 2.5V or 3.3V/1.8V            | 544                          | CCGA-625  | 7M                        |

#### 5.2.1.5 Technology Flow Definition

The Technology Flow Definition domain covers the design, fabrication, assembly and testing of the ATC18RHA standard cells family.

#### 1. Design

The design manual and the ASIC library data books cover the design in the Microchip Technology Nantes associated Design Centers (Nantes-France, Milan-Italy, Garching-Germany and Winnersh-UK).

- ATC18RHA Design manual ATD-DE-GR-R0212

- ATC18RHA TOS manual ATD-DE-GR-R0324

- ATC18RHA Buffers library databook ATD-TS-LR-R0252

|                                          |                 |

|------------------------------------------|-----------------|

| – ATC18RHA Cells library databook        | ATD-TS-LR-R0251 |

| – ATC18RHA Memory cells library databook | ATD-TS-LR-R0254 |

| – ATC18RHA specific library databook     | ATD-TS-LR-R0253 |

All ASIC designs will be performed by the customer at the customer site, with Microchip supported tools (front end).

No new design is proposed on this ASIC technology, replaced by the ATM150RHA.

## 2. Fabrication

The ATC58KRHA, processed in UMC Taiwan, is a 0.18µm CMOS, 6 metal, Ti, TiN and AlCu process.

From 2021 December, wafer fabrication shall not be maintained. Flight models shall be manufactured from wafer in stock.

## 3. Assembly

The assembly of ATC18RHA devices is performed in MMT, Thailand, with the following capabilities:

- Die attach Cyanate Ester (JM7000)

- Wire bond Ultrasonic Wedge, 25 and 32 µm Al

- Lid sealing Brazed with Au/Sn alloy or seam welded

- Leads/pads Gold plated (CQFP and CLGA)

The assembly of columns is performed in SERMA HCM, La Rochelle, with the following capabilities:

- Columns 85Pb15Sn with Tinned Copper ribbon, 0.38 mm diameter

## 4. Control and Test

The control and test of ATC18RHA devices is performed in Microchip technology Nantes. It includes Lot Acceptance, Test Flows and Test Procedures, Qualification Test and Reliability Monitoring, Screening and associated electrical tests and inspections.

## 5. TCVs and SEC

The die ATC18RHA\_324 is used for both test vehicles. All details are described in the ATC18RHA test chip specification, reference ADF-DE-R0561-CUP.

### **V56 TEST VEHICLE**

The V56 is a buffer test vehicle representative of the range of buffers available for performance testing in the CQFP 256 package. It contains standard IO33 buffers, specific IO33 buffers (LVDS, PCI), a PLL, a set of ring oscillators made of different library cells and a set of interconnect lines.

### **V40 (5 METAL LAYERS) OR V52 (6 METAL LAYERS) TEST VEHICLE – TECHNOLOGY SEC**

The V40/V52 SEC is developed for performance and radiation testing in the CQFP 256 package. It contains a set of memory blocks (compiled memories with and without EDACs and synthesized (on gates) memories made with standard and hardened latches), shift registers chains and a PLL.

## 6. Radiation Characteristics

The AT58KRHA family has been developed to fulfil the following characteristics:

- No Single Event Latch-up below a LET Threshold of 80MeV/mg/cm<sup>2</sup> at high temperature

- Availability of SEU hardened cells

- Total dose capability over 100 krads(Si)

### 5.2.1.6 Manufacturing sites

**DESIGN:**

Microchip Technology Nantes, BP70602, 44306 Nantes Cedex 3, France

**WAFER FABRICATION:**

UMC Fab 8S, Hsin-Chu, Taiwan

**DIE ASSEMBLY:**

MMT, Microchip Technology (Thailand) Co., Ltd. 17/2 Moo 18 Suwintawong Road, Saladang, Bangnumpiew Chachoengsao, Thailand 24000

**CCGA COLUMN ASSEMBLY:**

HCM SYSTREL, 34 Av. Joliot Curie, ZI Perigny, 17185 Perigny Cedex, France

**CONTROL AND TEST:**

Microchip Technology Nantes, BP70602, 44306 Nantes Cedex 3, France

### 5.2.2 Microchip Technology, France: ATMX150RHA

#### 5.2.2.1 Contact Information

| Address                                                                  | ESCC Chief Inspector                                                                                                                                        |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microchip Technology Nantes<br>Route de Gachet<br>44300 Nantes<br>France | Ms V. Lepaludier<br>Tel. +33 2 40 18 1633<br>FAX +33 2 40 18 1946<br><a href="mailto:Valerie.Lepaludier@microchip.com">Valerie.Lepaludier@microchip.com</a> |

#### 5.2.2.2 Qualification

| Current Qualification Certificate No. | In QML since: | Type Designation                                                                                   |

|---------------------------------------|---------------|----------------------------------------------------------------------------------------------------|

| 359C                                  | May 2019      | Integrated Circuits, Silicon, Monolithic, CMOS, Cell-Based Array, based on ATMX150RHA ASIC family. |

**Remark:**

Certificate 359 supersedes previous certificate 342 Rev1. New certificate reflects significant changes in the supply chain.

An End-Of-Life of the ATMX150RHA ASIC offer for new design has been announced by Microchip in April 2025. Information added in QML issue 31. Microchip will stop wafer manufacturing launch by October 2025. Microchip commits to maintain the wafer/die stock, based on customer needs. Microchip will continue Flight Models manufacturing from this wafer/die stock.

**APPLICABLE DOCUMENTS:**

ESCC Generic Specification No. [9000](#); ESCC Detail Specification No. [9202/083](#)

Microchip Process Identification Document PID 37 Rev G, MMT PID 1G-QM-0105, HCM columns manufacturing and assembly PID 11 issue F.

#### 5.2.2.3 *List of Qualified Components*

For each ASIC design an ASIC Sheet is produced by Microchip for use in conjunction with the ESCC Detail Specification No. [9202/083](#). Where the ASIC is not proprietary to the customer the ASIC sheet is published in ESCIES as a supporting document.

| ASIC Sheet | Component Type |

|------------|----------------|

|            |                |

#### 5.2.2.4 *Technology Flow Abstract*

**GENERAL FEATURES**

The ATMX150RHA is a mixed-signal ASIC offer providing high-performance and high-density solutions for space applications. The ATMX150RHA standard cells family is designed with a 0.15µm radiation-hardened CMOS technology. This offer is based on a 5 metal layers with an optional 6th thick metal layer technology, dedicated for large ASIC's to avoid voltage drop issues. The core is supplied at 1.8V +/-0.15V and the periphery at 3.3V +/-0.3V or 2.5V +/- 0.2V. This family features arrays with up to 22 Mgates and more than 700 pads. With its high-speed performance, its low supply current and its radiation hardening level, the ATMX150RHA is suitable for digital applications working in radiation intensive environment.

**BASIC INFORMATION**

- CMOS technology AT77K9RHA

- 40 to 70 kgates per mm<sup>2</sup>

- Periphery power supply 3.3V and 2.5V

- Core power supply 1.8V

- Low supply current: Operating maximum value: 8.8 nA/gate/MHz with a duty cycle at 20%

- I/O Interfaces:

- Cold sparing

- High speed LVDS (655 Mps) and LVPECL

- PCI

- 704 pads (+ 8 pads power only)

- Compiled memory cells (ROM, SRAM, DPRAM, register files)

- Pre-qualified IP's

- a regulator 1.8V 200mA Linear Voltage Regulator REG200RHA

- a 8-channels analog input multiplexer MUX8RHA

- a PLL 40 to 450 MHz PLL400MRHA

- a RC Oscillator 4/8/10/12 MHz OSCRC10MRHA

- a bandgap 1.215V reference BG1V2RHA

- Radiation:

- No Single Event Latchup to a LET threshold of 67.7 MeV.cm<sup>2</sup>/mg, and up to 78. 2 MeV.cm<sup>2</sup>/mg, 30°-tilted at high temperature.

- SEU Hardened DFF's to 30 MeV/mg/ cm<sup>2</sup>

- Tested up to 300 kRads(Si).

### **COMPONENT TYPES**

Device Types as per ESCC Detail Specification [9202/083](#) and individual custom ESCC ASIC Sheets:

| Die            | Supply Voltage<br>I/O / core | Max<br>programmable<br>I/O's | Case     | Typical Routable<br>gates |

|----------------|------------------------------|------------------------------|----------|---------------------------|

| ATMX150RHA_216 | 2.5V or 3.3V/1.8V            | 216                          | CQFP-256 | 1M                        |

| ATMX150RHA_216 | 2.5V or 3.3V/1.8V            | 216                          | CQFP-132 | 1M                        |

| ATMX150RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CQFP-352 | 2.2M                      |

| ATMX150RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CQFP-256 | 2.2M                      |

| ATMX150RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CQFP-132 | 2.2M                      |

| ATMX150RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CLGA-472 | 2.2M                      |

| ATMX150RHA_324 | 2.5V or 3.3V/1.8V            | 324                          | CCGA-472 | 2.2M                      |

| ATMX150RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CQFP-352 | 3.5M                      |

| ATMX150RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CQFP-256 | 3.5M                      |

| ATMX150RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CLGA-625 | 3.5M                      |

| ATMX150RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CLGA-472 | 3.5M                      |

| ATMX150RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CCGA-625 | 3.5M                      |

| ATMX150RHA_404 | 2.5V or 3.3V/1.8V            | 404                          | CCGA-472 | 3.5M                      |

| Die            | Supply Voltage<br>I/O / core | Max<br>programmable<br>I/O's | Case     | Typical Routable<br>gates |

|----------------|------------------------------|------------------------------|----------|---------------------------|

| ATMX150RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CQFP-352 | 5.5M                      |

| ATMX150RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CQFP-256 | 5.5M                      |

| ATMX150RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CLGA-625 | 5.5M                      |

| ATMX150RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CLGA-472 | 5.5M                      |

| ATMX150RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CCGA-625 | 5.5M                      |

| ATMX150RHA_504 | 2.5V or 3.3V/1.8V            | 504                          | CCGA-472 | 5.5M                      |

| ATMX150RHA_544 | 2.5V or 3.3V/1.8V            | 544                          | CQFP-352 | 6.5M                      |

| ATMX150RHA_544 | 2.5V or 3.3V/1.8V            | 544                          | CQFP-256 | 6.5M                      |

| ATMX150RHA_544 | 2.5V or 3.3V/1.8V            | 544                          | CLGA-625 | 6.5M                      |

| ATMX150RHA_544 | 2.5V or 3.3V/1.8V            | 544                          | CLGA-472 | 6.5M                      |

| ATMX150RHA_544 | 2.5V or 3.3V/1.8V            | 544                          | CCGA-625 | 6.5M                      |

| ATMX150RHA_544 | 2.5V or 3.3V/1.8V            | 544                          | CCGA-472 | 6.5M                      |

| ATMX150RHA_604 | 2.5V or 3.3V/1.8V            | 604                          | CQFP-352 | 7.5M                      |

| ATMX150RHA_604 | 2.5V or 3.3V/1.8V            | 604                          | CLGA-896 | 7.5M                      |

| ATMX150RHA_604 | 2.5V or 3.3V/1.8V            | 604                          | CLGA-625 | 7.5M                      |

| ATMX150RHA_604 | 2.5V or 3.3V/1.8V            | 604                          | CCGA-896 | 7.5M                      |

| ATMX150RHA_604 | 2.5V or 3.3V/1.8V            | 604                          | CCGA-625 | 7.5M                      |

| ATMX150RHA_644 | 2.5V or 3.3V/1.8V            | 644                          | CQFP-352 | 8.7M                      |

| Die            | Supply Voltage<br>I/O / core | Max<br>programmable<br>I/O's | Case     | Typical Routable<br>gates |

|----------------|------------------------------|------------------------------|----------|---------------------------|

| ATMX150RHA_644 | 2.5V or 3.3V/1.8V            | 644                          | CLGA-896 | 8.7M                      |

| ATMX150RHA_644 | 2.5V or 3.3V/1.8V            | 644                          | CLGA-625 | 8.7M                      |

| ATMX150RHA_644 | 2.5V or 3.3V/1.8V            | 644                          | CCGA-896 | 8.7M                      |

| ATMX150RHA_644 | 2.5V or 3.3V/1.8V            | 644                          | CCGA-625 | 8.7M                      |

| ATMX150RHA_704 | 2.5V or 3.3V/1.8V            | 704                          | CQFP-352 | 10.4M                     |

| ATMX150RHA_704 | 2.5V or 3.3V/1.8V            | 704                          | CLGA-896 | 10.4M                     |

| ATMX150RHA_704 | 2.5V or 3.3V/1.8V            | 704                          | CLGA-625 | 10.4M                     |

| ATMX150RHA_704 | 2.5V or 3.3V/1.8V            | 704                          | CCGA-896 | 10.4M                     |

| ATMX150RHA_704 | 2.5V or 3.3V/1.8V            | 704                          | CCGA-625 | 10.4M                     |

### 5.2.2.5 Technology Flow Definition

The Technology Flow covers the design, fabrication, assembly and testing of the ATMX150RHA standard cells ASIC family.

#### 1. Design

The design manual and the ASIC library data books cover the design in the Microchip Technology Nantes associated Design Centers (Nantes and Rousset-France, Milan-Italy, Garching-Germany and Winnersh-UK).

|                                                  |                 |

|--------------------------------------------------|-----------------|

| ATMX150RHA design manual                         | 2012_EC_054_ELE |

| ATMX150RHA TOS (Test Oriented Simulation) Manual | ATD-DE-GR-R0324 |

| ATMX150RHA supply & ESD buffer databook          | 2012_EC_055_ELE |

| ATMX150RHA buffer 3.3V databook                  | 2012_EC_051_ELE |

| ATMX150RHA buffer 2.5V databook                  | 2012_EC_052_ELE |

| ATMX150RHA Cells library databook                | 2012_EC_050_ELE |

| ATMX150RHA memory cells library databook         | 2012_EC_053_ELE |

| ATMX150RHA power grid verification flow          | 2014_EC_131-ELE |

All ASIC designs will be performed by customer at customer site, with Microchip supported tools (front end).

#### 2. Fabrication

The AT77K9RHA, processed in UMC Taiwan, is a 0.15  $\mu\text{m}$  CMOS, 5-metal with an optional 6th thick metal, Ti, TiN and AlCu process.

#### 3. Assembly

The assembly of ATMX150RHA devices is performed in MMT, Thailand, with the following capabilities:

- Die attach Cyanate Ester (JM7000)

- Wire bond Ultrasonic Wedge, 25 and 32  $\mu\text{m}$  Al

- Lid sealing Brazed with Au/Sn alloy or seam welded

- Leads/pads Gold plated (CQFP and CLGA)

The assembly of columns on CLGA is performed in SERMA HCM, La Rochelle, with the following capabilities:

- Columns 85Pb15Sn with Tinned Copper ribbon, 0.38 mm diameter

#### 4. Control & Test

The control and test of ATMX150RHA devices is performed in Microchip Technology Nantes.

It includes Lot Acceptance, Test Flows and Test Procedures, Qualification Test and Reliability Monitoring, Screening and associated electrical tests and inspections.

## 5. TCVs and SEC

### **002NY TEST VEHICLE**

The 002NY is a buffer test vehicle representative of the range of buffers available for performance testing in the CQFP-352 package. It contains standard IO33 buffers, specific IO33 buffers (LVDS, PCI), a PLL, a set of ring oscillators made of different library cells and a set of interconnect lines.

### **002PF TEST VEHICLE**

The 002PF is a test vehicle representative of the IP blocks available for performance testing in the CQFP-256 package. It contains the REG200RHA, the OSCR10MRHA, the MUX8RHA, the BG1V2RHA and the PLL400MRHA.

### **002OP TEST VEHICLE – TECHNOLOGY SEC**

The 002OP SEC is developed for radiation testing, process stability, reliability monitoring and performance characterization, it is assembled in the CQFP-352 package. It contains a set of memory blocks (compiled memories with and without EDACs), shift registers chains, high speed LVDS, PCI buffers and a PLL. It uses the thick-metal layer option.

### **002MS TEST VEHICLE – TECHNOLOGY SEC**

The 002MS has the same characteristics than the 002OP, without the thick-metal layer option. 002MS will be embarked on MPW (Multi-Project Wafer) instead of 002OP when MPW ASIC's do not need thick metal layer. When so, 002MS shall be used for reliability quarterly monitoring.

## 6. Radiation Characteristics

The AT77K9RHA technology has been developed to fulfil the following characteristics:

- Total dose capability over 100 kRads (Si).

- No Single Event Latchup to a LET threshold of 67.7 MeV.cm<sup>2</sup>/mg, and up to 78.2 MeV.cm<sup>2</sup>/mg, 30° tilted at high temperature.

- Availability of SEU hardened cells.

### 5.2.2.6 *Manufacturing sites*

#### **DESIGN:**

Microchip Technology Nantes, BP70602, 44306 Nantes Cedex 3, France

#### **WAFER FABRICATION:**

UMC Fab 8C, Hsin-Chu, Taiwan

#### **DIE ASSEMBLY:**

MMT, Microchip Technology (Thailand) Co., Ltd. 17/2 Moo 18 Suwintawong Road, Saladang, Bangnumpiew Chachoengsao, Thailand 24000

#### **CCGA COLUMN ASSEMBLY:**

SERMA Microelectronics, 34 Av. Joliot Curie, 17185 Perigny Cedex, France

#### **CONTROL AND TEST:**

Microchip Technology Nantes, BP70602, 44306 Nantes Cedex 3, France

5.2.3 ST Microelectronics, France: ASIC platform C65Space

5.2.3.1 *Contact Information*

| Address                                                                     | ESCC Chief Inspector                                                                       |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| STMicroelectronics (Tours) SAS<br>3 rue de Suisse<br>35200 Rennes<br>France | Ms Emmanuelle Guerinel<br>Tel. +33 2 99 26 4800<br>emmanuelle.guerinel@st.com              |

|                                                                             | ASICs QA Project Manager                                                                   |

|                                                                             | M. Jean-Noël LETRILLARD<br>Tel. +33 2 99 26 4800 ext : 4937<br>jean-noel.letrillard@st.com |

5.2.3.2 *Qualification*

| Current Qualification Certificate No. | In QML since: | Type Designation                                                                                             |

|---------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------|

| 381A                                  | Aug 2022      | Integrated Circuits, Silicon, Monolithic, CMOS Radiation Hardened 65nm ASIC Platform, based on type C65Space |

**Applicable documents:**

ESCC Generic Specification No. [9000](#); ESCC Detail Specification No. [9202/086](#)

STMicroelectronics Process Identification Documents:

- 8097046: GENERIC PID Ref. ST.01.2008

- DM00508779: PID FOR ASICs C65S WB and FC

- DM00508782: PID ASICs C65Space WB and FC Die Layout

5.2.3.3 *List of Qualified Components*

| Component Number | Detail Specification     | Generic part number | Circuit function                             | FPGA Matrix | Package  |

|------------------|--------------------------|---------------------|----------------------------------------------|-------------|----------|

| 930401001A       | <a href="#">9304/010</a> | NX1H35AS-CQ352      | 3M System gate field programmable gate array | NX1H35AS    | CQFP-352 |

#### 5.2.3.4 Technology Flow Abstract

### **GENERAL FEATURES**

The CMOS 65nm SPACE is a silicon technology node, 8 metal layers. It provides a logic capacity with additional DSPs, a 400 Mbs SpaceWire physical interface and also a DDR 2/3 physical interface. Benefiting from an advanced underlying technology, the NG-Medium provides high performances in terms of frequency and consumption. It is also reprogrammable without any limits.

- Power supply:

- o Core: 1.2V±10%.

- o IOS: 1.5V±10% or 1.8V±10% or 2.5V±10% or 3.3V±10%.

- Performance:

- o 250MHz Logic.

- o 333MHz DSP.

- o 800Mbps I/O.

- Temperature :

- o -55°C to +125°C.

### **BASIC INFORMATION**

#### **Main features**

- 65 nm ST-SPACE process technology.

- 4-Input Look-up tables.

- Lut expander to support up to 16 bits boolean functions.

- High performance carry chains.

- Advanced interconnect network to support random logic and coarse grain block functions.

- DSP Blocks for complex arithmetic operations.

- User memories with variable width and depth.

- Configuration modes: JTAG, Parallel 8 bits, Parallel 16 bits, Serial dump bus, Space Wire

- Integrated Space Wire interface available for user applications.

- Dedicated lowskew distribution network for clock, reset and load enable signals.

- On-chip thermal monitoring capability.

#### **Input/Output features**

- Multiple I/O powering support from 1.5V to 3.3V

- Cold sparing support.

- Programmable output drive to support multiple industry standards.

- Embedded logic to support DDR2 and DDR3.

- 800 Mbps I/O support.

- LVDS compatible mode.

- All pins support 2000V of ESD-HBM.

- Embedded logic to support Space Wire Data Strobe encoding.

- Programmable delay lines on all pins.

- Programmable resistive termination.

## COMPONENT TYPES

Device Types as per ESCC Detail Specification [9202/086](#) and individual custom ESCC ASIC Sheets:

| Part number     | Part Type | Package  | Temperature range |

|-----------------|-----------|----------|-------------------|

| 920208601A##### | C65SPACE  | CQFP-352 | -55°C to +125°C   |

### 5.2.3.5 *Technology Flow Definition*

The Technology Flow Definition domain covers the design, fabrication, assembly and testing of packaged products using ST C65Space silicon technology node and ST assembly line technology capabilities in CQFP352 package family.

## 7. Design

The following features are based on ST ESCC evaluated libraries from C65SPACE Design Environment:

- DSPs,

- DPRAMs & SPREGs memories,

- Input / Output in I/O Banks (except for the pas itself, which keeps original pad structure but receives Custom Design Add On featuring)

- Bitstream manager,

- PLLs (1201),

- Waveform generators,

- SapceWire Interface (including LVDS pads).

Other features designed by NanoXplore are full in compliant with ST C65Space design rules.

The NG-MEDIUM FPGA is based on NanoXplore patented interconnect architecture offering the highest logic density as well as high efficiency mapping. Application mapping is supported by NanoXplore tools based on proprietary algorithms tailored to the interconnect topology.

The device is composed of a central fabric embedding the programmable logic, RAM and DSP blocks, and peripheral I/O buffers. The fabric is covered with a grid of high level functional blocks interleaved with interconnect structures providing routing resources to realize the connections within the fabric and to the peripheral I/O buffers. The programmable logic resources are arranged in a hierarchical structure called a TILE with a specific local interconnect network. The I/O buffers are arranged into multiple banks. Each bank has its own I/O buffer supply voltage.

## 8. Fabrication

The wafer manufacturing is performed in ST Crolles 300mm fab using the new C65SPACE technology silicon node developed in ST Crolles 300mm and successfully qualified by ST in September 2014.

The main characteristics of the silicon die are described below:

Mask Levels: 41.

Masks Levels of Metallization: 8 (7 Layers in Cu + 1 Layer Ta/TaN/AlCu).

Die size: 15.3\*10.96 mm<sup>2</sup>.

Die Pad Pitch: 70µm min.

Die Pad Opening: 44\*108 µm<sup>2</sup>.

Die Pads Numbers: 374 non-staggered.

Die Finish Front Side (passivation): PSG + Nitride.

Die Finish Back Side: Raw Silicon.

An additional step of OPM (Over Pad Metallization) deposition is performed at a third party subcontractor ChipBond (TW), under ST quality control.

OPM : TiW/Au (Au= 3.5µm±1µm)

OPM Pad size : 54\*165 µm<sup>2</sup>

## 9. Assembly

### Process

The assembly process of the C65 Space devices is set-up in the historical ST Space certified plant in Rennes, France using the main following process capabilities:

Die Attach Medium: "Cyanate Ester" JM7000

Wire Bonding technology: Ultrasonic Gold Ball-Bonding.

Wire: 0.8 mils (20µm) Gold 4N

Bonding Decks & Bonding wire number:

|                       |         |

|-----------------------|---------|

|                       | CQFP352 |

| Bonding decks N#      | 2       |

| Bonding wires N#      | 448     |

| Bond Wires on Deck #1 | 223     |

| Bond Wires on Deck #2 | 225     |

### Package

Ceramic Quad Flat Package with 352 leads (CQFP352) with Ceramic Tie Bar

Dimensions: 75\*75\*3.51 mm3.

Cavity Size: 17\*12.66 mm<sup>2</sup>

Cavity Volume: 320 mm3.

Lid Material: Kovar with Plating Layers (Ni/Au)

Lid Size: 23.62\*19.30 mm<sup>2</sup>

Lead finishing: Au Plated

## 10. Control and Test

The control & test of C65 Space devices are performed in both ST Grenoble plant, France for electrical testing and accelerated ageing (reliability screening) and Rennes, France for all other space related tests or at subcontracted third parties under Rennes Quality monitoring and control.

All these space related manufacturing operations are performed under the supervision and control of the ST ESCC Chief Inspector, located in our basic space plant, Rennes.

## 11. TCVs and SEC

TCV program has been carried out to address intrinsic failure mechanisms of the C65Space technology. NG-Medium encapsulated in CQFP352 are used as SECs to conduct all the requested evaluation and qualification tests.

## 12. Radiation Characteristics

The ST C65SPACE technology has been developed to fulfil the following characteristics:

- SEL immune up to LET > 60MeV.cm<sup>2</sup>/mg.

- TID tolerance = 300 krad(Si).

### 5.2.3.6 *Manufacturing sites*

#### **DESIGN:**

NanoXplore

1 avenue de la Cristallerie, 92310 Sèvres, France

#### **WAFER FABRICATION:**

ST Crolles 300 - 850 rue Jean Monnet 38926 Crolles, France

#### **ASSEMBLY:**

ST Rennes – 3 rue de Suisse 35200 Rennes, France. Basic Plant

#### **CONTROL AND TEST:**

ST Grenoble - 12 rue Jules Horowitz, B.P. 217 38019 Grenoble, France

ST Rennes – 3 rue de Suisse 35200 Rennes, France. Basic Plant

5.2.4 ST Microelectronics, France: ASIC platform FDSOI 28nm

5.2.4.1 *Contact Information*

| Address                                                                     | ESCC Chief Inspector                                                                                                   |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| STMicroelectronics (Tours) SAS<br>3 rue de Suisse<br>35200 Rennes<br>France | Ms Emmanuelle Guerinel<br>Tel. +33 2 99 26 4800<br>emmanuelle.guerinel@st.com                                          |

|                                                                             | ASICs QA Project Manager<br>M. Jean-Noël LETRILLARD<br>Tel. +33 2 99 26 4800 ext : 4937<br>jean-noel.letrillard@st.com |

5.2.4.2 *Qualification*

| Current Qualification Certificate No. | In QML since: | Type Designation                                                   |

|---------------------------------------|---------------|--------------------------------------------------------------------|

| 394                                   | Nov 2025      | Integrated Circuits, Silicon, Monolithic, FDSOI 28nm ASIC Platform |

**Applicable documents:**

ESCC Generic Specification No. [9000](#); ESCC Detail Specification No. [9304/012](#)

STMicroelectronics Process Identification Documents:

- 8097046: GENERIC PID Ref. ST.01.2008

- DM00978658: PID for ASICs C28FDSOI Space FC

- DM00978698: PID for ASICs C28FDSOI Space FC Die Layout

5.2.4.3 *List of Qualified Components*

| Component Number | Detail Specification     | Generic part number | Circuit function                  | FPGA Matrix | Package      |

|------------------|--------------------------|---------------------|-----------------------------------|-------------|--------------|

| 930401201P       | <a href="#">9304/012</a> | NX2H540TSC-FF1760   | SoC field programmable gate array | NX2H540ATSC | FCTEBGA-1760 |

#### 5.2.4.1 Technology Flow Abstract

##### **GENERAL FEATURES**

The NG-ULTRA NX2H540TSC is a Radiation Hardened By Design (RHBD) SoC FPGA in 28nm with quadcore ARM R52 running at 600MHz each, based on ST CMOS28FDSOI SPACE GEO Technology Platform from STMicroelectronics. It has a logic capacity of 537KLUT. The hardening techniques used in the NG-ULTRA, alongside the FD-SOI technology, provide radiation hardening performance.

NG-ULTRA NX2H540TSC contains two parts: A programmable logic matrix and Microprocessor subsystem.

First part is composed of a central fabric embedding the programmable logic, RAM and DP blocks. The fabric takes benefit from the highspeed connectivity such as High-Speed Serial Links (HSSLs) and DDR2/3 interfaces.

It is covered with a grid of high-level functional blocks interleaved with interconnect structures providing routing resources to realize the connections within the fabric and to the peripheral I/Os. The programmable logic resources are arranged in a hierarchical structure called a TILE with a specific local interconnect network. I/Os are arranged into multiple banks. Each bank has its own I/O buffer supply voltage.

Second part is the microprocessor subsystem which is based on a complete System on Chip.

| Power Supply                                                        | Description                      | Maximum ratings (V)                           |

|---------------------------------------------------------------------|----------------------------------|-----------------------------------------------|

| Supply Voltages                                                     | VDDCORE<br>VDD_AUX<br>VDD_SWITCH | 1 $\pm$ 5%<br>1.8 $\pm$ 10%<br>1.8 $\pm$ 10%  |

| Input/Output Voltage Range<br>Complex I/O Bank:<br>Simple I/O Bank: | VDDIO                            | 1.2; 1.5; 1.8;<br>1.8; 2.5; 3.3;<br>$\pm$ 10% |

Table1: maximum ratings of VDDIO

##### **BASIC INFORMATION**

###### **Main features**

- Technology Node: ST CMOS28FDSOI SPACE GEO technology

- Processing System: Quad core ARM Cortex R52 based System-on-Chip (SoC)

- Programmable Logic:

- 537KLUT (4-input Look-Up Tables)

- High-performance carry chains

- Advanced interconnect network enabling both logic and coarse-grain block functions

- Arithmetic Capabilities: Dedicated DSP blocks for complex computations

- User-configurable memories with variable width and depth

- Configuration interfaces:

- Master Serial SPI (Single, Sequential, Triple Modular Redundancy - TMR)

- SpaceWire Protocol Support

- Debug interfaces:

- JTAG

- 16-bit Parallel UART

- Dedicated lowskew distribution network for clock, reset and load signals

- On-chip thermal monitoring for system reliability

### **Input/Output features**

- Multiple I/O voltage supported from 1.2V to 3.3V

- Integrated Cold Splicing Capability

- Programmable output drive strength to support various industry standards.

- High-Speed Interfaces:

- Embedded logic to support SpaceWire interface (data strobe encoding)

- Embedded logic to support DDR2, DDR3 for the fabric + DDR4 via the SoC memory

- Up to 1.6 Gbps I/O speed for SSTL, HSTL and POD standards

- LVDS compatible mode

- All I/O pins support 2000V ESD-HBM protection

- Programmable delay lines on complex I/O pins

- Programmable resistive termination on complex I/O pins

- Optional register single rate for direct I/O pins and single or double rate for complex I/O pins

### **COMPONENT TYPES**

Device Types as per ESCC Detail Specification [9304/012](#) and individual custom ESCC ASIC Sheets:

| Part number | Part Type                            | Package                                                                        | Temperature range |

|-------------|--------------------------------------|--------------------------------------------------------------------------------|-------------------|

| 930401201P  | NX2H540ATS<br>C-FF1760<br>(NG-ULTRA) | Fine pitch Flip-Chip<br>Organic Ball Grid<br>Array with 1760 balls<br>(FF1760) | -40°C to +125°C   |

#### *5.2.4.2 Technology Flow Definition*

##### **1. Design**

NG-ULTRA is a SoC-FPGA divided into 2 parts:

- PS: It is composed of 4 ARM cores with multiple peripherals. The PS is responsible for booting, executing the ASW and transferring the bitstream to the PL part.

- PL: It is composed of a central fabric with analog elements on the ring. The PL is managed by a bitstream manager responsible for programming this matrix.

The NG-ULTRA PS features a quad-core ARM Cortex-R52, optimized for real-time and safety-critical systems. This architecture supports hardware-enforced isolation and fault tolerant execution, enabling secure partitioning of tasks and robust system behaviour under adverse conditions.

The following IPs are based on ST ESCC evaluated libraries from ST CMOS28FDSOI SPACE GEO Design Environment:

- Clock subsystem

- Reset subsystem

- Watchdog

- Bootrom

- Flash Controller

- AXI Controller

- Error Management

- QoS Monitor

- SoC Monitoring

- DMA

- eRAM

- RS DDR Controller

- Space Wire Boot AHB

- Network Interconnect

- UART

- DSP

- Register file

- Bitstream Manager

- iobank\_complex

- iobank\_direct

- iobank\_hssi

- iobank\_clockgen

- iobank\_soc\_ddr.

ST CMOS28FDSOI SPACE GEO Standard libraries :

***analogmixed***

C28SOI\_AN\_VTSENS\_SPACE

C28SOI\_PLL\_PF\_5000MHZ\_SPACE

***fuse***

C28SOI\_FU\_SAFMEMHV\_SPACE

***digital standard cells***

C28SOI\_SC\_12/8\_CORE/CLK\_LL/LR

C28SOI\_SC\_8\_CORESPACE\_LL

***memory***

C28SOI\_MEM\_ROM\_SPACE

C28SOI\_MEM\_SRAM\_DPHD\_SPACE

C28SOI\_MEM\_SRAM\_DPREG\_SPACE

C28SOI\_MEM\_SRAM\_SPHD\_SPACE

C28SOI\_MEM\_SRAM\_SPREG\_SPACE

***io***

C28SOI\_IO\_SPACE

## 2. Fabrication

The wafer manufacturing is performed in ST Crolles 300mm fab using the ST CMOS28FDSOI SPACE GEO technology silicon node developed in ST Crolles 300mm and successfully qualified by ST in May 2019.

The main characteristics of the silicon die are described below:

Mask Levels: 42.

Masks Levels of Metallization: 11 (10 Layers in Cu + 1 Layer Ta/TaN/AlCu).

Die size: 21.888\*20.348 mm2.

Die Pad Pitch: 180µm min.

Die Pad Opening: 87  $\mu\text{m}$ .

Die Pads Numbers: 11236 non-staggered.

Die Finish Front Side (passivation): PSG + Nitride + PIx

Die Finish Back Side: Raw Silicon.

### 3. Assembly

#### Process

The assembly process of the ST CMOS28FDSOI SPACE GEO devices is set-up in the historical ST Space certified plant in Rennes, France using the main following process capabilities:

Substrate : FCTEBGA 45sq, 1760 land pads, SOP  $\mu$ Balls on FC Pads + OSP on bottom side

Flip chip soldering (lead free solder bump): flux dipping

SMD : Capacitor 0.1 $\mu\text{F}$ , 0603, 25v +/-10%, Pure Tin finishing, JAXA qualified

Underfill : epoxy liquid

Thermal Interface Material : thermal grease

Lid material : Copper Alloy, nickel finishing

Lid size : 44mm \* 44mm

Lid attach : glue

Ball material : SnPb 63/37

Ball size : 0.64mm

### 4. Control and Test

The control & test of ST CMOS28FDSOI SPACE GEO devices are performed in both ST Grenoble plant, for electrical testing and accelerated ageing (reliability screening) and Rennes, for all other space related tests or at subcontracted third parties under Rennes Quality monitoring and control.

All these space related manufacturing operations are performed under the supervision and control of the ST ESCC Chief Inspector, located in ST basic space plant, Rennes.

### 5. TCVs and SEC

NG-ULTRA packaged in organic non hermetic FCTEBGA 45\*45 is used as SEC to conduct all the requested evaluation and qualification tests.

### 6. Radiation Characteristics

Radiation Tolerance:

- Radiation-hardened design applied to configuration memories and registers for enhanced resilience

- Single Event Upset (SEU) immunity validated up to LET > 60 MeV.cm<sup>2</sup>/mg for configuration memory, DPRAM user memory and programmable logic registers.

- Total Ionizing Dose (TID) tolerance up to 50Krad (Si), ensuring long-term reliability in harsh environments

- Embedded Error Detection and Correction (EDAC) mechanisms safeguard user memory integrity

- Critical logic blocks are triplicated to enhance fault tolerance and reliability

#### 5.2.4.3 *Manufacturing sites*

##### **DESIGN:**

NG-ULTRA

NanoXplore

1 avenue de la Cristallerie, 92310 Sèvres, France

##### **WAFER FABRICATION:**

ST Crolles 300 - 850 rue Jean Monnet 38926 Crolles, France

##### **WAFER LOT BUMPING**

AMKOR Korea - 150, Songdomirae-ro, Yeonsu-gu, Incheon 21991, Korea

##### **WAFERLOT ELECTRICAL TESTING**

ST GRENOBLE - 12 RUE JULES HOROWITZ, B.P. 217 38019 GRENOBLE, FRANCE

##### **ASSEMBLY:**

ST Rennes – 3 rue de Suisse 35200 Rennes, France. Basic Plant

##### **CONTROL AND TEST:**

ST GRENOBLE - 12 RUE JULES HOROWITZ, B.P. 217 38019 GRENOBLE, FRANCE

ST RENNES – 3 RUE DE SUISSE 35200 RENNES, FRANCE. BASIC PLANT

## 5.2.5 United Monolithic Semiconductors, France : GaN HEMT

### 5.2.5.1 *Contact Information*

| Address                                                                                                                               | ESCC Chief Inspector                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| United Monolithic Semiconductors<br>Batiment Charmille<br>Mosaic parc Courtaboeuf<br>10 avenue du Quebec<br>91140 Villebon sur Yvette | Mr B. LAMBERT<br>+33 6 45 74 51 75<br>+33 1 69 86 32 88<br><a href="mailto:Benoit.Lambert@ums-rf.com">Benoit.Lambert@ums-rf.com</a> |

### 5.2.5.2 *Qualification*

| Current Qualification<br>Certificate No. | In QML since: | Type Designation                                                                                  |

|------------------------------------------|---------------|---------------------------------------------------------------------------------------------------|

| 388                                      | Mar 2024      | Transistors, Microwave, GaN HEMT Unmatched in Metal Ceramic<br>Package CHKxxxx-SYx Product Family |

### 5.2.5.3 *List of Qualified Components*

| Variant<br>number | Detail<br>Specification | Generic part<br>number | Component type | Package                        |

|-------------------|-------------------------|------------------------|----------------|--------------------------------|

| 01                | 5614/009                | CHK8101-SYC            | 15W @ 1.7GHz   | Ceramic-Metal, Flanged, Type C |

| 02                | 5614/009                | CHK8201-SYA            | 50W @ 1.7GHz   | Ceramic-Metal, Flanged, Type A |

| 03                | 5614/009                | CHKA012bSYA            | 130W @ 1.7GHz  | Ceramic-Metal, Flanged, Type A |

### 5.2.5.4 *Technology Flow Abstract*

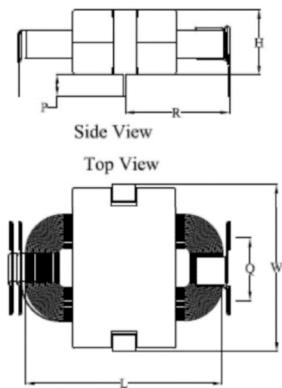

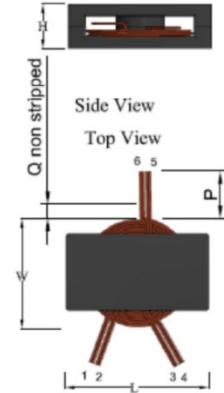

CHKxxxx-SYx Product Family is based on the UMS GH50-20 GaN power bar technology. Power bars are assembled using AuSn eutectic soldering in a highly dissipated ceramic-metal Flanged packaged. To assure RF stability of each component type, an RF absorber is used in the package cavity. All manufacturing and test production is performed in accordance to the ESCC/5010.

| <b>CAPABILITY APPROVAL DOMAIN</b>                              |                                                                                                                                                                          |

|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>RIC1 (Product: CHK8101-SYC) RIC3 (Product: CHKA012bSYA)</b> |                                                                                                                                                                          |

| <b>GaN DIE PROCESS</b>                                         |                                                                                                                                                                          |

| Die overview                                                   |       |

| Manufacturer                                                   | UMS – Ulm – Germany                                                                                                                                                      |

| Power bar dies technology                                      | UMS 4GH50-20                                                                                                                                                             |

| Gate pitches                                                   | 70µm                                                                                                                                                                     |

| Unitary gate finger width                                      | 250µm & 400µm                                                                                                                                                            |

| Finger gates per block                                         | 8                                                                                                                                                                        |

| Number of blocks                                               | 2 , 4, 8                                                                                                                                                                 |

| Max operating Freq. (GHz)                                      | 6 GHz                                                                                                                                                                    |

| <b>PACKAGE TECHNOLOGY</b>                                      |                                                                                                                                                                          |

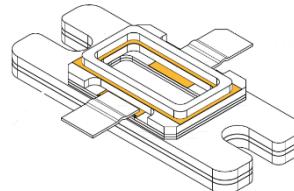

| <u>Package overview</u><br><u>(without Lid)</u>                |   |

| Package manufacturer                                           | Kyocera – Gamo – Japan                                                                                                                                                   |

| UMS Package reference                                          | SYC SYA                                                                                                                                                                  |

| UMS SAP Material N°                                            | 47003170                                                                                                                                                                 |

| Sealing                                                        | Seam-welding process                                                                                                                                                     |

|                                         |              |                       |

|-----------------------------------------|--------------|-----------------------|

| Lead                                    | 2            | 4                     |

| Base plate length (mm)                  | 17.5         | 20                    |

| Base plate width (mm)                   | 6.7          |                       |

| <u>Lid for Package:</u><br>Manufacturer | Hi-REL Group |                       |

| UMS Drawing Document N°                 | 61504640     | 61503116 last version |

| <u>RF Absorber :</u><br>Manufacturer    | DEMGY        |                       |

| UMS Material N°                         | 47003186     | 47003186              |

#### ASSEMBLY TECHNOLOGY

|                           |                                                                                                                                                                                                                                                                         |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Assembly subcontractor    | RHe Microsystems GmbH – Radeberg – Germany                                                                                                                                                                                                                              |

| Preform characteristics   | Material: Eutectic Au80Sn20 (Liquidis:278°C),                                                                                                                                                                                                                           |

| Sealing process           | Hermetical seam sealed                                                                                                                                                                                                                                                  |

| Assembly screening (100%) | Stabilization bake - 24h @ 150°C / MIL-STD-750 method 1032<br>Temp. Cycling - 20 cycles -55/+150°C / MIL-STD-750 method 1051<br>PIND test - MIL-STD-750 method 2052<br>X-ray - Wire bonding inspection / MIL-STD-883 2009.12<br>Leak test - MIL-STD-883-1014.15 Cond A2 |

#### ELECTRICAL SCREENING FLOW

|                                                 |                                                                                                                                                                                                     |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manufacturer                                    | UMS – Villebon – France                                                                                                                                                                             |

| Burn In 1<br>Electrical Stabilization<br>(100%) | 10hrs - Tamb=+125°C; VD=+50V; VG=-7V<br>10hrs - Tj=200°C; VD=+50V; VG=cst (RIC1:ID=256mA / RIC3:ID=1.25A)                                                                                           |

| Burn-In 2<br>(100%)                             | 240hrs - Tj=200°C; VD=+50V; VG=cst (RIC1:ID=256mA / RIC3:ID=1.25A)<br>RF characterization / Acceptance criteria based on specification and on parameter drift (before/after burn-in) / Pulsed or CW |

| FINAL PRODUCT                                       |                                                                                    |

|-----------------------------------------------------|------------------------------------------------------------------------------------|

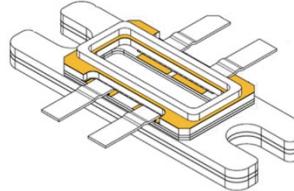

| Product overview                                    |  |