Pages 1 to 36

# INTEGRATED CIRCUITS, SILICON MONOLITHIC, CMOS 8K X

## 16 DUAL-PORT STATIC RANDOM ACCESS MEMORY WITH

## THREE STATE OUTPUTS

BASED ON TYPE 67025E

ESCC Detail Specification No. 9301/050

| Issue 1 | October 2007 |

|---------|--------------|

|         |              |

Document Custodian: European Space Agency - see https://escies.org

**ISSUE 1**

#### LEGAL DISCLAIMER AND COPYRIGHT

European Space Agency, Copyright © 2007. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

### DOCUMENTATION CHANGE NOTICE

(Refer to https://escies.org for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION |

|---------|--------------------|

|         |                    |

## TABLE OF CONTENTS

| <u>1.</u> | GENERAL                                                               | <u>5</u>  |

|-----------|-----------------------------------------------------------------------|-----------|

| 1.1       | Scope                                                                 | 5         |

| 1.2       | Applicable Documents                                                  | 5         |

| 1.3       | Terms, Definitions, Abbreviations, Symbols and Units                  | 5         |

| 1.4       | The ESCC Component Number and Component Type Variants                 | 5         |

| 1.4.1     | The ESCC Component Number                                             | 5         |

| 1.4.2     | Component Type Variants                                               | 5         |

| 1.5       | Maximum Ratings                                                       | 6         |

| 1.6       | Handling Precautions                                                  | 6         |

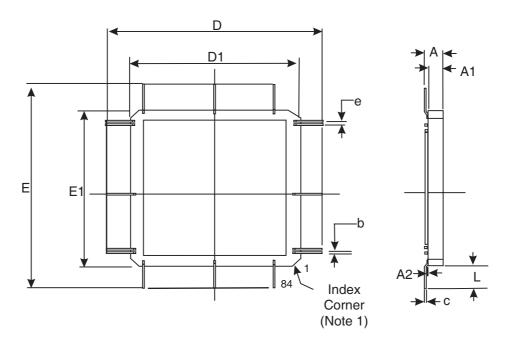

| 1.7       | Physical Dimensions and Terminal Identification                       | 7         |

| 1.7.1     | Multilayer Quad Flat Package (MQFP-F84) - 84 Lead                     | 7         |

| 1.8       | Functional Diagram                                                    | 8         |

| 1.9       | Pin Assignment                                                        | 8         |

| 1.10      | Truth Tables and Timing Diagrams                                      | 11        |

| 1.10.1    | Non Contention and Semaphore Read/Write Control                       | 11        |

| 1.10.2    | Arbitration Options                                                   | 12        |

| 1.10.3    | Interrupt Flag                                                        | 12        |

| 1.10.4    | Arbitration                                                           | 12        |

| 1.10.5    | Consolidated Notes for Truth Tables                                   | 13        |

| 1.10.6    | Timing Diagrams                                                       | 13        |

| 1.11      | Protection Networks                                                   | 24        |

| <u>2.</u> | REQUIREMENTS                                                          | <u>24</u> |

| 2.1       | General                                                               | 24        |

| 2.1.1     | Deviations from the Generic Specification                             | 24        |

| 2.1.1.1   | Deviations from Screening Tests-Chart F3                              | 24        |

| 2.2       | Marking                                                               | 24        |

| 2.3       | Electrical Measurements at Room, High and Low Temperatures            | 25        |

| 2.3.1     | Room Temperature Electrical Measurements                              | 25        |

| 2.3.2     | High and Low Temperatures Electrical Measurements                     | 33        |

| 2.4       | Parameter Drift Values                                                | 33        |

| 2.5       | Intermediate and End-Point Electrical Measurements                    | 34        |

| 2.6       | Power Burn-in Conditions                                              | 34        |

| 2.7       | Operating Life Conditions                                             | 35        |

| 2.8       | Total Dose Radiation Testing                                          | 35        |

| 2.8.1     | Bias Conditions and Total Dose Level for Total Dose Radiation Testing | 35        |

| 2.8.2     | Electrical Measurements for Total Dose Radiation Testing              | 36        |

#### 1. <u>GENERAL</u>

#### 1.1 <u>SCOPE</u>

This specification details the ratings, physical and electrical characteristics and test and inspection data for the component type variants and/or the range of components specified below. It supplements the requirements of, and shall be read in conjunction with, the ESCC Generic Specification listed under Applicable Documents.

#### 1.2 <u>APPLICABLE DOCUMENTS</u>

The following documents form part of this specification and shall be read in conjunction with it:

- (a) ESCC Generic Specification No. 9000

- (b) MIL-STD-883, Test Methods and Procedures for Microelectronics

#### 1.3 TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESCC Basic Specification No. 21300 shall apply.

#### 1.4 THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS

# 1.4.1 The ESCC Component Number The ESCC Component Number shall be constituted as follows:

Example: 930105001D

- Detail Specification Reference: 9301050

- Component Type Variant Number: 01 (as required)

- Total Dose Radiation Level Letter: D (as required)

#### 1.4.2 <u>Component Type Variants</u>

The component type variants applicable to this specification are as follows:

| Variant<br>Number | Based on Type | Access<br>Time<br>(ns) | Case         | Lead/Terminal<br>Material and Finish | Weight<br>max g | Total Dose<br>Radiation Level<br>Letter |

|-------------------|---------------|------------------------|--------------|--------------------------------------|-----------------|-----------------------------------------|

| 01                | 67025E-30     | 30                     | MQFP-<br>F84 | G2                                   | 5               | D [10kRAD(Si)]                          |

| 02                | 67025E-45     | 45                     | MQFP-<br>F84 | G2                                   | 5               | D [10kRAD(Si)]                          |

The lead/terminal material and finish shall be in accordance with the requirements of ESCC Basic Specification No. 23500.

The total dose radiation level letter shall be as defined in ESCC Basic Specification No. 22900. If an alternative radiation test level is specified in the Purchase Order the letter shall be changed accordingly.

#### 1.5 MAXIMUM RATINGS

The maximum ratings shall not be exceeded at any time during use or storage.

Maximum ratings shall only be exceeded during testing to the extent specified in this specification and when stipulated in Test Methods and Procedures of the ESCC Generic Specification.

| Characteristics                               | Symbols                            | Maximum Ratings              | Units | Remarks          |

|-----------------------------------------------|------------------------------------|------------------------------|-------|------------------|

| Supply Voltage                                | V <sub>DD</sub>                    | -0.5 to 7                    | V     | Note 1           |

| Input Voltage Range                           | V <sub>IN</sub>                    | -0.5 to V <sub>DD</sub> +0.3 | V     | Notes 1, 2       |

| Output Voltage Range                          | V <sub>OUT</sub>                   | -0.5 to V <sub>DD</sub> +0.3 | V     | Notes 1, 2       |

| Output Current Connected to $V_{DD}$ $V_{SS}$ | I <sub>O+</sub><br>I <sub>O-</sub> | 120<br>-60                   | mA    | Note 3           |

| Device Power Dissipation                      | PD                                 | 1.8                          | W     |                  |

| Operating Temperature Range                   | T <sub>op</sub>                    | -55 to +125                  | °C    | T <sub>amb</sub> |

| Storage Temperature Range                     | T <sub>stg</sub>                   | -65 to +150                  | °C    |                  |

| Soldering Temperature                         | T <sub>sol</sub>                   | +265                         | °C    | Note 4           |

| Junction Temperature                          | Тj                                 | +165                         | °C    | Note 5           |

| Thermal Resistance,<br>Junction to Case       | R <sub>th(j-c)</sub>               | 6                            | °C/W  |                  |

#### NOTES:

- 1. All voltages are with respect to V<sub>SS</sub>. Device is functional for  $4.5 \le V_{DD} \le 5.5V$ .

- 2. V<sub>DD</sub> +0.3V shall not exceed 7V.

- 3. The maximum output current of any single output.

- 4. Duration 10 seconds maximum at a distance of not less than 1.6mm from the device body and the same terminal shall not be resoldered until 3 minutes have elapsed.

- 5. Maximum junction temperature may be increased to +175°C during Power Burn-in and Operating Life.

#### 1.6 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are categorised as Class 1 per ESCC Basic Specification 23800 with a Minimum Critical Path Failure Voltage of 1000 Volts.

#### 1.7 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

#### 1.7.1 Multilayer Quad Flat Package (MQFP-F84) - 84 Lead

| Symbols | Dimensio   | Notes |         |

|---------|------------|-------|---------|

| Cymbola | Min        | Мах   | - Notes |

| A       | 2.05       | 2.89  | 2       |

| A1      | 1.82       | 2.67  |         |

| A2      | A2 - 0.356 |       | 2       |

| b       | 0.406      | 0.508 | 2, 4    |

| С       | 0.22       | 0.31  | 2       |

| D, E    | 44.16      | 45.86 |         |

| D1, E1  | 28.96      | 29.46 |         |

| е       | 1.27       | 2, 3  |         |

| L       | 7.6        | 8.2   | 2       |

- 1. Index mark: a notch or lead 1 identification mark shall be located adjacent to lead 1.

- 2. All terminals.

- 3. 80 places. The true position pin spacing is 1.27mm between centrelines. Each lead centreline shall be located within ±0.13mm of its true longitudinal position relative to the package centrelines.

- 4. 21 leads per side.

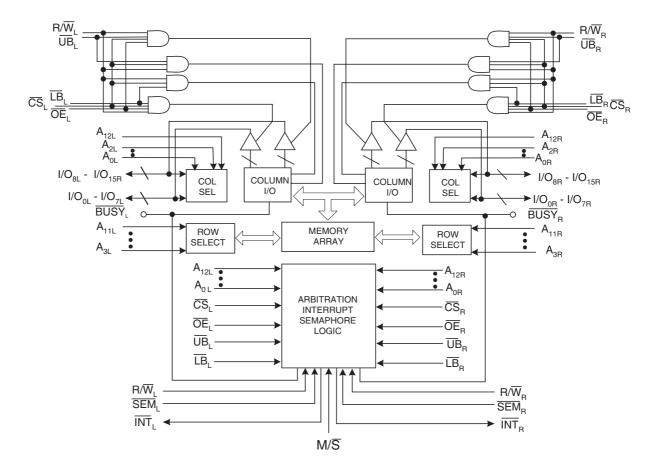

#### 1.8 FUNCTIONAL DIAGRAM

#### 1.9 <u>PIN ASSIGNMENT</u>

| Pin | Function                        |

|-----|---------------------------------|

| 1   | I/O8L Input/Output (Left Port)  |

| 2   | I/O9L Input/Output (Left Port)  |

| 3   | I/O10L Input/Output (Left Port) |

| 4   | I/O11L Input/Output (Left Port) |

| 5   | I/O12L Input/Output (Left Port) |

| 6   | I/O13L Input/Output (Left Port) |

| 7   | V <sub>SS</sub>                 |

| 8   | I/O14L Input/Output (Left Port) |

| 9   | I/O15L Input/Output (Left Port) |

| 10  | V <sub>DD</sub>                 |

| 11  | V <sub>SS</sub>                 |

| 12  | I/O0R Input/Output (Right Port) |

| Pin | Function                                   |

|-----|--------------------------------------------|

| 13  | I/O1R Input/Output (Right Port)            |

| 14  | I/O2R Input/Output (Right Port)            |

| 15  | V <sub>DD</sub>                            |

| 16  | I/O3R Input/Output (Right Port)            |

| 17  | I/O4R Input/Output (Right Port)            |

| 18  | I/O5R Input/Output (Right Port)            |

| 19  | I/O6R Input/Output (Right Port)            |

| 20  | I/O7R Input/Output (Right Port)            |

| 21  | I/O8R Input/Output (Right Port)            |

| 22  | I/O9R Input/Output (Right Port)            |

| 23  | I/O10R Input/Output (Right Port)           |

| 24  | I/O11R Input/Output (Right Port)           |

| 25  | I/O12R Input/Output (Right Port)           |

| 26  | I/O13R Input/Output (Right Port)           |

| 27  | I/O14R Input/Output (Right Port)           |

| 28  | V <sub>SS</sub>                            |

| 29  | I/O15R Input/Output (Right Port)           |

| 30  | OER Input (Output Enable, Right Port)      |

| 31  | R/WR Input (Read/Write Enable, Right Port) |

| 32  | V <sub>SS</sub>                            |

| 33  | SEMR Input (Semaphore Enable, Right Port)  |

| 34  | CSR Input (Chip Select, Right Port)        |

| 35  | UBR Input (Upper Byte Select, Right Port)  |

| 36  | LBR Input (Lower Byte Select, Right Port)  |

| 37  | A12R Input (Address, Right Port)           |

| 38  | A11R Input (Address, Right Port)           |

| 39  | A10R Input (Address, Right Port)           |

| 40  | A9R Input (Address, Right Port)            |

| 41  | A8R Input (Address, Right Port)            |

| 42  | A7R Input (Address, Right Port)            |

| 43  | A6R Input (Address, Right Port)            |

| 44  | A5R Input (Address, Right Port)            |

| 45  | A4R Input (Address, Right Port)            |

| 46  | A3R Input (Address, Right Port)            |

| 47  | A2R Input (Address, Right Port)            |

| 48  | A1R Input (Address, Right Port)            |

| Pin | Function                                                       |  |  |  |  |  |

|-----|----------------------------------------------------------------|--|--|--|--|--|

| 49  | A0R Input (Address, Right Port)                                |  |  |  |  |  |

| 50  | INTR Output (Interrupt Flag, Right Port)                       |  |  |  |  |  |

| 51  | BUSYR Input (Slave)/Output (Master) (Busy<br>Flag, Right Port) |  |  |  |  |  |

| 52  | M/S Input (Master or Slave Select)                             |  |  |  |  |  |

| 53  | V <sub>SS</sub>                                                |  |  |  |  |  |

| 54  | BUSYL Input (Slave)/Output (Master) (Busy<br>Flag, Left Port)  |  |  |  |  |  |

| 55  | INTL Output (Interrupt Flag, Left Port)                        |  |  |  |  |  |

| 56  | A0L Input (Address, Left Port)                                 |  |  |  |  |  |

| 57  | A1L Input (Address, Left Port)                                 |  |  |  |  |  |

| 58  | A2L Input (Address, Left Port)                                 |  |  |  |  |  |

| 59  | A3L Input (Address, Left Port)                                 |  |  |  |  |  |

| 60  | A4L Input (Address, Left Port)                                 |  |  |  |  |  |

| 61  | A5L Input (Address, Left Port)                                 |  |  |  |  |  |

| 62  | A6L Input (Address, Left Port)                                 |  |  |  |  |  |

| 63  | A7L Input (Address, Left Port)                                 |  |  |  |  |  |

| 64  | A8L Input (Address, Left Port)                                 |  |  |  |  |  |

| 65  | A9L Input (Address, Left Port)                                 |  |  |  |  |  |

| 66  | A10L Input (Address, Left Port)                                |  |  |  |  |  |

| 67  | A11L Input (Address, Left Port)                                |  |  |  |  |  |

| 68  | A12L Input (Address, Left Port)                                |  |  |  |  |  |

| 69  | LBL Input (Lower Byte Select, Left Port)                       |  |  |  |  |  |

| 70  | UBL Input (Upper Byte Select, Left Port)                       |  |  |  |  |  |

| 71  | CSL Input (Chip Select, Left Port)                             |  |  |  |  |  |

| 72  | SEML Input (Semaphore Enable, Left Port)                       |  |  |  |  |  |

| 73  | R/WL Input (Read/Write Enable, Left Port)                      |  |  |  |  |  |

| 74  | V <sub>DD</sub>                                                |  |  |  |  |  |

| 75  | OEL Input (Output Enable, Left Port)                           |  |  |  |  |  |

| 76  | I/O0L Input/Output (Left Port)                                 |  |  |  |  |  |

| 77  | I/O1L Input/Output (Left Port)                                 |  |  |  |  |  |

| 78  | V <sub>SS</sub>                                                |  |  |  |  |  |

| 79  | I/O2L Input/Output (Left Port)                                 |  |  |  |  |  |

| 80  | I/O3L Input/Output (Left Port)                                 |  |  |  |  |  |

| 81  | I/O4L Input/Output (Left Port)                                 |  |  |  |  |  |

| 82  | I/O5L Input/Output (Left Port)                                 |  |  |  |  |  |

**ISSUE 1**

| Pin | Function                       |

|-----|--------------------------------|

| 83  | I/O6L Input/Output (Left Port) |

| 84  | I/O7L Input/Output (Left Port) |

#### 1.10 TRUTH TABLES AND TIMING DIAGRAMS

Consolidated notes for the truth table and the instruction set follow the tables.

#### 1.10.1 Non Contention and Semaphore Read/Write Control

|    |          | Inp | outs |    |     | Out                 | puts                | Mode                                          |

|----|----------|-----|------|----|-----|---------------------|---------------------|-----------------------------------------------|

| CS | R/W      | ŌĒ  | UB   | LB | SEM | I/O8 - I/O15        | I/O0 - I/O7         | -                                             |

| Н  | Х        | Х   | Х    | Х  | Н   | Z                   | Z                   | Deselected: Power<br>Down (Note 2)            |

| X  | Х        | Х   | Н    | Н  | Н   | Z                   | Z                   | Both Bytes Deselected:<br>Power Down (Note 2) |

| L  | L        | Х   | L    | Н  | H   | DATA <sub>IN</sub>  | Z                   | Write to Upper Byte Only<br>(Note 2)          |

| L  | L        | Х   | H    | L  | H   | Z                   | DATA <sub>IN</sub>  | Write to Lower Byte Only<br>(Note 2)          |

| L  | L        | Х   | L    | L  | H   | DATA <sub>IN</sub>  | DATA <sub>IN</sub>  | Write to Both Bytes<br>(Note 2)               |

| L  | H        | L   | L    | Н  | H   | DATA <sub>OUT</sub> | Z                   | Read Upper Byte Only<br>(Note 2)              |

| L  | H        | L   | H    | L  | H   | Z                   | DATA <sub>OUT</sub> | Read Lower Byte Only<br>(Note 2)              |

| L  | H        | L   | L    | L  | H   | DATA <sub>OUT</sub> | DATA <sub>OUT</sub> | Read Both Bytes<br>(Note 2)                   |

| X  | Х        | Н   | Х    | Х  | Х   | Z                   | Z                   | Outputs Disabled<br>(Note 2)                  |

| Н  | Н        | L   | Х    | Х  | L   | DATA <sub>OUT</sub> | DATA <sub>OUT</sub> | Read Data in<br>Semaphore Flag                |

| X  | Н        | L   | Н    | Н  | L   | DATA <sub>OUT</sub> | DATA <sub>OUT</sub> | Read Data in<br>Semaphore Flag                |

| Н  | <b>↑</b> | Х   | Х    | Х  | L   | DATA <sub>IN</sub>  | DATA <sub>IN</sub>  | Write D <sub>IN0</sub> into<br>Semaphore Flag |

| X  | <b>↑</b> | Х   | Н    | Н  | L   | DATA <sub>IN</sub>  | DATA <sub>IN</sub>  | Write D <sub>IN0</sub> into<br>Semaphore Flag |

| L  | Х        | Х   | L    | Х  | L   | -                   | -                   | Not Allowed                                   |

| L  | Х        | Х   | Х    | L  | L   | -                   | -                   | Not Allowed                                   |

**ISSUE 1**

### 1.10.2 <u>Arbitration Options</u>

| Options               | Inputs |    |    |     | Outputs |        |        |

|-----------------------|--------|----|----|-----|---------|--------|--------|

|                       | CS     | ŪB | LB | M/S | SEM     | BUSY   | INT    |

| Busy Logic Master     | L      | Х  | L  | Н   | Н       | Output | -      |

|                       | L      | L  | Х  | Н   | Н       | Signal | -      |

| Busy Logic Slave      | L      | Х  | L  | L   | Н       | Input  | -      |

| Dusy Logic Slave      | L      | L  | Х  | L   | Н       | Signal | -      |

| Interrupt Logic       | L      | Х  | L  | Х   | Н       | -      | Output |

|                       | L      | L  | Х  | Х   | Н       | -      | Signal |

| Semaphore Logic (Note | Н      | Х  | Х  | Н   | L       | Н      | -      |

| 3)                    | Н      | Х  | Х  | L   | L       | Z      | -      |

### 1.10.3 Interrupt Flag

|      | I   | Left Port |               |       |      | I   | Right Po | Function      |       |                       |

|------|-----|-----------|---------------|-------|------|-----|----------|---------------|-------|-----------------------|

| R/WL | CSL | ŌĒL       | A0L -<br>A12L | INTL  | R/WR | CSR | ŌĒR      | A0R -<br>A12R | ĪNTR  | Note 4                |

| L    | L   | Х         | 1FFF          | Х     | Х    | Х   | Х        | Х             | L (5) | Set Right INTR Flag   |

| Х    | Х   | Х         | Х             | Х     | Х    | L   | L        | 1FFF          | H (6) | Reset Right INTR Flag |

| Х    | Х   | Х         | Х             | L (6) | L    | L   | Х        | 1FFE          | Х     | Set Left INTL Flag    |

| Х    | L   | L         | 1FFE          | H (5) | Х    | Х   | Х        | Х             | Х     | Reset Left INTL Flag  |

#### 1.10.4 <u>Arbitration</u>

| L                                           | eft Port         | Ri       | ght Port        | Flags<br>Note 7 |       | Function             |  |

|---------------------------------------------|------------------|----------|-----------------|-----------------|-------|----------------------|--|

| CSL                                         | A0L - A12L       | CSR      | A0R - A12R      | BUSYL           | BUSYR |                      |  |

| Н                                           | Х                | Н        | Х               | Н               | Н     | No Contention        |  |

| L                                           | Any              | Н        | Х               | Н               | Н     | No Contention        |  |

| Н                                           | Х                | L        | Any             | Н               | Н     | No Contention        |  |

| L                                           | ≠A0R - A12R      | L        | ≠A0L - A12L     | Н               | Н     | No Contention        |  |

| Address                                     | Arbitration With | CS Low B | efore Address I | Match           |       |                      |  |

| L                                           | LV5R             | L        | LV5R            | Н               | L     | L-Port Wins          |  |

| L                                           | RV5L             | L        | RV5L            | L               | Н     | R-Port Wins          |  |

| L                                           | Same             | L        | Same            | Н               | L     | Arbitration Resolved |  |

| L                                           | Same             | L        | Same            | L               | Н     | Arbitration Resolved |  |

| CS Arbitration With Address Match Before CS |                  |          |                 |                 |       |                      |  |

| LL5R                                        | = A0R - A12R     | LL5R     | = A0L - A12L    | Н               | L     | L-Port Wins          |  |

**ISSUE 1**

| L    | Left Port    |      | ght Port     | Fla<br>Not |       | Function             |

|------|--------------|------|--------------|------------|-------|----------------------|

| CSL  | A0L - A12L   | CSR  | A0R - A12R   | BUSYL      | BUSYR |                      |

| RL5L | = A0R - A12R | RL5L | = A0L - A12L | L          | Н     | R-Port Wins          |

| LW5R | = A0R - A12R | LW5R | = A0L - A12L | Н          | L     | Arbitration Resolved |

| LW5R | = A0R - A12R | LW5R | = A0L - A12L | L          | Н     | Arbitration Resolved |

#### 1.10.5 Consolidated Notes for Truth Tables

- Logic Level Definitions: L = Low Level, H = High Level, X = Irrelevant, Z = High Impedance, ↑ = Rising edge of signal, NC = No Change, LV5R = Left Address Valid ≥ 5ns before Right Address, RV5L = Right Address Valid ≥ 5ns before Left Address, Same = Left and Right Addresses match within 5ns of each other, LL5R = CSL = Low ≥5ns before CSR, RL5L = CSR = Low ≥5ns before CSL, LW5R = CSL and CSR = Low within 5ns of each other.

- 2. A0L A12L  $\neq$  A0R A12R.

- 3. Input Signals are for Semaphore Flags set and test (Write and Read) operations.

- 4. Assumes  $\overline{\text{BUSYL}} = \overline{\text{BUSYR}} = \text{H}$ .

- 5. If  $\overline{\text{BUSYL}} = L$ , then NC.

- 6. If  $\overline{\text{BUSY}}R = L$ , then NC.

- 7.  $\overline{INTL}$ ,  $\overline{INTR}$  flags = X.

#### 1.10.6 <u>Timing Diagrams</u>

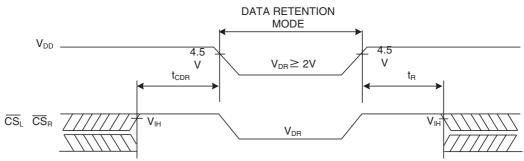

#### Data Retention (Notes 1, 2, 3)

- 1. Chip select ( $\overline{CSL}$ ,  $\overline{CSR}$ ) must be held high during data retention within V<sub>DD</sub> to V<sub>DD</sub>-0.2V.

- 2.  $\overline{\text{CSL}}$ ,  $\overline{\text{CSR}}$  must be kept between V<sub>DD</sub> 0.2V and 70% of V<sub>DD</sub> during the power up and power down transitions.

- 3. The RAM shall begin operation >  $t_R$  after  $V_{DD}$  reaches the minimum operating voltage (4.5 Volts).

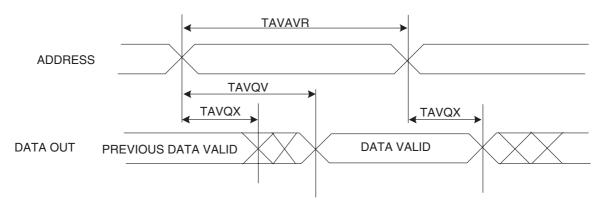

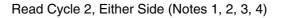

#### Read Cycle 1, Either Side (Notes 1, 2, 3)

#### NOTES:

- 1.  $R/\overline{W}$  is high for read cycles.

- 2. Device is continuously enabled:  $\overline{CS} = V_{IL}$ ,  $\overline{UB}$  or  $\overline{LB} = V_{IL}$ . This waveform cannot be used for semaphore reads.

3.  $\overline{OE} = V_{IL}$ .

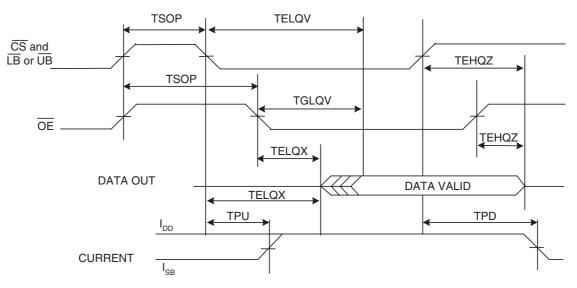

- 1.  $R/\overline{W}$  is high for read cycles.

- 2. Addresses valid prior to or coincident with  $\overline{CS}$  transition low.

- 3. To access RAM,  $\overline{CS} = V_{IL}$ ,  $\overline{UB}$  or  $\overline{LB} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . To access semaphore,  $\overline{CS} = V_{IH}$ ,  $\overline{SEM} = V_{IL}$ . Refer to Non Contention and Semaphore Read/Write Control table.

- 4.  $\overline{OE} = V_{IL}$ .

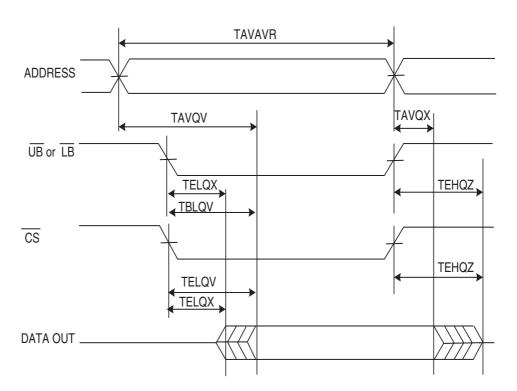

Read Cycle 3, Either Side (Notes 1, 2, 3, 4)

- $R/\overline{W}$  is high for read cycles. 1.

- 2.

- Addresses valid prior to or coincident with  $\overline{CS}$  transition low. To access RAM,  $\overline{CS} = V_{IL}$ ,  $\overline{UB}$  or  $\overline{LB} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . To access semaphore,  $\overline{CS} = V_{IH}$ ,  $\overline{SEM} = V_{IL}$ . Refer to Non Contention and Semaphore Read/Write Control table. 3.

- 4.  $\overline{OE} = V_{IL}$ .

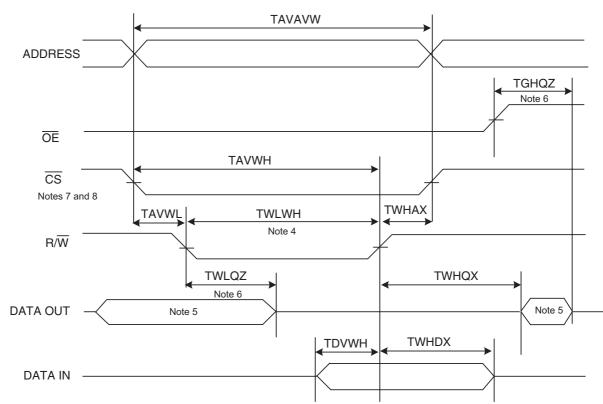

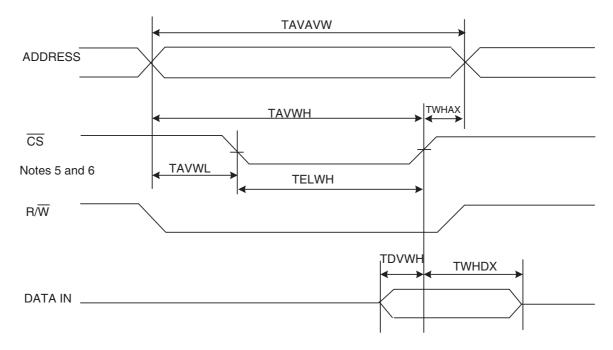

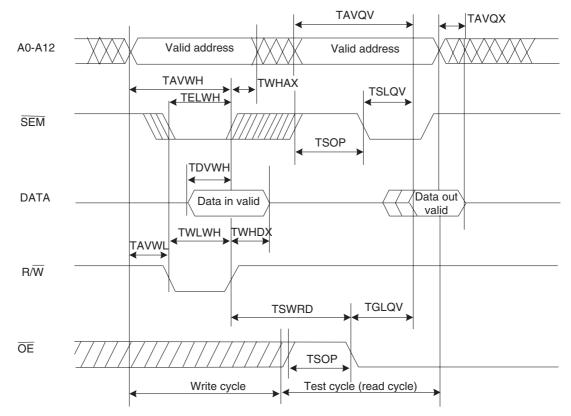

#### Write Cycle 1 (R/W Controlled) (Notes 1, 2, 3, 4)

- R/W must be high during all address transitions. 1.

- A write occurs during the overlap (TWLWH) of a low  $\overline{\text{CS}}$  or  $\overline{\text{SEM}}$  and a low  $R/\overline{W}$ . 2.

- TWHAX is measured from the earlier of  $\overline{CS}$  or  $R/\overline{W}$  (or  $\overline{SEM}$  or  $R/\overline{W}$ ) going high to the end of write 3. cvcle.

- 4. If OE is low during an R/W controlled write cycle, the write pulse width must be the larger of TWLWH or (TWLQZ+TDVWH) to allow the I/O drivers to turn off and data to be placed on the bus for the required TDVWH. If OE is high during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified TWLWH.

- 5. During this period, the I/O pins are in the output state, and input signals must not be applied.

- Transition is measured ±500mV from steady state with a 5pF load (including scope and jig). This 6. parameter is sampled and not 100% tested.

- 7.

- To access RAM,  $\overline{CS} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . To access upper byte,  $\overline{CS} = V_{IL}$ ,  $\overline{UB} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . To access lower byte,  $\overline{CS} = V_{IL}$ ,  $\overline{LB} = V_{IL}$ , 8.  $\overline{\text{SEM}} = V_{IH}$ .

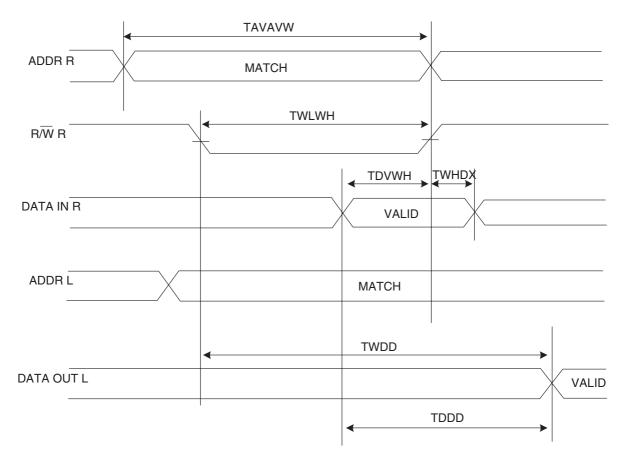

#### Write Cycle 2 (CS Controlled) (Notes 1, 2, 3, 4)

- 1.  $\overline{\text{CS}}$  must be high during all address transitions.

- A write occurs during the overlap (TELWH) of a low  $\overline{CS}$  or  $\overline{SEM}$  and a low  $R/\overline{W}$ . 2.

- TWHAX is measured from the earlier of CS or R/W (or SEM or R/W) going high to the end of write 3. cycle.

- 4. If the CS or SEM low transition occurs simultaneously with or after the R/W low transition, the

- 5.

- To access RAM,  $\overline{CS} = V_{IL}$ .  $\overline{SEM} = V_{IH}$ . To access upper byte  $\overline{CS} = V_{IL}$ ,  $\overline{UB} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . To access lower byte,  $\overline{CS} = V_{IL}$ ,  $\overline{LB} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . 6.

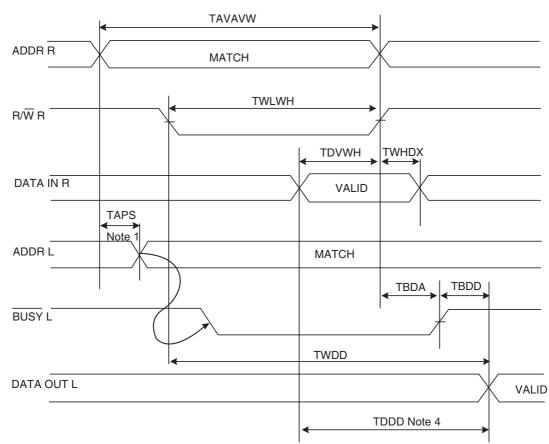

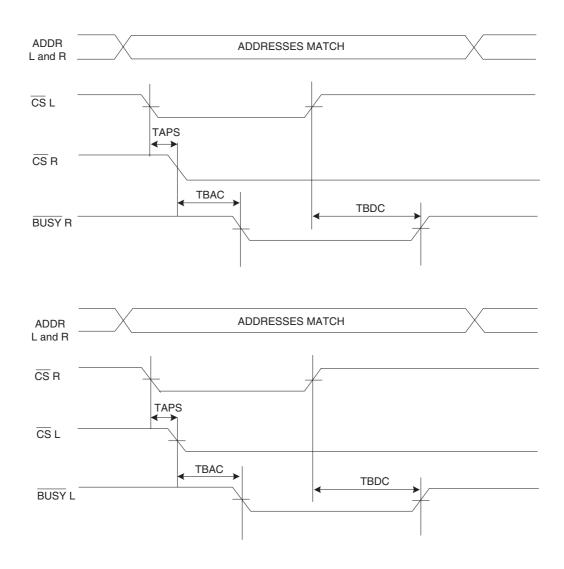

#### Arbitration Read with Busy for Master 67025E (Notes 2, 3, 4)

- 1. To ensure that the earlier of the 2 ports wins.

- 2. Write cycle parameters should be adhered to, to ensure proper writing.

- 3. Device is continuously enabled for both ports.

- 4.  $\overline{OE}$  is low for the reading port.

#### Arbitration Write with Port-to-Port for Slave 67025E (Notes 1, 2, 3)

#### NOTES:

- 1. Assume  $\overline{\text{BUSY}}$  is high for the writing port and  $\overline{\text{OE}}$  is low for the reading port.

- 2. Write cycle parameters should be adhered to ensure proper writing.

- 3. Device is continuously enabled for both ports.

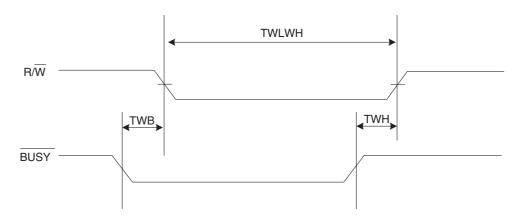

#### Write with Busy for Slave 67025E

**ISSUE 1**

## Contention Cycle No. 1 - $\overline{\text{CS}}$ Arbitration for Master 67025E

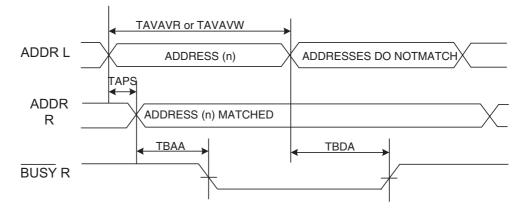

#### Contention Cycle No. 2 - Address Valid Arbitration for Master 67025E (Note 1)

Left Address Valid First:

Right Address Valid First:

1.  $\overline{\text{CSR}} = \overline{\text{CSL}} = V_{\text{IL}}$ .

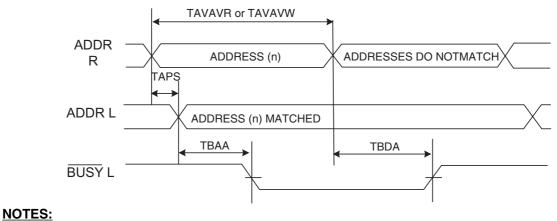

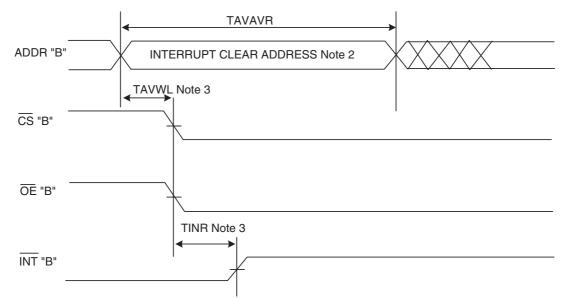

Interrupt Timing (Note 1)

- 1. All timings are the same for both ports. Port "A" may be either the left or right port. Port "B" is the port opposite to "A".

- 2. See interrupt truth table.

- 3. Timing depends on which enable signal is asserted last.

- 4. Timing depends on which enable signal is de-asserted first.

**ISSUE 1**

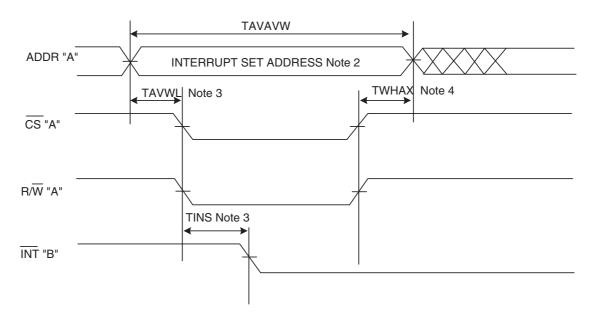

#### Semaphore Read After Write Timing, Either Side (Note 1)

1.  $\overline{CS} = V_{IH}$  for the duration of the above timing (both read and write cycle).

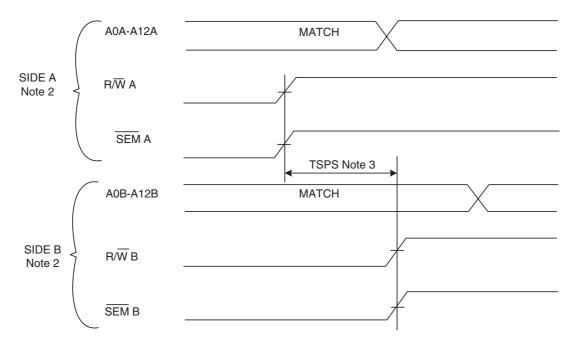

#### Semaphore Contention (Notes 1, 3, 4)

#### NOTES:

1.  $D_{OR} = D_{OL} = V_{IL}$ ,  $\overline{CSR} = \overline{CSL} = V_{IH}$ , semaphore flag is released from both sides (reads as ones from

**ISSUE 1**

both sides) at cycle start.

- 2. Either side A = left and side B = right, or side A = right and side B = left.

- 3. This parameter is measured from the point where R/WA or SEMA goes high until R/WB or SEMB goes high.

- 4. If TSPS is violated, the semaphore will fall positively to one side or the other, but there is no guarantee on which side will obtain the flag.

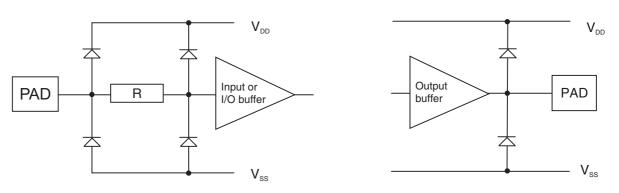

#### 1.11 PROTECTION NETWORKS

EQUIVALENT OF EACH OUTPUT

#### 2. <u>REQUIREMENTS</u>

#### 2.1 <u>GENERAL</u>

The complete requirements for procurement of the components specified herein are as stated in this specification and the ESCC Generic Specification. Permitted deviations from the Generic Specification, applicable to this specification only, are listed below.

Permitted deviations from the Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESCC requirement and do not affect the component's reliability, are listed in the appendices attached to this specification.

#### 2.1.1 Deviations from the Generic Specification

- 2.1.1.1 Deviations from Screening Tests-Chart F3

- (a) High Temperature Reverse Bias Burn-in shall not be performed.

#### 2.2 MARKING

The marking shall be in accordance with the requirements of ESCC Basic Specification No. 21700 and as follows.

**ISSUE 1**

The information to be marked on the component shall be:

- (a) Terminal identification.

- (b) The ESCC qualified components symbol (for ESCC qualified components only).

- (c) The ESCC Component Number.

- (d) Traceability information.

#### 2.3 <u>ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES</u> Electrical measurements shall be performed at room, high and low temperatures.

#### 2.3.1 <u>Room Temperature Electrical Measurements</u>

The measurements shall be performed at  $T_{amb}$ =+22 ±3°C.

| Characteristics                                                 | Symbols          | MIL-STD-883 | Test Conditions                                                                                                                                                                                                                                         | Lin  | nits | Units |

|-----------------------------------------------------------------|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|

|                                                                 |                  | Test Method | Note 1                                                                                                                                                                                                                                                  | Min  | Max  |       |

| Functional Test 1                                               | -                | 3014        | Verify Truth Table<br>Note 2                                                                                                                                                                                                                            | -    | -    | -     |

| Functional Test 2                                               | -                | 3014        | Verify Truth Table<br>Note 2                                                                                                                                                                                                                            | -    | -    | -     |

| Functional Test 3                                               | -                | 3014        | Verify Truth Table<br>Note 2                                                                                                                                                                                                                            | -    | -    | -     |

| Functional Test 4                                               | -                | 3014        | Verify Truth Table<br>Note 2                                                                                                                                                                                                                            | -    | -    | -     |

| Input Clamp<br>Voltage                                          | V <sub>IC</sub>  | 3008        | I <sub>IN</sub> (Under Test)=-300μA<br>All Other Pins =0V<br>V <sub>DD</sub> =V <sub>SS</sub> =0V                                                                                                                                                       | -0.2 | -1.2 | V     |

| Low Level Input<br>Current                                      | IL               | 3009        | V <sub>IN</sub> (Under Test)=0V<br>V <sub>IN</sub> (Remaining<br>Inputs)=0V or 5.5V<br>V <sub>DD</sub> =5.5V, V <sub>SS</sub> =0V                                                                                                                       | -    | -5   | μΑ    |

| High Level Input<br>Current                                     | IIH              | 3010        | V <sub>IN</sub> (Under Test)=5.5V<br>V <sub>IN</sub> (Remaining<br>Inputs)=0V or 5.5V<br>V <sub>DD</sub> =5.5V, V <sub>SS</sub> =0V                                                                                                                     | -    | 5    | μΑ    |

| Output Leakage<br>Current, Third<br>State, Low Level<br>Applied | I <sub>OZL</sub> | 3020        | $\begin{array}{l} V_{OUT} \ (Under \ Test)=0V\\ Other \ Outputs \ Floating\\ V_{IN}(\overline{CSL}, \ \overline{CSR}, \ \overline{OEL}, \\ \overline{OER})=5.5V\\ V_{IN}(R/\overline{WL}, \ R/\overline{WR})=0V\\ V_{DD}=5.5V, \ V_{SS}=0V \end{array}$ | -    | -5   | μA    |

| Characteristics                                                      | Symbols            | MIL-STD-883 | Test Conditions                                                                                                                                                                                                                                                                                                                                                   | Lin | nits       | Units |

|----------------------------------------------------------------------|--------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-------|

|                                                                      |                    | Test Method | Note 1                                                                                                                                                                                                                                                                                                                                                            | Min | Max        |       |

| Output Leakage<br>Current, Third<br>State, High Level<br>Applied     | I <sub>ОZH</sub>   | 3021        | $\begin{array}{l} V_{OUT} \ (Under \\ Test)=5.5V \\ Other \ Outputs \ Floating \\ V_{IN}(\overline{CSL}, \ \overline{CSR}, \ \overline{OEL}, \\ \overline{OER})=5.5V \\ V_{IN}(R/\overline{W}L, \ R/\overline{W}R)=0V \\ V_{DD}=5.5V, \ V_{SS}=0V \end{array}$                                                                                                    | -   | 5          | μA    |

| Low Level Output<br>Voltage                                          | V <sub>OL</sub>    | 3007        | V <sub>IL</sub> =0.8V, V <sub>IH</sub> =2.2V<br>I <sub>OL</sub> =4mA<br>V <sub>DD</sub> =4.5V, V <sub>SS</sub> =0V<br>Note 3                                                                                                                                                                                                                                      | -   | 400        | mV    |

| High Level Output<br>Voltage                                         | V <sub>OH</sub>    | 3006        | $\begin{array}{l} V_{IL} = 0.8V, \ V_{IH} = 2.2V \\ I_{OH} = -4mA \\ V_{DD} = 4.5V, \ V_{SS} = 0V \\ Note \ 4 \end{array}$                                                                                                                                                                                                                                        | 2.4 | -          | V     |

| Stand-by Supply<br>Current 1<br>(Both Ports TTL<br>Level Inputs)     | I <sub>DDSB1</sub> | 3005        | $\label{eq:VIN} \begin{array}{l} \hline V_{IN}(\overline{CSR}, \overline{CSL}, \overline{SEMR}, \\ \overline{SEML}) = 5.3V \\ V_{IN}(Remaining \\ Inputs) = 0.2V \\ f = 0Hz \\ V_{DD} = 5.5V, \ V_{SS} = 0V \\ Note \ 5 \end{array}$                                                                                                                              | -   | 10         | mA    |

| Stand-by Supply<br>Current 2<br>(Both Ports<br>CMOS Level<br>Inputs) | I <sub>DDSB2</sub> | 3005        | $\label{eq:VIN} \begin{array}{l} V_{IN}(\overline{CS}L,\overline{CS}R,\overline{SEM}L,\\ \overline{SEM}R){=}5.3V\\ V_{IN}(Remaining\\ Inputs){=}0.2V \text{ or } 5.3V\\ I_{OUT}{=}0mA\\ f{=}0Hz\\ V_{DD}{=}5.5V,V_{SS}{=}0V\\ Note 5 \end{array}$                                                                                                                 | -   | 500        | μA    |

| Dynamic<br>OperatingCurrent<br>1 (Both Ports<br>Active)              | I <sub>DDOP1</sub> | 3005        | $\begin{array}{l} V_{IN}(\overline{\text{SEM}}, \overline{\text{OE}}) = 2.2 V \\ V_{IN}(\overline{\text{CSR}}, \overline{\text{CSL}}) = 0.8 V \\ \text{All Outputs Open} \\ f_{\text{write}} = 33 \text{MHz} (\text{Variant} \\ 01) 22.2 \text{MHz} (\text{Variant} \\ 02) \\ V_{DD} = 5.5 V, V_{SS} = 0 V \\ \text{Variant 01} \\ \text{Variant 02} \end{array}$ | -   | 320<br>260 | mA    |

| Characteristics                                                                  | Symbols            | MIL-STD-883 | Test Conditions                                                                                                                                                                      | Lin      | nits       | Units |

|----------------------------------------------------------------------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|-------|

|                                                                                  |                    | Test Method | Note 1                                                                                                                                                                               | Min      | Max        | 1     |

| Dynamic<br>Operating Current<br>2<br>(One Port Active -<br>One Port Stand<br>By) | I <sub>DDOP2</sub> | 3005        | $\label{eq:VIN} \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                | -        | 200<br>180 | mA    |

| Data Retention<br>Current                                                        | I <sub>DDDR</sub>  | 3005        | $\begin{array}{c} V_{DR}=\!2V \\ V_{IN}(\overline{CSL}, \overline{CSR}, \overline{SEML}, \\ \overline{SEMR})=\!2V \\ V_{IL}=\!0V, V_{IH}=\!2V \\ Notes 5 \text{ and } 6 \end{array}$ | -        | 400        | μΑ    |

| Data Retention<br>Test                                                           | -                  | -           | Note 6                                                                                                                                                                               | -        | -          | -     |

| Input<br>Capacitance                                                             | C <sub>IN</sub>    | 3012        | V <sub>IN</sub> =V <sub>DD</sub> =V <sub>SS</sub> =0V<br>f=1MHz<br>Note 7                                                                                                            | -        | 5          | pF    |

| Output<br>Capacitance                                                            | C <sub>OUT</sub>   | 3012        | V <sub>IN</sub> =V <sub>DD</sub> =V <sub>SS</sub> =0V<br>f=1MHz<br>Note 7                                                                                                            | -        | 7          | pF    |

| Read Cycle Time<br>(Both Ports)                                                  | t <sub>AVAVR</sub> | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variant 01<br>Variant 02                                                                                             | 30<br>45 |            | ns    |

| Address Access<br>Time<br>(Both Ports)                                           | t <sub>avqv</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variant 01<br>Variant 02                                                                                             | -        | 30<br>45   | ns    |

| Output Hold from<br>Address Change<br>(One Port)                                 | t <sub>AVQX</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                                                                                                                         | 3        | -          | ns    |

| Semaphore Flag<br>Update Pulse<br>(Output Enable or<br>Semaphore<br>Enable)      | t <sub>SOP</sub>   | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                                                                                                                         | 15       | -          | ns    |

| Chip Select<br>Access Time<br>(Both Ports)                                       | t <sub>ELQV</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variant 01<br>Variant 02                                                                                             | -        | 30<br>45   | ns    |

| Characteristics                                   | Symbols            | MIL-STD-883 | Test Conditions                                                                          | Lin      | nits     | Units |

|---------------------------------------------------|--------------------|-------------|------------------------------------------------------------------------------------------|----------|----------|-------|

|                                                   |                    | Test Method | Note 1                                                                                   | Min      | Max      | 1     |

| Output Enable<br>Access Time<br>(One Port)        | t <sub>GLQV</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 7<br>Variant 01<br>Variant 02 | -        | 15<br>25 | ns    |

| Chip Select High<br>or Output Enable<br>High to Z | t <sub>ehqz</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 7<br>Variant 01<br>Variant 02 | -        | 15<br>20 | ns    |

| Chip Select Low<br>or Output Enable<br>Low to Z   | t <sub>ELQX</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 7<br>Variant 01<br>Variant 02 | 3<br>5   |          | ns    |

| Chip Select to<br>Power Up Time<br>(One Port)     | t <sub>PU</sub>    | 3003        | V <sub>DD</sub> =5.5V<br>V <sub>SS</sub> =0V<br>Note 7                                   | 0        | -        | ns    |

| Chip Select to<br>Power Down<br>Time (One Port)   | t <sub>PD</sub>    | 3003        | V <sub>DD</sub> =5.5V<br>V <sub>SS</sub> =0V<br>Note 7                                   | -        | 50       | ns    |

| Byte Enable<br>Access Time<br>(Both Ports)        | t <sub>BLQV</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>Note 9<br>V <sub>SS</sub> =0V<br>Variant 01<br>Variant 02 |          | 30<br>45 | ns    |

| Write Cycle Time<br>(Both Ports)                  | t <sub>AVAVW</sub> | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variant 01<br>Variant 02 | 30<br>45 |          | ns    |

| Output High Z<br>Time                             | t <sub>GHQZ</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 7<br>Variant 01<br>Variant 02 |          | 15<br>20 | ns    |

| Address Valid to<br>End of Write<br>(Both Ports)  | t <sub>avwh</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variant 01<br>Variant 02 | 25<br>40 |          | ns    |

| Address Set-up<br>Time (One Port)                 | t <sub>AVWL</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                             | 0        | -        | ns    |

| Characteristics                                             | Symbols           | MIL-STD-883 | Test Conditions                                                                          | Lin      | nits     | Units |

|-------------------------------------------------------------|-------------------|-------------|------------------------------------------------------------------------------------------|----------|----------|-------|

|                                                             |                   | Test Method | Note 1                                                                                   | Min      | Max      | 1     |

| Write Pulse Width<br>(Both Ports)                           | twlwh             | 3003        | $V_{DD}$ =4.5 & 5.5V<br>$V_{SS}$ =0V<br>Note 9<br>Variant 01<br>Variant 02               | 25<br>35 | -        | ns    |

| Write Recovery<br>Time (Both Ports)                         | t <sub>WHAX</sub> | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                             | 0        | -        | ns    |

| Write Enable to<br>Output Inactive                          | twlqz             | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 7<br>Variant 01<br>Variant 02 | -        | 15<br>20 | ns    |

| Output Active<br>From End of Write<br>(One Port)            | t <sub>WHQX</sub> | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                             | 0        | -        | ns    |

| Data Valid to End<br>of Write (Both<br>Ports)               | t <sub>DVWH</sub> | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variant 01<br>Variant 02 | 20<br>25 | -        | ns    |

| Data Hold Time<br>(One Port)                                | t <sub>WHDX</sub> | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9                             | 0        | -        | ns    |

| Chip Select to<br>End of Write<br>(Both Ports)              | t <sub>ELWH</sub> | 3003        | $V_{DD}$ =4.5 & 5.5V<br>$V_{SS}$ =0V<br>Note 8<br>Variant 01<br>Variant 02               | 25<br>40 |          | ns    |

| Write Pulse to<br>Data Delay<br>(Both Ports)                | t <sub>WDD</sub>  | 3003        | $V_{DD}$ =4.5 & 5.5V<br>$V_{SS}$ =0V<br>Note 9<br>Variant 01<br>Variant 02               | -        | 55<br>70 | ns    |

| Write Data Valid<br>to Read Data<br>Delay<br>(Both Ports)   | t <sub>DDD</sub>  | 3003        | $V_{DD}$ =4.5 & 5.5V<br>$V_{SS}$ =0V<br>Note 9<br>Variant 01<br>Variant 02               | -        | 40<br>55 | ns    |

| Arbitration Priority<br>Setup Time<br>(Both Ports)          | t <sub>APS</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                             | 5        | -        | ns    |

| Busy Access<br>Time from Chip<br>Select Low<br>(Both Ports) | t <sub>BAC</sub>  | 3003        | $V_{DD}=4.5 \& 5.5V$ $V_{SS}=0V$ Note 9<br>Variant 01<br>Variant 02                      |          | 25<br>30 | ns    |

| Characteristics                                                     | Symbols           | MIL-STD-883 | Test Conditions                                                                                                     | Lin      | nits     | Units |

|---------------------------------------------------------------------|-------------------|-------------|---------------------------------------------------------------------------------------------------------------------|----------|----------|-------|

|                                                                     |                   | Test Method | Note 1                                                                                                              | Min      | Max      |       |

| Busy Disable<br>Time from Chip<br>Select High<br>(Both Ports)       | t <sub>BDC</sub>  | 3003        | $\begin{array}{c} V_{DD}{=}4.5 \ \& \ 5.5 V \\ V_{SS}{=}0V \\ Note \ 8 \\ Variant \ 01 \\ Variant \ 02 \end{array}$ | -        | 20<br>25 | ns    |

| Busy Access<br>Time from<br>Address Match<br>(Both Ports)           | t <sub>BAA</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variant 01<br>Variant 02                            | -        | 30<br>35 | ns    |

| Busy Disable<br>Time from<br>Address not<br>Matched (Both<br>Ports) | t <sub>BDA</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variant 01<br>Variant 02                            | -        | 25<br>30 | ns    |

| Busy Disable<br>Time to Valid<br>Data Out                           | t <sub>BDD</sub>  | 3003        | -                                                                                                                   | Note     | e 10     | ns    |

| Interrupt Set Time<br>(Both Ports)                                  | t <sub>INS</sub>  | 3003        | $V_{DD}$ =4.5 & 5.5V<br>$V_{SS}$ =0V<br>Note 9<br>Variant 01<br>Variant 02                                          | -        | 25<br>35 | ns    |

| Interrupt Reset<br>Time (Both Ports)                                | t <sub>INR</sub>  | 3003        | $V_{DD}$ =4.5 & 5.5V<br>$V_{SS}$ =0V<br>Note 9<br>Variant 01<br>Variant 02                                          |          | 25<br>35 | ns    |

| Busy Input to<br>Write (Both Ports)                                 | t <sub>WB</sub>   | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                                                        | 0        | -        | ns    |

| Write Hold After<br>Busy<br>(Both Ports)                            | t <sub>WH</sub>   | 3003        | $V_{DD}=4.5 \& 5.5V$ $V_{SS}=0V$ Note 8 Variant 01 Variant 02                                                       | 20<br>25 | -        | ns    |

| Semaphore Flag<br>Contention<br>Window<br>(Both Ports)              | t <sub>SPS</sub>  | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                                                        | 10       | -        | ns    |

| Semaphore<br>Address Access<br>Time                                 | t <sub>SLQV</sub> | 3003        | $V_{DD}=4.5 \& 5.5V$ $V_{SS}=0V$ Note 8 Variant 01 Variant 02                                                       | 30<br>45 | -        | ns    |

**ISSUE 1**

| Characteristics                         | Symbols           | MIL-STD-883 | Test Conditions                                              | Lin | Units |    |

|-----------------------------------------|-------------------|-------------|--------------------------------------------------------------|-----|-------|----|

|                                         |                   | Test Method | Method Note 1                                                |     | Max   |    |

| Semaphore Flag<br>Write to Read<br>Time | t <sub>SWRD</sub> | 3003        | V <sub>DD</sub> =4.5 & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8 | 10  | -     | ns |

#### NOTES:

- Unless otherwise specified all inputs shall be tested for each characteristic, inputs not under test 1. shall be  $V_{IN} = V_{SS}$  or  $V_{DD}$  and outputs not under test shall be open. Functional go-no-go test with the following test sequences:

- 2.

#### **FUNCTIONAL TEST 1**

| Pattern      | Timing<br>(ns) | Access<br>Note (c) | V <sub>DD</sub><br>(V) | V <sub>SS</sub><br>(V) | V <sub>IL</sub><br>(V) | V <sub>IH</sub><br>(V) | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>out comp</sub><br>(V)<br>Note (b) |

|--------------|----------------|--------------------|------------------------|------------------------|------------------------|------------------------|-------------------------|-------------------------|------------------------------------------|

| MARCH        | 110            | L                  | 4.5 & 5.5              | 0                      | 0                      | 3                      | +4                      | -4                      | 1.5                                      |

| CHECKERBOARD | 110            | R/L                | 4.5 & 5.5              | 0                      | 0                      | 3                      | +4                      | -4                      | 1.5                                      |

| CEDES        | 110            | L                  | 4.5 & 5.5              | 0                      | 0                      | 3                      | +4                      | -4                      | 1.5                                      |

| DUAL PORT    | 110            | R/L                | 4.5 & 5.5              | 0                      | 0                      | 3                      | +4                      | -4                      | 1.5                                      |

#### **FUNCTIONAL TEST 2**

| Pattern         | Timing<br>(ns) | Access<br>Note (c) | V <sub>DD</sub><br>(V) | V <sub>SS</sub><br>(V) | V <sub>IL</sub><br>(V) | V <sub>IH</sub><br>(V) | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>out comp</sub><br>(V)<br>Note (b) |

|-----------------|----------------|--------------------|------------------------|------------------------|------------------------|------------------------|-------------------------|-------------------------|------------------------------------------|

| MARCH           | 110            | L                  | 4.5                    | 0                      | -0.5                   | 4.5                    | +4                      | -4                      | 1.5                                      |

| MARCH           | 110            | L                  | 5.5                    | 0                      | -0.5                   | 6                      | +4                      | +4                      | 1.5                                      |

| MARCH           | 110            | L                  | 6.5                    | 0                      | 0                      | 6.5                    | +4                      | +4                      | 1.5                                      |

| CHECKERBOARD    | 110            | R                  | 4.5                    | 0                      | -0.5                   | 4.5                    | +4                      | +4                      | 1.5                                      |

| CHECKERBOARD    | 110            | R                  | 5.5                    | 0                      | -0.5                   | 6                      | +4                      | -4                      | 1.5                                      |

| CHECKERBOARD    | 110            | R                  | 6.5                    | 0                      | 0                      | 6.5                    | +4                      | -4                      | 1.5                                      |

| V <sub>IL</sub> | 110            | R/L                | 5.5                    | 0                      | 0                      | 2.2                    | +4                      | -4                      | 1.5                                      |

| V <sub>IH</sub> | 110            | R/L                | 4.5                    | 0                      | 0.8                    | 3                      | +4                      | -4                      | 1.5                                      |

#### **FUNCTIONAL TEST 3**

| Pattern<br>Note (a) | Timing<br>(ns) | Access<br>Note (c) | V <sub>DD</sub><br>(V) | V <sub>SS</sub><br>(V) | V <sub>IL</sub><br>(V) | V <sub>IH</sub><br>(V) | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>out comp</sub><br>(V)<br>Note (b) |

|---------------------|----------------|--------------------|------------------------|------------------------|------------------------|------------------------|-------------------------|-------------------------|------------------------------------------|

| BUSY                | 110            | R/L                | 4.5 & 5.5              | 0                      | 0                      | 3                      | +4                      | +4                      | 1.5                                      |

| INT                 | 110            | R/L                | 4.5 & 5.5              | 0                      | 0                      | 3                      | +4                      | +4                      | 1.5                                      |

| SEM                 | 110            | R/L                | 4.5 & 5.5              | 0                      | 0                      | 3                      | +4                      | +4                      | 1.5                                      |

**ISSUE 1**

#### FUNCTIONAL TEST 4

| Pattern<br>Note (a)                                     | Timing (ns)   |               | Access<br>Note (c) | V <sub>DD</sub><br>(V) | V <sub>SS</sub><br>(V) | V <sub>IL</sub><br>(V) | V <sub>IH</sub><br>(V) | V <sub>out comp</sub><br>(V)<br>Note (b) |

|---------------------------------------------------------|---------------|---------------|--------------------|------------------------|------------------------|------------------------|------------------------|------------------------------------------|

|                                                         | Variant<br>01 | Variant<br>02 | R/L                |                        |                        |                        |                        |                                          |

| MARCH/<br>CHECKERBOARD/<br>BUSY/ INT/ SEM/<br>DUAL PORT | 30            | 45            |                    | 4.5 & 5.5              | 0                      | 0                      | 3                      | 1.5                                      |

(a)

The Busy Left shall be performed with:

- Busy read right with left contention

- Busy left generation arbitration

- Busy arbitration port left

The Busy Right pattern shall be performed with:

- Busy read left with right contention

- Busy right generation arbitration

- Busy arbitration port right

- (b) The maximum input rise and fall time shall be 5ns.

- (c) When both ports R/L are specified, only the worst case shall be recorded.

- (d) Input Timing Reference Level = 1.5V

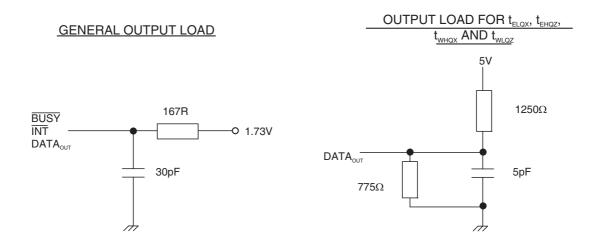

- (e) Output Loading including jig & scope = 30pF except for t<sub>ELQX</sub>, t<sub>EHQZ</sub>, t<sub>WHQX</sub>, and t<sub>WLQZ</sub> where this = 5pF, see circuits below:

- 3. Select address inputs to produce a low level at pin under test.

- 4. Select address inputs to produce a high level at the pin under test.

- 5. Measurements are performed with the memory loaded with a background of zeros, then with a

**ISSUE 1**

background of ones, for all inputs High, then Low. Only the worst case is recorded.

- 6. Data retention procedure:

- (a) Write memory at  $V_{DD}$  = 4.5V with CHECKERBOARD pattern with  $V_{IL}$  = 0V and  $V_{IH}$  = 3V, Timing = 110ns.

- (b) Power down to  $V_{DD} = 2V$  for 250ms.

- (c) Restore  $V_{DD}$  to 4.5V, wait  $t_R$  (operation recovery time, see (e) below) and compare with the original pattern.

- (d) Repeat the procedure with CHECKERBOARD pattern.

- (e)  $t_B = 30$ ns for Variant 01 and 45ns for Variant 02.

- 7. Guaranteed but not tested.

- 8. Measurements shall be performed, on a go-no-go basis, during Functional Test 4.

- 9. Measurements shall be performed during Functional Test 4.

- t<sub>BBD</sub> is a calculated parameter and shall be: either 0ns < t<sub>BDD</sub> ≤ (t<sub>DDD</sub> -t<sub>DVWH</sub>) or 0ns < t<sub>BDD</sub> ≤ (t<sub>WDD</sub> - t<sub>WLWH</sub>)

2.3.2 <u>High and Low Temperatures Electrical Measurements</u>

The measurements shall be performed at  $T_{amb}$ =+125 (+0 -5)°C and  $T_{amb}$ =- 55 (+5 -0)°C.

The characteristics, test methods, conditions and limits shall be the same as specified for Room Temperature Electrical Measurements.

#### 2.4 PARAMETER DRIFT VALUES

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$ =+22 ±3°C.

The test methods and test conditions shall be as per the corresponding test defined in Room Temperature Electrical Measurements.

The drift values ( $\Delta$ ) shall not be exceeded for each characteristic specified. The corresponding absolute limit values for each characteristic shall not be exceeded.

| Characteristics                                            | Symbols            |                     | Limits | Units |    |

|------------------------------------------------------------|--------------------|---------------------|--------|-------|----|

| Note 1                                                     |                    | Drift<br>Value<br>Δ | Abs    |       |    |

|                                                            |                    |                     | Min    | Max   |    |

| Low Level Input Current                                    | IIL                | ±0.1                | -      | -5    | μA |

| High Level Input Current                                   | I <sub>IH</sub>    | ±0.1                | -      | 5     | μA |

| Output Leakage Current, Third State, Low<br>Level Applied  | I <sub>OZL</sub>   | ±0.1                | -      | -5    | μΑ |

| Output Leakage Current, Third State, High<br>Level Applied | I <sub>ОZH</sub>   | ±0.1                | -      | 5     | μΑ |

| Low Level Output Voltage                                   | V <sub>OL</sub>    | ±100                | -      | 400   | mV |

| High Level Output Voltage                                  | V <sub>OH</sub>    | ±0.1                | 2.4    | -     | V  |

| Stand-by Supply Current 1                                  | I <sub>DDSB1</sub> | ±1                  | -      | 10    | mA |

| Stand-by Supply Current 2                                  | I <sub>DDSB2</sub> | ±50                 | -      | 500   | μΑ |

| Data Retention Current                                     | I <sub>DDDR</sub>  | ±40                 | -      | 400   | μΑ |

#### NOTES:

1. Unless otherwise specified all inputs and outputs shall be tested for each characteristic.

## 2.5 INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$ =+22 ±3°C.

The test methods, test conditions and limits shall be as specified for Room Temperature Electrical Measurements.

#### 2.6 <u>POWER BURN-IN CONDITIONS</u>

| Characteristics                                                                                                                                 | Symbols              | Test Conditions                                                    | Units |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------|-------|

| Ambient Temperature                                                                                                                             | T <sub>amb</sub>     | 125 (+0 -5)                                                        | °C    |

| Outputs BUSYL, BUSYR, INTL,<br>INTR                                                                                                             | V <sub>OUT</sub>     | $V_{\text{DD}}$ and $V_{\text{SS}}$                                | V     |

| Inputs A0L and A0R                                                                                                                              | V <sub>IN</sub>      | V <sub>GEN</sub> (S6)                                              | V     |

| Inputs A1L, R to A12L, R                                                                                                                        | V <sub>IN</sub>      | V <sub>GEN</sub> (S7) to V <sub>GEN</sub> (S18)<br>(Note 1)        | V     |

| Input R/WL                                                                                                                                      | V <sub>IN</sub>      | V <sub>GEN</sub> (S1)<br>(Note 2)                                  | V     |

| Input R/WR                                                                                                                                      | V <sub>IN</sub>      | V <sub>GEN</sub> (S2)<br>(Note 2)                                  | V     |

| Inputs OEL, OER                                                                                                                                 | V <sub>IN</sub>      | V <sub>GEN</sub> (S3)<br>(Note 2)                                  | V     |

| Inputs CSL, LBL, UBL                                                                                                                            | V <sub>IN</sub>      | V <sub>GEN</sub> (S4)<br>(Note 2)                                  | V     |

| Inputs CSR, LBR, UBR                                                                                                                            | V <sub>IN</sub>      | V <sub>GEN</sub> (S5)<br>(Note 2)                                  | V     |

| Inputs SEML, SEMR, M/S                                                                                                                          | V <sub>IN</sub>      | V <sub>DD</sub>                                                    | V     |

| Inputs/Outputs I/O0L, I/O2L,<br>I/O4L, I/O6L, I/O8L, I/O10L,<br>I/O12L, I/O14L, I/O0R, I/O2R,<br>I/O4R, I/O6R, I/O8R, I/O10R,<br>I/O12R, I/O14R | V <sub>IN</sub>      | V <sub>GEN</sub> (S19)<br>(Note 1)                                 | V     |

| Inputs/Outputs I/O1L, I/O3L,<br>I/O5L, I/O7L, I/O9L, I/O11L,<br>I/O13L, I/O15L, I/O1R, I/O3R,<br>I/O5R, I/O7R, I/O9R, I/O11R,<br>I/O13R, I/O15R | V <sub>IN</sub>      | V <sub>GEN</sub> (S20)<br>(Note 1)                                 | V     |

| Pulse Voltage                                                                                                                                   | V <sub>GEN</sub>     | 0V to V <sub>DD</sub>                                              | V     |

| Pulse Frequency Square Wave                                                                                                                     | f <sub>GEN(S6)</sub> | $\begin{array}{c} 82.5\\ 50\pm15\% \text{ duty cycle} \end{array}$ | kHz   |

**ISSUE 1**

| Characteristics         | Symbols         | Test Conditions | Units |

|-------------------------|-----------------|-----------------|-------|

| Positive Supply Voltage | V <sub>DD</sub> | 5 (+0.5 -0)     | V     |

| Negative Supply Voltage | V <sub>SS</sub> | 0               | V     |

#### NOTES:

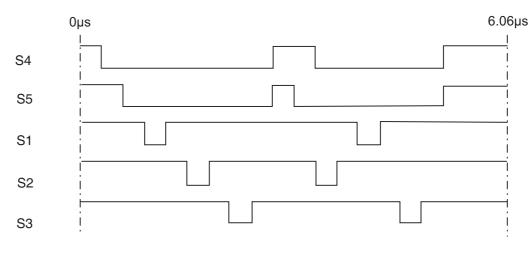

- $f_{GEN(Sn)} = f_{GEN(Sn-1)}/2$ , for n=7 to 20 Signals S1 to S5 are shown below: 1.

- 2.

$t_r$  and  $t_r < 100$  ns

3. Input Protection Resistor = Output Load =  $1k\Omega$ .

#### 2.7 **OPERATING LIFE CONDITIONS** The conditions shall be as specified for Power Burn-in.

#### 2.8 TOTAL DOSE RADIATION TESTING

2.8.1 Bias Conditions and Total Dose Level for Total Dose Radiation Testing Continuous bias shall be applied during radiation testing as specified below.

> The total dose level applied shall be as specified in the component type variant information herein or in the Purchase Order.

| Characteristics                                                                                                                                                                                                                                                                           | Symbols          | Test Conditions | Units |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------|

| Ambient Temperature                                                                                                                                                                                                                                                                       | T <sub>amb</sub> | +22 ±3          | °C    |

| Outputs INTL, INTR, BUSYL, BUSYR                                                                                                                                                                                                                                                          | V <sub>OUT</sub> | Open            | V     |

| Inputs A12L, A12R                                                                                                                                                                                                                                                                         | V <sub>IN</sub>  | Open            | V     |

| Inputs A0L to A11L, A0R to A11R, $\overline{CSL}$ , $\overline{CSR}$ , $\overline{SEML}$ , $\overline{SEMR}$ , $R/\overline{WL}$ , $R/\overline{WR}$ , $\overline{UBL}$ , $\overline{UBR}$ , $\overline{LBL}$ , $\overline{LBR}$ , $M/\overline{S}$ , $\overline{OEL}$ , $\overline{OER}$ | V <sub>IN</sub>  | V <sub>DD</sub> | V     |

**ISSUE 1**

| Characteristics            | Symbols         | Test Conditions | Units |

|----------------------------|-----------------|-----------------|-------|

| Input/Outputs I/OnL, I/OnR | V <sub>IN</sub> | Open            | V     |

| Positive Supply Voltage    | V <sub>DD</sub> | 5(+0.5 -0)      | V     |

| Negative Supply Voltage    | V <sub>SS</sub> | 0               | V     |

#### NOTES:

1. Input protection resistors =  $1 \text{ k}\Omega$ .

#### 2.8.2 Electrical Measurements for Total Dose Radiation Testing

Prior to, during and on completion of radiation testing the devices shall successfully meet the Room Temperature Electrical Measurements specified herein.

Unless otherwise specified the measurements shall be performed at  $T_{amb} = +22\pm3^{\circ}C$ .

The characteristics, test methods, conditions and limits shall be the same as specified for Room Temperature Electrical Measurements.