Pages 1 to 24

# CHARGE COUPLED DEVICES, SILICON, PHOTOSENSITIVE,

# ADVANCED INVERTED MODE SENSOR, BACK

# ILLUMINATED, 740 X 514 IMAGE AREA, FRAME TRANSFER

**BASED ON TYPE CCD55-20**

ESCC Detail Specification No. 9610/004

| Issue 1 December 2010 |

|-----------------------|

|-----------------------|

Document Custodian: European Space Agency - see https://escies.org

**ISSUE 1**

#### LEGAL DISCLAIMER AND COPYRIGHT

European Space Agency, Copyright © 2010. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

# DOCUMENTATION CHANGE NOTICE

(Refer to https://escies.org for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION |

|---------|--------------------|

|         |                    |

# TABLE OF CONTENTS

| <u>1.</u>      | GENERAL                                                                                                                           | 5         |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1.1            | Scope                                                                                                                             | 5         |

| 1.2            | Applicable Documents                                                                                                              | 5         |

| 1.3            | Terms, Definitions, Abbreviations, Symbols and Units                                                                              | 5         |

| 1.4            | The ESCC Component Number and Component Type Variants                                                                             | 5         |

| 1.4.1          | The ESCC Component Number                                                                                                         | 5         |

| 1.4.2          | Component Type Variants                                                                                                           | 5         |

| 1.5            | Maximum Ratings                                                                                                                   | 6         |

| 1.6            | Handling Precautions                                                                                                              | 6         |

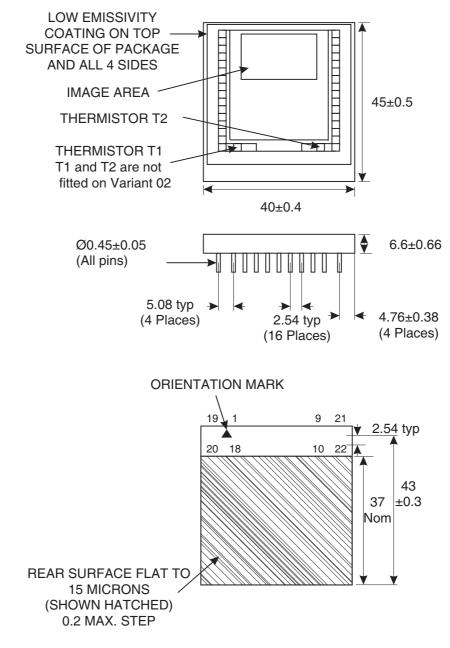

| 1.7            | Physical Dimensions and Terminal Identification                                                                                   | 7         |

| 1.7.1          | Pin Grid Array (PGA) - 22 Pin                                                                                                     | 7         |

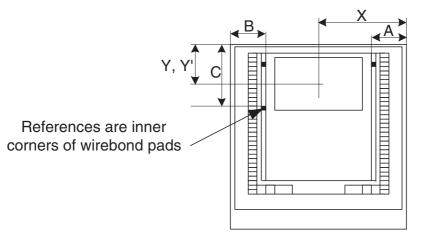

| 1.7.2          | Geometrical References                                                                                                            | 8         |

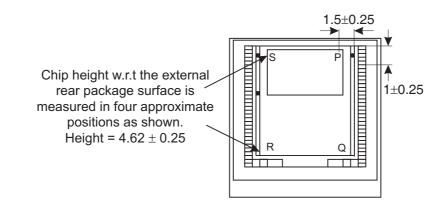

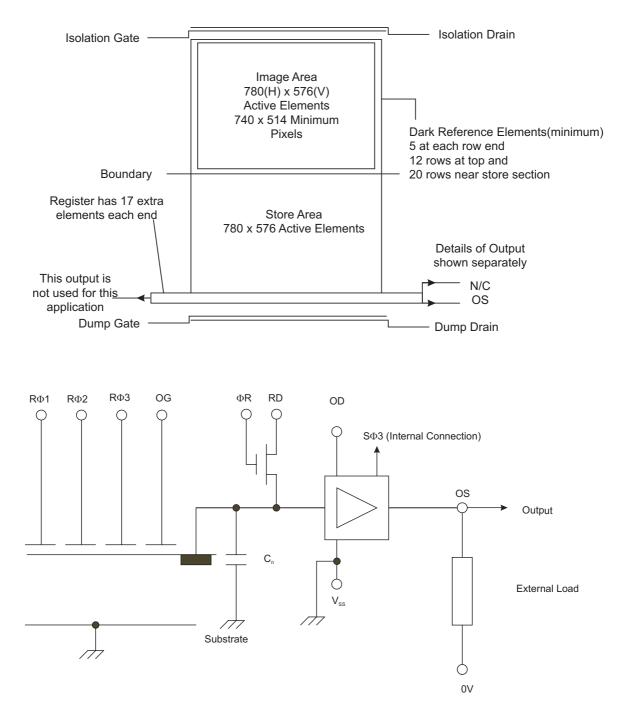

| 1.8            | Functional Diagram                                                                                                                | g         |

| 1.9            | Pin Assignment                                                                                                                    | g         |

| 1.10           | Timing Diagrams                                                                                                                   | 11        |

| 1.11           | Input Protection Network                                                                                                          | 12        |

| 1.12           | Materials and Finishes                                                                                                            | 13        |

| <u>2.</u>      | REQUIREMENTS                                                                                                                      | <u>13</u> |

| 2.1            | General                                                                                                                           | 13        |

| 2.1.1          | Deviations from the Generic Specification                                                                                         | 13        |

| 2.1.1.1        | Devations from Production Control                                                                                                 | 13        |

| 2.1.1.2        | Deviations from Special In-Process Controls - Chart F2                                                                            | 14        |

| 2.1.1.3        | Deviations from Qualification and Periodic Tests - Chart F4                                                                       | 14        |

| 2.1.1.4        | Deviations from Data Documentation Report                                                                                         | 14        |

| 2.2            | Marking                                                                                                                           | 14        |

| 2.3            | Electrical Measurements at Reference, High and Low Temperatures                                                                   | 14        |

| 2.3.1          | Reference Temperature Electrical Measurements                                                                                     | 14        |

| 2.3.2          | High and Low Temperatures Electrical Measurements                                                                                 | 16        |

| 2.3.3          | Notes to Electrical Measurement Tables                                                                                            | 16        |

| 2.4            | Parameter Drift Values                                                                                                            | 19        |

| 2.5            | Intermediate and End-Point Electrical Measurements                                                                                | 19        |

| 2.6            | Burn-in Conditions                                                                                                                | 21        |

| 2.7            | Operating Life Conditions                                                                                                         | 21        |

| 2.8            | Total Dose Radiation Testing                                                                                                      | 22        |

| 2.8.1<br>2.8.2 | Bias Conditions and Total Dose Level for Total Dose Radiation Testing<br>Electrical Measurements for Total Dose Radiation Testing | 22<br>22  |

| 2.0.2          | Lieunda measurements for Total Dose natiation resting                                                                             | 22        |

APPENDIX A

24

#### 1. <u>GENERAL</u>

#### 1.1 <u>SCOPE</u>

This specification details the ratings, physical, electro-optical and electrical characteristics and test and inspection data for the component type variants and/or the range of components specified below. It supplements the requirements of, and shall be read in conjunction with, the ESCC Generic Specification listed under Applicable Documents.

#### 1.2 <u>APPLICABLE DOCUMENTS</u>

The following documents form part of this specification and shall be read in conjunction with it:

- (a) ESCC Generic Specification No. 9020.

- (b) ESCC 25000, Electro-optical Test Methods for Charge Coupled Devices.

- (c) MIL-STD-883, Test Methods and Procedures for Microelectronics.

- 1.3 <u>TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS</u> For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESCC Basic Specification No. 21300 shall apply.

#### 1.4 THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS

#### 1.4.1 <u>The ESCC Component Number</u>

The ESCC Component number shall be constituted as follows:

Example: 961000401D

- Detail Specification Reference: 9610004

- Component Type Variant Number: 01 (as required)

- Total Dose Radiation Level Letter: D (as required)

#### 1.4.2 <u>Component Type Variants</u>

The component type variants applicable to this specification are as follows:

| Variant<br>Number | Based on Type  | Reference<br>Temperature<br>T <sub>ref</sub> ( <sup>o</sup> C) | Case | Weight<br>Max (g) | Total Dose<br>Radiation Level<br>Letter | Number of<br>Thermistors<br>per Device |

|-------------------|----------------|----------------------------------------------------------------|------|-------------------|-----------------------------------------|----------------------------------------|

| 01                | CCD55-20-*-B18 | +5                                                             | PGA  | 35                | D [10kRAD(Si)]                          | 2                                      |

| 02                | CCD55-20-*-C61 | +5                                                             | PGA  | 35                | D [10kRAD(Si)]                          | 0                                      |

Total dose radiation level letters are defined in ESCC Basic Specification No. 22900. If an alternative radiation test level is specified in the Purchase Order the letter shall be changed accordingly.

#### 1.5 MAXIMUM RATINGS

The maximum ratings shall not be exceeded at any time during use or storage.

Maximum ratings shall only be exceeded during testing to the extent specified in this specification and when stipulated in Test Methods and Procedures of the ESCC Generic Specification.

| Characteristics                          | Symbols          | Maximum Ratings | Units  | Remarks                         |

|------------------------------------------|------------------|-----------------|--------|---------------------------------|

| Input Voltage                            | V <sub>IN</sub>  | -20 to +20      | V      | Notes 1, 3                      |

|                                          |                  | -0.3 to +25     |        | Notes 2, 3                      |

| Input Voltage, Pin OD                    | V <sub>IN</sub>  | -0.3 to +35     | V      | Notes 3, 4                      |

| Output Voltage, Pin OS                   | V <sub>OUT</sub> | -0.3 to +25     | V      | Notes 3, 4                      |

| Thermistor Maximum Voltage<br>Difference | -                | Note 5          | -      | Not applicable to<br>Variant 02 |

| Operating Temperature Range              | T <sub>op</sub>  | -55 to +50      | °C     | Note 6                          |

| Storage Temperature Range                | T <sub>stg</sub> | -55 to +125     | °C     |                                 |

| Rate of Change of Temperature            | -                | 5               | °C/min | Note 7                          |

#### NOTES:

- 1. For input pins ΦR, IΦn, RΦn, SΦn, IG, DG, OG.

- 2. For input pins RD, DD.

- 3. With respect to V<sub>SS</sub>.

- 4. Maximum voltage applied between OD and OS shall not exceed  $\pm 15V$ .

- 5. Maximum voltage difference across T1+ and T1- and T2+ and T2- shall be such that the thermistor temperature does not exceed 150°C (given that 1mW raises T by 1°C).

- 6. Device is functional for -55≤T<sub>op</sub>≤+125<sup>o</sup>C but with degraded performance. Parameters are not guaranteed in this temperature range.

- 7. Rate of change of temperature is applicable over the operating and storage (non-operating) temperature ranges.

#### 1.6 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are categorised as Class 1 per ESCC Basic Specification No. 23800.

#### 1.7 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

#### 1.7.1 Pin Grid Array (PGA) - 22 Pin

### NOTES:

- 1. All dimensions in mm.

- 2. Pin numbers shown for identification purposes only.

#### 1.7.2 <u>Geometrical References</u>

X and Y define the centre of the 576 x 780 array of active elements. X and Y' define the centre of the minimum imaging 514 x 740 pixels. A, B and C are measured from the optical references.  $X = A + 10.10, X = 20 \pm 0.45$  $Y = C - 6.39, Y = 9.72 \pm 0.25, Y' = Y - 0.09$

#### NOTES:

1. All dimensions in mm.

#### 1.8 FUNCTIONAL DIAGRAM

### 1.9 <u>PIN ASSIGNMENT</u>

| Pin | Function                                  |

|-----|-------------------------------------------|

| 1   | R $\Phi$ 3 Input (Readout Register Clock) |

| Pin | Function                                                           |

|-----|--------------------------------------------------------------------|

| 2   | RΦ2 Input (Readout Register Clock)                                 |

| 3   | SØ3 Input (Storage Section Clock)                                  |

| 4   | S       S                                                          |

| 5   | S                                                                  |

| 6   | DG Input (Dump Gate)                                               |

| 7   | IG Input (Isolation Gate)                                          |

| 8   | OD Input (Output Transistor Drain)                                 |

| 9   | OG input (Output Gate)                                             |

| 10  | RD Input (Reset Transistor Drain)                                  |

| 11  | OS Output (Output Transistor Source)                               |

| 12  | DD Input (Dump Drain)                                              |

| 13  | V <sub>SS</sub> (Substrate Bias)                                   |

| 14  | I      I                                                           |

| 15  | I  4 2 Input (Image Section Clock)                                 |

| 16  | I  4 3 Input (Image Section Clock)                                 |

| 17  | ΦR Input (Output Reset Pulse)                                      |

| 18  | R                                                                  |

| 19  | Variant 01 = T1 + Output (Thermistor) ; Variant 02 = No Connection |

| 20  | Variant 01 = T1 - Output (Thermistor) ; Variant 02 = No Connection |

| 21  | Variant 01 = T2 + Output (Thermistor) ; Variant 02 = No Connection |

| 22  | Variant 01 = T2 - Output (Thermistor) ; Variant 02 = No Connection |

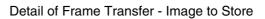

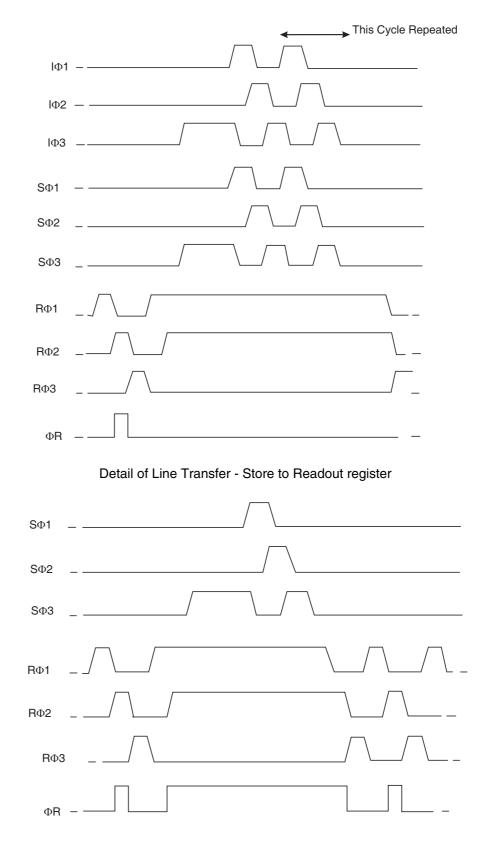

### 1.10 <u>TIMING DIAGRAMS</u>

#### Detail of Vertical Line Transfer - Single line dump

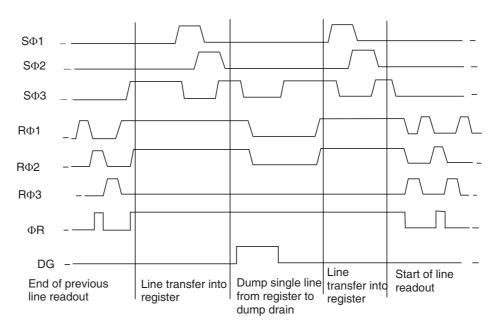

#### Drive Pulse Waveform

#### NOTES:

- 1. Pulses should be symmetrical and overlap at 50% points, as shown.

- 2. Rise and fall times (t<sub>r</sub>, t<sub>f</sub>), 10 to 90%, are defined in Note 2 of Notes to Electrical Measurement Tables herein.

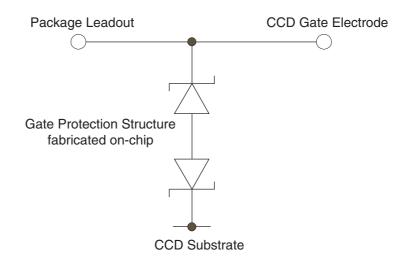

1.11

INPUT PROTECTION NETWORK

Inputs DG, IG, OG, ΦR, IΦn, RΦn and SΦn are protected as shown:

#### 1.12 <u>MATERIALS AND FINISHES</u>

a) CCD Package

The CCD package shall be of multilayered co-fired aluminium oxide and aluminium nitride construction. The external top and side surfaces shall be gold plated over nickel and tungsten.

- b) Input Window/Lid Seal

- None

- c) Terminal Material and Finish The terminal material shall be Type D in accordance with ESCC Basic Specification No. 23500. The terminal finish shall be gold, thickness 1.524μm min over nickel, thickness 1.27μm min, 8.89μm max.

#### 2. <u>REQUIREMENTS</u>

#### 2.1 <u>GENERAL</u>

The complete requirements for procurement of the components specified herein are as stated in this specification and the ESCC Generic Specification. Permitted deviations from the Generic Specification, applicable to this specification only, are listed below.

Permitted deviations from the Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESCC requirement and do not affect the component's reliability, are listed in the appendices attached to this specification.

#### 2.1.1 Deviations from the Generic Specification

#### 2.1.1.1 Devations from Production Control

(a) Rebonding of wire bonds is permitted as defined:

No more than three rebonds are permitted anywhere on any one device. No bondlink may be reworked more than once; ie there may be no more than two bond feet, or attempted bond feet, on any bond pad, whether chip or package. No more than two adjacent bond pads, on chip or package,

may be subjected to rebonding.

#### 2.1.1.2 Deviations from Special In-Process Controls - Chart F2

- (a) Die Shear/Substrate Attach Strength testing is not performed.

- 2.1.1.3 Deviations from Qualification and Periodic Tests Chart F4

- (a) Permanence of Marking shall not be performed.

- (b) Operating Life. For Periodic Tests, the duration shall be 1000 hours, with electrical measurements performed in accordance with Intermediate and End-Point Electrical Measurements herein at 0 and 1000 ±48 hours.

- 2.1.1.4 Deviations from Data Documentation Report

- (a) Special In-Process Controls data shall be held by the manufacturer and not delivered.

#### 2.2 <u>MARKING</u>

The marking shall be in accordance with the requirements of ESCC Basic Specification No. 21700 and as follows.

The information to be marked on the component shall be:

- (a) Terminal identification.

- (b) The ESCC qualified components symbol (for ESCC qualified components only).

- (c) The ESCC Component Number.

- (d) Traceability information.

- 2.3 <u>ELECTRICAL MEASUREMENTS AT REFERENCE, HIGH AND LOW TEMPERATURES</u> Electrical measurements shall be performed at reference, high and low temperatures. Consolidated Notes are given after the tables.

#### 2.3.1 <u>Reference Temperature Electrical Measurements</u>

Unless otherwise specified the measurements shall be performed at  $T_{ref} \pm 3^{\circ}C$ .

| Characteristics                   |    | Test Conditions      | Limits                                                                                              |     | Units |    |

|-----------------------------------|----|----------------------|-----------------------------------------------------------------------------------------------------|-----|-------|----|

|                                   |    | Test Method<br>Para. |                                                                                                     | Min | Max   |    |

| Leakage Current<br>on Input Gates | ΙL | 5.1                  | $V_{IN}(Input Gates)=20V V_{IN}(Remaining Inputs)=0V V_{OUT}=0V V_{SS}=0V T_{amb}=+21\pm3^{\circ}C$ | -   | 10    | nA |

**ISSUE 1**

| Characteristics                             | Symbols             | ESCC 25000               | Test Conditions                                                                                               | Lin                        | nits                  | Units         |

|---------------------------------------------|---------------------|--------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|---------------|

|                                             |                     | Test Method<br>Para.     |                                                                                                               | Min                        | Мах                   | 1             |

| Power Supply<br>Current 1                   | I <sub>OD</sub>     | 5.3                      | Notes 1, 2                                                                                                    | -                          | 10                    | mA            |

| Power Supply<br>Current 2                   | I <sub>RD</sub>     | 5.3                      | Notes 1, 2                                                                                                    | -                          | 100                   | nA            |

| DC Output<br>Voltage Level                  | V <sub>REF</sub>    | 5.4                      | V <sub>IN</sub> (ΦR)=12V, V <sub>IN</sub><br>(Remaining Inputs)=0V                                            | Note 3                     |                       | V             |

| Reset Pulse<br>Feedthrough                  | V <sub>RESET</sub>  | 5.5                      | Notes 1, 2                                                                                                    | -                          | 100                   | mV            |

| Offset Voltage                              | V <sub>OFFSET</sub> | 6.5                      | Notes, 1, 2                                                                                                   | -                          | 25                    | mV            |

| Thermistor<br>Resistance<br>Variant 01 only | R <sub>T</sub>      | -                        | -                                                                                                             | No                         | te 4                  | kΩ            |

| Charge to Voltage<br>Conversion Factor      | CVF                 | 6.18                     | Notes 1, 2                                                                                                    | 0.8                        | 1.2                   | μV/e          |

| Full Well Capacity<br>(Image Section)       | V <sub>SAT-IM</sub> | 6.7(a):<br>Global Method | Uniform illumination<br>Notes 1, 2                                                                            | 300                        | -                     | ke            |

| Full Well Capacity<br>(Readout<br>Register) | V <sub>SAT-RE</sub> | 6.8                      | Number of binned lines<br>= 8,<br>Uniform illumination<br>Notes 1, 2                                          | 1200                       | -                     | ke            |

| Linearity Error (to 240ke/p)                | LE                  | 6.6                      | Uniform illumination<br>Notes 1, 2                                                                            | -                          | 1                     | %             |

| Average Dark<br>Signal                      | DS <sub>AV</sub>    | 6.20                     | Notes 1, 2                                                                                                    | -                          | 125                   | e/pix<br>el/s |

| Dark Signal Non-<br>uniformity              | DSNU                | 6.21                     | Notes 1, 2                                                                                                    | -                          | 50                    | e/pix<br>el/s |

| Quantum<br>Efficiency                       | QE                  | 6.19                     | Uniform illumination<br>Notes 1, 2, 5<br>Wavelength=<br>350nm<br>400nm<br>500nm<br>650nm<br>900nm             | 50<br>80<br>80<br>75<br>30 | -<br>-<br>-<br>-<br>- | %             |

| Photo Response<br>Non-uniformity            | PRNU                | 6.14                     | Uniform illumination<br>Notes 1, 2<br>Wavelength=<br>400nm (~10nm<br>bandwidth)<br>550nm (~80nm<br>bandwidth) | -                          | 5<br>3                | %             |

**ISSUE 1**

| Characteristics                                        | Symbols          | ESCC 25000           | Test Conditions                                                                       | Limits |         | Units |

|--------------------------------------------------------|------------------|----------------------|---------------------------------------------------------------------------------------|--------|---------|-------|

|                                                        |                  | Test Method<br>Para. |                                                                                       | Min    | Max     |       |

| Total Charge<br>Transfer<br>Inefficiency -<br>Vertical | VCTI             | 6.12                 | No illumination<br>Notes 1, 2, 6                                                      | -      | 1.5     | %     |

| Store Shield<br>Position                               | -                | -                    | Uniform illumination<br>Notes 1, 2, 7                                                 | -      | -       | -     |

| Photo Response<br>Defects<br>Pixels<br>Columns         | -                | -                    | Notes 1, 2, 8<br>(Identified from the<br>data frame of the<br>measurement of<br>PRNU) | -      | 20<br>0 | -     |

| Defects in<br>Darkness<br>Pixels<br>Columns            | -                | -                    | Notes 1, 2, 9                                                                         | -      | 60<br>0 | -     |

| Output Impedance                                       | Z <sub>OUT</sub> | -                    | Notes 1, 2, 10                                                                        | -      | -       | -     |

## 2.3.2 High and Low Temperatures Electrical Measurements

The measurements shall be performed at temperatures defined below.

| Characteristics                             | Symbols         | ESCC 25000           | Test Conditions                                                                            | Limits |      | Units |

|---------------------------------------------|-----------------|----------------------|--------------------------------------------------------------------------------------------|--------|------|-------|

|                                             |                 | Test Method<br>Para. | Note 11                                                                                    | Min    | Max  |       |

| Charge to Voltage                           | CVF             | 6.18                 | Notes 1, 2                                                                                 |        |      | μV/e  |

| Conversion Factor                           |                 |                      | T <sub>amb</sub> =+50(+0 -5) <sup>o</sup> C<br>T <sub>amb</sub> =-27(+5 -0) <sup>o</sup> C | 0.7    | 1.1  |       |

|                                             |                 |                      | $T_{amb}^{-1} = -27(+5 - 0)^{\circ}C$                                                      | 0.9    | 1.3  |       |

| Power Supply                                | I <sub>OD</sub> | 5.3                  | Notes 1, 2                                                                                 |        |      | mA    |

| Current 1                                   |                 |                      | T <sub>amb</sub> =+50(+0 -5) <sup>o</sup> C<br>T <sub>amb</sub> =-27(+5 -0) <sup>o</sup> C | -      | 10   |       |

|                                             |                 |                      | $T_{amb}^{-1} = -27(+5 - 0)^{\circ}C$                                                      | -      | 10   |       |

| Thermistor<br>Resistance<br>Variant 01 only | R <sub>T</sub>  | -                    | T <sub>amb</sub> =+50(+0 -5) <sup>o</sup> C<br>T <sub>amb</sub> =-27(+5 -0) <sup>o</sup> C | Not    | te 4 | kΩ    |

### 2.3.3 Notes to Electrical Measurement Tables

1. The CCD shall be biased as follows during electro-optical tests:

| Parameter              | Symbol          | Conditions            | Unit |

|------------------------|-----------------|-----------------------|------|

| Output Amplifier Drain | V <sub>OD</sub> | 32(+1 -5)             | V    |

| Reset Drain Bias       | V <sub>RD</sub> | 19±2                  | V    |

| Substrate Bias         | V <sub>SS</sub> | 9(+2 -1)              | V    |

| Output Gate Bias       | V <sub>OG</sub> | 3±2                   | V    |

| Diode Drain            | V <sub>DD</sub> | 25 to V <sub>OD</sub> | V    |

**ISSUE 1**

| Parameter                               | Symbol          | Conditions | Unit |

|-----------------------------------------|-----------------|------------|------|

| Unused Register (as set on test camera) | V <sub>IG</sub> | 10(+0 -10) | V    |

2. All Clock low levels taken as 0±0.5V, except Readout Clock low =1±0.5V. Readout frequency  $\sim$ 1MHz, External Load Resistance on test camera  $\sim$ 4k $\Omega$ .

| Clock Description | Parameter                               | Conditions     | Unit |

|-------------------|-----------------------------------------|----------------|------|

| Image Clocks IΦn  | High Level                              | 15(+0 -3)      | V    |

|                   | Pulse Width                             | ≥2             | μs   |

|                   | Initial Pulse Width after Static Clocks | 10(+90 -5)     |      |

|                   | Rise/Fall Times                         | 0.2(+0.3 -0.1) |      |

|                   | Overlap                                 | ≥90            | %    |

| Store Clocks S    | High Level                              | 15(+0 -3)      | V    |

|                   | Pulse Width                             | ≥2             | μs   |

|                   | Initial Pulse Width after Static Clocks | 10(+90 -5)     |      |

|                   | Rise/Fall Times                         | 0.2(+0.3 -0.1) |      |

|                   | Overlap                                 | ≥90            | %    |

| Readout Clocks    | High Level                              | 13(+2 -3)      | V    |

| RΦn               | Rise/Fall Times                         | 45(+5 -35)     | ns   |

|                   | Overlap                                 | 100            | %    |

| Reset Pulse RD    | High Level                              | 12(+3 -2)      | V    |

|                   | Pulse Width                             | ≥100           | ns   |

|                   | Rise/Fall Times                         | 35(+15 -25)    |      |

| Dump Gate DG      | High Level                              | 14(+1 -4)      | V    |

|                   | Rise/Fall Times                         | ≥50            | ns   |

- 3. DC level is typically 4 to 6 Volts below V<sub>OD</sub>.

- 4. Thermistor resistance is measured for information only.

- 5. The pixel area is defined as rows 250 to 299 inclusive with a width of 740 pixels (the minimum guaranteed pixel area). The average signal shall be approximately 50% of the measured full well capacity.

- 6. The average signal shall be approximately 80% of the measured full well capacity. The clock sequence is modified to give frame transfer operations with the following features:

- i) a frame transfer at normal rate but including an additional 10 line transfer cycles (overscan times). The dump gate is held high during the frame transfer operation but is taken low before the line readout commences.

- ii) The normal line by line readout of the store section signal (576 rows) with digitisation and frame stored as normal.

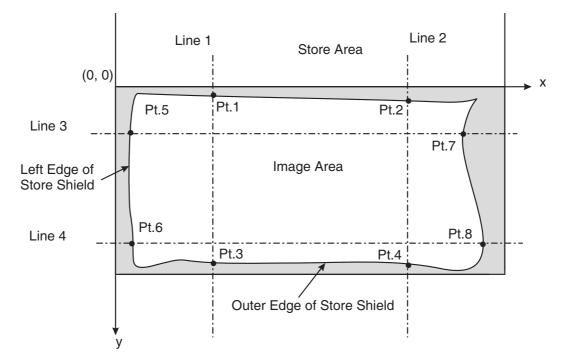

- 7. Refer to the Functional Diagram herein. The Store Shield Position is calculated using eight points at specific places on the image area, as shown below. Each point is the location of a pixel with at least 50% of the unshielded signal level and having two immediately adjacent pixels of this value or greater.

Lines 1, 2, 3 and 4 are at 1/4 and 3/4 across the image area in each direction. Points 1, 2, 3,..., 8, with coordinates (x1, y1), (x2, y2), etc., are the locations of the 50% threshold pixels (see above). The coordinates of these points are used to calculate, in pixels, the average Left, Right, Outer and Store Edge positions and Shield Rotation as follows:

Average Store Edge Position = (y1 + y2) / 2

Average Outer Edge Position = 575 - (y3 + y4) / 2

Average Left Edge Position = (x5 + x6) / 2

Average Right Edge Position = 779 - (x7 + x8) / 2

Average Rotation = {(x5 - x6 + x7 - x8) + (y2 - y1 + y4 - y3) x 514 / 740} / 2

- 8. Photo response defect pixels are those whose signal is more than 20% below the mean signal level of all of the pixels. Column defects are defined as those columns with ≥50 defective pixels.

- 9. Defects in darkness pixels are defined as pixels with signals above a pre-defined threshold when the device is un-illuminated. Column defects are defined as those columns with ≥50 defective pixels. The threshold for defect counting is set to be 50 times the maximum specified mean dark signal at the reference temperature.

- 10. The procedure for calculating  $Z_{OUT}$  is as follows:

- Measure the output signal for a given level of illumination (nominally 50% of saturation) averaged over a 100 x 100 pixel block.

- Shunt the amplifier output with a (known) AC coupled resistive load and repeat the output signal measurement.

- The output impedance can then be calculated from the ratio of the two output signals:

$$\frac{1}{Z_{\text{OUT}}} = \frac{1}{R_{\text{TEST}}(\text{refsig}/\text{shntsig}-1)} - \frac{1}{R_{\text{LOAD}}}$$

Where

$R_{TEST}$  = test resistive load (nominally 470 $\Omega$ ).

$R_{LOAD} = CCD$  output load resistor (nominally  $4k\Omega$ ).

refsig = output signal, no test load.

shntsig = output signal with test load.

11. Read and record measurements shall be performed on a sample of 5 components with 0 failures allowed. Alternatively a 100% inspection may be performed.

#### 2.4 PARAMETER DRIFT VALUES

Unless otherwise specified, the measurements shall be performed at  $T_{ref} \pm 3^{\circ}C$ .

The test methods and test conditions shall be as per the corresponding test defined in Reference Temperature Electrical Measurements.

The drift values ( $\Delta$ ) shall not be exceeded for each characteristic specified. The corresponding absolute limit values for each characteristic shall not be exceeded.

| Characteristics                | Symbols          | Limits             |      |       | Units     |

|--------------------------------|------------------|--------------------|------|-------|-----------|

|                                |                  |                    | Abso | olute |           |

|                                |                  | Value<br>$\Delta$  | Min  | Max   |           |

| Leakage Current on Input Gates | ΙL               | ±1 or (1)<br>±100% | -    | 10    | nA        |

| Power Supply Current 1         | I <sub>OD</sub>  | ±25%               | -    | 10    | mA        |

| Average Dark Signal            | DS <sub>AV</sub> | ±100%              | -    | 125   | e/pixel/s |

#### NOTES:

1. Whichever is the greater, referred to the initial value.

#### 2.5 INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS

Unless otherwise specified, the measurements shall be performed at  $T_{ref} \pm 3^{\circ}C$ .

The test methods and test conditions shall be as per the corresponding test defined in Reference Temperature Electrical Measurements.

The drift values ( $\Delta$ ) shall not be exceeded for each characteristic where specified. The corresponding absolute limit values for each characteristic shall not be exceeded.

| Characteristics                | Symbols         |                               | Limits |       | Units |

|--------------------------------|-----------------|-------------------------------|--------|-------|-------|

|                                |                 | Drift                         | Abso   | olute |       |

|                                |                 | Value<br>$\Delta$<br>(Note 2) | Min    | Max   |       |

| Leakage Current on Input Gates | ΙL              | ±1 or<br>(1)<br>± 100%        | -      | 10    | nA    |

| Power Supply Current 1         | I <sub>OD</sub> | ±25%                          | -      | 10    | mA    |

**ISSUE 1**

| Characteristics                                      | Symbols             |                            | Limits |         | Units     |

|------------------------------------------------------|---------------------|----------------------------|--------|---------|-----------|

|                                                      |                     | Drift                      | Abs    | olute   | -         |

|                                                      |                     | Value<br><u> </u> (Note 2) | Min    | Max     |           |

| Power Supply Current 2                               | I <sub>RD</sub>     | -                          | -      | 100     | nA        |

| DC Output Voltage Level                              | V <sub>REF</sub>    | -                          | No     | te 3    | V         |

| Reset Pulse Feedthrough                              | V <sub>RESET</sub>  | -                          | -      | 100     | mV        |

| Offset Voltage                                       | V <sub>OFFSET</sub> | -                          | -      | 25      | mV        |

| Charge to Voltage Conversion<br>Factor               | CVF                 | -                          | 0.8    | 1.2     | μV/e      |

| Full Well Capacity (Image Section)                   | V <sub>SAT-IM</sub> | -                          | 300    | -       | ke        |

| Full Well Capacity (Readout Register)                | V <sub>SAT-RE</sub> | -                          | 1200   | -       | ke        |

| Linearity Error (to 240ke/p)                         | LE                  | -                          | -      | 1       | %         |

| Average Dark Signal                                  | DS <sub>AV</sub>    | ±100%                      | -      | 125     | e/pixel/s |

| Dark Signal Non-uniformity                           | DSNU                | -                          | -      | 50      | e/pixel/s |

| Quantum Efficiency (Note 4)                          | QE                  |                            |        |         | %         |

| Wavelength = 350nm                                   |                     | -                          | 50     | -       |           |

| Wavelength = 400nm                                   |                     | -                          | 80     | -       |           |

| Wavelength = 500nm                                   |                     | -                          | 80     | -       |           |

| Wavelength = 650nm                                   |                     | -                          | 75     | -       |           |

| Wavelength = 900nm                                   |                     | -                          | 30     | -       |           |

| Photo Response Non-uniformity<br>(Note 4)            | PRNU                |                            |        |         | %         |

| Wavelength = 400nm (~10nm bandwidth)                 | -                   | -                          | -      | 5       |           |

| Wavelength = 550nm (~80nm bandwidth)                 | -                   | -                          | -      | 3       |           |

| Total Charge Transfer Inefficiency -<br>Vertical     | VCTI                | -                          | -      | 1.5     | %         |

| Store Shield Position                                | -                   | -                          | -      | -       | -         |

| Photo Response Defects (Note 4)<br>Pixels<br>Columns |                     |                            | -      | 20<br>0 | -         |

| Defects in Darkness<br>Pixels<br>Columns             | -                   |                            | -      | 60<br>0 | -         |

| Output Impedance                                     | Z <sub>OUT</sub>    | -                          | -      | -       | -         |

**ISSUE 1**

### NOTES:

- Whichever is greater, referred to the initial value. 1.

- 2. The drift values ( $\Delta$ ) are applicable to the Operating Life test only.

- DC level is typically 4 to 6 Volts below V<sub>OD</sub>. З.

- 4. These parameters are not measured as part of the Mechanical and Environmental subgroups of Chart F4 of ESCC Specification No. 9020.

#### 2.6 **BURN-IN CONDITIONS**

| Characteristics               | Symbols           | Test Conditions          | Unit  |

|-------------------------------|-------------------|--------------------------|-------|

| Case Temperature              | T <sub>case</sub> | 125(+0, -5)              | °C    |

| Output Transistor Drain Bias  | V <sub>OD</sub>   | 25.5                     | V     |

| Reset Transistor Drain Bias   | V <sub>RD</sub>   | 10.5                     | V     |

| Dump Drain Bias               | V <sub>DD</sub>   |                          |       |

| Substrate Bias                | V <sub>SS</sub>   | 0                        | V     |

| Storage Section Clock         | V <sub>SФ3</sub>  | V <sub>X0</sub> (Note 3) | V     |

| Dump Gate Bias                | V <sub>DG</sub>   |                          |       |

| Isolation Gate Bias           | V <sub>IG</sub>   |                          |       |

| Image Section Clock           | V <sub>IΦ3</sub>  |                          |       |

| Readout Register Clock        | V <sub>RΦ3</sub>  | V <sub>X1</sub> (Note 3) | V     |

| Readout Register Clock        | V <sub>RΦ2</sub>  | V <sub>X2</sub> (Note 3) | V     |

| Storage Section Clock         | ν <sub>SΦ2</sub>  |                          |       |

| Image Section Clock           | V <sub>ΙΦ2</sub>  |                          |       |

| Output Reset Pulse            | $V_{\Phi R}$      |                          |       |

| Storage Section Clock         | ν <sub>SΦ1</sub>  | V <sub>X3</sub> (Note 3) | V     |

| Output Gate Bias              | V <sub>OG</sub>   |                          |       |

| Image Section Clock           | V <sub>ΙΦ1</sub>  |                          |       |

| Readout Register Clock        | V <sub>RΦ1</sub>  |                          |       |

| Constant Current Load         | I <sub>OS</sub>   | 7.5±1                    | mA    |

| Switched Voltage Cycle Period | t <sub>sv</sub>   | 6±0.1                    | hours |

| Thermistors (Variant 01 only) | V <sub>th</sub>   | Open                     | V     |

#### NOTES:

- All voltages are  $\pm 0.2V$ . 1.

- 2. The CCD is illuminated so that the pixel well capacities are over saturated (to ensure that a sufficient number of holes are generated to pin the silicon surface to  $V_{SS}$ ).

- З.  $V_{X0}=V_{X1}=V_{X2}=V_{X3}=-15V$  with a 0V period of duration  $t_{sv}$  applied sequentially during each 24 hour period.

### **OPERATING LIFE CONDITIONS**

The conditions shall be as specified for Burn-in.

2.7

#### 2.8 <u>TOTAL DOSE RADIATION TESTING</u>

2.8.1 <u>Bias Conditions and Total Dose Level for Total Dose Radiation Testing</u> Continuous bias shall be applied during irradiation as specified below.

The total dose level applied shall be as specified in the component type variant information herein or in the Purchase Order.

| Characteristics               | Symbols           | Test Conditions | Unit |  |

|-------------------------------|-------------------|-----------------|------|--|

| Case Temperature              | T <sub>case</sub> | +20±10          | °C   |  |

| Output Transistor Drain Bias  | V <sub>OD</sub>   | 32±1            | V    |  |

| Dump Drain Bias               | V <sub>DD</sub>   |                 |      |  |

| Reset Transistor Drain Bias   | V <sub>RD</sub>   | 19±0.5          | V    |  |

| Substrate Bias                | V <sub>SS</sub>   | 9±1             | V    |  |

| Output Reset Pulse            | $V_{\Phi R}$      | 10±0.2          | V    |  |

| Storage Section Clocks        | V <sub>SΦn</sub>  | 0±0.2           | V    |  |

| Image Section Clocks          | V <sub>IΦn</sub>  |                 |      |  |

| Readout Register Clocks       | V <sub>RΦn</sub>  |                 |      |  |

| Dump Gate Bias                | V <sub>DG</sub>   |                 |      |  |

| Isolation Gate Bias           | V <sub>IG</sub>   |                 |      |  |

| Output Gate Bias              | V <sub>OG</sub>   |                 |      |  |

| Thermistors (Variant 01 only) | V <sub>th</sub>   |                 |      |  |

| Output Transistor Source Bias | V <sub>OS</sub>   | Note 1          | V    |  |

#### NOTES:

1. OS is connected to 0V via a  $3.6k\Omega$  resistor to give approximately 7mA in the CCD output transistor.

#### 2.8.2 <u>Electrical Measurements for Total Dose Radiation Testing</u>

Prior to irradiation the devices shall have successfully met Reference Temperature Electrical Measurements specified herein.

Unless otherwise stated the measurements shall be performed at  $T_{ref} \pm 3 \text{ }^{o}\text{C}$ . The test methods and test conditions shall be as per the corresponding test defined in Reference Temperature Electrical Measurements.

The parameters to be measured during and on completion of irradiation are shown below.

| Characteristics                | Symbols         | Limits |     | Units |

|--------------------------------|-----------------|--------|-----|-------|

|                                |                 | Min    | Max |       |

| Leakage Current on Input Gates | ١L              | -      | 10  | nA    |

| Power Supply Current 1         | I <sub>OD</sub> | -      | 10  | mA    |

| Power Supply Current 2         | I <sub>RD</sub> | -      | 100 | nA    |

| Characteristics                                         | Symbols             | Lin  | nits    | Units     |

|---------------------------------------------------------|---------------------|------|---------|-----------|

|                                                         |                     | Min  | Мах     |           |

| DC Output Voltage Level                                 | V <sub>REF</sub>    | Not  | te 2    | V         |

| Offset Voltage (Note 3)                                 | V <sub>OFFSET</sub> | -    | 25      | mV        |

| Charge to Voltage Conversion Factor (Note 3)            | CVF                 | 0.8  | 1.2     | μV/e      |

| Full Well Capacity (Image Section)                      | V <sub>SAT-IM</sub> | 300  | -       | ke        |

| Full Well Capacity (Readout Register)                   | V <sub>SAT-RE</sub> | 1200 | -       | ke        |

| Linearity Error (to 240ke/p)                            | LE                  | -    | 2       | %         |

| Average Dark Signal (Nominal V <sub>SS</sub> ) (Note 4) | DS <sub>AV</sub>    | -    | 150     | e/pixel/s |

| Dark Signal Non-uniformity (Note 3)                     | DSNU                | -    | 75      | e/pixel/s |

| Total Charge Transfer Inefficiency - Vertical           | VCTI                | -    | 2       | %         |

| Photo Response Defects<br>Pixels<br>Columns             | -                   | -    | 20<br>0 | -         |

| Defects in Darkness<br>Pixels<br>Columns<br>(Note 5)    | -                   | -    | 60<br>0 | -         |

#### NOTES:

- 1. The limits listed are valid for measurements during and on completion of irradiation and after annealing.

- 2. DC level is typically 4 to 6 Volts below V<sub>OD</sub>.

- 3.  $V_{OD}$ ,  $V_{RD}$  and  $V_{SS}$  bias voltages may require correction for irradiation induced threshold shift to perform these measurements.

- 4. Measurements may be performed at various V<sub>SS</sub> settings to determine the threshold voltage shift after irradiation.

- 5. Defect Threshold to be scaled with the increased limit for Dark Signal.

**ISSUE 1**

## APPENDIX A

#### AGREED DEVIATIONS FOR E2V TECHNOLOGIES

| ITEMS AFFECTED                        | DESCRIPTION OF DEVIATIONS                                                                                                                                                                                                                                                         |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviations from Production<br>Control | Wafer Lot Acceptance Total Dose Radiation Testing. The sample size defined in ESCC Basic Specification No. 22900 shall be replaced by a minimum sample of 4 test devices, selected at random from a minimum of two different diffusion lots making a minimum of 8 samples in all. |