Page i

# INTEGRATED CIRCUITS, SILICON MONOLITHIC, ADVANCED CMOS TRIPLE 3-INPUT AND GATES, BASED ON TYPE 54AC11

ESCC Detail Specification No. 9201/138

# ISSUE 1 October 2002

# **ESCC Detail Specification**

| PAGE  | ii |

|-------|----|

| ISSUE | 1  |

### **LEGAL DISCLAIMER AND COPYRIGHT**

European Space Agency, Copyright © 2002. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or allleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Ageny and provided that it is not used for a commercial purpose, may be:

- copied in whole in any medium without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

# european space agency agence spatiale européenne

Pages 1 to 42

# INTEGRATED CIRCUITS, SILICON MONOLITHIC, ADVANCED CMOS TRIPLE 3-INPUT AND GATES, BASED ON TYPE 54AC11

ESA/SCC Detail Specification No. 9201/138

# space components coordination group

|                 |                | Approved by   |                                    |  |

|-----------------|----------------|---------------|------------------------------------|--|

| Issue/Rev. Date |                | SCCG Chairman | ESA Director General or his Deputy |  |

| Issue 1         | September 1993 | Tomores       | t. tedu                            |  |

|                 |                |               |                                    |  |

PAGE 2

ISSUE 1

# **DOCUMENTATION CHANGE NOTICE**

|                | DOCUMENTATION CHANGE NOTICE |           |                |              |            |

|----------------|-----------------------------|-----------|----------------|--------------|------------|

| Rev.<br>Letter | Rev.<br>Date                | Reference | CHANGE<br>Item | Appro<br>DCR | ved<br>No. |

|                |                             |           |                |              | :          |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              | į          |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

|                |                             |           |                |              |            |

PAGE 3

ISSUE 1

# TABLE OF CONTENTS

| 1.           | GENERAL                                                                                   | <u>Page</u><br><b>5</b> |

|--------------|-------------------------------------------------------------------------------------------|-------------------------|

| 1.1          | Scope                                                                                     | 5                       |

| 1.2          | Component Type Variants                                                                   | 5                       |

| 1.3          | Maximum Ratings                                                                           | 5                       |

| 1.4          | Parameter Derating Information                                                            | 5                       |

| 1.5          | Physical Dimensions                                                                       | 5                       |

| 1.6          | Pin Assignment                                                                            | 5                       |

| 1.7          | Truth Table                                                                               | 5                       |

| 1.8          | Circuit Schematic                                                                         | 5                       |

| 1.9          | Functional Diagram                                                                        | 5                       |

| 1.10         | Handling Precautions                                                                      | 5                       |

| 1.11         | Input and Output Protection Networks                                                      | 5                       |

| 2.           | APPLICABLE DOCUMENTS                                                                      | 13                      |

| 3.           | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS                                      | 13                      |

| 4.           | REQUIREMENTS                                                                              | 13                      |

| 4.1          | General                                                                                   | 13                      |

| 4.2          | Deviations from Generic Specification                                                     | 13                      |

| 4.2.1        | Deviations from Special In-process Controls                                               | 13                      |

| 4.2.2        | Deviations from Final Production Tests                                                    | 13                      |

| 4.2.3        | Deviations from Burn-in Tests                                                             | 13                      |

| 4.2.4        | Deviations from Qualification Tests                                                       | 13                      |

| 4.2.5        | Deviations from Lot Acceptance Tests                                                      | 14                      |

| 4.3          | Mechanical Requirements                                                                   | 14                      |

| 4.3.1        | Dimension Check                                                                           | 14                      |

| 4.3.2        | Weight                                                                                    | 14                      |

| 4.4          | Materials and Finishes                                                                    | 14                      |

| 4.4.1        | Case                                                                                      | 14                      |

| 4.4.2        | Lead Material and Finish                                                                  | 14                      |

| 4.5          | Marking                                                                                   | 14                      |

| 4.5.1        | General                                                                                   | 14                      |

| 4.5.2        | Lead Identification                                                                       | 14                      |

| 4.5.3        | The SCC Component Number                                                                  | 15                      |

| 4.5.4        | Traceability Information                                                                  | 15                      |

| 4.6          | Electrical Measurements                                                                   | 15                      |

| 4.6.1        | Electrical Measurements at Room Temperature                                               | 15                      |

| 4.6.2        | Electrical Measurements at High and Low Temperatures Circuits for Electrical Measurements | 15<br>15                |

| 4.6.3<br>4.7 | Burn-in Tests                                                                             | 15                      |

| 4.7<br>4.7.1 | Parameter Drift Values                                                                    | 15                      |

| 4.7.1        | Conditions for H.T.R.B. and Power Burn-in                                                 | 15                      |

| 4.7.2        | Electrical Circuits for H.T.R.B. and Power Burn-in                                        | 15                      |

| 4.7.3        | Environmental and Endurance Tests                                                         | 39                      |

| 4.8.1        | Electrical Measurements on Completion of Environmental Tests                              | 39                      |

| 4.8.2        | Electrical Measurements at Intermediate Points during Endurance Tests                     | 39                      |

| 4.8.3        | Electrical Measurements on Completion of Endurance Tests                                  | 39                      |

| 4.8.4        | Conditions for Operating Life Tests                                                       | 39                      |

| 4.8.5        | Electrical Circuits for Operating Life Tests                                              | 39                      |

| 4.8.6        | Conditions for High Temperature Storage Test                                              | 39                      |

PAGE 4 ISSUE 1

| 4.9<br>4.9.1<br>4.9.2 | Total Dose Irradiation Testing Application Bias Conditions Electrical Measurements                                                                | <u>Page</u><br>39<br>39<br>39<br>39 |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 4.9.3                 |                                                                                                                                                   | 33                                  |

| TABLE                 | <u>:5</u>                                                                                                                                         |                                     |

| 1(a)                  | Type Variants                                                                                                                                     | 6                                   |

| 1(b)                  | Maximum Ratings                                                                                                                                   | 6                                   |

| 2                     | Electrical Measurements at Room Temperature - d.c. Parameters                                                                                     | 16                                  |

| 0(-)                  | Electrical Measurements at Room Temperature - a.c. Parameters                                                                                     | 20<br>22                            |

| 3(a)                  | Electrical Measurements at High Temperature                                                                                                       | 22<br>26                            |

| 3(b)<br>4             | Electrical Measurements at Low Temperature Parameter Drift Values                                                                                 | 34                                  |

| 4<br>5(a)             | Conditions for Burn-in High Temperature Reverse Bias, N-Channels                                                                                  | 35                                  |

| 5(b)                  | Conditions for Burn-in High Temperature Reverse Bias, P-Channels                                                                                  | 35                                  |

| 5(c)                  | Conditions for Power Burn-in and Operating Life Tests                                                                                             | 36                                  |

| 6                     | Electrical Measurements on Completion of Environmental Tests and                                                                                  | 40                                  |

|                       | at Intermediate Points and on Completion of Endurance Testing                                                                                     |                                     |

| 7                     | Electrical Measurements During and on Completion of Irradiation Testing                                                                           | 41                                  |

| FIGUR                 | <u>res</u>                                                                                                                                        |                                     |

| 1                     | Not applicable                                                                                                                                    |                                     |

| 2                     | Physical Dimensions                                                                                                                               | 7                                   |

| 3(a)                  | Pin Assignment                                                                                                                                    | 11                                  |

| 3(b)                  | Truth Table                                                                                                                                       | 11                                  |

| 3(c)                  | Circuit Schematic                                                                                                                                 | 12                                  |

| 3(d)                  | Functional Diagram                                                                                                                                | 12                                  |

| 3(e)                  | Input and Output Protection Networks                                                                                                              | 12                                  |

| 4                     | Circuits for Electrical Measurements                                                                                                              | 30<br>37                            |

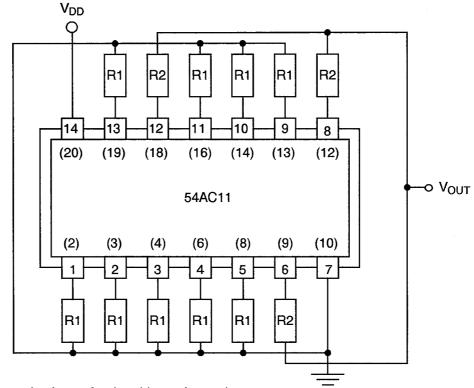

| 5(a)                  | Electrical Circuit for Burn-in High Temperature Reverse Bias, N-Channels Electrical Circuit for Burn-in High Temperature Reverse Bias, P-Channels | 37<br>37                            |

| 5(b)                  | Electrical Circuit for Power Burn-in and Operating Life Tests                                                                                     | 38                                  |

| 5(c)<br>6             | Bias Conditions for Irradiation Testing                                                                                                           | 41                                  |

|                       | TRIOTO (A sella la procific Manufacture e el )                                                                                                    |                                     |

| APPER<br>'A'          | NDICES (Applicable to specific Manufacturers only) AGREED DEVIATIONS FOR MOTOROLA (F)                                                             | 42                                  |

| А                     | AGREED DEVIATIONS FOR MOTOROLA (F)                                                                                                                | 42                                  |

PAGE

ISSUE 1

5

## 1. **GENERAL**

### 1.1 SCOPE

This specification details the ratings, physical and electrical characteristics, test and inspection data for a silicon, monolithic, advanced CMOS Triple 3-Input AND Gate, having fully buffered outputs, based on Type 54AC11. It shall be read in conjunction with ESA/SCC Generic Specification No. 9000, the requirements of which are supplemented herein.

### 1.2 COMPONENT TYPE VARIANTS

Variants of the basic type integrated circuits specified herein, which are also covered by this specification, are given in Table 1(a).

### 1.3 MAXIMUM RATINGS

The maximum ratings, which shall not be exceeded at any time during use or storage, applicable to the integrated circuits specified herein, are as scheduled in Table 1(b).

### 1.4 PARAMETER DERATING INFORMATION (FIGURE 1)

Not applicable.

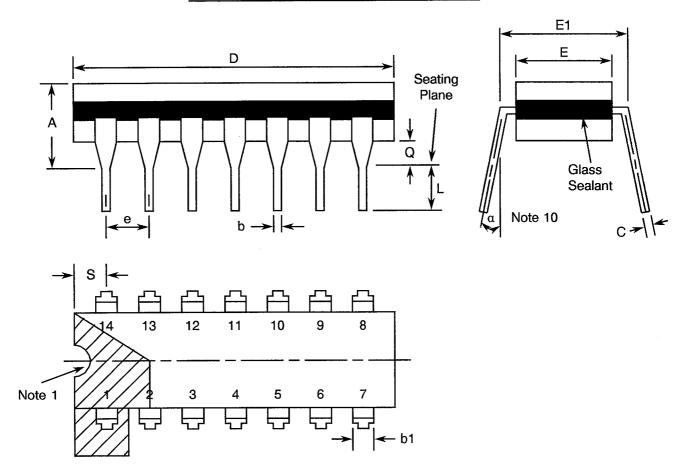

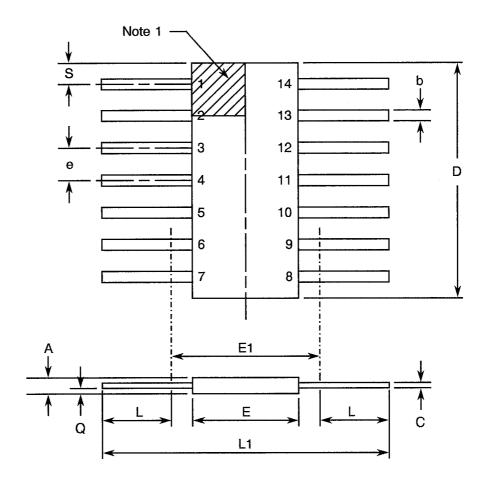

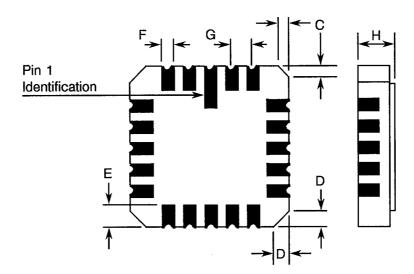

### 1.5 PHYSICAL DIMENSIONS

As per Figure 2.

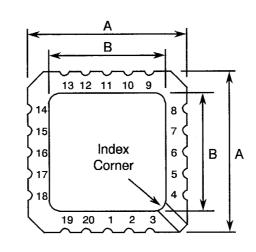

### 1.6 PIN ASSIGNMENT

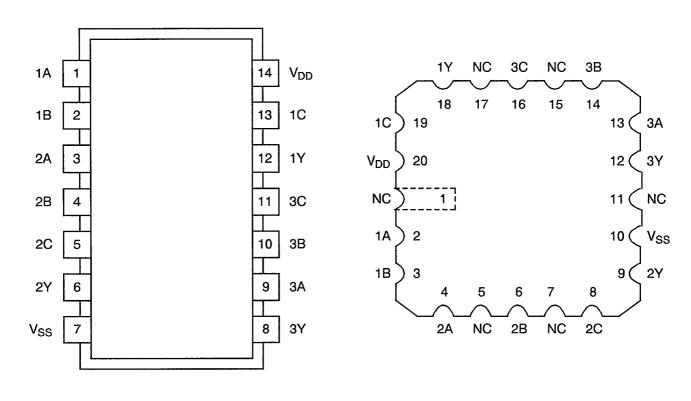

As per Figure 3(a).

### 1.7 TRUTH TABLE

As per Figure 3(b).

## 1.8 <u>CIRCUIT SCHEMATIC</u>

As per Figure 3(c).

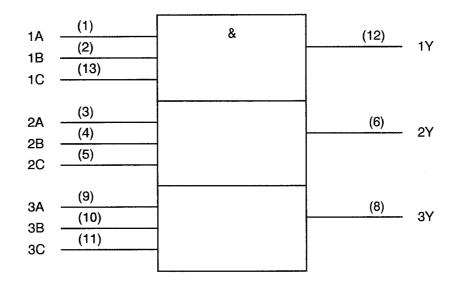

### 1.9 FUNCTIONAL DIAGRAM

As per Figure 3(d).

### 1.10 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are Categorised as Class 2 with a Minimum Critical Path Failure Voltage of 4000 Volts.

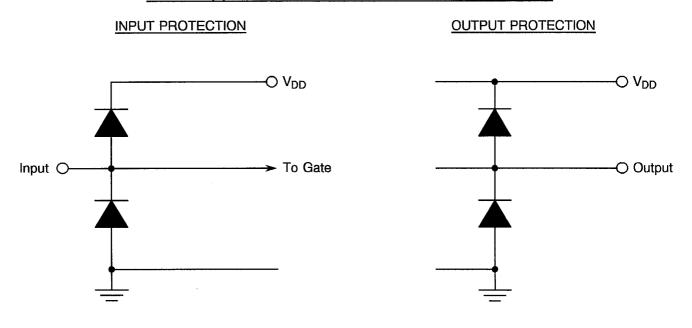

### 1.11 INPUT AND OUTPUT PROTECTION NETWORKS

Protection networks shall be incorporated into each input and output as shown in Figure 3(e).

PAGE 6

ISSUE 1

### **TABLE 1(a) - TYPE VARIANTS**

| VARIANT | CASE         | FIGURE | LEAD MATERIAL<br>AND/OR FINISH |

|---------|--------------|--------|--------------------------------|

| 01      | D.I.L.       | 2(a)   | G4                             |

| 02      | FLAT         | 2(b)   | G4                             |

| 03      | CHIP CARRIER | 2(c)   | 2                              |

| 04      | CHIP CARRIER | 2(c)   | 4                              |

### TABLE 1(b) - MAXIMUM RATINGS

| No. | CHARACTERISTICS                                    | SYMBOL            | MAXIMUM RATINGS               | UNITS | REMARKS          |

|-----|----------------------------------------------------|-------------------|-------------------------------|-------|------------------|

| 1   | Supply Voltage                                     | $V_{DD}$          | -0.5 to +6.0                  | V     | Note 1           |

| 2   | Input Voltage                                      | V <sub>IN</sub>   | -0.5 to V <sub>DD</sub> + 0.5 | ٧     | Notes 1, 2       |

| 3   | Output Voltage                                     | V <sub>OUT</sub>  | -0.5 to V <sub>DD</sub> +0.5  | V     | Notes 1, 3       |

| 4   | Device Dissipation (Continuous)                    | P <sub>D</sub>    | 396                           | mW    | Note 4           |

| 5   | Supply Current                                     | I <sub>DDop</sub> | 72                            | mA    |                  |

| 6   | Operating Temperature<br>Range                     | T <sub>op</sub>   | - 55 to +125                  | °C    | T <sub>amb</sub> |

| 7   | Storage Temperature<br>Range                       | T <sub>stg</sub>  | -65 to +150                   | °C    |                  |

| 8   | Soldering Temperature<br>For FP and DIP<br>For CCP | T <sub>sol</sub>  | + 265<br>+ 245                | °C    | Note 5<br>Note 6 |

### **NOTES**

- 1. Device is functional for 3.0V ≤ V<sub>DD</sub> ≤ 5.5V.

- 2. Input current limited to  $I_{IC}$  =  $\pm 20$ mA.

- 3. Output current limited to  $I_{OUT} = \pm 50 \text{mA}$ .

- 4. The maximum device dissipation is determined by I<sub>DDop</sub> max. (mA)×5.5V.

- 5. Duration 10 seconds maximum at a distance of not less than 1.5mm from the device body and the same lead shall not be resoldered until 3 minutes have elapsed.

- 6. Duration 5 seconds maximum and the same terminal shall not be resoldered until 3 minutes have elapsed.

### FIGURE 1 - PARAMETER DERATING INFORMATION

Not applicable.

PAGE 7

ISSUE 1

# FIGURE 2 - PHYSICAL DIMENSIONS

# FIGURE 2(a) - DUAL-IN-LINE PACKAGE, 14-PIN

| CVMDOL | MILLIM | NOTES        |       |

|--------|--------|--------------|-------|

| SYMBOL | MIN    | MAX          | NOTES |

| Α      | -      | 5.08         |       |

| b      | 0.35   | 0.56         | 8     |

| b1     | 1.40   | 1.77         | 8     |

| С      | 0.20   | 0.38         | 8     |

| D      | 19.05  | 19.94        | 4     |

| E      | 6.10   | 7.49         | 4     |

| E1     | 7.62 T | 7.62 TYPICAL |       |

| е      | 2.54 T | PICAL        | 6, 9  |

| L      | 3.10   | 4.31         | 8     |

| Q      | 0.25   | 1.02         | 3     |

| S      | 1.54   | 2.40         | 7     |

| α      | 0°     | 15°          | 10    |

PAGE 8

ISSUE 1

# FIGURE 2 - PHYSICAL DIMENSIONS (CONTINUED)

# FIGURE 2(b) - FLAT PACKAGE, 14-PIN

| SYMBOL   | MILLIMETRES  |        | NOTES |

|----------|--------------|--------|-------|

| STIVIBOL | MIN          | MAX    | NOTES |

| Α        | 1.52         | 2.16   |       |

| b        | 0.36         | 0.56   | 8     |

| С        | 0.08         | 0.17   | 8     |

| D        | 9.42         | 9.90   | 4     |

| E        | 5.84         | 7.24   |       |

| E1       | 7.00 TYPICAL |        | 4     |

| е        | 1.27 T       | /PICAL | 5, 9  |

| L        | 5.84         | 9.14   | 8     |

| L1       | 18.93        | 25.39  |       |

| Q        | -            | 1.02   | 2     |

| S        | -            | 1.40   | 7     |

PAGE

ISSUE 1

9

# FIGURE 2 - PHYSICAL DIMENSIONS (CONTINUED)

# FIGURE 2(c) - SQUARE CHIP CARRIER PACKAGE, 20-TERMINAL

| SYMBOL   | MILLIMETRES  |      | NOTES |

|----------|--------------|------|-------|

| STIVIDOL | MIN          | MAX  | NOTES |

| Α        | 8.69         | 9.09 |       |

| В        | 7.80         | 9.09 |       |

| С        | 0.25         | 0.51 | 11    |

| D        | 0.89         | 1.14 | 12    |

| E        | 1.14         | 1.40 | 8     |

| F.       | 0.56         | 0.71 | 8     |

| G        | 1.27 TYPICAL |      | 5, 9  |

| Н        | 1.63         | 2.54 |       |

PAGE 10

ISSUE

# FIGURE 2 - PHYSICAL DIMENSIONS (CONTINUED)

### NOTES TO FIGURES 2(a) TO 2(c) INCLUSIVE

- 1. Index area: a notch, letter or dot shall be located adjacent to Pin 1 and shall be within the shaded area shown. For chip carrier packages the index shall be as defined in Figure 2(c).

- 2. Dimension Q shall be measured at the point of exit of the lead from the body.

- 3. The dimension shall be measured from the seating plane to the base plane.

- 4. The dimension allows for off-centre lids, meniscus and glass overrun.

- 5. The true position pin or terminal spacing is 1.27mm between centrelines. Each pin or terminal centreline shall be located within ±0.13mm of it's true longitudinal position relative to Pin 1 and the highest pin number.

- 6. The true position pin spacing is 2.54mm between centrelines. Each pin centreline shall be located within ± 0.25mm of it's true longitudinal position relative to Pin 1 and the highest pin number.

- 7. Applies to all 4 corners.

- 8. All leads or terminals.

- 9. 12 spaces for flat and dual-in-line packages.

- 16 spaces for chip carrier packages.

- 10. Lead centreline when  $\alpha$  is 0°.

- 11. Index corner only 2 dimensions.

- 12. 3 non-index corners 6 dimensions.

PAGE 11

ISSUE 1

# FIGURE 3(a) - PIN ASSIGNMENT

### DUAL-IN-LINE AND FLAT PACKAGE

### CHIP CARRIER PACKAGE

**TOP VIEW**

**TOP VIEW**

### FLAT PACKAGE AND DUAL-IN-LINE TO CHIP CARRIER PIN ASSIGNMENT

FLAT PACKAGE AND **DUAL-IN-LINE PIN OUTS** 3 9 10 11 12 13 14 CHIP CARRIER PIN OUTS 2 3 4 6 8 9 10 12 13 14 16 18 19 20

### FIGURE 3(b) - TRUTH TABLE (EACH GATE)

| INPUTS      |                  |             | OUTPUT      |

|-------------|------------------|-------------|-------------|

| А           | В                | Y = A.B.C   |             |

| H<br>L<br>X | H<br>X<br>L<br>X | H<br>X<br>L | H<br>L<br>L |

# **NOTES**

1. Logic Level Definitions: L = Low Level, H = High Level, X = Irrelevant.

PAGE 12

ISSUE 1

# FIGURE 3(c) - CIRCUIT SCHEMATIC

Not applicable.

# FIGURE 3(d) - FUNCTIONAL DIAGRAM

# **NOTES**

1. Pin numbers shown are for DIP and FP.

# FIGURE 3(e) - INPUT AND OUTPUT PROTECTION NETWORKS

PAGE 13

ISSUE -

### 2. APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:-

- (a) ESA/SCC Generic Specification No. 9000 for Integrated Circuits.

- (b) MIL-STD-883, Test Methods and Procedures for Micro-electronics.

### 3. TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESA/SCC Basic Specification No. 21300 shall apply. In addition, the following symbols are used:

V<sub>IC</sub> = Input Clamp Voltage.

$I_{IC}$  = Input Clamp Diode Current.  $V_{OLP}$  = Ground Bounce Outputs Low.  $V_{OHV}$  = Ground Bounce Outputs High.

### 4. REQUIREMENTS

### 4.1 GENERAL

The complete requirements for procurement of the integrated circuits specified herein are stated in this specification and ESA/SCC Generic Specification No. 9000 for Integrated Circuits. Deviations from the Generic Specification, applicable to this specification only, are listed in Para. 4.2.

Deviations from the applicable Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESA/SCC requirements and do not affect the components' reliability, are listed in the appendices attached to this specification.

### 4.2 DEVIATIONS FROM GENERIC SPECIFICATION

### 4.2.1 Deviations from Special In-process Controls

- (a) Para. 5.2.2, Total Dose Irradiation Testing: Shall be performed during qualification and maintenance of qualification.

- (b) Para. 5.2.2, Total Dose Irradiation Testing: If specified in a Purchase Order, shall be performed during procurement on a lot acceptance basis at the total dose irradiation level specified in the Purchase Order.

### 4.2.2 <u>Deviations from Final Production Tests (Chart II)</u>

None.

### 4.2.3 Deviations from Burn-in Tests (Chart III)

None.

### 4.2.4 Deviations from Qualification Tests (Chart IV)

None.

PAGE 14

ISSUE 1

### 4.2.5 Deviations from Lot Acceptance Tests (Chart V)

None.

### 4.3 MECHANICAL REQUIREMENTS

### 4.3.1 Dimension Check

The dimensions of the integrated circuits specified herein shall be checked. They shall conform to those shown in Figure 2.

### 4.3.2 Weight

The maximum weight of the integrated circuits specified herein shall be 2.2 grammes for the dual-in-line package, 0.7 grammes for the flat package and 0.6 grammes for the chip carrier package.

### 4.4 MATERIALS AND FINISHES

The materials shall be as specified herein. Where a definite material is not specified, a material which will enable the integrated circuits specified herein to meet the performance requirements of this specification shall be used. Acceptance or approval of any constituent material does not quarantee acceptance of the finished product.

### 4.4.1 Case

The case shall be hermetically sealed and have a metal body with hard glass seals or a ceramic body and the lids shall be welded, brazed, preform-soldered or glass frit sealed.

### 4.4.2 Lead Material and Finish

For dual-in-line and flat packages, the material shall be Type 'G' with Type '4' finish in accordance with the requirements of ESA/SCC Basic Specification No. 23500. For chip carrier packages the finish shall be Type '2' or Type '4' in accordance with the requirements of ESA/SCC Basic Specification No. 23500. (See Table 1(a) for Type Variants).

### 4.5 MARKING

### 4.5.1 General

The marking of all components delivered to this specification shall be in accordance with the requirements of ESA/SCC Basic Specification No. 21700. Each component shall be marked in respect of:-

- (a) Lead Identification.

- (b) The SCC Component Number.

- (c) Traceability Information.

### 4.5.2 Lead Identification

For dual-in-line and flat packages, an index shall be located at the top of the package in the position defined in Note 1 to Figure 2 or, alternatively, a tab may be used to identify Pin No. 1. The pin numbering must be read with the index or tab on the left-hand side. For chip carrier packages, the index shall be as defined by Figure 2(c).

PAGE 15

ISSUE 1

### 4.5.3 The SCC Component Number

Each component shall bear the SCC Component Number which shall be constituted and marked as follows:

920113801BF

Detail Specification Number

Type Variant (see Table 1(a))

Testing Level (B or C, as applicable)

Total Dose Irradiation Level (if applicable)

The Total Dose Irradiation Level designation shall be added for those devices for which a sample has been successfully tested to the level in question. For these devices, a code letter shall be added in accordance with the requirements of ESA/SCC Basic Specification No. 22900.

### 4.5.4 Traceability Information

Each component shall be marked in respect of traceability information in accordance with the requirements of ESA/SCC Basic Specification No. 21700.

### 4.6 ELECTRICAL MEASUREMENTS

# 4.6.1 Electrical Measurements at Room Temperature

The parameters to be measured in respect of electrical characteristics are scheduled in Table 2. Unless otherwise specified, the measurements shall be performed at  $T_{amb} = +22 \pm 3$  °C.

### 4.6.2 Electrical Measurements at High and Low Temperatures

The parameters to be measured at high and low temperatures are scheduled in Table 3. The measurements shall be performed at  $T_{amb} = +125 (+0.5)$  °C and -55 (+5.0) °C respectively.

### 4.6.3 Circuits for Electrical Measurements

Circuits and test sequences for use in performing electrical measurements listed in Tables 2 and 3 of this specification are shown in Figure 4.

### 4.7 BURN-IN TESTS

### 4.7.1 Parameter Drift Values

The parameter drift values applicable to H.T.R.B. and Power Burn-in are specified in Table 4 of this specification. Unless otherwise stated, measurements shall be performed at  $T_{amb}$  = +22 ±3 °C. The parameter drift values ( $\Delta$ ) applicable to the parameters scheduled, shall not be exceeded. In addition to these drift value requirements, the appropriate limit value specified for a given parameter in Table 2 shall not be exceeded.

For H.T.R.B. Burn-in, the parameter drift values ( $\Delta$ ) shall be applied before the N-Channel (0 hours) and after the P-Channel (144 hours) burn-in.

### 4.7.2 Conditions for H.T.R.B. and Power Burn-in

The requirements for H.T.R.B. and Power Burn-in are specified in Section 7 of ESA/SCC Generic Specification No. 9000. The conditions for H.T.R.B. and Power Burn-in shall be as specified in Tables 5(a), 5(b) and 5(c) of this specification.

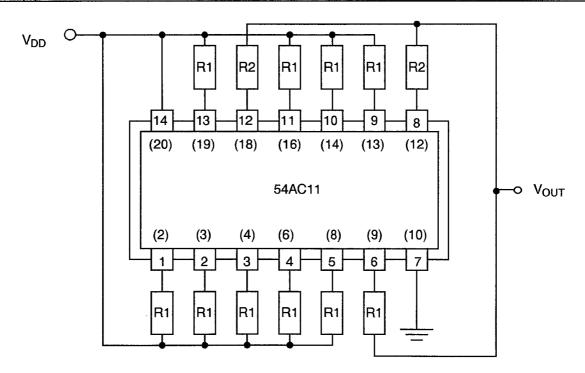

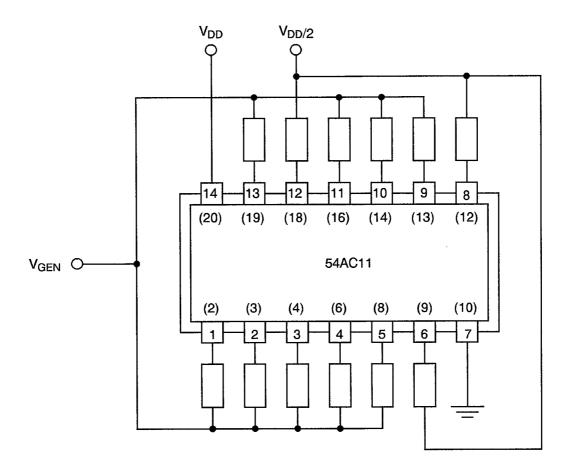

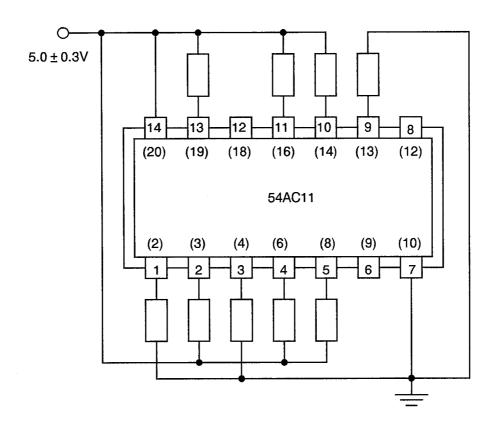

### 4.7.3 Electrical Circuits for H.T.R.B and Power Burn-in

Circuits for use in performing the H.T.R.B. and Power Burn-in tests are shown in Figures 5(a), 5(b) and 5(c) of this specification.

PAGE 16

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS

| No             | CHARACTERISTICS             | SYMBOL          | TEST<br>METHOD | TEST         | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                                         | LIM | IITS | UNIT |

|----------------|-----------------------------|-----------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| No.            | CHARACTERISTICS             | STIVIBUL        | MIL-STD<br>883 | FIG.         | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                                                | MIN | MAX  | UNIT |

| 1              | Functional Test 1           | •               | -              | 3(b)         | Verify Truth Table with Load. $V_{IL} = 0.45V, \ V_{IH} = 2.5V$ $I_{OL} = 1.0\text{mA}, \ I_{OH} = -1.0\text{mA}$ $V_{DD} = 3.0V, \ V_{SS} = 0V$ $t_r = t_f < 100\text{ns}$ $f = 10\text{kHz (min)}$ Note 1 | -   | •    | -    |

| 2              | Functional Test 2           | •               | -              | 3(b)         | Verify Truth Table with Load. $V_{IL} = 0.6V, V_{IH} = 3.7V$ $I_{OL} = 1.0mA, I_{OH} = -1.0mA$ $V_{DD} = 4.5V, V_{SS} = 0V$ $t_r = t_f < 50ns$ $f = 10kHz \ (min)$ Note 1                                   | 1   | •    | -    |

| 3              | Functional Test 3           | -               | -              | 3(b)         | Verify Truth Table with Load. $V_{IL} = 1.0V, V_{IH} = 4.5V$ $I_{OL} = 1.0mA, I_{OH} = -1.0mA$ $V_{DD} = 5.5V, V_{SS} = 0V$ $t_r = t_f < 50ns$ $f = 10kHz \ (min)$ Note 1                                   | -   | -    | -    |

| 4<br>to<br>7   | Quiescent Current           | l <sub>DD</sub> | 3005           | 4(a)         | $V_{IL}$ = 0V, $V_{IH}$ = 5.5V<br>$V_{DD}$ = 5.5V, $V_{SS}$ = 0V<br>All Outputs Open<br>Note 2<br>(Pin D/F 14)<br>(Pin C 20)                                                                                | -   | 0.5  | μА   |

| 8<br>to<br>16  | Input Current<br>Low Level  | I <sub>IL</sub> | 3009           | <b>4</b> (b) | $V_{IN}$ (Under Test) = 0V<br>$V_{IN}$ (Remaining Inputs) = 5.5V<br>$V_{DD}$ = 5.5V, $V_{SS}$ = 0V<br>(Pins D/F 1-2-3-4-5-9-10-11-13)<br>(Pins C 2-3-4-6-8-13-14-16-19)                                     | -   | -100 | nA   |

| 17<br>to<br>25 | Input Current<br>High Level | l <sub>IH</sub> | 3010           | 4(c)         | $V_{IN}$ (Under Test) = 5.5V<br>$V_{IN}$ (Remaining Inputs) = 0V<br>$V_{DD}$ = 5.5V, $V_{SS}$ = 0V<br>(Pins D/F 1-2-3-4-5-9-10-11-13)<br>(Pins C 2-3-4-6-8-13-14-16-19)                                     | -   | 100  | nA   |

PAGE 17

ISSUE 1

TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS (CONT'D)

| No.            | CHARACTERISTICS               | SYMBOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                     | LIM | ITS | UNIT  |

|----------------|-------------------------------|------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| NO.            | CHARACTERISTICS               | STIMBOL          | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                            | MIN | MAX | OIVIT |

| 26<br>to<br>28 | Output Voltage<br>Low Level 1 | V <sub>OL1</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 2.1V$ , $V_{IN2} = 0.9V$ , $I_{OL} = 50\mu$ A All Other Gates: $V_{IN} = 0V$ $V_{DD} = 3.0V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)   | •   | 0.1 | V     |

| 29<br>to<br>31 | Output Voltage<br>Low Level 2 | V <sub>OL2</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.15V$ , $V_{IN2} = 1.35V$ , $I_{OL} = 50\mu A$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18) | -   | 0.1 | V     |

| 32<br>to<br>34 | Output Voltage<br>Low Level 3 | V <sub>OL3</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V$ , $V_{IN2} = 1.65V$ , $I_{OL} = 50\mu$ A All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18) | -   | 0.1 | V     |

| 35<br>to<br>37 | Output Voltage<br>Low Level 4 | V <sub>OL4</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 2.1V$ , $V_{IN2} = 0.9V$ , $I_{OL} = 12mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 3.0V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)      | -   | 0.4 | V     |

| 38<br>to<br>40 | Output Voltage<br>Low Level 5 | V <sub>OL5</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.15V$ , $V_{IN2} = 1.35V$ , $I_{OL} = 24mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)    | -   | 0.4 | V     |

| 41<br>to<br>43 | Output Voltage<br>Low Level 6 | V <sub>OL6</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V$ , $V_{IN2} = 1.65V$ , $I_{OL} = 24mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)    | -   | 0.4 | V     |

PAGE 18

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS (CONT'D)

| No.            | CHARACTERISTICS                | SYMBOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                          | LIM | ITS      | UNIT  |

|----------------|--------------------------------|------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|

| NO.            | CHARACTERISTICS                | STWIBOL          | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                                 | MIN | MAX      | OINIT |

| 44<br>to<br>46 | Output Voltage<br>Low Level 7  | V <sub>OL7</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V$ , $V_{IN2} = 1.65V$ , $I_{OL} = 50$ mA All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ Note 3 (Pins D/F 6-8-12) (Pins C 9-12-18) | •   | 1.65     | >     |

| 47<br>to<br>49 | Output Voltage<br>High Level 1 | V <sub>OH1</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}=2.1V,\ I_{OH}=-50\mu A$ All Other Gates: $V_{IN}=0V$ $V_{DD}=3.0V,\ V_{SS}=0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                                   | 2.9 | 1        | >     |

| 50<br>to<br>52 | Output Voltage<br>High Level 2 | V <sub>OH2</sub> | 3006           | 4(e) | Gate Under Test:<br>$V_{IN}$ = 3.15V, $I_{OH}$ = $-50\mu$ A<br>All Other Gates: $V_{IN}$ = 0V<br>$V_{DD}$ = 4.5V, $V_{SS}$ = 0V<br>(Pins D/F 6-8-12)<br>(Pins C 9-12-18)                     | 4.4 | <u>.</u> | >     |

| 53<br>to<br>55 | Output Voltage<br>High Level 3 | V <sub>ОН3</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN} = 3.85V$ , $I_{OH} = -50\mu A$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                    | 5.4 | -        | V     |

| 56<br>to<br>58 | Output Voltage<br>High Level 4 | V <sub>OH4</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}$ = 2.1V, $I_{OH}$ = $-4.0$ mA All Other Gates: $V_{IN}$ = 0V $V_{DD}$ = 3.0V, $V_{SS}$ = 0V (Pins D/F 6-8-12) (Pins C 9-12-18)                                      | 2.4 | -        | >     |

| 59<br>to<br>61 | Output Voltage<br>High Level 5 | V <sub>OH5</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN} = 3.15V$ , $I_{OH} = -24mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                       | 3.7 | -        | V     |

PAGE 19

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS (CONT'D)

| No.            | CHARACTERISTICS                              | SYMBOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                     | LIM  | ITS   | UNIT |

|----------------|----------------------------------------------|------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|

| INO.           | CHARACTERISTICS                              | STIVIDOL         | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                            | MIN  | MAX   | UNIT |

| 62<br>to<br>64 | Output Voltage<br>High Level 6               | V <sub>OH6</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}$ = 3.85V, $I_{OH}$ = $-24$ mA All Other Gates: $V_{IN}$ = 0V $V_{DD}$ = 5.5V, $V_{SS}$ = 0V (Pins D/F 6-8-12) (Pins C 9-12-18)                 | 4.7  | -     | V    |

| 65<br>to<br>67 | Output Voltage<br>High Level 7               | V <sub>OH7</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}$ = 3.85V, $I_{OH}$ = $-50$ mA All Other Gates: $V_{IN}$ = 0V $V_{DD}$ = 5.5V, $V_{SS}$ = 0V Note 3 (Pins D/F 6-8-12) (Pins C 9-12-18)          | 3.85 | -     | V    |

| 68<br>to<br>76 | Input Clamp Voltage<br>(to V <sub>SS</sub> ) | V <sub>IC1</sub> | 3022           | 4(f) | $I_{IN}$ (Under Test) = $-1.0$ mA<br>$V_{DD}$ = Open, $V_{SS}$ = 0V<br>All Other Pins Open<br>(Pins D/F 1-2-3-4-5-9-10-11-<br>13)<br>(Pins C 2-3-4-6-8-13-14-16-<br>19) | -0.4 | - 1.5 | V    |

| 77<br>to<br>85 | Input Clamp Voltage<br>(to V <sub>DD</sub> ) | V <sub>IC2</sub> | 3022           | 4(f) | $I_{IN}$ (Under Test) = 1.0mA<br>$V_{DD}$ = 0V, $V_{SS}$ = Open<br>All Other Pins Open<br>(Pins D/F 1-2-3-4-5-9-10-11-<br>13)<br>(Pins C 2-3-4-6-8-13-14-16-<br>19)     | 0.4  | 1.5   | V    |

- 1. Maximum time to output comparator strobe 30µs.

- 2. Test each pattern of Figure 4(a).

- 3. No more than one output shall be measured at a time and the duration of the test shall not exceed 2.0ms.

- 4. Guaranteed but not tested.

- 5. Measurements shall be performed on a 100% basis go-no-go, with read and record on a sample basis, LTPD7 (32 pieces) after Chart III (Burn-in) Tests.

- 6. Hand test on 5 samples to be performed during Qualification and Extension of Qualification only.

PAGE 20

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - a.c. PARAMETERS

|                | OLIADA OTEDIOTIOS                              | CVMPOL                | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                                                                                                                                             | LIM | ITS | UNIT  |

|----------------|------------------------------------------------|-----------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| No.            | CHARACTERISTICS                                | SYMBOL                | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                                                                                                                                                    | MIN | MAX | OIVII |

| 86<br>to<br>94 | Input Capacitance                              | C <sub>IN</sub>       | 3012           | 4(g) | $V_{IN}$ (Not Under Test) = 0Vdc $V_{DD} = V_{SS} = 0V$ Note 4 (Pins D/F 1-2-3-4-5-9-10-11-13) (Pins C 2-3-4-6-8-13-14-16-19)                                                                                                                                                                                   | -   | 8.0 | pF    |

| 95             | Propagation Delay<br>Low to High<br>(1A to 1Y) | <sup>t</sup> PLH      | 3003           | 4(h) | Gate Under Test: $V_{IN2} = \text{Pulse Generator}$ $V_{IN1} = V_{IN3} = V_{DD}$ $V_{IN} \text{ (Remaining Inputs)} = 0V$ $V_{DD} = 4.5V, V_{SS} = 0V$ $Note 5$ $\frac{\text{Pins D/F}}{1 \text{ to } 12} \frac{\text{Pins C}}{2 \text{ to } 18}$                                                               | 1   | 8.0 | ns    |

| 96             | Propagation Delay<br>High to Low<br>(1A to 1Y) | t <sub>PHL</sub>      | 3003           | 4(h) | $\begin{aligned} &\text{Gate Under Test:} \\ &V_{IN2} = \text{Pulse Generator} \\ &V_{IN1} = V_{IN3} = V_{DD} \\ &V_{IN} \text{ (Remaining Inputs)} = 0V \\ &V_{DD} = 4.5V, \ V_{SS} = 0V \\ &\text{Note 5} \\ &\frac{\text{Pins D/F}}{1 \text{ to } 12} &\frac{\text{Pins C}}{2 \text{ to } 18} \end{aligned}$ | -   | 7.0 | ns    |

| 97             | Ground Bounce<br>Output Low<br>(High to Low)   | V <sub>OLP(H-L)</sub> | -              | 4(i) | $V_{IN}(1A, 1B, 1C) = 1.0V$<br>$V_{IN}$ (Remaining Inputs) =<br>Pulse Generator<br>$V_{DD} = 5.5V$ , $V_{SS} = 0V$<br>Note 6<br>(Pin D/F 12)<br>(Pin C 18)                                                                                                                                                      | -   | 1.5 | V     |

| 98             | Ground Bounce<br>Output Low<br>(Low to High)   | V <sub>OLP(L-H)</sub> | -              | 4(i) | $V_{IN}(1A, 1B, 1C) = 1.0V$<br>$V_{IN}$ (Remaining Inputs) =<br>Pulse Generator<br>$V_{DD} = 5.5V$ , $V_{SS} = 0V$<br>Note 6<br>(Pin D/F 12)<br>(Pin C 18)                                                                                                                                                      | -   | 1.5 | V     |

PAGE 21

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - a.c. PARAMETERS (CONT'D)

| No   | CHADACTEDISTICS                               | SYMBOL                | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                        | LIM | ITS | UNIT |

|------|-----------------------------------------------|-----------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| 140. | No. CHARACTERISTICS                           | STVIDOL               | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                               | MIN | MAX | ONIT |

| 99   | Ground Bounce<br>Output High<br>(High to Low) | V <sub>OHV(H-L)</sub> | •              | 4(i) | $V_{IN}(1A, 1B, 1C) = 4.0V$<br>$V_{IN}$ (Remaining Inputs) =<br>Pulse Generator<br>$V_{DD} = 5.5V$ , $V_{SS} = 0V$<br>Note 6<br>(Pin D/F 12)<br>(Pin C 18) | -   | 1.5 | V    |

| 100  | Ground Bounce<br>Output High<br>(Low to High) | V <sub>OHV(L-H)</sub> | -              | 4(i) | $V_{IN}(1A, 1B, 1C) = 4.0V$<br>$V_{IN}$ (Remaining Inputs) =<br>Pulse Generator<br>$V_{DD} = 5.5V$ , $V_{SS} = 0V$<br>Note 6<br>(Pin D/F 12)<br>(Pin C 18) | -   | 1.5 | V    |

PAGE 22

ISSUE 1

# TABLE 3(a) - ELECTRICAL MEASUREMENTS AT HIGH TEMPERATURE

| No.            | CHARACTERISTICS             | SYMBOL          | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                                         | LIM | ITS   | UNIT  |

|----------------|-----------------------------|-----------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|

| NO.            | CHARACTERISTICS             | STIVIBOL        | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                                                | MIN | MAX   | CIVIT |

| 1              | Functional Test 1           | -               | -              | 3(b) | Verify Truth Table with Load. $V_{IL} = 0.45V, \ V_{IH} = 2.5V$ $I_{OL} = 1.0\text{mA}, \ I_{OH} = -1.0\text{mA}$ $V_{DD} = 3.0V, \ V_{SS} = 0V$ $t_r = t_f < 100\text{ns}$ $f = 10\text{kHz (min)}$ Note 1 | -   | 1     | -     |

| 2              | Functional Test 2           | -               | -              | 3(b) | Verify Truth Table with Load. $V_{IL} = 0.6V, V_{IH} = 3.7V$ $I_{OL} = 1.0\text{mA}, I_{OH} = -1.0\text{mA}$ $V_{DD} = 4.5V, V_{SS} = 0V$ $t_r = t_f < 50\text{ns}$ $f = 10\text{kHz (min)}$ Note 1         | •   | •     | -     |

| 3              | Functional Test 3           | -               | -              | 3(b) | Verify Truth Table with Load. $V_{IL} = 1.0V, \ V_{IH} = 4.5V$ $I_{OL} = 1.0mA, \ I_{OH} = -1.0mA$ $V_{DD} = 5.5V, \ V_{SS} = 0V$ $t_r = t_f < 50ns$ $f = 10kHz \ (min)$ Note 1                             | •   | -     | •     |

| 4<br>to<br>7   | Quiescent Current           | I <sub>DD</sub> | 3005           | 4(a) | $V_{IL}$ = 0V, $V_{IH}$ = 5.5V<br>$V_{DD}$ = 5.5V, $V_{SS}$ = 0V<br>All Outputs Open<br>Note 2<br>(Pin D/F 14)<br>(Pin C 20)                                                                                | -   | 10    | μА    |

| 8<br>to<br>16  | Input Current<br>Low Level  | lιL             | 3009           | 4(b) | $V_{IN}$ (Under Test) = 0V<br>$V_{IN}$ (Remaining Inputs) = 5.5V<br>$V_{DD}$ = 5.5V, $V_{SS}$ = 0V<br>(Pins D/F 1-2-3-4-5-9-10-11-13)<br>(Pins C 2-3-4-6-8-13-14-16-19)                                     | -   | - 1.0 | μA    |

| 17<br>to<br>25 | Input Current<br>High Level | lH              | 3010           | 4(c) | $V_{IN}$ (Under Test) = 5.5V<br>$V_{IN}$ (Remaining Inputs) = 0V<br>$V_{DD}$ = 5.5V, $V_{SS}$ = 0V<br>(Pins D/F 1-2-3-4-5-9-10-11-13)<br>(Pins C 2-3-4-6-8-13-14-16-19)                                     | -   | 1.0   | μΑ    |

PAGE 23

ISSUE 1

# TABLE 3(a) - ELECTRICAL MEASUREMENTS AT HIGH TEMPERATURE (CONT'D)

| Na             | OLIADA OTEDICTIOS             | CVMDOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                     | LIM | ITS | UNIT |

|----------------|-------------------------------|------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| No.            | CHARACTERISTICS               | SYMBOL           | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                            | MIN | MAX | UNIT |

| 26<br>to<br>28 | Output Voltage<br>Low Level 1 | V <sub>OL1</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 2.1V$ , $V_{IN2} = 0.9V$ , $I_{OL} = 50\mu A$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 3.0V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)   | -   | 0.1 | V    |

| 29<br>to<br>31 | Output Voltage<br>Low Level 2 | V <sub>OL2</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.15V$ , $V_{IN2} = 1.35V$ , $I_{OL} = 50\mu$ A All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18) | -   | 0.1 | ٧    |

| 32<br>to<br>34 | Output Voltage<br>Low Level 3 | V <sub>OL3</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V$ , $V_{IN2} = 1.65V$ , $I_{OL} = 50\mu$ A All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18) | -   | 0.1 | ٧    |

| 35<br>to<br>37 | Output Voltage<br>Low Level 4 | V <sub>OL4</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 2.1V$ , $V_{IN2} = 0.9V$ , $I_{OL} = 12mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 3.0V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)      |     | 0.5 | ٧    |

| 38<br>to<br>40 | Output Voltage<br>Low Level 5 | V <sub>OL5</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.15V$ , $V_{IN2} = 1.35V$ , $I_{OL} = 24mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)    | -   | 0.5 | ٧    |

| 41<br>to<br>43 | Output Voltage<br>Low Level 6 | V <sub>OL6</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V$ , $V_{IN2} = 1.65V$ , $I_{OL} = 24mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)    | -   | 0.5 | V    |

PAGE 24

ISSUE 1

# TABLE 3(a) - ELECTRICAL MEASUREMENTS AT HIGH TEMPERATURE (CONT'D)

|                |                                |                  | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                          | LIM | ITS      |      |

|----------------|--------------------------------|------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------|

| No.            | CHARACTERISTICS                | SYMBOL           | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                                 | MIN | MAX      | UNIT |

| 44<br>to<br>46 | Output Voltage<br>Low Level 7  | V <sub>OL7</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V$ , $V_{IN2} = 1.65V$ , $I_{OL} = 50$ mA All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ Note 3 (Pins D/F 6-8-12) (Pins C 9-12-18) | -   | 1.65     | V    |

| 47<br>to<br>49 | Output Voltage<br>High Level 1 | V <sub>OH1</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}=2.1V,\ I_{OH}=-50\mu\text{A}$ All Other Gates: $V_{IN}=0V$ $V_{DD}=3.0V,\ V_{SS}=0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                             | 2.9 | ı        | V    |

| 50<br>to<br>52 | Output Voltage<br>High Level 2 | V <sub>OH2</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN} = 3.15V$ , $I_{OH} = -50\mu A$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                    | 4.4 | <b>-</b> | V    |

| 53<br>to<br>55 | Output Voltage<br>High Level 3 | V <sub>OH3</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN} = 3.85V$ , $I_{OH} = -50\mu A$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                    | 5.4 | 1        | V    |

| 56<br>to<br>58 | Output Voltage<br>High Level 4 | V <sub>OH4</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN} = 2.1V, \ I_{OH} = -4.0 \text{mA}$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 3.0V, \ V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                 | 2.4 | -        | V    |

| 59<br>to<br>61 | Output Voltage<br>High Level 5 | V <sub>OH5</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN} = 3.15V$ , $I_{OH} = -24mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                       | 3.7 | -        | V    |

PAGE 25

ISSUE 1

# TABLE 3(a) - ELECTRICAL MEASUREMENTS AT HIGH TEMPERATURE (CONT'D)

| N.             | OLIADA OTEDIOTIOS                            | CVMPOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                     | LIM  | ITS  | UNIT |

|----------------|----------------------------------------------|------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| No.            | CHARACTERISTICS                              | SYMBOL           | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                            | MIN  | MAX  | UNIT |

| 62<br>to<br>64 | Output Voltage<br>High Level 6               | V <sub>OH6</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}$ = 3.85V, $I_{OH}$ = $-24$ mA All Other Gates: $V_{IN}$ = 0V $V_{DD}$ = 5.5V, $V_{SS}$ = 0V (Pins D/F 6-8-12) (Pins C 9-12-18)                 | 4.7  | -    | V    |

| 65<br>to<br>67 | Output Voltage<br>High Level 7               | V <sub>OH7</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}=3.85V,\ I_{OH}=-50mA$ All Other Gates: $V_{IN}=0V$ $V_{DD}=5.5V,\ V_{SS}=0V$ Note 3 (Pins D/F 6-8-12) (Pins C 9-12-18)                         | 3.85 | -    | V    |

| 68<br>to<br>76 | Input Clamp Voltage<br>(to V <sub>SS</sub> ) | V <sub>IC1</sub> | 3022           | 4(f) | $I_{IN}$ (Under Test) = $-1.0$ mA<br>$V_{DD}$ = Open, $V_{SS}$ = 0V<br>All Other Pins Open<br>(Pins D/F 1-2-3-4-5-9-10-11-<br>13)<br>(Pins C 2-3-4-6-8-13-14-16-<br>19) | -0.1 | -1.5 | V    |

| 77<br>to<br>85 | Input Clamp Voltage<br>(to V <sub>DD</sub> ) | V <sub>IC2</sub> | 3022           | 4(f) | $I_{IN}$ (Under Test) = 1.0mA<br>$V_{DD}$ = 0V, $V_{SS}$ = Open<br>All Other Pins Open<br>(Pins D/F 1-2-3-4-5-9-10-11-<br>13)<br>(Pins C 2-3-4-6-8-13-14-16-<br>19)     | 0.1  | 1.5  | V    |

PAGE 26

ISSUE 1

# TABLE 3(b) - ELECTRICAL MEASUREMENTS AT LOW TEMPERATURE

| No             | CHARACTERISTICS             | SYMBOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                                                                    | LIM | IITS | UNIT |

|----------------|-----------------------------|------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| No.            | CHARACTERISTICS             | STMBOL           | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                                                                           | MIN | MAX  | UNIT |

| 1              | Functional Test 1           | -                | -              | 3(b) | Verify Truth Table with Load. $V_{IL}=0.45V,\ V_{IH}=2.5V$ $I_{OL}=1.0\text{mA},\ I_{OH}=-1.0\text{mA}$ $V_{DD}=3.0V,\ V_{SS}=0V$ $t_r=t_f<100\text{ns}$ $f=10\text{kHz}\ (\text{min})$ Note 1                                         | 1   | -    | -    |

| 2              | Functional Test 2           | -                | -              | 3(b) | Verify Truth Table with Load. $V_{IL} = 0.6V, \ V_{IH} = 3.7V$ $I_{OL} = 1.0\text{mA}, \ I_{OH} = -1.0\text{mA}$ $V_{DD} = 4.5V, \ V_{SS} = 0V$ $t_r = t_f < 50\text{ns}$ $f = 10\text{kHz (min)}$ Note 1                              | •   | -    | -    |

| ß              | Functional Test 3           | -                | -              | 3(b) | Verify Truth Table with Load. $V_{IL}=1.0V,\ V_{IH}=4.5V$ $I_{OL}=1.0\text{mA},\ I_{OH}=-1.0\text{mA}$ $V_{DD}=5.5V,\ V_{SS}=0V$ $t_r=t_f<50\text{ns}$ $f=10\text{kHz}\ (\text{min})$ Note 1                                           |     | -    | -    |

| 4<br>to<br>7   | Quiescent Current           | I <sub>DD</sub>  | 3005           | 4(a) | $V_{IL}$ = 0V, $V_{IH}$ = 5.5V<br>$V_{DD}$ = 5.5V, $V_{SS}$ = 0V<br>All Outputs Open<br>Note 2<br>(Pin D/F 14)<br>(Pin C 20)                                                                                                           | -   | 0.5  | μА   |

| 8<br>to<br>16  | Input Current<br>Low Level  | I <sub>IL</sub>  | 3009           | 4(b) | $\begin{split} &V_{IN} \text{ (Under Test)} = 0V \\ &V_{IN} \text{ (Remaining Inputs)} = 5.5V \\ &V_{DD} = 5.5V, \ V_{SS} = 0V \\ &\text{(Pins D/F 1-2-3-4-5-9-10-11-13)} \\ &\text{(Pins C 2-3-4-6-8-13-14-16-19)} \end{split}$       | •   | -100 | nA   |

| 17<br>to<br>25 | Input Current<br>High Level | l <sub>і</sub> н | 3010           | 4(c) | $V_{IN} \; (\text{Under Test}) = 5.5 \text{V} \\ V_{IN} \; (\text{Remaining Inputs}) = 0 \text{V} \\ V_{DD} = 5.5 \text{V}, \; V_{SS} = 0 \text{V} \\ (\text{Pins D/F 1-2-3-4-5-9-10-11-13}) \\ (\text{Pins C 2-3-4-6-8-13-14-16-19})$ | -   | 100  | nA   |

PAGE 27

ISSUE 1

# TABLE 3(b) - ELECTRICAL MEASUREMENTS AT LOW TEMPERATURE (CONT'D)

| No.            | CHARACTERISTICS               | SYMBOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                     | LIM | ITS | UNIT |

|----------------|-------------------------------|------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| NO.            | CHARACTERISTICS               | STIVIBUL         | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                            | MIN | MAX | ONIT |

| 26<br>to<br>28 | Output Voltage<br>Low Level 1 | V <sub>OL1</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 2.1V$ , $V_{IN2} = 0.9V$ , $I_{OL} = 50\mu$ A All Other Gates: $V_{IN} = 0V$ $V_{DD} = 3.0V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)   | -   | 0.1 | V    |

| 29<br>to<br>31 | Output Voltage<br>Low Level 2 | V <sub>OL2</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.15V$ , $V_{IN2} = 1.35V$ , $I_{OL} = 50\mu A$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18) | •   | 0.1 | V    |

| 32<br>to<br>34 | Output Voltage<br>Low Level 3 | V <sub>OL3</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V$ , $V_{IN2} = 1.65V$ , $I_{OL} = 50\mu$ A All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18) | -   | 0.1 | V    |

| 35<br>to<br>37 | Output Voltage<br>Low Level 4 | V <sub>OL4</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 2.1V$ , $V_{IN2} = 0.9V$ , $I_{OL} = 12mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 3.0V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)      | •   | 0.4 | V    |

| 38<br>to<br>40 | Output Voltage<br>Low Level 5 | V <sub>OL5</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.15V$ , $V_{IN2} = 1.35V$ , $I_{OL} = 24mA$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)    | •   | 0.4 | V    |

| 41<br>to<br>43 | Output Voltage<br>Low Level 6 | V <sub>OL6</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V,$ $V_{IN2} = 1.65V, I_{OL} = 24\text{mA}$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V, V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)    | -   | 0.4 | V    |

PAGE 28

ISSUE 1

# TABLE 3(b) - ELECTRICAL MEASUREMENTS AT LOW TEMPERATURE (CONT'D)

| No.            | CHARACTERISTICS                | SYMBOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                                          | LIM | ITS  | UNIT     |

|----------------|--------------------------------|------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----------|

| INO.           | CHARACTERISTICS                | STIVIBOL         | MIL-STD<br>883 | FIG. | D/F = DIP AND FP<br>C = CCP)                                                                                                                                                                 | MIN | MAX  | UNIT     |

| 44<br>to<br>46 | Output Voltage<br>Low Level 7  | V <sub>OL7</sub> | 3007           | 4(d) | Gate Under Test: $V_{IN1} = V_{IN3} = 3.85V$ , $V_{IN2} = 1.65V$ , $I_{OL} = 50$ mA All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ Note 3 (Pins D/F 6-8-12) (Pins C 9-12-18) | •   | 1.65 | V        |

| 47<br>to<br>49 | Output Voltage<br>High Level 1 | V <sub>OH1</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}=2.1V,\ I_{OH}=-50\mu A$ All Other Gates: $V_{IN}=0V$ $V_{DD}=3.0V,\ V_{SS}=0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                                   | 2.9 | -    | V        |

| 50<br>to<br>52 | Output Voltage<br>High Level 2 | V <sub>OH2</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN} = 3.15V$ , $I_{OH} = -50\mu A$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                    | 4.4 | -    | <b>V</b> |

| 53<br>to<br>55 | Output Voltage<br>High Level 3 | V <sub>ОН3</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN} = 3.85V$ , $I_{OH} = -50\mu A$ All Other Gates: $V_{IN} = 0V$ $V_{DD} = 5.5V$ , $V_{SS} = 0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                    | 5.4 | •    | V        |

| 56<br>to<br>58 | Output Voltage<br>High Level 4 | V <sub>OH4</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}$ = 2.1V, $I_{OH}$ = $-4.0$ mA All Other Gates: $V_{IN}$ = 0V $V_{DD}$ = 3.0V, $V_{SS}$ = 0V (Pins D/F 6-8-12) (Pins C 9-12-18)                                      | 2.4 | -    | V        |

| 59<br>to<br>61 | Output Voltage<br>High Level 5 | V <sub>OH5</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}$ = 3.15V, $I_{OH}$ = $-$ 24mA All Other Gates: $V_{IN}$ = 0V $V_{DD}$ = 4.5V, $V_{SS}$ = 0V (Pins D/F 6-8-12) (Pins C 9-12-18)                                      | 3.7 | -    | <b>V</b> |

PAGE 29

ISSUE 1

# TABLE 3(b) - ELECTRICAL MEASUREMENTS AT LOW TEMPERATURE (CONT'D)

| No.            | CHARACTERISTICS                              | SYMBOL           | TEST<br>METHOD | TEST | TEST CONDITIONS<br>(PINS UNDER TEST                                                                                                                                     | LIMITS |       | UNIT |

|----------------|----------------------------------------------|------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------|

| IVO.           | CHARACTERISTICS                              | STVIBOL          | MIL-STD<br>883 | 1 1  |                                                                                                                                                                         | MIN    | MAX   |      |

| 62<br>to<br>64 | Output Voltage<br>High Level 6               | V <sub>OH6</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}=3.85V,\ I_{OH}=-24mA$ All Other Gates: $V_{IN}=0V$ $V_{DD}=5.5V,\ V_{SS}=0V$ (Pins D/F 6-8-12) (Pins C 9-12-18)                                | 4.7    | 1     | V    |

| 65<br>to<br>67 | Output Voltage<br>High Level 7               | V <sub>OH7</sub> | 3006           | 4(e) | Gate Under Test: $V_{IN}=3.85V,\ I_{OH}=-50\text{mA}$ All Other Gates: $V_{IN}=0V$ $V_{DD}=5.5V,\ V_{SS}=0V$ Note 3 (Pins D/F 6-8-12) (Pins C 9-12-18)                  | 3.85   | -     | V    |

| 68<br>to<br>76 | Input Clamp Voltage<br>(to V <sub>SS</sub> ) | V <sub>IC1</sub> | 3022           | 4(f) | $I_{IN}$ (Under Test) = $-1.0$ mA<br>$V_{DD}$ = Open, $V_{SS}$ = 0V<br>All Other Pins Open<br>(Pins D/F 1-2-3-4-5-9-10-11-<br>13)<br>(Pins C 2-3-4-6-8-13-14-16-<br>19) | - 0.1  | - 1.5 | V    |

| 77<br>to<br>85 | Input Clamp Voltage<br>(to V <sub>DD</sub> ) | V <sub>IC2</sub> | 3022           | 4(f) | $I_{IN}$ (Under Test) = 1.0mA<br>$V_{DD}$ = 0V, $V_{SS}$ = Open<br>All Other Pins Open<br>(Pins D/F 1-2-3-4-5-9-10-11-<br>13)<br>(Pins C 2-3-4-6-8-13-14-16-<br>19)     | 0.1    | 1.5   | V    |

PAGE 30

ISSUE 1

# FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS

### FIGURE 4(a) - QUIESCENT CURRENT TEST TABLE

|                | INPUTS |   |        |        |        |         |          |          | OUTPUTS  |        | PACKAGE | D.C. SUPPLY |                |                 |          |

|----------------|--------|---|--------|--------|--------|---------|----------|----------|----------|--------|---------|-------------|----------------|-----------------|----------|

| PATTERN<br>NO. | 1 2    | 2 | 3<br>4 | 4<br>6 | 5<br>8 | 9<br>13 | 10<br>14 | 11<br>16 | 13<br>19 | 6<br>9 | 8<br>12 | 12<br>18    | DIL, FP<br>CCP | 7<br>10         | 14<br>20 |

| 1              | 1      | 1 | 1      | 1      | 1      | 1       | 1        | 1        | 1        |        | OPEN    | 1           |                | V <sub>SS</sub> | $V_{DD}$ |

| 2              | 1      | 0 | 1      | 0      | 0      | 1       | 0        | 0        | 0        |        | OPEN    | ١           | :              |                 |          |

| 3              | 0      | 1 | 0      | 1      | 0      | 0       | 1        | 0        | 0        |        | OPE     | N           |                |                 |          |

| 4              | 0      | 0 | 0      | 0      | 1      | 0       | 0        | 1        | 1        |        | OPE     | ١           |                | <b>V</b>        | . ↓      |

#### NOTES

- 1. Figure 4(a) illustrates one series of test patterns. Any other pattern series must be agreed with the Qualifying Space Agency and shall be included as an Appendix.

- 2. Logic Level Definitions:  $1 = V_{IH} = V_{DD}$ ,  $0 = V_{IL} = V_{SS}$ .

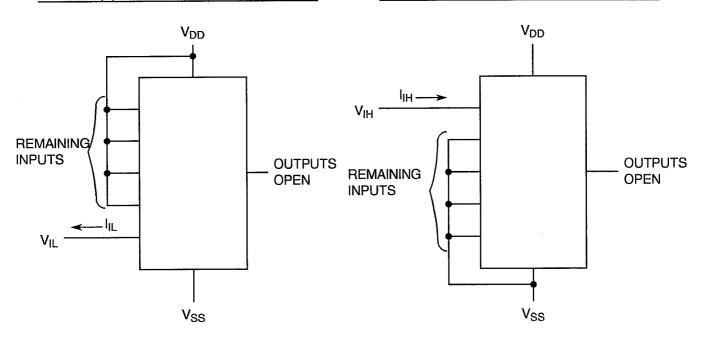

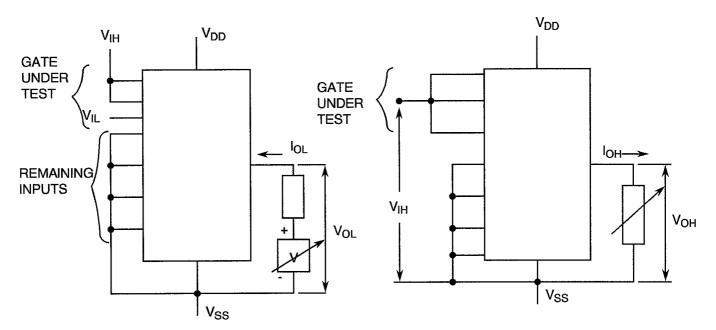

# FIGURE 4(b) - INPUT CURRENT LOW LEVEL

# FIGURE 4(c) - INPUT CURRENT HIGH LEVEL

### **NOTES**

1. Each input to be tested separately.

### **NOTES**

1. Each input to be tested separately.

PAGE 31

ISSUE 1

# FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS (CONTINUED)

# FIGURE 4(d) - OUTPUT VOLTAGE LOW LEVEL

# FIGURE 4(e) - OUTPUT VOLTAGE HIGH LEVEL

### **NOTES**

1. Each output to be tested separately.

### **NOTES**

1. Each output to be tested separately.

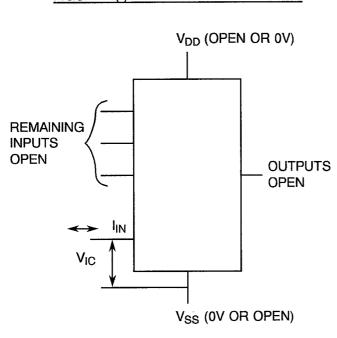

# FIGURE 4(f) - INPUT CLAMP VOLTAGE

# FIGURE 4(g) - INPUT CAPACITANCE

# **NOTES**

1. Each input to be tested separately.

- 1. Each input to be tested separately.

- 2. f = 100kHz to 1MHz.

PAGE 32

ISSUE 1

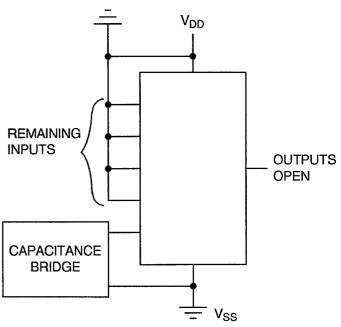

# FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS (CONTINUED)

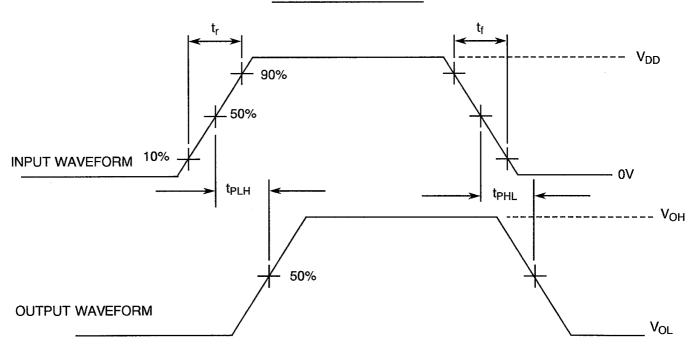

# FIGURE 4(h) - PROPAGATION DELAY

### **VOLTAGE WAVEFORMS**

- 1. Pulse Generator  $V_P = 0V$  to  $V_{DD}$ ,  $t_r$  and  $t_f \le 6$ ns,  $t_r = 1.0$ MHz minimum, 50% Duty Cycle,  $t_r = 50$ Ω.

- 2.  $C_L$  = 50pF ± 5% including scope, wiring and stray capacitance without package in test fixture,  $R_L$  = 500 $\Omega$  ± 5%.

PAGE 33

ISSUE 1

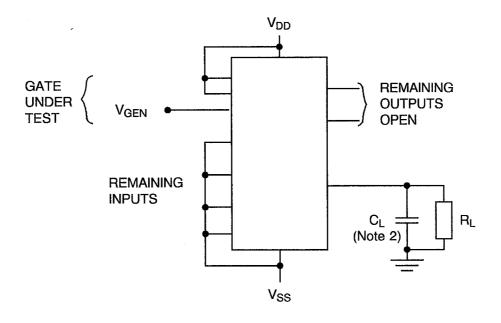

# FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS (CONTINUED)

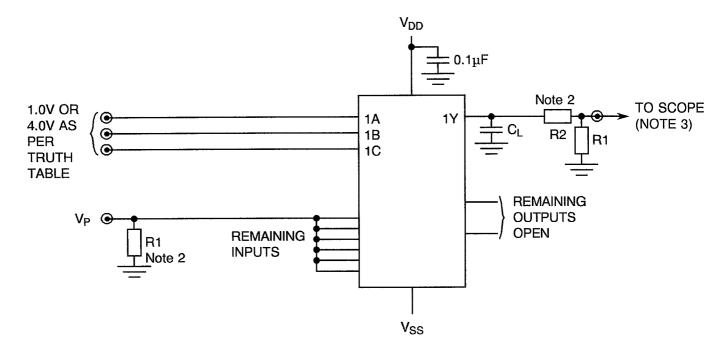

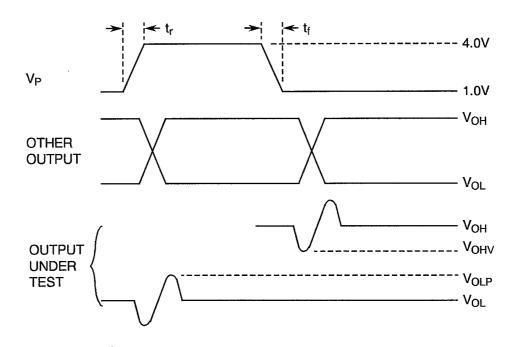

## FIGURE 4(i) - GROUND BOUNCE

# **VOLTAGE WAVEFORMS**

- 1. Pulse Generator  $V_P = 1.0V$  to 4.0V,  $t_r$  and  $t_f \le 6.0$ ns,  $t_r = 1.0$ MHz, 50% Duty Cycle,  $t_r = 50$ Ω.

- 2.  $C_L = 50pF \pm 5\%$ ,  $R1 = 51\Omega \pm 5\%$ ,  $R2 = 450\Omega \pm 5\%$ .

- 3. Oscilloscope  $Z_{IN} = 50\Omega$ , Bandwidth  $\ge 1.0 GHz$  with memory capability.

PAGE 34

ISSUE 1

# **TABLE 4 - PARAMETER DRIFT VALUES**

| No.            | CHARACTERISTICS                | SYMBOL           | SPEC. AND/OR<br>TEST METHOD | TEST CONDITIONS | CHANGE<br>LIMITS<br>(Δ) | UNIT |

|----------------|--------------------------------|------------------|-----------------------------|-----------------|-------------------------|------|

| 4<br>to<br>7   | Quiescent Current              | I <sub>DD</sub>  | As per Table 2              | As per Table 2  | ± 150                   | nA   |

| 8<br>to<br>16  | Input Current<br>Low Level     | Ŀ                | As per Table 2              | As per Table 2  | ±20                     | nA   |

| 17<br>to<br>25 | Input Current<br>High Level    | IH               | As per Table 2              | As per Table 2  | ±20                     | nA   |

| 41<br>to<br>43 | Output Voltage<br>Low Level 6  | V <sub>OL6</sub> | As per Table 2              | As per Table 2  | ±0.04                   | V    |

| 62<br>to<br>64 | Output Voltage<br>High Level 6 | V <sub>OH6</sub> | As per Table 2              | As per Table 2  | ± 0.2                   | ٧    |

PAGE 35

ISSUE 1

# TABLE 5(a) - CONDITIONS FOR BURN-IN HIGH TEMPERATURE REVERSE BIAS, N-CHANNELS

| No. | CHARACTERISTICS                                                            | SYMBOL           | CONDITION     | UNIT  |

|-----|----------------------------------------------------------------------------|------------------|---------------|-------|

| 1   | Ambient Temperature                                                        | T <sub>amb</sub> | + 125( + 0-5) | °C    |

| 2   | Outputs - (Pins D/F 6-8-12)<br>(Pins C 9-12-18)                            | V <sub>OUT</sub> | Open          | -     |

| 3   | Inputs - (Pins D/F 1-2-3-4-5-9-10-11-13)<br>(Pins C 2-3-4-6-8-13-14-16-19) | V <sub>IN</sub>  | $V_{SS}$      | V     |

| 4   | Positive Supply Voltage<br>(Pin D/F 14)<br>(Pin C 20)                      | V <sub>DD</sub>  | 5.5( + 0-0.5) | V     |

| 5   | Negative Supply Voltage<br>(Pin D/F 7)<br>(Pin C 10)                       | V <sub>SS</sub>  | 0             | V     |

| 6   | Duration                                                                   | t                | 72            | Hours |

# **NOTES**

- 1. Input Protection Resistor = R1 =  $1.0k\Omega$ .

- 2. Output Load =  $R2 = 10k\Omega$ .

# TABLE 5(b) - CONDITIONS FOR BURN-IN HIGH TEMPERATURE REVERSE BIAS, P-CHANNELS

| No. | CHARACTERISTICS                                                            | SYMBOL           | CONDITION     | UNIT  |

|-----|----------------------------------------------------------------------------|------------------|---------------|-------|

| 1   | Ambient Temperature                                                        | T <sub>amb</sub> | + 125( + 0-5) | °C    |