Page i

# INTEGRATED CIRCUITS, SILICON MONOLITHIC,

# **CMOS 8-BIT MICRO-CONTROLLER,**

# BASED ON TYPES 80C32E AND 80C52E

# ESCC Detail Specification No. 9521/002

# ISSUE 1 October 2002

Document Custodian: European Space Agency - see https://escies.org

#### LEGAL DISCLAIMER AND COPYRIGHT

European Space Agency, Copyright © 2002. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Ageny and provided that it is not used for a commercial purpose, may be:

- copied in whole in any medium without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

european space agency agence spatiale européenne

Pages 1 to 75

# INTEGRATED CIRCUITS, SILICON MONOLITHIC, CMOS 8-BIT MICRO-CONTROLLER, BASED ON TYPES 80C32E AND 80C52E ESA/SCC Detail Specification No. 9521/002

# space components coordination group

|              |               | Appro         | oved by                               |

|--------------|---------------|---------------|---------------------------------------|

| lssue/Rev.   | Date          | SCCG Chairman | ESA Director General<br>or his Deputy |

| Issue 1      | February 1996 | Tomment       | Hoom                                  |

| Revision 'A' | June 1997     | Sa mitte      | Arom                                  |

|              |               |               |                                       |

|              |               |               |                                       |

•...

Rev. 'A'

# **DOCUMENTATION CHANGE NOTICE**

| Rev.<br>Letter | Rev.<br>Date | CHANGE<br>Reference Item | Approved<br>DCR No. |

|----------------|--------------|--------------------------|---------------------|

|                |              |                          |                     |

|                |              |                          |                     |

|                                                                                                                                                                                                                                                               | See                                                                                                                                                                                                                                                      | ESA/SCC Detail Specification<br>No. 9521/002                                                                                                                                                                                                                                                                                                                               |         | PAGE<br>ISSUE | 3<br>1                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                          | TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                          |         | D             | 200                                                                                                                                                                                    |

| 1.                                                                                                                                                                                                                                                            | GENERAL                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                            |         | <u> </u>      | age<br>5                                                                                                                                                                               |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8<br>1.9<br>1.10<br>1.11                                                                                                                                                                                   | Scope<br>Component Type Varia<br>Maximum Ratings<br>Parameter Derating Infe<br>Physical Dimensions<br>Pin Assignment<br>Truth Table/Instruction<br>Circuit Description<br>Functional Diagram<br>Handling Precautions<br>Input Protection Netwo           | Set                                                                                                                                                                                                                                                                                                                                                                        |         |               | 5 5 5 5 5 5 5 5 5 5 5                                                                                                                                                                  |

| 2.                                                                                                                                                                                                                                                            | APPLICABLE DOCUM                                                                                                                                                                                                                                         | <u>IENTS</u>                                                                                                                                                                                                                                                                                                                                                               |         |               | 33                                                                                                                                                                                     |

| 3.                                                                                                                                                                                                                                                            | TERMS, DEFINITION                                                                                                                                                                                                                                        | S, ABBREVIATIONS, SYMBOLS AND L                                                                                                                                                                                                                                                                                                                                            | INITS   |               | 33                                                                                                                                                                                     |

| 4.                                                                                                                                                                                                                                                            | <b>REQUIREMENTS</b>                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                            |         |               | 34                                                                                                                                                                                     |

| $\begin{array}{c} 4.1\\ 4.2\\ 4.2.1\\ 4.2.2\\ 4.2.3\\ 4.2.4\\ 4.2.5\\ 4.3\\ 4.2.5\\ 4.3.1\\ 4.3.2\\ 4.4\\ 4.4.1\\ 4.4.2\\ 4.5\\ 4.5.1\\ 4.5.2\\ 4.5.3\\ 4.5.4\\ 4.6.1\\ 4.6.2\\ 4.6.3\\ 4.7\\ 4.7.1\\ 4.7.2\\ 4.7.3\\ 4.8\\ 4.8.1\\ 4.8.2\\ 4.8.3\end{array}$ | Electrical Measuremen<br>Circuits for Electrical M<br>Burn-in Tests<br>Parameter Drift Values<br>Conditions for Power E<br>Electrical Circuits for P<br>Environmental and Enc<br>Electrical Measuremen<br>Electrical Measuremen<br>Electrical Measuremen | I In-process Controls<br>roduction Tests<br>a Tests<br>cation Tests<br>ceptance Tests<br>nts<br>sh<br>Number<br>ts<br>ts at Room Temperature<br>ts at High and Low Temperatures<br>leasurements<br>Rurn-in<br>ower Burn-in<br>lurance Tests<br>ts on Completion of Environmental Tests<br>ts at Intermediate Points during Enduranc<br>ts on Completion of Endurance Tests | e Tests |               | 34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>35<br>35<br>35<br>35<br>35<br>35<br>35<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36<br>36 |

| 4.8.4<br>4.8.5<br>4.8.6                                                                                                                                                                                                                                       | Conditions for Operatin<br>Electrical Circuits for C                                                                                                                                                                                                     | g Life Tests                                                                                                                                                                                                                                                                                                                                                               |         |               | 70<br>70<br>70<br>70                                                                                                                                                                   |

Г

|       | <u>see</u>                                                                                                                        | ESA/SCC Detail Specification<br>No. 9521/002 |           | PAGE 4<br>ISSUE 1 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------|-------------------|

|       |                                                                                                                                   |                                              |           | Page              |

| 4.9   | Total Dose Irradiation T                                                                                                          | esting                                       |           | 70                |

| 4.9.1 | Application                                                                                                                       | Ū                                            |           | 70                |

| 4.9.2 | Bias Conditions                                                                                                                   |                                              |           | 70                |

| 4.9.3 | Electrical Measurement                                                                                                            | ts                                           |           | 70                |

| TABLE | <u>:S</u>                                                                                                                         |                                              |           |                   |

| 1(a)  | Type Variants                                                                                                                     |                                              |           | 6                 |

| 1(b)  | Maximum Ratings                                                                                                                   |                                              |           | 6                 |

| 2     | Electrical Measuremen                                                                                                             | ts at Room Temperature - d.c. Parameter      | S         | 37                |

|       | Electrical Measuremen                                                                                                             | ts at Room Temperature - a.c. Parameter      | S         | 44                |

| 3     | Electrical Measuremen                                                                                                             | ts at High and Low Temperatures - d.c. P     | arameters | 50                |

| 3     | Electrical Measuremen                                                                                                             | ts at High and Low Temperatures - a.c. P     | arameters | 57                |

| 4     | Parameter Drift Values                                                                                                            |                                              |           | 67                |

| 5     |                                                                                                                                   | urn-in and Operating Life Tests              |           | 68                |

| 6     | 6 Electrical Measurements on Completion of Environmental Tests and<br>at Intermediate Points and on Completion of Endurance Tests |                                              |           | 71                |

| 7     |                                                                                                                                   |                                              |           | 75                |

| FIGUE | RES                                                                                                                               |                                              |           |                   |

| 1     | Parameter Derating Inf                                                                                                            | ormation                                     |           | 6                 |

| 2     | Physical Dimonsions                                                                                                               |                                              |           | 7                 |

| 1    | Farameter Derating information                                | 0  |

|------|---------------------------------------------------------------|----|

| 2    | Physical Dimensions                                           | 7  |

| 3(a) | Pin Assignment                                                | 10 |

| 3(b) | Truth Table/Instruction Set                                   | 12 |

| 3(c) | Circuit Description                                           | 23 |

| 3(d) | Functional Diagram                                            | 31 |

| 3(e) | Input Protection Networks                                     | 32 |

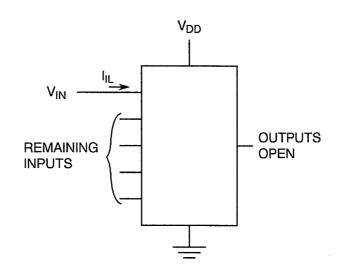

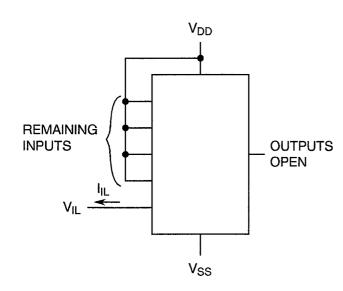

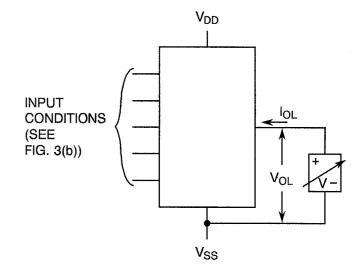

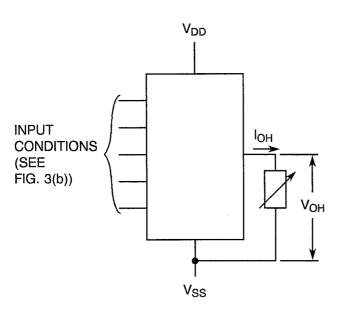

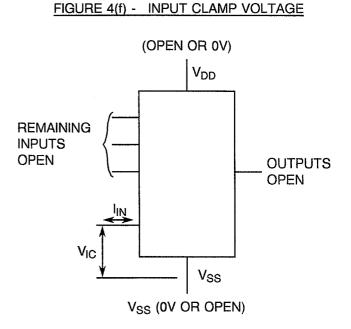

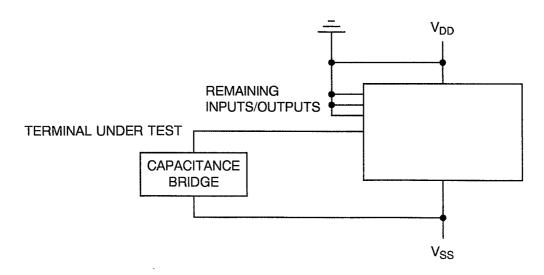

| 4    | Circuits for Electrical Measurements                          | 62 |

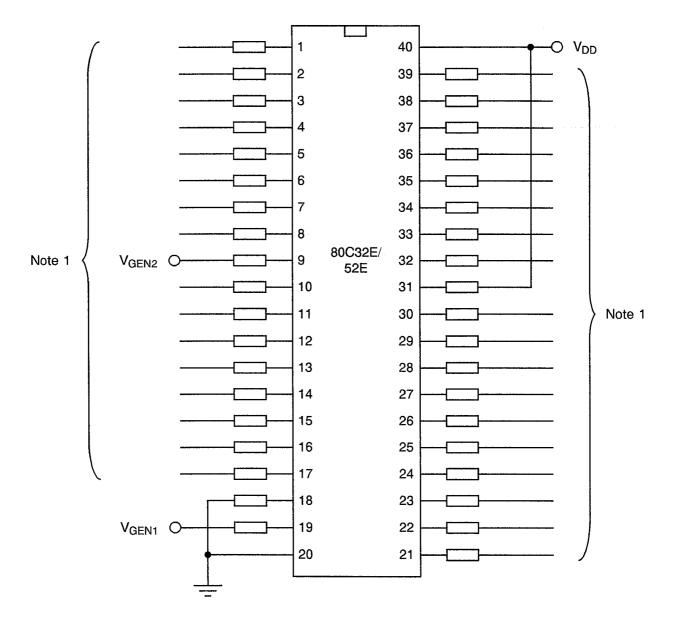

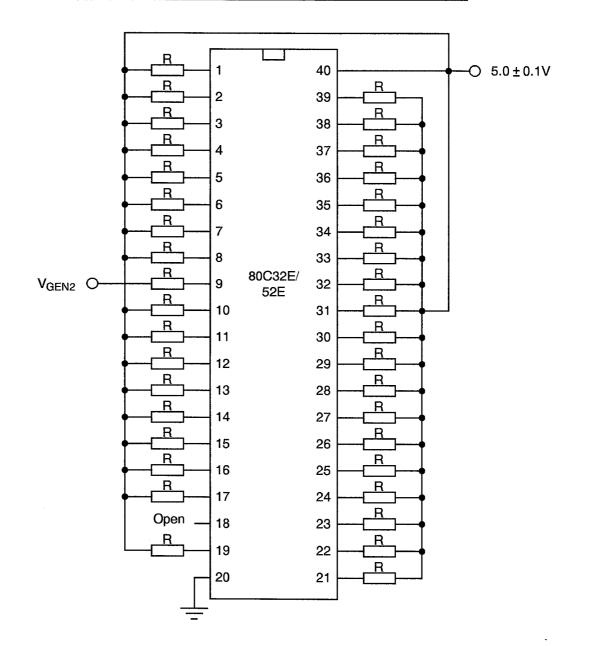

| 5    | Electrical Circuit for Power Burn-in and Operating Life Tests | 69 |

| 6    | Bias Conditions for Irradiation Testing                       | 74 |

|      |                                                               |    |

. .

APPENDICES (Applicable to specific Manufacturers only) None.

#### 1. <u>GENERAL</u>

#### 1.1 <u>SCOPE</u>

This specification details the ratings, physical and electrical characteristics, test and inspection data for a silicon monolithic, CMOS 8-Bit Micro-Controller, based on Types 80C32E and 80C52E. It shall be read in conjunction with ESA/SCC Generic Specification No. 19000, the requirements of which are supplemented herein.

#### 1.2 COMPONENT TYPE VARIANTS

Variants of the basic type integrated circuits specified herein, which are also covered by this specification, are given in Table 1(a).

#### 1.3 MAXIMUM RATINGS

The maximum ratings, which shall not be exceeded at any time during use or storage, applicable to the integrated circuits specified herein, are as scheduled in Table 1(b).

1.4 PARAMETER DERATING INFORMATION (FIGURE 1)

Not applicable.

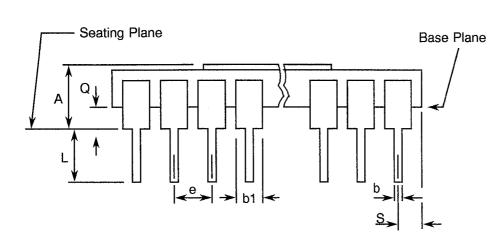

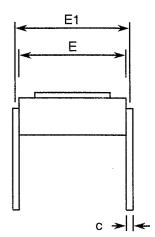

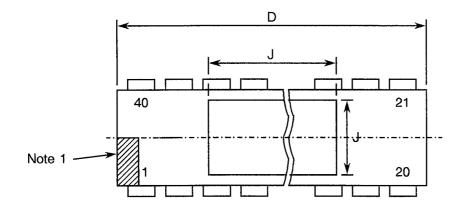

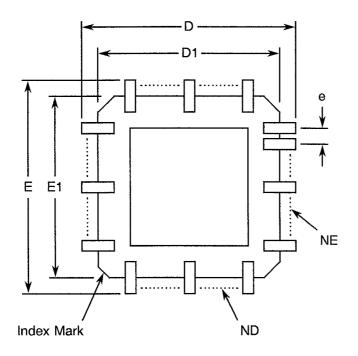

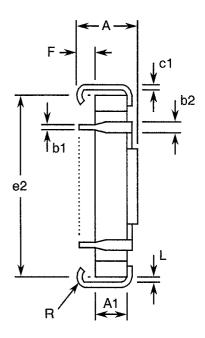

1.5 PHYSICAL DIMENSIONS

As per Figure 2.

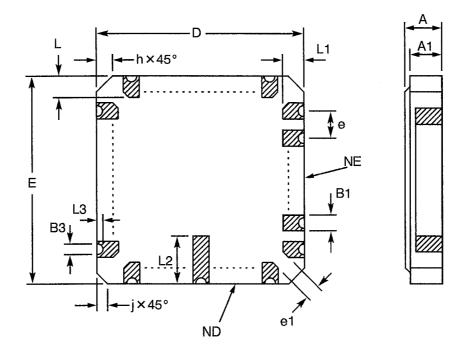

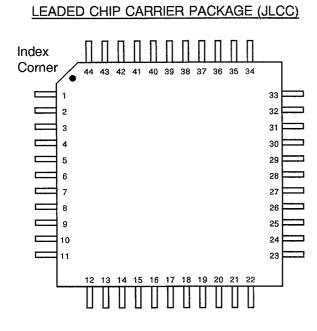

- 1.6 <u>PIN ASSIGNMENT</u> As per Figure 3(a).

- 1.7 <u>TRUTH TABLE/INSTRUCTION SET</u> As per Figure 3(b).

- 1.8 <u>CIRCUIT DESCRIPTION</u> As per Figure 3(c).

- 1.9 FUNCTIONAL DIAGRAM

As per Figure 3(d).

#### 1.10 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are categorised as Class 1 with a Minimum Critical Path Failure Voltage of 500Volts.

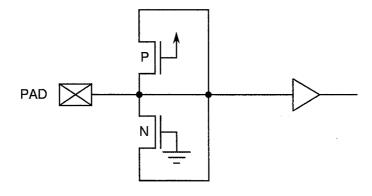

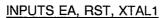

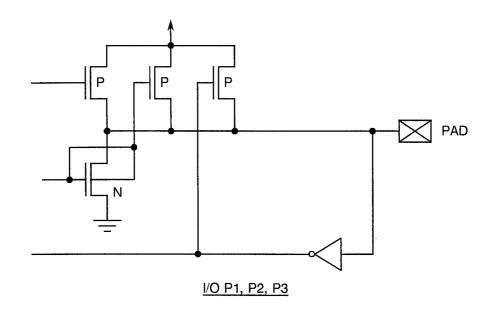

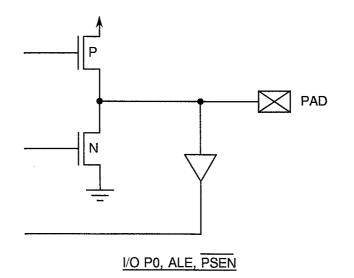

1.11 INPUT PROTECTION NETWORKS

Protection Networks shall be incorporated into each input as shown in Figure 3(e).

#### TABLE 1(a) - TYPE VARIANTS

| VARIANT | BASED ON<br>TYPE | CASE   | FIGURE | LEAD MATERIAL<br>AND/OR FINISH |

|---------|------------------|--------|--------|--------------------------------|

| 01      | 80C32E           | D.I.L. | 2(a)   | D2                             |

| 02      | 80C32E           | JLCC44 | 2(b)   | G3                             |

| 03      | 80C32E           | LCC44  | 2(c)   | 2                              |

| 04      | 80C52E           | D.I.L. | 2(a)   | D2                             |

| 05      | 80C52E           | JLCC44 | 2(b)   | G3                             |

| 06      | 80C52E           | LCC44  | 2(c)   | 2                              |

#### TABLE 1(b) - MAXIMUM RATINGS

| No. | CHARACTERISTICS                                    | SYMBOL               | MAXIMUM RATINGS                | UNIT | REMARKS            |

|-----|----------------------------------------------------|----------------------|--------------------------------|------|--------------------|

| 1   | Supply Voltage                                     | V <sub>DD</sub>      | -0.3 to +7.0                   | V    | Note 1             |

| 2   | Input Voltage                                      | V <sub>IN</sub>      | -0.3 to +V <sub>DD</sub> + 0.3 | V    | Note 2<br>Power On |

| 3   | Output Current                                     | ± lout               | 80                             | mA   | Note 3             |

| 4   | Device Dissipation<br>(Continuous)                 | PD                   | 0.3                            | W    | Per package        |

| 5   | Operating Temperature<br>Range                     | Т <sub>ор</sub>      | -55 to +125                    | °C   | T <sub>amb</sub>   |

| 6   | Storage Temperature<br>Range                       | T <sub>stg</sub>     | -65 to +150                    | °C   | -                  |

| 7   | Soldering Temperature<br>For DIL and FP<br>For CCP | T <sub>sol</sub>     | + 265<br>+ 245                 | °C   | Note 4<br>Note 5   |

| 8   | Junction Temperature                               | ТJ                   | 165                            | °C   | -                  |

| 9   | Thermal Resistance                                 | R <sub>TH(J-A)</sub> | 30                             | °C/W | -                  |

#### **NOTES**

- 1. Device is functional from +4.5V to +5.5V with reference to Ground.

- 2.  $V_{DD}$  + 0.3 should not exceed + 7.0V.

- 3. The maximum output current of any single output.

- 4. Duration 10 seconds maximum at a distance of not less than 1.5mm from the device body and the same lead shall not be resoldered until 3 minutes have elapsed.

- 5. Duration 10 seconds maximum and the same terminal shall not be resoldered until 3 minutes have elapsed.

#### FIGURE 1 - PARAMETER DERATING INFORMATION

Not applicable.

. .

# FIGURE 2 - PHYSICAL DIMENSIONS

# FIGURE 2(a) - DUAL-IN-LINE PACKAGE, 40 PIN

| SYMBOL  | MILLIM | ETRES | NOTES |  |

|---------|--------|-------|-------|--|

| 3 TMBOL | MIN    | MAX   | NOTES |  |

| А       | 2.20   | 4.80  |       |  |

| b       | 0.38   | 0.58  | 3     |  |

| b1      | 0.97   | 1.52  | 3     |  |

| с       | 0.20   | 0.38  |       |  |

| D       | 50.30  | 51.58 |       |  |

| E       | 14.74  | 15.49 |       |  |

| E1      | 15.12  | 15.87 |       |  |

| е       | 2.54   | ТҮР   | 4     |  |

| J       | 10.80  | TYP   | 4     |  |

| L ·     | 3.18   | 4.44  | 3     |  |

| Q       | 0.51   | 1.77  | 2     |  |

| S       | 0.77   | 1.65  | 5     |  |

# FIGURE 2 - PHYSICAL DIMENSIONS (CONTINUED)

# FIGURE 2(b) - CENTRE LEADED CHIP CARRIER, 44 LEADS

| SYMBOL | MILLIM | IETERS NOTES |       |

|--------|--------|--------------|-------|

| STNDUL | MIN.   | MAX.         | NUTES |

| А      | 2.95   | 4.82         |       |

| A1     | 1.65   | NOM.         |       |

| b1     | 0.33   | 0.50         |       |

| b2     | 0.55   | 0.88         |       |

| c1     | 0.17   | 0.25         |       |

| D/E    | 17.14  | 17.78        |       |

| D1/E1  | 15.74  | 16.76        |       |

| е      | 1.27   | BSC          |       |

| e2     | 16.00  | BSC          |       |

| F      | 0.023  | -            |       |

| L      | 0.12   | -            |       |

| ND/NE  | 11     |              |       |

| R      | 0.50   | 1.01         |       |

# NOTES: See Page 10.

# FIGURE 2 - PHYSICAL DIMENSIONS (CONTINUED)

# FIGURE 2(c) - CENTRE LEADLESS CHIP CARRIER, 44 LEADS

| SYMBOL   | MILLIM | ETERS | NOTES |

|----------|--------|-------|-------|

| STIVIDUL | MIN.   | MAX.  | NOTES |

| А        | 1.63   | 3.05  |       |

| A1       | 1.37   | 2.23  |       |

| B1       | 0.56   | 0.71  |       |

| B3       | 0.15   | 0.56  |       |

| D/E      | 16.25  | 16.82 |       |

| е        | 1.27   | BSC   |       |

| e1       | 0.38   | -     |       |

| h        | 1.02   | REF   |       |

| j        | 0.51   | REF   |       |

| L/L1     | 1.14   | 1.40  |       |

| L2       | 1.90   | 2.41  |       |

| L3       | 0.08   | 0.38  |       |

| ND/NE    | 11.    | /11   |       |

**<u>NOTES</u>**: See Page 10.

# FIGURE 2 - PHYSICAL DIMENSIONS (CONTINUED)

#### NOTES TO FIGURES 2(a) TO 2(c) INCLUSIVE

- 1. Index area; a notch, letter or dot shall be located adjacent to Pin 1 and shall be within the shaded area shown.

- 2. The dimension shall be measured from the seating plane to the base plane.

- 3. All leads or terminals.

- 4. 38 spaces.

- 5. All 4 corners.

- 6. Lead centre when  $\propto$  is 0°.

### FIGURE 3(a) - PIN ASSIGNMENT

**DUAL-IN-LINE PACKAGE**

TOP VIEW

. .

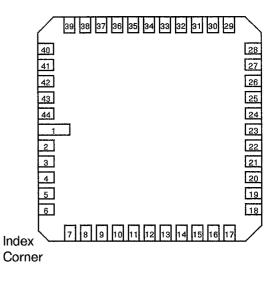

# FIGURE 3(a) - PIN ASSIGNMENT (CONTINUED)

LEADLESS CHIP CARRIER PACKAGE (LCC)

| Pin No. | Description     | Pin No. | Description     |

|---------|-----------------|---------|-----------------|

| 1       | P1.5            | 23      | P2.5            |

| 2       | P1.6            | 24      | P2.6            |

| 3       | P1.7            | 25      | P2.7            |

| 4       | RST             | 26      | PSEN            |

| 5       | P3.0/RXD        | 27      | ALE             |

| 6       | N/C             | 28      | N/C             |

| 7       | P3.1/TXD        | 29      | EA              |

| 8       | P3.2/INT0       | 30      | P0.7            |

| 9       | P3.3/INT1       | 31      | P0.6            |

| 10      | P3.4/T0         | 32      | P0.5            |

| 11      | P3.5/T1         | 33      | P0.4            |

| 12      | P3.6/WR         | 34      | P0.3            |

| 13      | P3.7/RD         | 35      | P0.2            |

| 14      | XTAL2           | 36      | P0.1            |

| 15      | XTAL1           | 37      | P0.0            |

| 16      | V <sub>SS</sub> | 38      | V <sub>DD</sub> |

| 17      | N/C             | 39      | N/C             |

| 18      | P2.0            | 40      | T2/P1.0         |

| 19      | P2.1            | 41      | T2EX/P1.1       |

| 20      | P2.2            | 42      | P1.2            |

| 21      | P2.3            | 43      | P1.3            |

| 22      | P2.4            | 44      | P1.4            |

| Pin No. | Description     | Pin No. | Description     |

|---------|-----------------|---------|-----------------|

| 1       | N/C             | 23      | N/C             |

| 2       | T2/P1.0         | 24      | P2.0            |

| 3       | T2EX/P1.1       | 25      | P2.1            |

| 4       | P1.2            | 26      | P2.2            |

| 5       | P1.3            | 27      | P2.3            |

| 6       | P1.4            | 28      | P2.4            |

| 7       | P1.5            | 29      | P2.5            |

| 8       | P1.6            | 30      | P2.6            |

| 9       | P1.7            | 31      | P2.7            |

| 10      | RST             | 32      | PSEN            |

| 11      | P3.0/RXD        | 33      | ALE             |

| 12      | N/C             | 34      | N/C             |

| 13      | P3.1/TXD        | 35      | ĒĀ              |

| 14      | P3.2/INT0       | 36      | P0.7            |

| 15      | P3.3/INT1       | 37      | P0.6            |

| 16      | P3.4/T0         | 38      | P0.5            |

| 17      | P3.5/T1         | 39      | P0.4            |

| 18      | P3.6/WR         | 40      | P0.3            |

| 19      | P3.7/RD         | 41      | P0.2            |

| 20      | XTAL2           | 42      | P0.1            |

| 21      | XTAL1           | 43      | P0.0            |

| 22      | V <sub>SS</sub> | 44      | V <sub>DD</sub> |

---

# FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET

# INSTRUCTIONS IN HEXADECIMAL ORDER

| HEX<br>CODE | NUMBER<br>OF BYTES | MNEMONIC   | OPERANDS    | HEX<br>CODE | NUMBER<br>OF BYTES | MNEMONIC | OPERANDS            |

|-------------|--------------------|------------|-------------|-------------|--------------------|----------|---------------------|

| 00          | 1                  | NOP        |             | 2B          | 1                  | ADD      | A.R3                |

| 01          | 2                  | AJMP       | code addr   | 2C          | 1                  | ADD      | A.R4                |

| 02          | 3                  | LJMP       | code addr   | 2D          | 1                  | ADD      | A.R5                |

| 03          | 1                  | RR         | А           | 2E          | 1                  | ADD      | A.R6                |

| 04          | 1                  | INC        | А           | 2F          | 1                  | ADD      | A.R7                |

| 05          | 2                  | INC        | data addr   | 30          | 3                  | JNB      | bit addr.           |

| 06          | 1                  | INC        | @R0         |             | •                  | 1011     | code addr           |

| 07          | 1                  | INC        | @R1         | 31          | 2                  | ACALL    | code addr           |

| 08          | 1                  | INC        | R0          | 32          | 1                  | RETI     |                     |

| 09          | 1                  | INC        | R1          | 33          | 1                  | RLC      | A                   |

| 0A          | 1                  | INC        | R2          | 34          | . 2                | ADDC     | A.#data             |

| 0B          | 1                  | INC        | R3          | 35          | 2                  | ADDC     | A.data addr         |

| 0C          | 1                  | INC        | R4          | 36          | 1                  | ADDC     | A.@R0               |

| 0D          | 1                  | INC        | R5          | 37          | 1                  | ADDC     | A.@R1               |

| 0E          | 1                  | INC        | R6          | 38          | 1                  | ADDC     | A.R0                |

| 0F          | 1                  | INC        | R7          | 39          | 1                  | ADDC     | A.R1                |

| 10          | 3                  | JBC        | bit addr.   | 3A          | 1                  | ADDC     | A.R2                |

|             | 0                  | A () A   1 | code addr   | 3B          | 1                  | ADDC     | A.R3                |

| 11          | 2                  | ACALL      | code addr   | 3C          | 1                  | ADDC     | A.R4                |

| 12          | 3                  | LCALL      | code addr   | 3D          | 1                  | ADDC     | A.R5                |

| 13          | 1                  | RRC        | A           | 3E          | 1                  | ADDC     | A.R6                |

| 14          | 1                  | DEC        | A           | 3F          | 1                  | ADDC     | A.R7                |

| 15          | 2                  | DEC        | data addr   | 40          | 2                  | JC       | code addr           |

| 16          | 1                  | DEC        | @R0         | 41          | 2                  | AJMP     | code addr           |

| 17          | 1                  | DEC        | @R1         | 42          | 2                  | ORL      | data addr.A         |

| 18<br>19    | 1                  | DEC<br>DEC | R0<br>R1    | 43          | 3                  | ORL      | data addr.<br>#data |

| 1A          | 1                  | DEC        | R2          | 44          | 2                  | ORL      | A.#data             |

| 1B          | 1                  | DEC        | R3          | 45          | 2                  | ORL      | A.data addr         |

| 1C          | 1                  | DEC        | R4          | 46          | 1                  | ORL      | A.@R0               |

| 1D          | 1                  | DEC        | R5          | 47          | 1                  | ORL      | A.@R1               |

| 1E          | 1                  | DEC        | R6          | 48          | 1                  | ORL      | A.R0                |

| 1F          | 1                  | DEC        | R7          | 49          | 1                  | ORL      | A.R1                |

| 20          | 3                  | JB         | bit addr.   | 4A          | 1                  | ORL      | A.R2                |

|             | -                  |            | code addr   | 4B          | 1                  | ORL      | A.R3                |

| 21          | 2                  | AJMP       | code addr   | 4C          | 1                  | ORL      | A.R4                |

| 22          | 1                  | RET        |             | 4D          | 1                  | ORL      | A.R5                |

| 23          | 1                  | RL         | A           | 4E          | 1                  | ORL      | A.R6                |

| 24          | 1                  | ADD        | A.data      | 4F          | 1                  | ORL      | A.R7                |

| 25          | 1                  | ADD .      | A.data addr | 50          | 2                  | JNC      | code addr           |

| 26          | 1                  | ADD        | A.@R0       | 51          | 2                  | ACALL    | code addr           |

| 27          | 1                  | ADD        | A.@R1       | 52          | 2                  | ANL      | code addr.A         |

| 28          | 1                  | ADD        | A.R0        | 53          | 3                  | ANL      | data addr.          |

| 29          | 1                  | ADD        | A.R1        |             |                    |          | #data               |

| 2A          | 1                  | ADD        | A.R2        | 54          | 2                  | ANL      | A.#data             |

|             |                    |            |             | 55          | 2                  | ANL      | A.data addr         |

# FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

# INSTRUCTIONS IN HEXADECIMAL ORDER (CONTINUED)

| HEX<br>CODE | NUMBER<br>OF BYTES | MNEMONIC | OPERANDS    |   | HEX<br>CODE | NUMBER<br>OF BYTES | MNEMONIC | OPERANDS      |

|-------------|--------------------|----------|-------------|---|-------------|--------------------|----------|---------------|

| 56          | 1                  | ANL      | A.@R0       |   | 82          | 2                  | ANL      | C.bit addr    |

| 57          | 1                  | ANL      | A.@R1       |   | 83          | 1                  | MOVC     | A.@A+PC       |

| 58          | 1                  | ANL      | A.R0        |   | 84          | 1                  | DIV      | AB            |

| 59          | 1                  | ANL      | A.R1        |   | 85          | 3                  | MOV      | data addr     |

| 5A          | 1                  | ANL      | A.R2        |   | 86          | 2                  | MOV      | data addr.@R0 |

| 5B          | 1                  | ANL      | A.R3        |   | 87          | 2                  | MOV      | data addr.@R1 |

| 5C          | 1                  | ANL      | A.R4        |   | 88          | 2                  | MOV      | data addr.R0  |

| 5D          | 1                  | ANL      | A.R5        |   | 89          | 2                  | MOV      | data addr.R1  |

| 5E          | 1                  | ANL      | A.R6        |   | 8A          | 2                  | MOV      | data addr.R2  |

| 5F          | 1                  | ANL      | A.R7        |   | 8B          | 2                  | MOV      | data addr.R3  |

| 60          | 2                  | JZ       | code addr   |   | 8C          | 2                  | MOV      | data addr.R4  |

| 61          | 2                  | AJMP     | code addr   |   | 8D          | 2                  | MOV      | data addr.R5  |

| 62          | 2                  | XRL      | code addr.A |   | 8E          | 2                  | MOV      | data addr.R6  |

| 63          | 3                  | XRL      | data addr.  |   | 8F          | 2                  | MOV      | data addr.R7  |

|             | -                  |          | #data       |   | 90          | 3                  | MOV      | DPTR.#data    |

| 64          | 2                  | XRL      | A.#data     |   | 91          | 2                  | ACALL    | code addr     |

| 65          | 2                  | XRL      | A.data addr |   | 92          | 2                  | MOV      | bit addr.C    |

| 66          | 1                  | XRL      | A.@R0       |   | 93          | 1                  | MOVC     | A.@A + DPTR   |

| 67          | 1                  | XRL      | A.@R1       |   | 94          | 2                  | SUBB     | A.#data       |

| 68          | 1                  | XRL      | A.R0        |   | 95          | 2                  | SUBB     | A.data addr   |

| 69          | 1                  | XRL      | A.R1        |   | 96          | 1                  | SUBB     | A.@R0         |

| 6A          | 1                  | XRL      | A.R2        |   | 97          | 1                  | SUBB     | A.@R1         |

| 6B          | 1                  | XRL      | A.R3        |   | 98          | 1                  | SUBB     | A.RO          |

| 6C          | 1                  | XRL      | A.R4        |   | 99          | 1                  | SUBB     | A.R1          |

| 6D          | 1                  | XRL      | A.R5        |   | 99<br>9A    | 1                  | SUBB     | A.R2          |

| 6E          | 1                  | XRL      | A.R6        |   | 98<br>98    | 1                  | SUBB     | A.R2          |

| 6F          | 1                  | XRL      | A.R7        |   | 9C          | 1                  | SUBB     | A.R4          |

| 70          | 2                  | JNZ      | code addr   |   | 90<br>9D    | 1                  | SUBB     | A.R5          |

| 71          | 2                  | ACALL    | code addr   |   | 9D<br>9E    | 1                  | SUBB     |               |

| 72          | 2                  | MOV      | C.bit addr  |   | 9E<br>9F    |                    |          | A.R6          |

| 73          | 1                  | JMP      | @A + DPTR   |   |             | 1                  | SUBB     | A.R7          |

| 74          | 2                  | MOV      | A.#data     |   | A0          | 2                  |          | C.bit addr    |

| 75          | 3                  | MOV      | data addr.  |   | A1          | 2                  | AJMP     | code addr     |

|             | 0                  |          | #data       |   | A2          | 2                  | MOV      | C.bit addr    |

| 76          | 2                  | MOV      | @R0.#data   |   | A3          | 1                  |          | DPTR          |

| 77          | 2                  | MOV      | @R1.#data   |   | A4          | 1                  | MUL      | AB            |

| 78          | 2                  | MOV      | R0.#data    |   | A5          | •                  | reserved |               |

| 79          | 2                  | MOV      | R1.#data    |   | A6          | 2                  | MOV      | @R0.data addr |

| 7A          | 2                  | MOV      | R2.#data    |   | A7          | 2                  | MOV      | @R1.data addr |

| 7B          | 2                  | MOV      | R3.#data    | 1 | A8          | 2                  | MOV      | R0.data addr  |

| 7C          | 2                  | MOV      | R4.#data    |   | A9          | 2                  | MOV      | R1.data addr  |

| 7D          | 2                  | MOV      | R5.#data    | I | AA          | 2                  | MOV      | R2.data addr  |

| 7E          | 2                  | MOV      | R6.#data    |   | AB          | 2                  | MOV      | R3.data addr  |

| 7E<br>7F    | 2                  | MOV      | R7.#data    |   | AC          | 2                  | MOV      | R4.data addr  |

| 80          | 2                  | SJMP     | code addr   |   | AD          | 2                  | MOV      | R5.data addr  |

| 81          | 2                  | AJMP     | code addr   | I | AE          | 2                  | MOV      | R6.data addr  |

|             | ۷                  |          |             | 1 | AF          | 2                  | MOV      | R7.data addr  |

# FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

# INSTRUCTIONS IN HEXADECIMAL ORDER (CONTINUED)

| HEX<br>CODE | NUMBER<br>OF BYTES | MNEMONIC | OPERANDS                  |   | HEX<br>CODE | NUMBER<br>OF BYTES | MNEMONIC     | OPERANDS                     |

|-------------|--------------------|----------|---------------------------|---|-------------|--------------------|--------------|------------------------------|

| B0          | 2                  | ANL      | C.bit addr                |   | D3          | 1                  | SETB         | С                            |

| B1          | 2                  | ACALL    | code addr                 |   | D4          | 1                  | DA           | А                            |

| B2          | 2                  | CPL      | bit addr                  |   | D5          | 3                  | DJNZ         | data addr.                   |

| B3          | 1                  | CPL      | С                         |   | _           |                    |              | code addr                    |

| B4          | 3                  | CJNE     | A.#data.                  |   | D6          | 1                  | XCHD         | A.@R0                        |

|             | _                  |          | code addr                 |   | D7          | 1                  | XCHD         | A.@R1                        |

| B5          | 3                  | CJNE     | A.data addr.<br>code addr |   | D8          | 2                  | DJNZ         | R0.code addr                 |

| B6          | 3                  | CJNE     | @R0.#data.                |   | D9          | 2                  | DJNZ         | R1.code addr                 |

| DO          | 3                  | COME     | code addr                 |   | DA          | 2                  | DJNZ         | R2.code addr                 |

| B7          | 3                  | CJNE     | @R1.#data.                |   | DB          | 2                  | DJNZ         | R3.code addr                 |

|             | U                  | 00112    | code addr                 |   | DC          | 2                  | DJNZ         | R4.code addr                 |

| B8          | 3                  | CJNE     | R0.#data.                 |   | DD          | 2                  | DJNZ         | R5.code addr<br>R6.code addr |

|             |                    |          | code addr                 |   | DE<br>DF    | 3                  | DJNZ<br>DJNZ |                              |

| B9          | 3                  | CJNE     | R1.#data.                 |   | E0          | 2                  | MOVX         | R7.code addr                 |

|             |                    |          | code addr                 |   | EU<br>E1    | 1<br>2             | AJMP         | A.@DPTR<br>code addr         |

| BA          | 3                  | CJNE     | R2.#data.                 |   | E1<br>E2    | 2                  | MOVX         | A.@R0                        |

|             | 0                  |          | code addr<br>R3.#data.    |   | E2<br>E3    | 1                  | MOVX         | A.@R1                        |

| BB          | 3                  | CJNE     | code addr                 |   | E3<br>E4    | 1                  | CLR          | A.@h}                        |

| вС          | 3                  | CJNE     | R4.#data.                 |   | E5          | 2                  | MOV          | A<br>A.data addr             |

|             | 0                  | CONL     | code addr                 |   | E6          | 2                  | MOV          | A.@R0                        |

| BD          | 3                  | CJNE     | R5.#data.                 |   | E7          | 1                  | MOV          | A.@R1                        |

|             |                    |          | code addr                 |   | E8          | 1                  | MOV          | A.RO                         |

| BE          | 3                  | CJNE     | R6.#data.                 |   | E9          | 1                  | MOV          | A.R1                         |

|             |                    |          | code addr                 |   | EA          | 1                  | MOV          | A.R2                         |

| BF          | 3                  | CJNE     | R7.#data.                 |   | EB          | 1                  | MOV          | A.R3                         |

| CO          | 0                  | PUSH     | code addr                 |   | EC          | 1                  | MOV          | A.R4                         |

| C0<br>C1    | 2                  | AJMP     | data addr<br>code addr    |   | ED          | 1                  | MOV          | A.R5                         |

| C1<br>C2    | 2<br>2             | CLR      | bit addr                  |   | EE          | 1                  | MOV          | A.R6                         |

| C2<br>C3    | 2<br>1             | CLR      | C                         |   | EF          | 1                  | MOV          | A.R7                         |

| C3          | 1                  | SWAP     | A                         |   | F0          | 1                  | MOVX         | @DPRT.A                      |

| C5          | 2                  | XCH      | A.data addr               |   | F1          | 2                  | ACALL        | code addr                    |

| C6          | 2<br>1             | XCH      | A.@R0                     |   | F2          | 1                  | MOVX         | @R0.A                        |

| C7          | 1                  | XCH      | A.@R1                     |   | F3          | 1                  | MOVX         | @R1.A                        |

| C8          | 1                  | XCH      | A.R0                      |   | F4          | 1                  | CPL          | Ă                            |

| C9          | 1                  | XCH      | A.R1                      |   | F5          | 2                  | MOV          | data addr.A                  |

| CA          | 1                  | XCH      | A.R2                      |   | F6          | 1                  | MOV          | @R0.A                        |

| СВ          | 1                  | XCH      | A.R3                      |   | F7          | 1                  | MOV          | @R1.A                        |

| cc          | 1                  | XCH      | A.R4                      |   | F8          | 1                  | MOV          | R0.A                         |

| CD          | 1                  | XCH      | A.R5                      |   | F9          | 1                  | MOV          | R1.A                         |

| CE          | 1                  | XCH      | A.R6                      |   | FA          | 1                  | MOV          | R2.A                         |

| CF          | 1                  | XCH      | A.R7                      |   | FB          | 1                  | MOV          | R3.A                         |

| DO          | 2                  | POP      | data addr                 |   | FC          | 1                  | MOV          | R4.A                         |

| D1          | 2                  | ACALL    | code addr                 |   | FD          | 1                  | MOV          | R5.A                         |

| D2          | 2                  | SETB     | bit addr                  |   | FE          | 1                  | MOV          | R6.A                         |

|             |                    |          |                           | - | FF          | 1                  | MOV          | R7.A                         |

Г

# FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

# DESCRIPTION OF INSTRUCTIONS

| ARITHM | ETIC OPERATION | <u>S</u>                                   |      |     |

|--------|----------------|--------------------------------------------|------|-----|

| Mnemor | nic            | Description                                | Byte | Сус |

| ADD    | A.Rn           | Add register to Accumulator                | 1    | 1   |

| ADD    | A.direct       | Add direct byte to Accumulator             | 2    | 1   |

| ADD    | A.@Ri          | Add indirect RAM to Accumulator            | 1    | 1   |

| ADD    | A.#data        | Add immediate data to Accumulator          | 2    | 1   |

| ADDC   | A.Rn           | Add register to Accumulator with Carry     | 1    | 1   |

| ADDC   | A.direct       | Add direct byte to A with Carry Flag       | 2    | 1   |

| ADDC   | A.@Ri          | Add indirect RAM to A with Carry Flag      | 1    | 1   |

| ADDC   | A.#data        | Add immediate data to A with Carry Flag    | 2    | 1   |

| SUBB   | A.Rn           | Subtract register from A with Borrow       | 1    | 1   |

| SUBB   | A.direct       | Subtract direct byte from A with Borrow    | 2    | 1   |

| SUBB   | A.@Ri          | Subtract indirect RAM from A with Borrow   | 1    | 1   |

| SUBB   | A.#data        | Subtract immediate data from A with Borrow | 2    | 1   |

| INC    | А              | Increment Accumulator                      | 1    | 1   |

| INC    | Rn             | Increment register                         | 1    | 1   |

| INC    | direct         | Increment direct byte                      | 2    | 1   |

| INC    | @Ri            | Increment indirect RAM                     | 1    | 1   |

| INC    | DPTR           | Increment Data Pointer                     | 1    | 2   |

| DEC    | А              | Decrement Accumulator                      | 1    | 1   |

| DEC    | Rn             | Decrement register                         | 1    | 1   |

| DEC    | direct         | Decrement direct byte                      | 2    | 1   |

| DEC    | @Ri            | Decrement indirect RAM                     | 1    | 1   |

| MUL    | AB             | Multiply A and B                           | 1    | 4   |

| DIV    | AB             | Divide A by B                              | 1    | 4   |

| DA     | Α              | Decimal Adjust Accumulator                 | 1    | 1   |

|        | OPERATIONS     |                                            |      |     |

| ANL    | A.Rn           | AND register to Accumulator                | 1    | 1   |

| ANL    | A.direct       | AND direct byte to Accumulator             | 2    | 1   |

| ANL    | A.@Ri          | AND indirect RAM to Accumulator            | 1    | 1   |

| ANL    | A.#data        | AND immediate data to Accumulator          | 2 -  | 1   |

| ANL    | direct.A       | AND Accumulator to direct byte             | 2    | 1   |

| ANL    | direct.#data   | AND immediate data to direct byte          | 3    | 2   |

| ORL    | A.Rn           | OR register to Accumulator                 | 1    | 1   |

| ORL    | A.direct       | OR direct byte to Accumulator              | 2    | 1   |

| ORL    | A.@Ri          | OR indirect RAM to Accumulator             | 1    | 1   |

| ORL    | A.#data        | OR immediate data to Accumulator           | 2    | 1   |

| ORL    | direct.A       | OR Accumulator to direct byte              | 2    | 1   |

| ORL    | direct.#data   | OR immediate data to direct byte           | 3    | 2   |

No. 9521/002

· •

# FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

# DESCRIPTION OF INSTRUCTIONS (CONTINUED)

|          | PERATIONS (CONT' | <u>D)</u>                                |      |     |

|----------|------------------|------------------------------------------|------|-----|

| Mnemonic |                  | Description                              | Byte | Сус |

| XRL      | A.Rn             | Exclusive-OR register to Accumulator     | 1    | 1   |

| XRL      | A.direct         | Exclusive-OR direct byte to Accumulator  | 2    | 1   |

| XRL      | A.@Ri            | Exclusive-OR indirect RAM to A           | 1    | 1   |

| XRL      | A.#data          | Exclusive-OR immediate data to A         | 2    | 1   |

| XRL      | direct.A         | Exclusive-OR Accumulator to direct byte  | 2    | 1   |

| XRL      | direct.#data     | Exclusive-OR immediate data to direct    | 3    | 2   |

| CLR      | А                | Clear Accumulator                        | 1    | 1   |

| CPL      | A                | Complement Accumulator                   | 1    | 1   |

| RL       | А                | Rotate Accumulator Left                  | 1    | 1   |

| RLC      | А                | Rotate A Left through the Carry Flag     | 1    | 1   |

| RR       | А                | Rotate Accumulator Right                 | 1    | 1   |

| RRC      | A                | Rotate A Right through Carry Flag        | 1    | 1   |

| SWAP     | A                | Swap nibbles within the Accumulator      | 1    | 1   |

| DATA TR  | RANSFER          |                                          |      |     |

| Mnemor   | nic              | Description                              | Byte | Сус |

| MOV      | A.Rn             | Move register to Accumulator             | 1    | 1   |

| MOV      | A.direct         | Move direct byte to Accumulator          | 2    | 1   |

| MOV      | A.@Ri            | Move indirect RAM to Accumulator         | 1    | 1   |

| MOV      | A.#data          | Move immediate data to Accumulator       | 2    | 1   |

| моу      | Rn.A             | Move Accumulator to register             | 1    | 1   |

| MOV      | Rn. direct       | Move direct byte to register             | 2    | 2   |

| моу      | Rn.#data         | Move immediate data to register          | 2    | 1   |

| MOV      | direct.A         | Move Accumulator to direct byte          | 2    | 1   |

| моу      | direct.Rn        | Move register to direct byte             | 2    | 2   |

| моу      | direct.direct    | Move direct byte to direct byte          | 3    | 2   |

| MOV      | direct.@Ri       | Move indirect RAM to direct byte         | 2    | 2   |

| моу      | direct.#data     | Move immediate data to direct byte       | 3    | 2   |

| моу      | @Ri.A            | Move Accumulator to indirect RAM         | 1    | 1   |

| MOV      | @Ri.direct       | Move direct byte to indirect RAM         | 2    | 2   |

| MOV      | @Ri.#data        | Move immediate data to indirect RAM      | 2    | 1   |

| MOV      | DPTR.#data 16    | Load Data Pointer with a 16-bit constant | 3    | 2   |

| MOVC     | A.@A + DPTR      | Move Code byte relative to DPTR to A     | 1    | 2   |

| MOVC     | A.@A+PC          | Move Code byte relative to PC to A       | 1    | 2   |

| MOVX     | A.@Ri            | Move External RAM (8-bit addr) to A      | 1    | 2   |

| MOVX     | A.@DPTR          | Move External RAM (16-bit addr) to A     | 1    | 2   |

| MOVX     | @Ri.A            | Move A to External RAM (8-bit addr)      | 1    | 2   |

| MOVX     | @DPTRA           | Move A to External RAM (16-bit addr)     | 1    | 2   |

| PUSH     | direct           | Push direct byte onto stack              | 2    | 2   |

| POP      | direct           | Pop direct byte from stack               | 2    | 2   |

| XCH      | A.Rn             | Exchange register with Accumulator       | 1    | 1   |

| ХСН      | A.direct         | Exchange direct byte with Accumulator    | 2    | 1   |

| XCH      | A.@Ri            | Exchange indirect RAM with A             | 1    | 1   |

| XCHD     | A.@Ri            | Exchange low-order nibble ind RAM with A | 1    | 1   |

- -

# FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

# DESCRIPTION OF INSTRUCTIONS (CONTINUED)

| <u>BOOLEA</u><br>MANIPUI | N VARIABLE<br>_ATION  |                                             |      |     |

|--------------------------|-----------------------|---------------------------------------------|------|-----|

| Mnemor                   | lic                   | Description                                 | Byte | Сус |

| CLR                      | С                     | Clear Carry flag                            | 1    | 1   |

| CLR                      | bit                   | Clear direct bit                            | 2    | 1   |

| SETB                     | С                     | Set Carry flag                              | 1    | 1   |

| SETB                     | bit                   | Set direct bit                              | 2    | 1   |

| CPL                      | С                     | Complement Carry flag                       | 1    | 1   |

| CPL                      | bit                   | Complement direct bit                       | 1    | 1   |

| ANL                      | C.bit                 | AND direct bit to Carry flag                | 2    | 2   |

| ANL                      | C./bit                | AND complement of direct bit to Carry       | 2    | 2   |

| ORL                      | C.bit                 | OR direct bit to Carry flag                 | 2    | 2   |

| ORL                      | C./bit                | OR complement of direct bit to Carry        | 2    | 2   |

| MOV                      | C.bit                 | Move direct bit to Carry flag               | 2    | 1   |

| MOV                      | bit.C                 | Move Carry flag to direct bit               | 2    | 2   |

|                          | AMME AND<br>E CONTROL |                                             |      |     |

| Mnemor                   | nic                   | Description                                 | Byte | Сус |

| ACALL                    | addr 11               | Absolute Subroutine Call                    | 2    | 2   |

| LCALL                    | addr 16               | Long Subroutine Call                        | · 3  | 2   |

| RET                      |                       | Return from Subroutine                      | 1    | 2   |

| RETI                     |                       | Return from interrupt                       | 1    | 2   |

| AJMP                     | addr 11               | Absolute jump                               | 2    | 2   |

| LJMP                     | addr 16               | Long jump                                   | 3    | 2   |

| SJMP                     | rel                   | Short jump (relative addr)                  | 2    | 2   |

| JMP                      | @A + DPTR             | Jump indirect relative to the DPTR          | 1    | 2   |

| JZ                       | rel                   | Jump if Accumulator is Zero                 | 2    | 2   |

| JNZ                      | rel                   | Jump if Accumulator is not Zero             | 2    | 2   |

| JC                       | rel                   | Jump if Carry flag is set                   | 2    | 2   |

| JNC                      | rel                   | Jump if No Carry flag                       | 2    | 2   |

| JB                       | bit.rel               | Jump if direct Bit set                      | 3    | 2   |

| JNB                      | bit.rel               | Jump if direct Bit not set                  | 3    | 2   |

| JCB                      | bit.rel               | Jump if direct Bit is set and Clear bit     | 3    | 2   |

| CJNE                     | A.direct.rel          | Compare direct to A and Jump if not Equal   | 3    | 2   |

| CJNE                     | A.#data.rel           | Compare immed. to A and Jump if not Equal   | 3    | 2   |

| CJNE                     | Rn.#data.rel          | Compare immed. to reg and Jump if not Equal | 3    | 2   |

| CJNE                     | @Ri.#data.rel         | Compare immed. to ind and Jump if not Equal | 3    | 2   |

| DJNZ                     | Rn.rel                | Decrement register and Jump if not Zero     | 2    | 2   |

| DJNZ                     | direct.rel            | Decrement direct and Jump if not Zero       | 3    | 2   |

| NOP                      |                       | No operation                                | 1    | 1   |

#### FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

#### DESCRIPTION OF INSTRUCTIONS (CONTINUED)

#### **NOTES**

1. Notes on data processing modes:-

| Rn       | - | Working register R0-R7.                                              |

|----------|---|----------------------------------------------------------------------|

| direct   | - | 128 internal RAM Locations, any I/O port control or status register. |

| @Ri      | - | Indirect internal RAM location addressed by register R0 or R1.       |

| #data    | - | 8-bit constant included in instruction.                              |

| #data 16 | - | 16-bit constant included as bytes 2 and 3 of instruction.            |

| bit      | - | 128 software flags, any I/O pin, control or status bit.              |

|          |   |                                                                      |

- 2. Notes on programme addressing modes:

- addr 16 Destination address for LCALL and LJMP may be anywhere within the 64k programme memory address space.

- addr 11 Destination address for ACALL and AJMP will be within the same 2k page of programme memory as the first byte of the following instruction.

- rel SJMP and all conditional jumps include an 8-bit offset byte. Range is + 127 128 bytes relative to first byte of the following instruction.

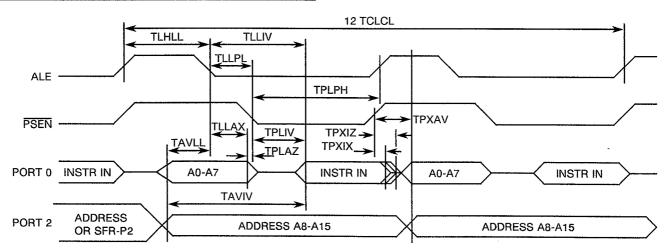

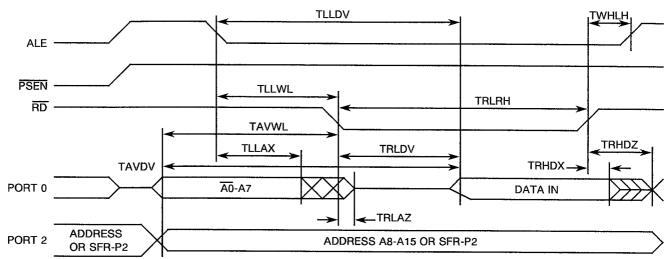

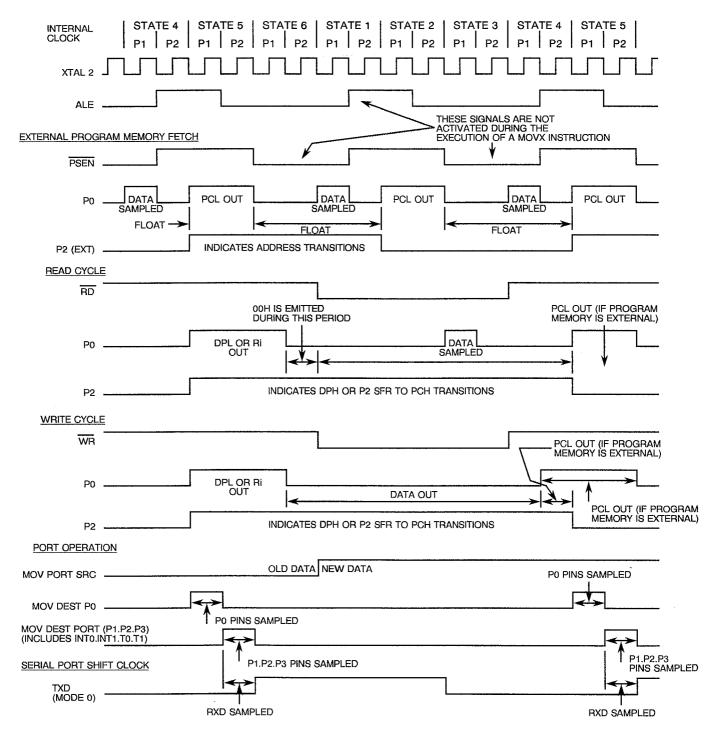

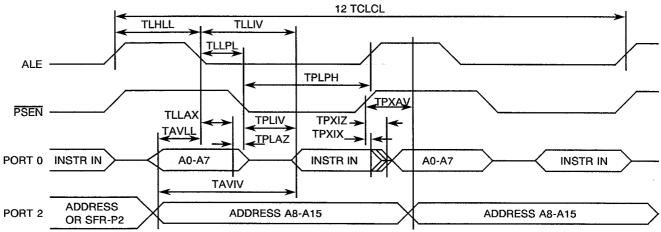

#### TIMING WAVEFORMS

#### EXTERNAL PROGRAMME MEMORY READ CYCLE

Rev. 'A'

#### FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

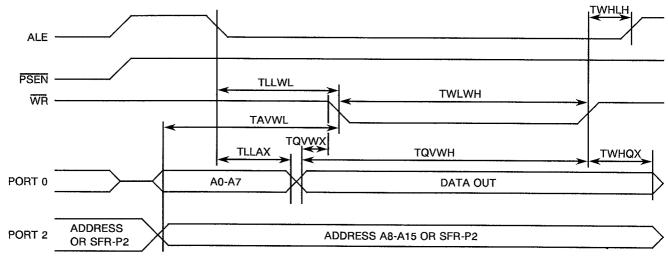

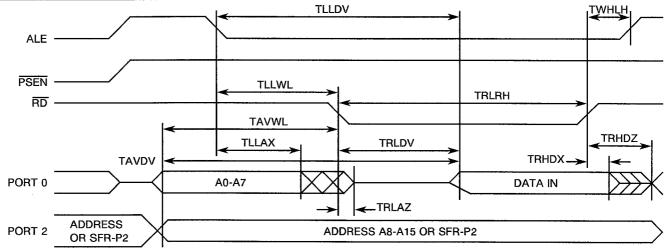

#### TIMING WAVEFORMS (CONTINUED)

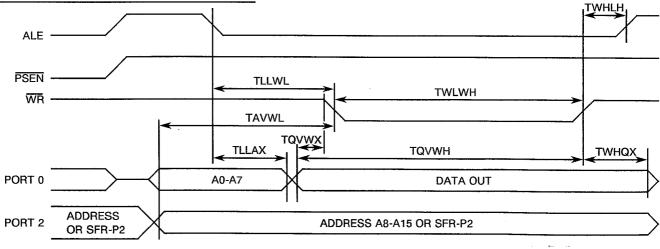

#### EXTERNAL DATA MEMORY WRITE CYCLE

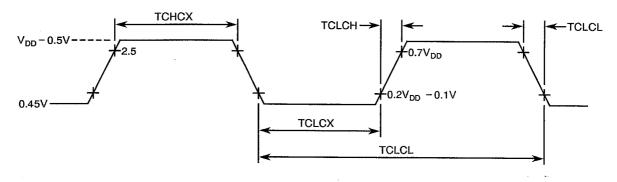

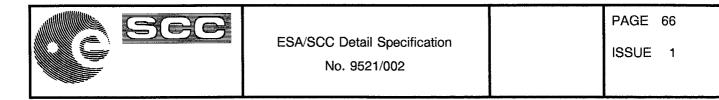

#### EXTERNAL CLOCK WAVEFORMS

. . .

#### FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

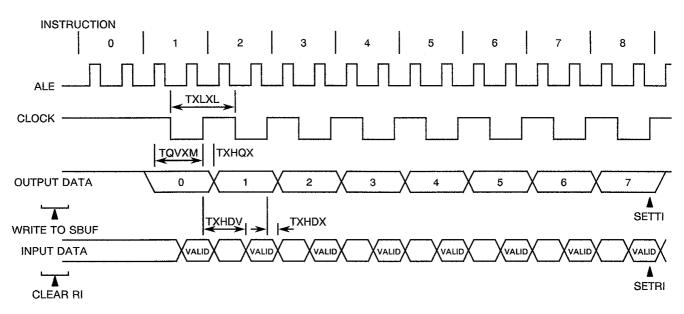

#### TIMING WAVEFORMS (CONTINUED)

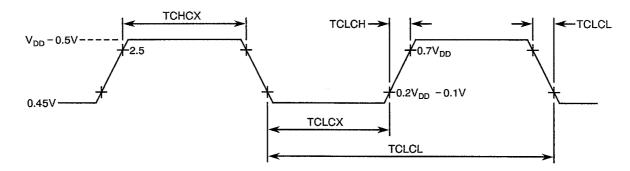

#### SHIFT REGISTER TIMING WAVEFORMS

| SYMBOL | PARAMETER                                | MIN.        | MAX.       | UNIT |

|--------|------------------------------------------|-------------|------------|------|

| TXLXL  | Serial Port Clock Time                   | 12TCLCL     | _          | μs   |

| TQVXH  | Output Data Setup to Clock Rising Edge   | 10TCLCL-133 | -          | ns   |

| TXHQX  | Output Data Hold After Clock Rising Edge | 2TCLCL-117  | -          | ns   |

| TXHDX  | Input Data Hold After Clock Rising Edge  | 0           | -          | ns   |

| TXHDV  | Clock Rising Edge to Input Data Valid    | -           | 10TLCL-133 | ns   |

#### FIGURE 3(b) - TRUTH TABLE/INSTRUCTION SET (CONTINUED)

#### TIMING WAVEFORMS (CONTINUED)

#### INTERNAL CLOCK WAVEFORMS

#### FIGURE 3(c) - CIRCUIT DESCRIPTION

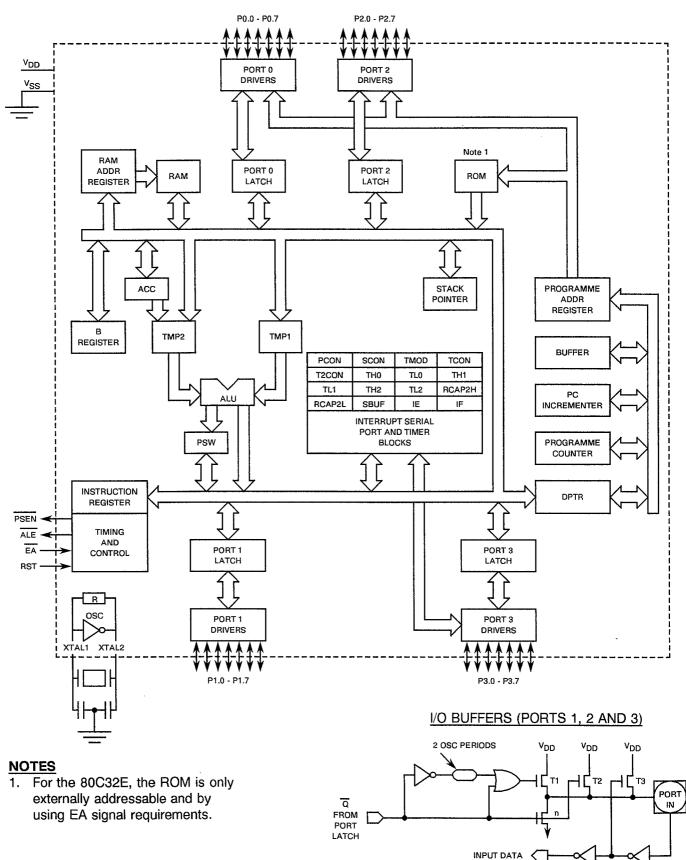

Port 0 - Port 0 is an 8-bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float and in that state can be used as high impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external programme and data memory. In this application, it uses strong internal pull-ups when emitting 1's. External pull-ups are required during programme verification. Port 0 can sink eight LS TTL inputs.

Port 0 also outputs the code bytes during programme verification in the 80C52E.

Port 1 - Port 1 is an 8-bit bi-directional I/O port with internal pull-ups. Port 1 pins that have 1's written to them are pulled high by the internal pull-ups, and in that state can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current because of the internal pull-ups.

Port 1 also receives the low-order address byte during programme verification. It can drive CMOS inputs without external pull-ups.

In the 80C52E, Port 1 can sink/source three LS TTL inputs.

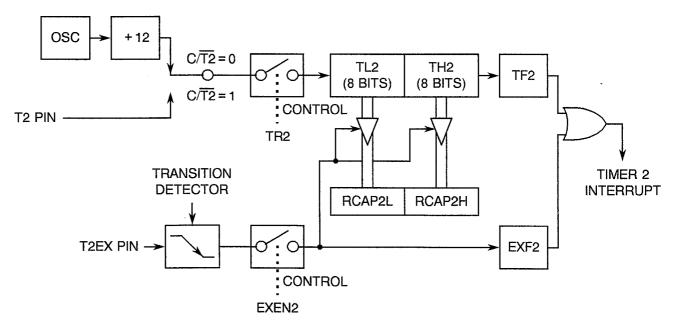

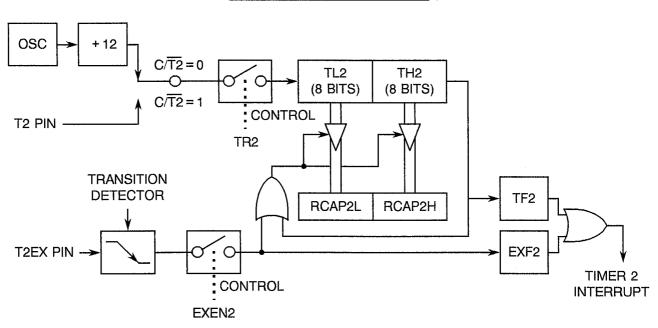

Two inputs of Port 1 are also used for Timer/Counter 2:

- P1.0 (T2): External clock inputs.

- P1.1 (T2EX): Trigger input to be reloaded or captured causing Timer/Counter 2 to interrupt.

- Port 2 Port 2 is an 8-bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1's written to them are pulled high by the internal pull-ups and in that state can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external Programme Memory and during accesses to external Data Memory that use 16-bit addresses. In this application, it uses strong internal pull-ups when emitting 1's. During access to external Data Memory that use 8-bit addresses, Port 2 emits the contents of the P2 Special Function Register.

Port 2 can sink/source three LS TTL inputs. It can drive CMOS inputs with external pull-ups.

In the 80C52E, Port 2 also receives the high-order address bits and control signals during programme verification

Port 3 - Port 3 is an 8-bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1's written to them are pulled high by the internal pull-ups and in that state can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current because of the pull-ups. It also serves the functions of various special features of the MCS-51 Family, as listed below.

| PORT PIN | ALTERNATE FUNCTION |                                     |  |  |

|----------|--------------------|-------------------------------------|--|--|

| P3.0     | RXD                | (Serial Input Port)                 |  |  |

| P3.1     | TXD                | (Serial Output Port)                |  |  |

| P3.2     | <b>INTO</b>        | (External Interrupt 0)              |  |  |

| P3.3     | INT1               | (External Interrupt 1)              |  |  |

| P3.4     | ТО                 | (Timer 0 External Input)            |  |  |

| P3.5     | T1                 | (Timer 1 External Input)            |  |  |

| P3.6     | WR                 | (External Data Memory Write Strobe) |  |  |

| P3.7     | RD                 | (External Data Memory Read Strobe)  |  |  |

Port 3 can sink/source three LS TTL inputs. It can drive CMOS inputs without external pull-ups.

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

- RST A high level on this for two machine cycles while the oscillator is running, resets the device. An internal pull-down resistor permits Power-On reset using only a capacitor connected to V<sub>DD</sub>. As soon as the reset is applied (V<sub>IN</sub>), Port 1, 2 and 3 are tied to "1". This operation is achieved asynchronously even if the oscillator does not startup.

- ALE Address Latch Enable output for latching the low byte of the address during accesses to external memory. ALE is activated as though for this purpose at a constant rate of 1/6 of the oscillator frequency except during an external data memory access at which time one ALE pulse is skipped. ALE can sink/source 8 LS TTL inputs. It can drive CMOS inputs without an external pull-up.

- I<sub>TL</sub> When an I/O pin on Ports 1, 2 and 3 is used as an input, the external circuit must sink current during the 1 to 0 transition. The maximum sink current is specified as I<sub>TL</sub>.

- IPD This is the power down I<sub>DD</sub> current when all output pins are disconnected.

- PSEN Programme Store Enable output is the read strobe to external Programme Memory. PSEN is activated twice each machine cycle during fetches from external Programme Memory (however, when executing out of external Programme Memory, two activations of PSEN are skipped during each access to external Data Memory). PSEN is not activated during fetches from internal Programme Memory. PSEN can sink/source 8 LS TTL inputs. It can drive CMOS inputs without an external pull-up.

- EA When EA is held high, the CPU executes out of internal Programme Memory (unless the Programme Counter exceeds 3FFFH). When EA is held low, the CPU executes only out of external Programme Memory. EA must not be floated.

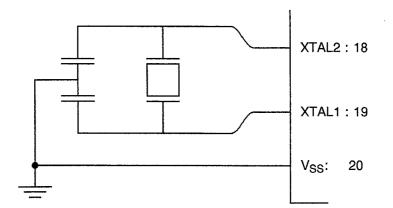

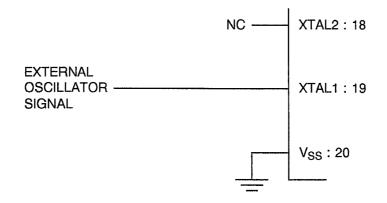

- XTAL1 Input to the inverting amplifier that forms the oscillator. Receives the external oscillator signal when an external oscillator is used.

- XTAL2 Output of the inverting amplifier that forms the oscillator and input of the internal clock generator. This pin should be floated when an external oscillator is used.

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

#### **OSCILLATOR CHARACTERISTICS**

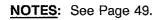

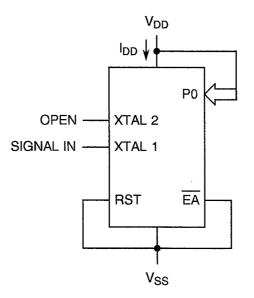

XTAL1 and XTAL2 are the input and output respectively, of an inverting amplifier which is configured for use as an on-chip oscillator, as shown in Figure 3(c)(i). Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected as shown in Figure 3(c)(ii). There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum high and low times specified must be observed.

#### FIGURE 3(c)(i) - CRYSTAL OSCILLATOR

#### FIGURE 3(c)(ii) - EXTERNAL DRIVE CONFIGURATION

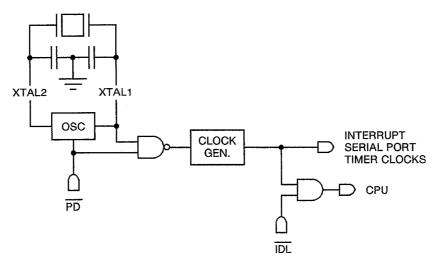

#### IDLE AND POWER DOWN OPERATION

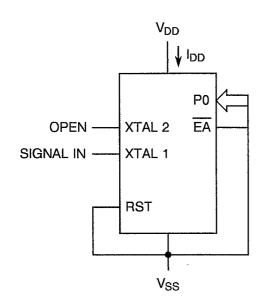

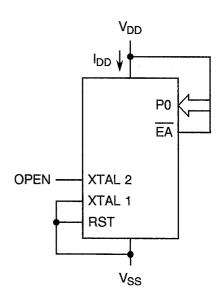

Figure 3(c)(iii) shows the internal Idle and Power Down clock configuration. As illustrated, Power Down operation stops the oscillator. Idle mode operation allows the interrupt, serial port and timer blocks to continue to function while the clock to the CPU is gated off.

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

The 80C52E has 2 additional software selectable modes of reduced activity for further reduction in power consumption as follows:-

- (a) In the Idle mode, the CPU is frozen while the RAM, timers, serial port and the interrupt system continue to function.

- (b) In the Power-down mode, the RAM is saved and all other functions are inoperative.

#### FIGURE 3(c)(iii) - IDLE AND POWER DOWN HARDWARE

These special modes are activated by software via the Special Function Register, PCON. Its hardware address is 87H. PCON is not bit addressable.

#### PCON: POWER CONTROL REGISTER

| (MSB)  |        |             |                                                                  |                |     |           | (LSB)        |  |  |

|--------|--------|-------------|------------------------------------------------------------------|----------------|-----|-----------|--------------|--|--|

| SMOD   | -      | -           | -                                                                | GF1            | GF0 | PD        | IDL          |  |  |

| SYMBOL | POSITI | <u>N NC</u> | NAME AND FUNCTION                                                |                |     |           |              |  |  |

| SMOD   | PCON.7 |             | ouble Baud ra                                                    |                |     |           | doubled when |  |  |

| -      | PCON.6 |             | eserved)                                                         | s being used i |     | 551,2013. |              |  |  |

| -      | PCON.  | 5 (r        | eserved)                                                         |                |     |           |              |  |  |

| -      | PCON.4 | 4 (r        | eserved)                                                         |                |     |           |              |  |  |

| GF1    | PCON.  | 3 G         | eneral-purpos                                                    | e flag bit.    |     |           |              |  |  |

| GF0    | PCON.2 | 2 G         | General-purpose flag bit.                                        |                |     |           |              |  |  |

| PD     | PCON.  | 1 P         | Power Down bit. Setting this bit activates power down operation. |                |     |           |              |  |  |

| IDL    | PCON.  | D Id        | Idle mode bit. Setting this bit activates idle mode operation.   |                |     |           |              |  |  |

If 1's are written to PD and IDL at the same time, PD takes precedence. The reset value of PCON is (000X0000).

- -- -

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

#### STATUS OF THE EXTERNAL PINS DURING IDLE AND POWER DOWN MODES

| MODE       | PROGRAMME<br>MEMORY | ALE | PSEN | PORT 0    | PORT 1    | PORT 2    | PORT 3    |

|------------|---------------------|-----|------|-----------|-----------|-----------|-----------|

| ldle       | Internal            | 1   | 1    | Port data | Port data | Port data | Port data |

| ldle       | External            | 1   | 1    | Floating  | Port data | Address   | Port data |

| Power down | Internal            | 0   | 0    | Port data | Port data | Port data | Port data |

| Power down | External            | 0   | 0    | Floating  | Port data | Port data | Port data |

#### IDLE MODE

The instruction that sets PCON.0 is the last instruction executed before the Idle mode is activated. Once in the Idle mode, the CPU status is preserved in its entirety: the Stack Pointer, Programme Counter, Programme Status Word, Accumulator, RAM and all other registers maintain their data during Idle. The table above describes the status of the external pins during Idle mode.

There are two ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating Idle mode. The interrupt is serviced, and following RET1, the next instruction to be executed will be the one following the instruction that wrote a 1 to PCON.0.

The flag bits GF0 and GF1 may be used to determine whether the interrupt was received during normal execution or during the ldle mode. For example, the instruction that writes to PCON.0 can also set or clear one or both flag bits. When ldle mode is terminated by an enabled interrupt, the service routine can examine the status of the flag bits.

The second way of terminating the Idle mode is with a hardware reset. Since the oscillator is still running, the hardware reset needs to be active for only 2 machine cycles (24 oscillator periods) to complete the reset operation.

#### POWER DOWN MODE

The instruction that sets PCON.1 is the last executed prior to entering power down. Once power is down, the oscillator is stopped. The contents of the on-chip RAM and the Special Function Register is saved during power down mode. A hardware reset initiates the Special Function Registers (see Table above).

In the Power Down mode,  $V_{DD}$  may be lowered to minimise circuit power consumption. Care must be taken to ensure the voltage is not reduced until the power down mode is entered and that the voltage is restored before the hardware reset is applied which frees the oscillator.

Reset should not be released until the oscillator has restarted and stabilised. The table above describes the status of the external pins while in the power down mode. It should be noted that if the power down mode is activated while in external programme memory, the port data that is held in the Special Function Register P2 is restored to Port 2. If the data is a 1, the port pin is held high during the power down mode by the strong pull-up.

#### STOP CLOCK MODE

Due to static design, the MHS80C32E and 80C52E clock speeds can be reduced to 0MHz without any data loss in memory or registers. This mode allows step by step utilisation and permits the reduction in system power consumption by bringing the clock frequency down to any value. At 0MHz, the power consumption is the same as in the Power Down Mode.

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)