Page 1 of 23

# INTEGRATED CIRCUITS, MONOLITHIC, CMOS SILICON-ON-SAPPHIRE, 6-BIT RF DIGITAL STEP ATTENUATOR, 500hm

# **BASED ON TYPE PE43652**

ESCC Detail Specification No. 9202/082

| Issue 1 | July 2014 |

|---------|-----------|

Document Custodian: European Space Agency - see https://escies.org

PAGE 2

### LEGAL DISCLAIMER AND COPYRIGHT

European Space Agency, Copyright © 2014. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

PAGE 3

No. 9202/082

**ISSUE 1**

### **DOCUMENTATION CHANGE NOTICE**

(Refer to https://escies.org for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION |

|---------|--------------------|

|         |                    |

### TABLE OF CONTENTS

| 1        | GENERAL                                                               | 5  |

|----------|-----------------------------------------------------------------------|----|

| 1.1      | SCOPE                                                                 | 5  |

| 1.2      | APPLICABLE DOCUMENTS                                                  | 5  |

| 1.3      | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS                  | 5  |

| 1.4      | THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS                 | 5  |

| 1.4.1    | The ESCC Component Number                                             | 5  |

| 1.4.2    | Component Type Variants                                               | 5  |

| 1.5      | MAXIMUM RATINGS                                                       | 6  |

| 1.6      | HANDLING PRECAUTIONS                                                  | 6  |

| 1.7      | PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION                       | 7  |

| 1.7.1    | Ceramic Quad Flat Package (CQFP-32) - 32 Terminals                    | 7  |

| 1.8      | FUNCTIONAL DIAGRAM                                                    | 8  |

| 1.9      | PIN ASSIGNMENT AND DESCRIPTION                                        | 9  |

| 1.10     | FUNCTIONAL DESCRIPTION                                                | 9  |

| 1.10.1   | Overview                                                              | 9  |

| 1.10.1.1 | Parallel/Serial Selection                                             | 10 |

| 1.10.1.2 | Serial Mode Interface                                                 | 10 |

| 1.10.1.3 | Parallel Mode Interface                                               | 12 |

| 1.10.1.4 | Reset Control                                                         | 13 |

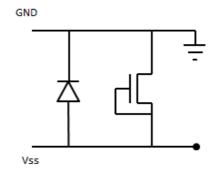

| 1.11     | INPUT AND OUTPUT PROTECTION NETWORKS                                  | 14 |

| 2        | REQUIREMENTS                                                          | 15 |

| 2.1      | GENERAL                                                               | 15 |

| 2.1.1    | Deviations from the Generic Specification                             | 15 |

| 2.1.1.1  | Deviations from Screening Tests - Chart F3                            | 15 |

| 2.2      | MARKING                                                               | 15 |

| 2.3      | ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES            | 15 |

| 2.3.1    | Room Temperature Electrical Measurements                              | 15 |

| 2.3.2    | High and Low Temperatures Electrical Measurements                     | 19 |

| 2.4      | PARAMETER DRIFT VALUES                                                | 19 |

| 2.5      | INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS                    | 20 |

| 2.6      | POWER BURN-IN CONDITIONS                                              | 20 |

| 2.7      | OPERATING LIFE CONDITIONS                                             | 21 |

| 2.8      | TOTAL DOSE RADIATION TESTING                                          | 21 |

| 2.8.1    | Bias Conditions and Total Dose Level for Total Dose Radiation Testing | 21 |

| 2.8.2    | Electrical Measurements for Total Dose Radiation Testing              | 22 |

| APPENDI  | X 'A'                                                                 | 23 |

PAGE 5 ISSUE 1

### 1 <u>GENERAL</u>

### 1.1 <u>SCOPE</u>

This specification details the ratings, physical and electrical characteristics and test and inspection data for the component type variants and/or the range of components specified below. It supplements the requirements of, and shall be read in conjunction with, the ESCC Generic Specification listed under Applicable Documents.

### 1.2 APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:

- (a) ESCC Generic Specification No. 9000.

- (b) MIL-STD-883, Test Methods and Procedures for Microelectronics.

#### 1.3 TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESCC Basic Specification No. 21300 shall apply.

#### 1.4 THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS

1.4.1 <u>The ESCC Component Number</u> The ESCC Component Number shall be constituted as follows:

Example: 920208201R

- Detail Specification Reference: 9202082

- Component Type Variant Number: 01

- Total Dose Radiation Level Letter: R (as required)

#### 1.4.2 Component Type Variants

The component type variants applicable to this specification are as follows:

| Variant<br>Number | Based on Type | Case    | Lead/Terminal Material and<br>Finish | Weight<br>max g | Total Dose<br>Radiation Level<br>Letter |

|-------------------|---------------|---------|--------------------------------------|-----------------|-----------------------------------------|

| 01                | PE43652       | CQFP-32 | G2                                   | 10              | R [100kRAD(Si)]                         |

The lead/terminal material and finish shall be in accordance with the requirements of ESCC Basic Specification No. 23500.

Total dose radiation level letters are defined in ESCC Basic Specification No. 22900. If an alternative radiation test level is specified in the Purchase Order the letter shall be changed accordingly.

PAGE 6

### 1.5 MAXIMUM RATINGS

The maximum ratings shall not be exceeded at any time during use or storage. Prolonged use of the device at the maximum ratings may reduce the device's overall reliability.

Maximum ratings shall only be exceeded during testing to the extent specified in this specification and when stipulated in Test Methods and Procedures of the ESCC Generic Specification.

| Characteristics                                                                             | Symbols          | Maximum Ratings              | Units      | Remarks |

|---------------------------------------------------------------------------------------------|------------------|------------------------------|------------|---------|

| Positive Power Supply Voltage<br>Range                                                      | V <sub>DD</sub>  | -0.3 to 4                    | V          | Note 1  |

| Negative Power Supply Voltage<br>Range                                                      | $V_{SS}$         | -3.7 to 0.3                  | V          | Note 2  |

| Voltage at any Digital Input                                                                | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> +0.3 | V          | Note 3  |

| Input Power (50Ω) Range<br>9kHz ≤ f <sub>in</sub> ≤ 20MHz<br>20MHz < f <sub>in</sub> ≤ 6GHz | P <sub>in</sub>  | +9<br>+23                    | dBm<br>dBm |         |

| Operating Temperature Range                                                                 | T <sub>op</sub>  | -40 to +85                   | °C         |         |

| Storage Temperature Range                                                                   | T <sub>stg</sub> | -65 to +150                  | °C         |         |

| Soldering Temperature                                                                       | T <sub>sol</sub> | +265                         | °C         | Note 4  |

### NOTES:

- 1. Device is functional for  $2.7V < V_{DD} < 3.6V$ .

- 2. Device is functional for  $-3.3V < V_{SS} < -2.7V$ .

- 3. Device is functional for 0V to  $V_{DD}$

- 4. Duration 10 seconds maximum at a distance of not less than 1.5mm form the device body and the same terminal shall not be re-soldered until 3 minutes have elapsed

### 1.6 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, shipment and any handling.

These components are categorised as Class 2 per ESCC Basic Specification No. 23800 with a minimum Critical Path Failure Voltage of 4000 Volts.

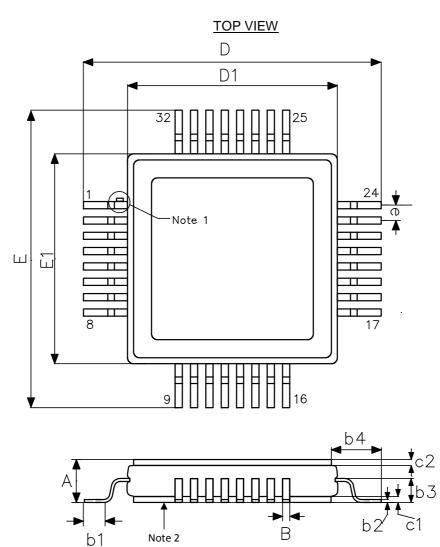

### 1.7 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

### 1.7.1 Ceramic Quad Flat Package (CQFP-32) - 32 Terminals

| Symbols | Dimensio | ons (mm) | Notes |

|---------|----------|----------|-------|

|         | Min      | Max      |       |

| A       | -        | 1.82     | 3     |

| В       | 0.25     | 0.35     | 3     |

| b1      | 0.88     | 3        |       |

| b2      | 0.1      | 0.16     | 3     |

| b3      | 0.76 T   | 3        |       |

| b4      | 2.26 T   | ypical   | 3     |

| c1      | 0.2      | 0.3      | 3     |

| c2      | 0.25 T   | ypical   |       |

| D/E     | 12.93    | 3        |       |

| D1 / E1 | -        | 8.89     |       |

| е       | 0.65     | BSC      | 3     |

PAGE 8

**ISSUE 1**

### NOTES:

- 1. A terminal 'pip' identification mark shall be located in the region of Pin 1 as shown. Terminal numbers shall increase counter clockwise when viewed from the top of the package.

- 2. The bottom of the package shall have a paddle (an exposed solder pad) for connection to ground.

- 3. Applies to all 32 terminals (8 per side).

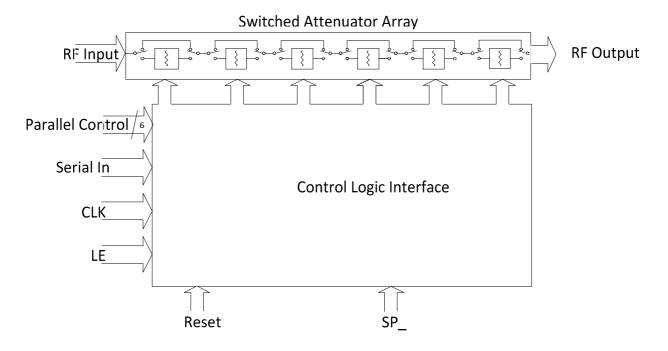

### 1.8 <u>FUNCTIONAL DIAGRAM</u>

### 1.9 PIN ASSIGNMENT AND DESCRIPTION

The table below describes each pin's assignment, type and standard, plus a brief description of its functionality.

| Pin<br>No. | Pin Name | Pin Type        | Pin<br>Standard | Serial/Parallel<br>Mode | Description                  |

|------------|----------|-----------------|-----------------|-------------------------|------------------------------|

| 1          | GND      | -               | -               | -                       | Ground                       |

| 2          | SP       | Digital Input   | CMOS            | Both                    | Serial/Parallel mode select  |

| 3          | RESET    | Digital Input   | CMOS            | Both                    | Reset to maximum attenuation |

| 4          | VDD      | Power Supply    | -               | -                       | Positive power supply pin    |

| 5          | GND      | -               | -               | -                       | Ground                       |

| 6          | RFIN     | Analogue Input  | RF              | Both                    | 50 $\Omega$ RF input port    |

| 7-18       | GND      | -               | -               | -                       | Ground                       |

| 19         | RFOUT    | Analogue Output | RF              | Both                    | 50 $\Omega$ RF output port   |

| 20         | GND      | -               | -               | -                       | Ground                       |

| 21         | VSS      | Power Supply    | -               | -                       | Negative power supply pin    |

| 22         | LE       | Digital Input   | CMOS            | Both                    | Transparent latch enable     |

| 23         | SI       | Digital Input   | CMOS            | Serial                  | Serial interface Data input  |

| 24         | GND      | -               | -               | -                       | Ground                       |

| 25         | CLK      | Digital Input   | CMOS            | Serial                  | Serial interface Clock input |

| 26         | D0       | Digital Input   | CMOS            | Parallel                | Parallel control bit: 0.25dB |

| 27         | D1       | Digital Input   | CMOS            | Parallel                | Parallel control bit: 0.5dB  |

| 28         | D2       | Digital Input   | CMOS            | Parallel                | Parallel control bit: 1dB    |

| 29         | D3       | Digital Input   | CMOS            | Parallel                | Parallel control bit: 2dB    |

| 30         | D4       | Digital Input   | CMOS            | Parallel                | Parallel control bit: 4dB    |

| 31         | D5       | Digital Input   | CMOS            | Parallel                | Parallel control bit: 8dB    |

| 32         | NC       | -               | -               | -                       | Not connected                |

| Paddle     | GND      | -               | -               | -                       | Ground                       |

### 1.10 FUNCTIONAL DESCRIPTION

### 1.10.1 <u>Overview</u>

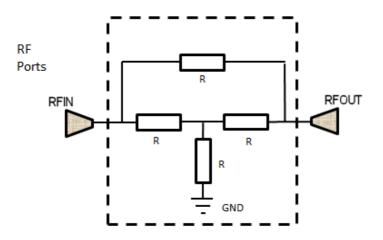

The PE43652 Digital Step Attenuator (DSA) consists of  $50\Omega$  resistive attenuators and CMOS/SOS RF switches to provide both high linearity and bandwidth. The switches are controlled via integrated CMOS logic.

#### 1.10.1.1 Parallel/Serial Selection

Either a parallel or serial-addressable interface can be used to control the DSA. The SP bit provides this selection, with SP = LOW selecting the parallel interface and SP = HIGH selecting the serial-addressable interface.

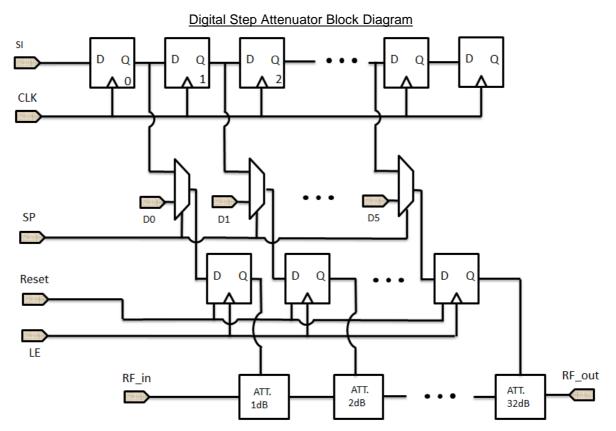

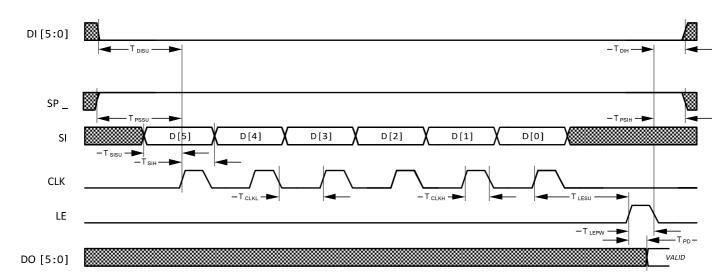

### 1.10.1.2 Serial Mode Interface

The serial-addressable interface is a 6-bit serial-in, parallel-out shift register buffered by a transparent latch. The 6-bits make up the Attenuation Word, which controls the state of the DSA.

The serial-addressable interface is controlled using three CMOS-compatible signals: Serial-In (SI), Clock (CLK), and Latch Enable (LE). The SI and CLK inputs allow data to be serially entered into the shift register. Serial data is clocked in MSB of the Attenuation word first.

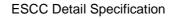

The shift register must be loaded while LE is held LOW to prevent the attenuator value from changing as data is entered. The LE input should then be toggled HIGH and brought LOW again, latching the new data into the DSA. The serial-addressable timing diagram is illustrated below.

PAGE 11

**ISSUE 1**

## Serial Mode Timing Diagram

Bits can either be set to logic high or logic low

| Symbol            | Parameter                                                               | Lin | nits | Unit |

|-------------------|-------------------------------------------------------------------------|-----|------|------|

|                   |                                                                         | Min | Max  |      |

| F <sub>CLK</sub>  | Serial clock frequency                                                  | -   | 10   | MHz  |

| T <sub>CLKH</sub> | Serial clock HIGH time                                                  | 30  | -    | ns   |

| T <sub>CLKL</sub> | Serial clock LOW time                                                   | 30  | -    | ns   |

| T <sub>LESU</sub> | Last serial clock rising edge setup<br>time to Latch Enable rising edge | 10  | -    | ns   |

| $T_{LEPW}$        | Latch Enable min. pulse width                                           | 30  | -    | ns   |

| T <sub>SISU</sub> | Serial data setup time                                                  | 10  | -    | ns   |

| T <sub>SIH</sub>  | Serial data hold time                                                   | 10  | -    | ns   |

| T <sub>DISU</sub> | Parallel data setup time                                                | 100 | -    | ns   |

| T <sub>DIH</sub>  | Parallel data hold time                                                 | 100 | -    | ns   |

| T <sub>PSSU</sub> | Parallel/Serial setup time                                              | 100 | -    | ns   |

| T <sub>PSH</sub>  | Parallel/Serial hold time                                               | 100 | -    | ns   |

| T <sub>PD</sub>   | Digital register delay (internal)                                       | -   | 10   | ns   |

Serial Mode Truth Table (Main Attenuation States)

|                           | Serial | Atten |    | Attenuation Setting |                          |                    |  |  |  |

|---------------------------|--------|-------|----|---------------------|--------------------------|--------------------|--|--|--|

| D5<br>(MSB)<br>(first in) | D4     | D3    | D2 | D1                  | D0<br>(LSB)<br>(last in) |                    |  |  |  |

| L                         | L      | L     | L  | L                   | L                        | 0dB (Reference IL) |  |  |  |

| L                         | L      | L     | L  | L                   | Н                        | 1dB                |  |  |  |

| L                         | L      | L     | L  | Н                   | L                        | 2dB                |  |  |  |

| L                         | L      | L     | Н  | L                   | L                        | 4dB                |  |  |  |

| L                         | L      | Н     | L  | L                   | L                        | 8dB                |  |  |  |

| L                         | Н      | L     | L  | L                   | L                        | 16dB               |  |  |  |

| Н                         | L      | L     | L  | L                   | L                        | 32dB               |  |  |  |

| Н                         | Н      | Н     | Н  | Н                   | Н                        | 63dB               |  |  |  |

### 1.10.1.3 Parallel Mode Interface

The parallel interface consists of six CMOS-compatible control lines that select the desired attenuation state.

For latched-parallel programming the Latch Enable (LE) should be held LOW while changing attenuation state control values, then pulse LE HIGH to LOW, to latch a new attenuation state into the device. Data is latched through to the attenuator elements on the rising edge of LE.

For direct parallel programming, the Latch Enable (LE) line should be pulled HIGH. Changing attenuation state control values will immediately change device state to new attenuation.

### Parallel Mode Timing Diagram

**ESCC** Detail Specification

No. 9202/082

**ISSUE 1**

PAGE 13

| Symbol            | Parameter                                           | Limits |     | Unit |

|-------------------|-----------------------------------------------------|--------|-----|------|

|                   |                                                     | Min    | Max |      |

| T <sub>LEPW</sub> | Latch Enable minimum pulse width                    | 30     | -   | ns   |

| T <sub>DISU</sub> | Parallel data setup time                            | 100    | -   | ns   |

| T <sub>DIH</sub>  | Parallel data hold time                             | 100    | -   | ns   |

| T <sub>PSSU</sub> | Parallel/Serial setup time                          | 100    | -   | ns   |

| T <sub>PSIH</sub> | Parallel/Serial hold time                           | 100    | -   | ns   |

| T <sub>PD</sub>   | Digital register delay (internal)                   | -      | 10  | ns   |

| T <sub>DIPD</sub> | Digital register delay (internal, direct mode only) | -      | 5   | ns   |

### Parallel Mode Truth Table (Main States)

| F           | Paralle | 1  | Attenuation |    |             |                       |

|-------------|---------|----|-------------|----|-------------|-----------------------|

| D5<br>(MSB) | D4      | D3 | D2          | D1 | D0<br>(LSB) | Setting               |

| L           | L       | L  | L           | L  | L           | 0dB (Reference<br>IL) |

| L           | L       | L  | L           | L  | Н           | 1dB                   |

| L           | L       | L  | L           | Н  | L           | 2dB                   |

| L           | L       | L  | Н           | L  | L           | 4dB                   |

| L           | L       | Н  | L           | L  | L           | 8dB                   |

| L           | Н       | L  | L           | L  | L           | 16dB                  |

| Н           | L       | L  | L           | L  | L           | 32dB                  |

| Н           | Н       | Н  | Н           | Н  | Н           | 63dB                  |

#### 1.10.1.4 Reset Control

While the RESET pin is held HIGH, the DSA will be held at the maximum attenuation setting (63dB). For both the serial-addressable and latched-parallel modes of operation the device will remain in this state until the RESET pin is returned LOW.

In direct-parallel mode, the DSA can be preset to any state within the maximum attenuation range by pre-setting the parallel control pins prior to power-up and tying the LE pin HIGH.

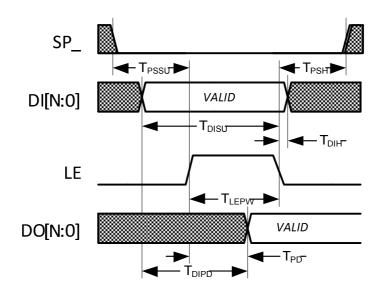

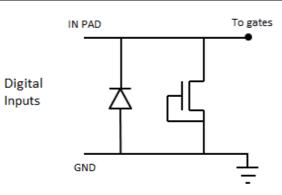

### 1.11 INPUT AND OUTPUT PROTECTION NETWORKS

Vdd

Vss

### 2 <u>REQUIREMENTS</u>

### 2.1 <u>GENERAL</u>

The complete requirements for procurement of the components specified herein are as stated in this specification and the ESCC Generic Specification.

### 2.1.1 Deviations from the Generic Specification

### 2.1.1.1 Deviations from Screening Tests - Chart F3

High Temperature Reverse Bias Burn-in and the subsequent Final Measurements for HTRB Burn-in shall be omitted.

### 2.2 <u>MARKING</u>

The marking shall be in accordance with the requirements of ESCC Basic Specification No. 21700 and as follows.

The information to be marked on the component shall be:

- (a) Terminal identification.

- (b) The ESCC qualified components symbol (for ESCC qualified components only).

- (c) The ESCC Component Number.

- (d) Traceability information.

- 2.3 <u>ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES</u> Electrical measurements shall be performed at room, high and low temperatures.

### 2.3.1 <u>Room Temperature Electrical Measurements</u> Electrical measurements shall be performed at $T_{amb} = +22 \pm 3^{\circ}C$ .

| Characteristics                                 | Symbols            | MIL-STD-883 | Test Conditions                                  | Lin     | Units |    |

|-------------------------------------------------|--------------------|-------------|--------------------------------------------------|---------|-------|----|

|                                                 |                    | Test Method | Note 1                                           | Min     | Max   |    |

| Continuity Check - V <sub>DD</sub>              | $V_{SH}$           | -           | $V_{DD} = V_{SS} = 0V$ $I_{IN} = -200 \mu A$     | -900    | -600  | mV |

| Continuity Check - V <sub>SS</sub>              | $V_{SH}$           | -           | $V_{DD} = V_{SS} = 0V$ $I_{IN} = -200 \mu A$     | 500     | 900   | mV |

| Continuity Check - Digital Inputs               | $V_{SH}$           | -           | $V_{DD} = V_{SS} = 0V$ $I_{IN} = -200 \mu A$     | -900    | -500  | mV |

| Continuity Check - Analogue<br>Input and Output | $V_{SH}$           | -           | $V_{DD} = V_{SS} = 0V$<br>$I_{IN} = -10mA$       | -1.1    | -0.3  | V  |

| Positive Supply Current with No<br>Attenuation  | I <sub>DD0dB</sub> | 3005        | Serial Mode, 0dB Attenuation                     | -       | 1     | mA |

| Negative Supply Current with No<br>Attenuation  | I <sub>SS0dB</sub> | 3005        | Serial Mode, 0dB Attenuation                     | -       | 10    | mA |

| Functional Test 1 - Nominal<br>Clock Duration   | -                  | 3014        | CLKH = CLKL = 50ns, f = 10MHz<br>Note 2          | Go/N    | loGo  | -  |

| Functional Test 2 - Clock HIGH<br>Duration      | -                  | 3014        | CLKH = 30ns, CLKL = 70ns,<br>f = 10MHz<br>Note 2 | Go/NoGo |       | -  |

### DC CHARACTERISTICS

PAGE 16

**ISSUE 1**

#### No. 9202/082

| Characteristics                                       | Symbols                | MIL-STD-883 Test Conditions Limit |                                                                                           | nits | Units |    |

|-------------------------------------------------------|------------------------|-----------------------------------|-------------------------------------------------------------------------------------------|------|-------|----|

|                                                       |                        | Test Method                       | Note 1                                                                                    | Min  | Max   |    |

| Functional Test 3 - Clock LOW<br>Duration             | -                      | 3014                              | CLKH = 70ns, CLKL = 30ns, Go/NoGo<br>f = 10MHz<br>Note 2                                  |      | NoGo  | -  |

| Input Voltage – HIGH Level -<br>Digital Inputs        | VIL                    | -                                 | RFIN = 400mV                                                                              | 800  | -     | mV |

| Input Voltage - HIGH Level -<br>Digital Inputs        | V <sub>IH</sub>        | -                                 | RFIN = 400mV                                                                              | -    | 1.9   | V  |

| Output Voltage -<br>Attenuation: 1dB                  | $V_{RFOUT1dB}$         | -                                 | 1dB Attenuation, RFIN = 400mV                                                             | 345  | 365   | mV |

| Output Voltage -<br>Attenuation: 2dB                  | $V_{RFOUT2dB}$         | -                                 | 2dB Attenuation, RFIN = 400mV                                                             | 280  | 305   | mV |

| Output Voltage -<br>Attenuation: 4dB                  | $V_{RFOUT4dB}$         | -                                 | 4dB Attenuation, RFIN = 400mV                                                             | 215  | 245   | mV |

| Output Voltage -<br>Attenuation: 8dB                  | $V_{RFOUT8dB}$         | -                                 | 8dB Attenuation, RFIN = 400mV                                                             | 135  | 165   | mV |

| Output Voltage -<br>Attenuation: 16dB                 | V <sub>RFOUT16dB</sub> | -                                 | 16dB Attenuation, RFIN = 400mV                                                            | 50   | 70    | mV |

| Output Voltage -<br>Attenuation: 32dB                 | V <sub>RFOUT32dB</sub> | -                                 | 32dB Attenuation, RFIN = 400mV                                                            | 5    | 10    | mV |

| Input Leakage Current, LOW<br>Level - Digital Inputs  | IIL                    | 3009                              | $V_{IN}$ (Under Test) = 0V<br>$V_{IN}$ (Remaining Inputs) = $V_{DD}$                      | -1   | 1     | nA |

| Input Leakage Current, HIGH<br>Level - Digital Inputs | I <sub>IH</sub>        | 3010                              | V <sub>IN</sub> (Under Test) = V <sub>DD</sub><br>V <sub>IN</sub> (Remaining Inputs) = 0V | 0    | 100   | nA |

### **RF CHARACTERISTICS**

|                                                                            |                     |                                                      |                                                                                     |      |      | 1  |

|----------------------------------------------------------------------------|---------------------|------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|----|

| Switching Time - Min to Max<br>Attenuation                                 | t <sub>on</sub>     | -                                                    | - $RF_{in} = +10dBm$ , f = 1GHz<br>LE = $V_{DD}/2$ to 10% RF <sub>in</sub> max      |      | 2700 | ns |

| Switching Time - Max to Min<br>Attenuation                                 | t <sub>off</sub>    | -                                                    | $RF_{in} = +10dBm, f = 1GHz$<br>LE = V <sub>DD</sub> /2 to 90% RF <sub>in</sub> max | 40   | 250  | ns |

| Output Rise Time - Max to Min<br>Attenuation                               | t <sub>rise</sub>   | -                                                    | RF <sub>in</sub> = +10dBm, f = 1GHz<br>10% to 90% RF <sub>in</sub> max              | 80   | 2200 | ns |

| Output Fall Time - Min to Max<br>Attenuation                               | t <sub>fall</sub>   | -                                                    | RF <sub>in</sub> = +10dBm, f = 1GHz<br>90% to 10% RF <sub>in</sub> max              | 40   | 550  | ns |

| Insertion Loss (at 10MHz)<br>(S-parameter: S21)                            | IL <sub>10M</sub>   | -                                                    | $P_{in} = +10 dBm, f = 10 MHz$                                                      | 0.5  | 3    | dB |

| Insertion Loss (at 1GHz)<br>(S-parameter: S21)                             | IL <sub>1000M</sub> | -                                                    | - P <sub>in</sub> = +10dBm, f = 1GHz                                                |      | 4.5  | dB |

| Insertion Loss (at 2GHz)<br>(S-parameter: S21)                             | IL <sub>2000M</sub> | -                                                    | - P <sub>in</sub> = +10dBm, f = 2GHz                                                |      | 4.5  | dB |

| Gain Compression at<br>Maximum P <sub>in</sub><br>(S-parameter: delta S21) | Pout                |                                                      | 0dB Attenuation, $f = 2GHz$<br>P <sub>in</sub> = +0dBm and +23dBm                   | 23.5 | 28.5 | dB |

| Monotonicity Error -<br>Attenuation: 4dB                                   | $ME_{4dB}$          | -                                                    | 4dB Attenuation, $f = 2.2GHz$<br>P <sub>in</sub> = +10dBm                           | -0.5 | 0.5  | dB |

| Monotonicity Error -<br>Attenuation: 8dB                                   | ME <sub>8dB</sub>   | - 8dB Attenuation, $f = 2.2GHz$<br>$P_{in} = +10dBm$ |                                                                                     | -0.5 | 0.5  | dB |

PAGE 17

**ISSUE 1**

### No. 9202/082

| Characteristics                                     | Symbols MIL-STD-883 Test Conditions |             | Limits                                                                  |      | Units |    |

|-----------------------------------------------------|-------------------------------------|-------------|-------------------------------------------------------------------------|------|-------|----|

|                                                     |                                     | Test Method | Note 1                                                                  | Min  | Max   |    |

| Input Return Loss (at 10MHz)<br>(S-parameter: S11)  | IRL <sub>10M</sub>                  | -           | P <sub>in</sub> = +10dBm, f = 10MHz                                     | -60  | -11   | dB |

| Input Return Loss (at 1GHz)<br>(S-parameter: S11)   | IRL <sub>1000M</sub>                | -           | P <sub>in</sub> = +10dBm, f = 1GHz                                      | -60  | -7    | dB |

| Input Return Loss (at 2GHz)<br>(S-parameter: S11)   | IRL <sub>2000M</sub>                | -           | P <sub>in</sub> = +10dBm, f = 2GHz                                      | -60  | -7    | dB |

| Output Return Loss (at 10MHz)<br>(S-parameter: S22) | ORL <sub>10M</sub>                  | -           | P <sub>in</sub> = +10dBm, f = 10MHz                                     | -60  | -11   | dB |

| Output Return Loss (at 1GHz)<br>(S-parameter: S22)  | ORL <sub>1000M</sub>                | -           | P <sub>in</sub> = +10dBm, f = 1GHz                                      | -60  | -6.5  | dB |

| Output Return Loss (at 2GHz)<br>(S-parameter: S22)  | ORL2000M                            | -           | P <sub>in</sub> = +10dBm, f = 2GHz                                      | -60  | -6.5  | dB |

| Third Order Intercept Point -<br>Attenuation: 0dB   | IIP3 <sub>0dB</sub>                 | -           | 0dB Attenuation, $P_{in} = +18dBm$<br>f1 = 895MHz & f2 = 905MHz         | 45   | 75    | dB |

| Third Order Intercept Point -<br>Attenuation: 1dB   | IIP3 <sub>1dB</sub>                 | -           | 1dB Attenuation, $P_{in} = +18dBm$<br>f1 = 895MHz & f2 = 905MHz         | 45   | 75    | dB |

| Third Order Intercept Point -<br>Attenuation: 2dB   | IIP3 <sub>2dB</sub>                 | -           | 2dB Attenuation, P <sub>in</sub> = +18dBm<br>f1 = 895MHz & f2 = 905MHz  | 45   | 75    | dB |

| Third Order Intercept Point -<br>Attenuation: 4dB   | IIP3 <sub>4dB</sub>                 | -           | 4dB Attenuation, P <sub>in</sub> = +18dBm<br>f1 = 895MHz & f2 = 905MHz  | 45   | 75    | dB |

| Third Order Intercept Point -<br>Attenuation: 8dB   | IIP3 <sub>8dB</sub>                 | -           | 8dB Attenuation, P <sub>in</sub> = +18dBm<br>f1 = 895MHz & f2 = 905MHz  | 45   | 75    | dB |

| Third Order Intercept Point -<br>Attenuation: 16dB  | IIP3 <sub>16dB</sub>                | -           | 16dB Attenuation, P <sub>in</sub> = +18dBm<br>f1 = 895MHz & f2 = 905MHz | 45   | 75    | dB |

| Third Order Intercept Point -<br>Attenuation: 32dB  | IIP3 <sub>32dB</sub>                | -           | 32dB Attenuation, P <sub>in</sub> = +18dBm<br>f1 = 895MHz & f2 = 905MHz | 45   | 75    | dB |

| Attenuation Error (at 10MHz) -<br>Attenuation: 0dB  | AE0dB <sub>10M</sub>                | -           | 0dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 10MHz                  | -0.5 | 0.5   | dB |

| Attenuation Error (at 1GHz) -<br>Attenuation: 0dB   | AE0dB <sub>1000M</sub>              | -           | 0dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 1GHz                   | -0.5 | 0.5   | dB |

| Attenuation Error (at 2GHz) -<br>Attenuation: 0dB   | AE0dB <sub>2000M</sub>              | -           | 0dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 2GHz                   | -0.5 | 0.5   | dB |

| Attenuation Error (at 4GHz) -<br>Attenuation: 0dB   | AE0dB <sub>4000M</sub>              | -           | 0dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 4GHz                   | -0.5 | 0.5   | dB |

| Attenuation Error (at 6GHz) -<br>Attenuation: 0dB   | AE0dB <sub>6000M</sub>              | -           | 0dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 6GHz                   | -0.5 | 0.5   | dB |

| Attenuation Error (at 10MHz) -<br>Attenuation: 1dB  | AE1dB <sub>10M</sub>                | -           | 1dB Attenuation, $P_{in} = +10$ dBm<br>f = 10MHz                        |      | 0.5   | dB |

| Attenuation Error (at 1GHz) -<br>Attenuation: 1dB   | AE1dB <sub>1000M</sub>              | -           |                                                                         |      | 0.5   | dB |

| Attenuation Error (at 2GHz) -<br>Attenuation: 1dB   | AE1dB <sub>2000M</sub>              | -           | - 1dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 2GHz                 |      | 0.5   | dB |

| Attenuation Error (at 4GHz) -<br>Attenuation: 1dB   | AE1dB <sub>4000M</sub>              | -           | 1dB Attenuation, $P_{in} = +10$ dBm<br>f = 4GHz                         |      | 0.9   | dB |

| Attenuation Error (at 6GHz) -<br>Attenuation: 1dB   | AE1dB <sub>6000M</sub>              | -           | 1dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 6GHz                   | -0.5 | 0.9   | dB |

Characteristics

Attenuation Error (at 10MHz) -

Attenuation Error (at 1GHz) -

Attenuation Error (at 2GHz) -

Attenuation: 32dB

Attenuation: 32dB

Attenuation: 32dB

AE32dB<sub>10M</sub>

AE32dB1000M

AE32dB<sub>2000M</sub>

-

-

-

### **ISSUE 1**

Limits

Units

#### No. 9202/082

**Test Conditions**

32dB Attenuation,  $P_{in} = +10$ dBm

32dB Attenuation,  $P_{in} = +10$ dBm

32dB Attenuation,  $P_{in} = +10$ dBm

f = 10MHz

f = 1GHz

f = 2GHz

-1.4

-1.7

-1.7

1.3

1.5

1.6

dB

dB

dB

MIL-STD-883

Symbols

| Onarabicitistics                                    | Test Method             |                                                          |                                                          | Ennits |     | Office |  |

|-----------------------------------------------------|-------------------------|----------------------------------------------------------|----------------------------------------------------------|--------|-----|--------|--|

|                                                     |                         |                                                          | Note 1                                                   | Min    | Max |        |  |

| Attenuation Error (at 10MHz) -<br>Attenuation: 2dB  | AE2dB <sub>10M</sub>    | -                                                        | 2dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 10MHz   | -0.5   | 0.5 | dB     |  |

| Attenuation Error (at 1GHz) -<br>Attenuation: 2dB   | AE2dB <sub>1000M</sub>  | -                                                        | 2dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 1GHz    | -0.5   | 0.5 | dB     |  |

| Attenuation Error (at 2GHz) -<br>Attenuation: 2dB   | AE2dB <sub>2000M</sub>  | -                                                        | 2dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 2GHz    | -0.5   | 0.5 | dB     |  |

| Attenuation Error (at 4GHz) -<br>Attenuation: 2dB   | AE2dB <sub>4000M</sub>  | -                                                        | 2dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 4GHz    | -1.1   | 1   | dB     |  |

| Attenuation Error (at 6GHz) -<br>Attenuation: 2dB   | AE2dB <sub>6000M</sub>  | -                                                        | 2dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 6GHz    | -1.1   | 1.1 | dB     |  |

| Attenuation Error (at 10MHz) -<br>Attenuation: 4dB  | AE4dB <sub>10M</sub>    | -                                                        | 4dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 10MHz   | -0.5   | 0.5 | dB     |  |

| Attenuation Error (at 1GHz) -<br>Attenuation: 4dB   | AE4dB <sub>1000M</sub>  | -                                                        | 4dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 1GHz    | -0.5   | 0.5 | dB     |  |

| Attenuation Error (at 2GHz) -<br>Attenuation: 4dB   | AE4dB <sub>2000M</sub>  | -                                                        | 4dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 2GHz    | -0.7   | 0.5 | dB     |  |

| Attenuation Error (at 4GHz) -<br>Attenuation: 4dB   | AE4dB <sub>4000M</sub>  | -                                                        | - 4dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 4GHz  |        | 1   | dB     |  |

| Attenuation Error (at 6GHz) -<br>Attenuation: 4dB   | AE4dB <sub>6000M</sub>  | -                                                        | - 4dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 6GHz  |        | 1.2 | dB     |  |

| Attenuation Error (at 10MHz) -<br>Attenuation: 8dB  | AE8dB <sub>10M</sub>    | -                                                        | 8dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 10MHz   | -0.6   | 0.7 | dB     |  |

| Attenuation Error (at 1GHz) -<br>Attenuation: 8dB   | AE8dB <sub>1000M</sub>  | -                                                        | 8dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 1GHz    | -1.1   | 0.7 | dB     |  |

| Attenuation Error (at 2GHz) -<br>Attenuation: 8dB   | AE8dB <sub>2000M</sub>  | -                                                        | 8dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 2GHz    | -1.2   | 0.7 | dB     |  |

| Attenuation Error (at 4GHz) -<br>Attenuation: 8dB   | AE8dB <sub>4000M</sub>  | -                                                        | 8dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 4GHz    | -2.9   | 1.2 | dB     |  |

| Attenuation Error (at 6GHz) -<br>Attenuation: 8dB   | AE8dB <sub>6000M</sub>  | -                                                        | 8dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 6GHz    | -3     | 1.2 | dB     |  |

| Attenuation Error (at 10MHz) -<br>Attenuation: 16dB | AE16dB <sub>10M</sub>   | -                                                        | 16dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 10MHz  | -0.8   | 0.9 | dB     |  |

| Attenuation Error (at 1GHz) -<br>Attenuation: 16dB  | AE16dB <sub>1000M</sub> | -                                                        | - 16dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 1GHz |        | 1   | dB     |  |

| Attenuation Error (at 2GHz) -<br>Attenuation: 16dB  | AE16dB <sub>2000M</sub> | - 16dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 2GHz |                                                          | -1.4   | 1   | dB     |  |

| Attenuation Error (at 4GHz) -<br>Attenuation: 16dB  | AE16dB <sub>4000M</sub> | -                                                        |                                                          |        | 2   | dB     |  |

| Attenuation Error (at 6GHz) -<br>Attenuation: 16dB  | AE16dB <sub>6000M</sub> | -                                                        | 16dB Attenuation, $P_{in} = +10dBm$<br>f = 6GHz          | -3     | 4.3 | dB     |  |

| [                                                   |                         |                                                          |                                                          |        |     |        |  |

PAGE 19

**ISSUE 1**

| Characteristics                                           | Symbols MIL-STD-883      |             | Test Conditions                                                | Limits |     | Units |

|-----------------------------------------------------------|--------------------------|-------------|----------------------------------------------------------------|--------|-----|-------|

|                                                           |                          | Test Method | Note 1                                                         | Min    | Max |       |

| Attenuation Error (at 4GHz) -<br>Attenuation: 32dB        | AE32dB <sub>4000M</sub>  | -           | 32dB Attenuation, P <sub>in</sub> = +10dBm<br>f = 4GHz         | -3.3   | 6   | dB    |

| Attenuation Error (at 10MHz) -<br>Attenuation: Max (63dB) | AEMaxdB <sub>10M</sub>   | -           | Max (63dB) Attenuation,<br>P <sub>in</sub> = +10dBm, f = 10MHz | -8     | 5.5 | dB    |

| Attenuation Error (at 1GHz) -<br>Attenuation: Max (63dB)  | AEMaxdB <sub>1000M</sub> | -           | Max (63dB) Attenuation,<br>P <sub>in</sub> = +10dBm, f = 1GHz  | 7.5    | 13  | dB    |

| Attenuation Error (at 2GHz) -<br>Attenuation: Max (63dB)  | AEMaxdB <sub>2000M</sub> | -           | Max (63dB) Attenuation,<br>P <sub>in</sub> = +10dBm, f = 2GHz  | 14     | 19  | dB    |

### NOTES:

- 1. Unless otherwise specified:

- Each characteristic shall be tested for both  $V_{DD} = 2.7V$ ,  $V_{SS} = -2.7V$  and  $V_{DD} = 3.6V$ ,  $V_{SS} = -3.3V$ .

- All inputs and outputs shall be tested for each characteristic (as applicable).

- Digital input conditions shall be  $V_{IH} = V_{DD}$ ,  $V_{IL} = 0V$ .

- Inputs not under test shall be  $V_{IN} = V_{SS}$  or  $V_{DD}$  and outputs not under test shall be open.

- 2. Functional testing shall be performed using suitable test patterns to verify correct function per truth table and timing diagram requirements.

### 2.3.2 <u>High and Low Temperatures Electrical Measurements</u> Electrical measurements shall be performed at $T_{amb} = +85 (+0.5)^{\circ}C$ and $T_{amb} = -40 (+5.0)^{\circ}C$

The characteristics, test methods, conditions and limits shall be the same as specified for Room Temperature Electrical Measurements.

### 2.4 PARAMETER DRIFT VALUES

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$  = +22 ±3°C.

The test methods and test conditions shall be as per the corresponding test defined in Room Temperature Electrical Measurements.

The drift values ( $\Delta$ ) shall not be exceeded for each characteristic specified. The corresponding absolute limit values for each characteristic shall not be exceeded.

| Characteristics                   | Symbols               |                | Limits   | Units |    |

|-----------------------------------|-----------------------|----------------|----------|-------|----|

|                                   |                       | Drift<br>Value | Absolute |       |    |

|                                   |                       | Δ              | Min      | Max   |    |

| Output Voltage - Attenuation: 2dB | $V_{RFOUT2dB}$        | ±2%            | 280      | 305   | mV |

| Output Voltage - Attenuation: 4dB | $V_{RFOUT4dB}$        | ±3%            | 215      | 245   | mV |

| Output Voltage - Attenuation: 8dB | V <sub>RFOUT8dB</sub> | ±5%            | 135      | 165   | mV |

PAGE 20 ISSUE 1

### 2.5 INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$  = +22 ±3°C.

The characteristics, test methods, conditions and limits shall be as specified for Room Temperature Electrical Measurements.

In addition, the drift values ( $\Delta$ ) for the following characteristics shall not be exceeded:

| Characteristics                   | Symbols               | Drift<br>Value $\Delta$ | Units |

|-----------------------------------|-----------------------|-------------------------|-------|

| Output Voltage - Attenuation: 2dB | $V_{RFOUT2dB}$        | ±2%                     | mV    |

| Output Voltage - Attenuation: 4dB | $V_{RFOUT4dB}$        | ±3%                     | mV    |

| Output Voltage - Attenuation: 8dB | V <sub>RFOUT8dB</sub> | ±5%                     | mV    |

### 2.6 POWER BURN-IN CONDITIONS

| Characteristics                                | Symbols          | Test Conditions                                  | Units | Notes |

|------------------------------------------------|------------------|--------------------------------------------------|-------|-------|

| Ambient Temperature                            | T <sub>amb</sub> | +125 (+0 -5)                                     | °C    |       |

| Positive Supply Voltage (VDD)                  | V <sub>DD</sub>  | +3.3 (+0 -5 %)                                   | V     |       |

| Negative Supply Voltage (VSS)                  | V <sub>SS</sub>  | -2.7 (+0 -5 %)                                   | V     |       |

| Analogue Input (RFIN)                          | P <sub>in</sub>  | 10MHz sine wave,<br>$V_{CM} = 0V, V_{pp} = 3.0V$ | V     | 1     |

| Analogue Output Load (RFOUT)                   | RL               | High Impedance                                   | -     |       |

| Digital Inputs (SP, RESET, LE, SI,<br>CLK, Dn) | V <sub>IN</sub>  | 0 or $V_{DD}$                                    | V     | 2     |

| Vector Length                                  | t <sub>o</sub>   | 1                                                | μs    | 2     |

### NOTES:

1. The RF input signal shall be fed through a suitable series capacitor.

2. The device shall be burned-in using 'functional' vectors that are looping indefinitely in order to exercise the DUT through various attenuation states in both parallel and serial modes. There shall be 10 different vectors in each sequence with a vector length as specified, as follows:

| Vector<br>Number | Series/Parallel<br>Mode | Attenuation<br>Word | Comment                 |

|------------------|-------------------------|---------------------|-------------------------|

| 1                | Parallel                | 000000              | Attenuation: 0db        |

| 2                | Parallel                | 101010              | Attenuation: 42dB       |

| 3                | Parallel                | 111111              | Attenuation: Max (63dB) |

| 4                | Parallel                | 010101              | Attenuation: 21dB       |

| 5                | Parallel                | 000000              | Attenuation: 0db        |

| 6                | Serial                  | 000000              | Attenuation: 0db        |

| 7                | Serial                  | 101010              | Attenuation: 42dB       |

| 8                | Serial                  | 111111              | Attenuation: Max (63B)  |

| 9                | Serial                  | 010101              | Attenuation: 21dB       |

| 10               | Serial                  | 000000              | Attenuation: 0db        |

### 2.7 OPERATING LIFE CONDITIONS

The conditions shall be as specified for Power Burn-in.

### 2.8 TOTAL DOSE RADIATION TESTING

2.8.1 <u>Bias Conditions and Total Dose Level for Total Dose Radiation Testing</u> Components shall be biased in both ON and OFF configurations as detailed below. The required test samples shall be divided equally between both bias configurations.

The total dose level applied shall be as specified in the component type variant information herein or in the Purchase Order.

Bias conditions:

- OFF Configuration Continuous Bias Conditions: All terminals shall be connected to ground with  $T_{amb}$  = +22 ±3°C.

- ON Configuration Continuous Bias Conditions:

| Characteristics                                                | Symbols          | Test Conditions              | Units |

|----------------------------------------------------------------|------------------|------------------------------|-------|

| Ambient Temperature                                            | T <sub>amb</sub> | +22 ±3                       | °C    |

| Positive Supply Voltage (VDD)                                  | V <sub>DD</sub>  | +3.3 (+0 -5 %)               | V     |

| Negative Supply Voltage (VSS)                                  | V <sub>SS</sub>  | -3.0 (+0 -5 %)               | V     |

| Analogue Input (RFIN)                                          | P <sub>in</sub>  | +10dBm minimum,<br>f ≥ 10MHz | -     |

| Analogue Output Load (RFOUT)                                   | RL               | 50                           | Ω     |

| Digital Input : D3 (Attenuation: 8dB)                          | V <sub>IN</sub>  | V <sub>DD</sub>              | V     |

| Digital Inputs : SP, RESET, LE, SI,<br>CLK, D0, D1, D2, D4, D5 | V <sub>IN</sub>  | 0                            | V     |

PAGE 22 ISSUE 1

2.8.2 <u>Electrical Measurements for Total Dose Radiation Testing</u>

Prior to irradiation testing the devices shall have successfully met Room Temperature Electrical Measurements specified herein.

Unless otherwise specified the measurements shall be performed at  $T_{amb}$  = +22 ±3°C.

The test methods and test conditions shall be as per the corresponding test defined in Electrical Measurements at Room temperature.

The parameters to be measured during and on completion of irradiation testing are shown below.

| Characteristics                                | Symbols            | Limits |     | Units |

|------------------------------------------------|--------------------|--------|-----|-------|

|                                                |                    | Min    | Max |       |

| Positive Supply Current with No<br>Attenuation | I <sub>DD0dB</sub> | -      | 1   | mA    |

| Negative Supply Current with No<br>Attenuation | I <sub>SS0dB</sub> | -      | 10  | mA    |

### DC CHARACTERISTICS

### **RF CHARACTERISTICS**

| Insertion Loss (at 10MHz)<br>(S-parameter: S21)<br>Note 1 | IL <sub>10M</sub>   | 0.5 | 3   | dB |

|-----------------------------------------------------------|---------------------|-----|-----|----|

| Insertion Loss (at 1GHz)<br>(S-parameter: S21)<br>Note 1  | IL <sub>1000M</sub> | 0.5 | 4.5 | dB |

| Insertion Loss (at 2GHz)<br>(S-parameter: S21)<br>Note 1  | IL <sub>2000M</sub> | 0.5 | 4.5 | dB |

### NOTES:

1. S-parameter characteristics shall only be measured on completion of irradiation testing.

ESCC Detail Specification

No. 9202/082

PAGE 23

**ISSUE 1**

# APPENDIX 'A'

### AGREED DEVIATIONS FOR PEREGRINE SEMICONDUCTOR EUROPE (GB)

| ITEMS AFFFECTED                                                                    | DESCRIPTION OF DEVIATIONS                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deviations from Screening<br>Tests – Chart F3                                      | Following PIND, additional Seal (Fine and Gross Leak) and External Visual Inspection may also be performed.                                                                                                                                                                                                                                                                   |

|                                                                                    | Initial High and Low Temperatures Electrical Measurements may also be performed prior to Burn-in.                                                                                                                                                                                                                                                                             |

| Deviations from Screening<br>Tests – Chart F3 &<br>Para. 7.1.1                     | For components that form part of the delivery lot, lead crop and form may be performed at any point prior to final Seal.                                                                                                                                                                                                                                                      |

|                                                                                    | Measurement of characteristics in the RF Characteristics section of either<br>Room Temperature Electrical Measurements or High and Low<br>Temperatures Electrical Measurements, may be performed separately<br>from the DC Characteristics, subsequent to lead crop and form.                                                                                                 |

|                                                                                    | Selection of components to be subjected to Qualification and Periodic<br>Tests may be performed prior to the completion of Screening Tests.                                                                                                                                                                                                                                   |

|                                                                                    | For components that will be subjected to Qualification and Periodic Tests,<br>lead crop and form may not be performed during Screening Tests.<br>Accordingly, characteristics in the RF Characteristics section of either<br>Room Temperature Electrical Measurements or High and Low<br>Temperatures Electrical Measurements, may not be measured during<br>Screening Tests. |

| Deviations from Screening<br>Tests – Chart F3 &<br>Paras. 6.2.3 & 6.4.1            | Any failures that occur during measurement of characteristics in the RF<br>Characteristics section of either Room Temperature Electrical<br>Measurements or High and Low Temperatures Electrical Measurements,<br>may not be counted as parameter limit failures during Check for Lot<br>Failure.                                                                             |

| Deviations from Screening<br>Tests – Chart F3 &<br>Para. 9.7                       | Radiographic Inspection shall be performed in accordance with ESCC<br>Basic Specification No. 20900. The Manufacturer may perform the<br>inspection at any point during Screening Tests subsequent to Serialisation<br>and prior to final Seal.                                                                                                                               |

|                                                                                    | Radiographic Inspection photographic results shall be recorded against component serial number and included in the data documentation package.                                                                                                                                                                                                                                |

| Deviations from<br>Qualification and Periodic<br>Tests – Chart F4 &<br>Para. 7.6.2 | Lead crop and form may be performed at any point during Qualification and Periodic Tests.                                                                                                                                                                                                                                                                                     |

|                                                                                    | Measurement of characteristics in the RF Characteristics section of<br>Intermediate and End-Point Electrical Measurements may be performed<br>separately from the DC Characteristics, subsequent to lead crop and form.<br>Any failures of RF Characteristics may not be counted as electrical failures<br>when determining lot failure.                                      |

|                                                                                    | Permanence of Marking may not be performed on devices which have been laser marked.                                                                                                                                                                                                                                                                                           |