Pages 1 to 13

# MICROSECTION EXAMINATION PREPARATION AND EVALUATION OF CAPACITORS FIXED CERAMIC LEADED AND CHIPS

**ESCC Basic Specification No. 23400**

Issue 2 April 2003

## LEGAL DISCLAIMER AND COPYRIGHT

European Space Agency, Copyright © 2003. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

ISSUE 2

# **DOCUMENTATION CHANGE NOTICE**

(Refer to https://escies.org for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION                                               |

|---------|------------------------------------------------------------------|

| 51      | Specification upissued to incorporate editorial changes per DCR. |

## ISSUE 2

# TABLE OF CONTENTS

| <u>1.</u>                                                                                      | SCOPE                                                                                                                                                                                                                                                                                | <u>5</u>                                       |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| <u>2.</u>                                                                                      | <u>PURPOSE</u>                                                                                                                                                                                                                                                                       | <u>5</u>                                       |

| <u>3.</u>                                                                                      | TERMS AND DEFINITIONS                                                                                                                                                                                                                                                                | <u>5</u>                                       |

| 3.6<br>3.7<br>3.8<br>3.9                                                                       | Sample Specimen Manufacturing Lot Chip Decapsulation Length Delamination Void Crack Margin Cover Plate                                                                                                                                                                               | 5 5 5 5 5 6 6 6 6 6 6 6                        |

| <u>4.</u>                                                                                      | SPECIMEN PREPARATION                                                                                                                                                                                                                                                                 | <u>6</u>                                       |

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4<br>4.5.5<br>4.5.6<br>4.5.7 | Introduction Mounting Specimen Grinding (or Cutting) Specimen Polishing Specimen Preparation Problems Excessive Pull-out Indined Component Mounting Cover Plate Cracking Dielectric Material Pull-out Small Delaminations Grinding Scratches (Inadequate Polishing) Component Relief | 6<br>7<br>8<br>8<br>8<br>9<br>9<br>9<br>9<br>9 |

| <u>5.</u>                                                                                      | INSPECTION REQUIREMENTS                                                                                                                                                                                                                                                              | <u>9</u>                                       |

| 5.1<br>5.2<br>5.3                                                                              | Sample Selection Microscopic Examination Procedure                                                                                                                                                                                                                                   | 9<br>9<br>10                                   |

| <u>6.</u>                                                                                      | REJECT CRITERIA                                                                                                                                                                                                                                                                      | <u>10</u>                                      |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                                | Delamination Voids Margin Defects (See Figure 4) Cracks in Ceramic Dielectric Non-Uniformities                                                                                                                                                                                       | 10<br>10<br>10<br>10<br>10                     |

| <u>7.</u>                                                                                      | DECAPSULATION                                                                                                                                                                                                                                                                        | <u>11</u>                                      |

|                                                                                                | <u>FIGURES</u>                                                                                                                                                                                                                                                                       | <u>11</u>                                      |

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5                                                                | Figure 1 Figure 2 Figure 3 Figure 4 Figure 5                                                                                                                                                                                                                                         | 11<br>12<br>12<br>13<br>13                     |

## 1. SCOPE

This specification details a procedure for the microscopic examination of the internal structural features of fixed multilayer ceramic capacitors by means of cross-sectioned and polished samples. The specification provides a method of sample selection and specimen preparation, the inspection procedure and the accept/reject criteria.

## 2. PURPOSE

This specification is primarily applicable to unencapsulated leadless chip capacitors. The application of this specification to encapsulated capacitors may entail the performance of decapsulation procedures.

When called up, the requirements of this specification shall apply in addition to established parametric testing, electrical screening, etc., and not supplant such functional tests.

Application shall be on a manufacturing lot basis and not on a combined lot sampling basis since the tendency for structural abnormalities to occur is manufacturing lot related.

Sampling plans and the number of allowable defects shall be as specified herein.

## 3. TERMS AND DEFINITIONS

For the purpose of this specification, the following terms and definitions shall apply.

## 3.1 SAMPLE

The sample is the quantity of individual (electrically good) capacitors taken at random from each production lot and used for the construction of the microsection specimen. It may be necessary to divide the sample into more than one specimen if, for example, the capacitors are physically large.

## 3.2 SPECIMEN

The sample capacitors mounted into an epoxy resin block suitably ground and polished for microscopic inspection.

## 3.3 MANUFACTURING LOT

A manufacturing lot shall be comprised solely of capacitors of the same physical size and capacitance value. They shall have been manufactured using identical materials and assembly procedures and from a single dielectric mix.

## 3.4 CHIP

An individual monolithic leadless ceramic capacitor having metallised terminations for external connection.

## 3.5 DECAPSULATION

Decapsulation is the process of removal of any protective casing from the ceramic element of leaded capacitors, such as epoxy conformal coating or plastic case.

#### 3.6 LENGTH

For the purposes of orientation, the length of a multilayer monolithic structure shall be the distance between the ends of the chip from which the active electrodes emerge.

It is recognised that some chip bodies will be wider than they are long by this definition.

## 3.7 DELAMINATION

A delamination is a separation within or between structural layers of the multilayer structure approximately parallel to the plane of the layers.

## 3.8 VOID

A void is the absence of material from a structural layer, usually in the form of a bubble or cavity.

#### 3.9 CRACK

CRACK A crack is a fissure between adjacent areas of the monolithic multilayer structure. Cracks may intersect more than a single layer or may be confined to a single layer, often the outermost layer of the structure.

#### 3.10 MARGIN

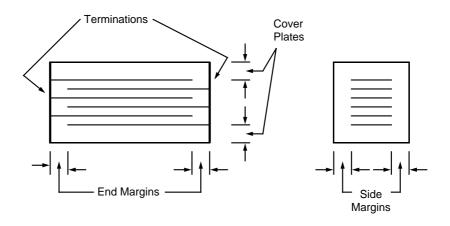

A margin is the area of ceramic surrounding the active area of a capacitor (see Figure 4).

## 3.11 COVER PLATE

Cover plates are the outer layers of dielectric material of the multilayer monolithic structure not forming a part of the active capacitor element and normally thicker than the active dielectric layers (see Figure 4).

## 4. SPECIMEN PREPARATION

## 4.1 <u>INTRODUCTION</u>

Cross-sectioning generally involves three discrete steps, mounting the sample capacitors in a block of epoxy resin to form the specimen, grinding or cutting the specimen, and polishing the surface so exposed.

## 4.2 <u>MOUNTING</u>

The purposes of this step are:

- (a) To hold the sample capacitors and their internal elements together during the sectioning process.

- (b) To provide a means of holding the sample capacitors during grinding and polishing operations.

- (c) To provide a convenient means of positioning the sample capacitors on the microscope stage for examination.

The capacitors being prepared for examination shall be cleaned before mounting in epoxy by agitation for five minutes in an ultrasonic cleaner while immersed in isopropyl alcohol. After removal from the alcohol, they shall be blotted on a clean absorbent tissue and transferred to a clean absorbent surface and allowed to air-dry for at least 2 to 3 minutes.

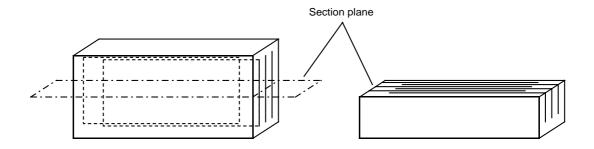

Three-quarters of the sample capacitors shall be mounted and sectioned to reveal the length and thickness dimensions showing the end termination areas and electrode overlap region as shown in Figure 1.

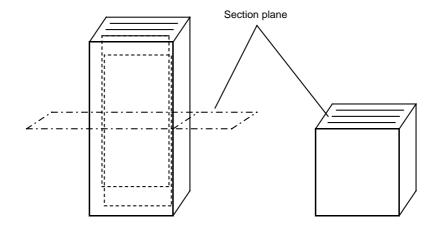

The remaining quarter of the sample capacitors shall be mounted so that sectioning will reveal the width and thickness dimensions and show a cross-section of the electrodes with isolation margins on each side

in accordance with Figure 2.

#### NOTES:

Figures 1 and 2 are in planes perpendicular to one another.

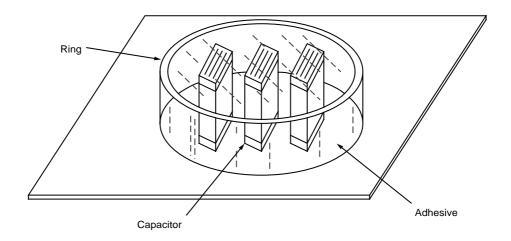

The capacitors shall be placed on one side of a double-sided adhesive tape, the other side being attached to the base of a suitable mould or to a surface encircled by a disposable plastic mounting ring as shown in Figure 3.

The capacitors shall be mounted such that none are within 3mm of the mould or ring and that none are within 1mm of each other to provide for adequate flow of epoxy resin between them. They shall be orientated such that the vertical electrodes are all aligned in the same direction, i.e. parallel to one another. They shall also be mounted such that the electrode plane is perpendicular within 5 degrees to the section plane.

The use of disposable mounting rings will obviate the use of force that might otherwise be necessary to remove the specimen from a re-usable mould. Grease or other release agent shall not be used.

A suitable epoxy resin shall be mixed in accordance with the Manufacturer's recommendations and poured into the mould to surround the capacitors completely. After the capacitors are completely covered, a lot identification label may be placed on the surface of the resin such that the addition of further resin will completely enclose the label within the specimen.

Suitable internal dimensions for the mould are 3cm diameter and 2 to 3cm high.

Several proprietary brands of epoxy resin are manufactured specifically for the purpose described in this document. A suitable resin will have the following properties:

- (a) It shall be curable at room temperature. No thermoplastic or thermosetting material requiring curing above room temperature, with or without pressure, shall be used. Such materials and methods result in harmful stresses within the ceramic capacitor.

- (b) Cure must take place without perceptible shrinkage which would leave surfaces of the mounted capacitors unsupported.

- (c) When mixed as prescribed by the Manufacturer and allowed to cure at room temperature, it shall not cause appreciable warming of the embedded capacitors due to the cure exotherm.

- (d) The cured epoxy resin should exhibit moderate residual compressive strain that will support the capacitor samples firmly without inducing stress relief cracking during sectioning and polishing. The hardness shall be such as to provide adequate ability to resist edge relief during polishing.

To add an additional hardening of the epoxy mix, glass beads of 0.4 to 0.6mm diameter may be added to the mix.

## 4.3 <u>SPECIMEN GRINDING (OR CUTTING)</u>

The purpose of this step is to quickly reach the broad region of interest. This enables the exact area of interest to be reached by subsequent slower polishing techniques in a reasonable period of time.

Grinding entails the use of silicon carbide paper, commencing with a coarse grade, followed by an intermediate grade (or grades) and finally the finest grade as the area of interest is approached. Grinding can be carried out by hand, using strips of paper in an appropriate holder, or alternatively using silicon carbide paper disks mounted on horizontal rotary grinding wheels. A continuous flow of water should be used for cooling and cleaning the wheels.

Grinding should be carried out in a direction approximately parallel to the alignment of the electrodes.

After each step, the specimen shall be cleaned in a mild (5%) detergent solution and rinsed with tap water. Any detergent is suitable provided it does not contain additives such as perfumes or oils, which will leave a residue.

In some instances, e.g. for sectioning large samples, the region of interest can be reached in a more efficient manner by cutting or sawing through the specimen. Proprietary equipment is available using diamond saw blades. This should be followed by standard grinding procedures referred to above.

The possibility of damage to the capacitors should be considered before resorting to cutting.

## 4.4 SPECIMEN POLISHING

The polishing steps of specimen preparation are to eliminate surface scratches produced during grinding, while maintaining sectioned capacitor features essentially unchanged so that a true view of these features is available for visual inspection. Polishing should be kept to a minimum to achieve scratch removal without producing exaggerated specimen relief or edge distortion.

The procedure is broadly divided into rough and fine polishing using a short nap, disk-shaped polishing cloth on a horizontal rotary grinding wheel.

The use of diamond lapping compounds is recommended having a maximum particle size of  $9\mu$ m down to  $3\mu$ m for rough polishing with smaller particle sizes being available for fine polishing.

A slurry of alpha alumina particles is commonly used as a polishing medium, but should not be used if aluminium contamination is likely to cause problems.

After each polishing step, the specimen should again be cleaned in a mild detergent solution followed by rinsing in tap water.

## 4.5 SPECIMEN PREPARATION PROBLEMS

Ceramic dielectrics are brittle materials with relatively low mechanical strength. The processes by which samples are mounted, sectioned and polished can readily induce high stresses in these materials. Such stresses can be, and often are, interpreted as product defects which did not exist in the undisturbed component.

Abnormalities resulting from faulty sample preparation techniques may include the following.

## 4.5.1 Excessive Pull-out

Pull-out and cracking may occur during specimen grinding if an excessively coarse grinding medium is combined with high contact pressure in a direction perpendicular to the electrodes. This condition in varying degrees can also be caused by chatter of the specimen against the grinding wheel, when the specimen slides, then grabs on the abrasive surface, and may occur even with the finest grade abrasive.

## 4.5.2 <u>Indined Component Mounting</u>

Wide wavy appearing electrodes result from samples which are mounted obliquely at an incline to the desired sectional plane. Faulty mounting invalidates the use of such specimens for microscopic analysis.

## 4.5.3 <u>Cover Plate Cracking</u>

Cracks in the cover plate frequently occur as a result of unsupported cover layers due to the use of too soft an epoxy or a mounting compound which shrinks away from the capacitor body in curing and fails to support the body against the stresses of grinding. This type of damage may also occur due to excessive pressure during hand-polishing on a rotating disk.

#### 4.5.4 Dielectric Material Pull-out

In the vicinity of an original void, dielectric material pull-out often increases the apparent size of the void. Careful grinding techniques can reduce such induced damage.

#### 4.5.5 Small Delaminations

Small delaminations can increase in size as a result of grinding stresses. Again, careful grinding techniques can reduce this damage.

## 4.5.6 <u>Grinding Scratches (Inadequate Polishing)</u>

The presence of grinding scratches not completely removed by polishing can be misinterpreted as defects in a capacitor. Such scratches pull out both ceramic dielectric and electrode materials. This may be interpreted erroneously as voids in the dielectric and discontinuous electrodes.

Inadequate polishing of a surface that has been ground perpendicular to the direction of the electrodes may also give the appearance of discontinuous electrodes.

## 4.5.7 Component Relief

High polishing pressure or an excessively long polishing time may cause section relief which rounds off the corners and edges of the capacitor. This can give the appearance of discontinuous termination coverage during microscopic examination due to termination material being below the place of focus at high magnification.

## 5. INSPECTION REQUIREMENTS

## 5.1 <u>SAMPLE SELECTION</u>

Sample Selection From each manufacturing lot, a sample of 20 (electrically good) capacitors shall be selected at random for inspection. These will normally form a single microsection specimen.

## 5.2 <u>MICROSCOPIC EXAMINATION</u>

The sample capacitors shall be examined microscopically using a compound microscope with vertical illumination to locate, identify and characterise defects which constitute reject criteria.

Preliminary examination at low magnification (x60) is advisable to locate and identify structural abnormalities to be examined subsequently at higher magnification.

In the event of a capacitor exhibiting one or more rejectable defects it shall constitute a single reject.

## 5.3 PROCEDURE

The lot will be accepted if there are 0 (nil) rejects and rejected if there are 3 (three) or more rejects.

In the event of there being either 1 or 2 rejects, a second sample of 20 capacitors shall be selected at random and undergo inspection.

The lot will be accepted if the cumulative total of rejects from both samples equals 3 or less, and will be rejected if the cumulative total equals 4 or more.

## 6. REJECT CRITERIA

A sample capacitor shall be rejected if it exhibits 1 or more of the defects listed in any of the following

paragraphs.

## 6.1 <u>DELAMINATION</u>

- (a) A delamination within the active area of the electrodes which exceeds 0.5mm or 25% of the total electrode length, whichever is greater.

- (b) 2 or more delaminations within the electrode area which are less than 0.5mm in length and overlap each other in 2 or more adjacent layers.

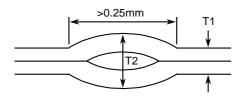

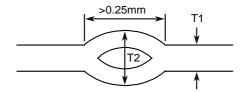

- (c) A delamination greater than 0.25mm in length within the electrode area which results in the displacement of the 2 adjacent dielectric layers by more than 50% of the average dielectric thickness. Calculation of the relative displacement shall be in accordance with the appropriate diagram of Figure 5.

- (d) A delamination which extends more than 50% of the distance from a termination to the approaching edge of an opposite electrode.

#### 6.2 VOIDS

- (a) Any void between adjacent opposed electrodes which reduces the nominal dielectric thickness by more than 50% along a line perpendicular to adjacent electrodes.

- (b) Any void or pin-hole in the ceramic cover plate which reduces the thickness of the cover plate to less than 0.08mm or less than the nominal dielectric thickness between adjacent opposed electrodes, whichever is less.

#### 6.3 MARGIN DEFECTS (SEE FIGURE 4)

A side or end-margin or cover plate displaying a thickness of less than 0.08mm of uninterrupted ceramic, or less than the nominal dielectric thickness between adjacent opposed electrodes, whichever is less.

## 6.4 CRACKS IN CERAMIC

- (a) Any crack in the dielectric which connects any 2 electrodes.

- (b) Any crack in the ceramic which connects an electrode with the surface of the capacitor element or the termination.

#### 6.5 DIELECTRIC NON-UNIFORMITIES

Any variation in dielectric thickness within the active area which results in more than 70% reduction in the thickness of any dielectric layer compared to the measured average for all other dielectric thicknesses.

## 7. DECAPSULATION

Whenever possible, a microsection examination shall be carried out on leaded ceramic capacitors prior to any subsequent encapsulation to avoid the complications of decapsulation procedures.

However, preparation for post-production analysis of the internal structure may require that encapsulating materials be removed prior to mounting and sectioning. This may be deemed necessary to avoid damage to the capacitors due to inadequate support of the ceramic body during sectioning, e.g. if there is an internal void in the structure or if there is uneven compression relief of moulded parts during grinding. Such stresses may cause apparent defects which were not present in the undisturbed body (refer also to Dielectric Material Pull-out under Specimen Preparation Problems).

Decapsulating materials and procedures must be such that minimum damage is done to the multilayer body and its leads and lead connections. These will differ depending on the characteristics of the encapsulant to be removed. All decapsulating chemical agents attack material interface and surface to some degree.

Several proprietary decapsulant materials are available and all present hazards to the User. Strict adherence to the Manufacturer's recommendations and good laboratory practice is mandatory.

## 8. FIGURES

## 8.1 <u>FIGURE 1</u>

## 8.2 <u>FIGURE 2</u>

# 8.3 <u>FIGURE 3</u>

# 8.4 <u>FIGURE 4</u>

# 8.5 <u>FIGURE 5</u>

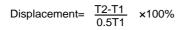

Displacement=  $\frac{\text{T2-T1}}{\text{T1}}$  ×100%