Page 1 of 37

# INTEGRATED CIRCUITS, MONOLITHIC, CMOS SILICON ON SAPPHIRE, 3.5GHz INTEGER-N PLL FREQUENCY SYNTHESISER

# **BASED ON TYPE PE33362**

ESCC Detail Specification No. 9202/078

Issue 3 August 2015

Document Custodian: European Space Agency – see <a href="https://escies.org">https://escies.org</a>

# **LEGAL DISCLAIMER AND COPYRIGHT**

European Space Agency, Copyright © 2015. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

# **DOCUMENTATION CHANGE NOTICE**

(Refer to <a href="https://escies.org">https://escies.org</a> for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION                                               |

|---------|------------------------------------------------------------------|

| 936     | Specification upissued to incorporate editorial changes per DCR. |

ISSUE 3

# **TABLE OF CONTENTS**

| 1        | GENERAL                                                    | 6  |

|----------|------------------------------------------------------------|----|

| 1.1      | SCOPE                                                      | 6  |

| 1.2      | APPLICABLE DOCUMENTS                                       | 6  |

| 1.3      | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS       | 6  |

| 1.4      | THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS      | 6  |

| 1.4.1    | The ESCC Component Number                                  | 6  |

| 1.4.2    | Component Type Variants                                    | 6  |

| 1.5      | MAXIMUM RATINGS                                            | 7  |

| 1.6      | HANDLING PRECAUTIONS                                       | 7  |

| 1.7      | PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION            | 8  |

| 1.7.1    | Ceramic Quad Flat Package J-BEND (CQFPJ-44) – 44 Terminals | 8  |

| 1.8      | FUNCTIONAL DIAGRAM                                         | 9  |

| 1.9      | PIN ASSIGNMENT AND DESCRIPTION                             | 10 |

| 1.10     | FUNCTIONAL DESCRIPTION                                     | 12 |

| 1.10.1   | Overview                                                   | 12 |

| 1.10.2   | Main Counter Chain                                         | 13 |

| 1.10.2.1 | Normal Operating Mode                                      | 13 |

| 1.10.2.2 | Prescaler Bypass Mode                                      | 13 |

| 1.10.3   | Reference Counter Chain                                    | 14 |

| 1.10.4   | Register Programming                                       | 14 |

| 1.10.4.1 | Parallel Interface Mode                                    | 14 |

| 1.10.4.2 | Serial Interface Mode                                      | 15 |

| 1.10.4.3 | Direct Interface Mode                                      | 16 |

| 1.10.4.4 | Enhancement Register                                       | 16 |

| 1.10.5   | Phase Detector                                             | 17 |

| 1.11     | INPUT AND OUTPUT PROTECTION NETWORKS                       | 18 |

| 2        | REQUIREMENTS                                               | 18 |

| 2.1      | GENERAL                                                    | 18 |

| 2.1.1    | Deviations from the Generic Specification                  | 19 |

| 2.1.1.1  | Deviations from Screening Tests - Chart F3                 | 19 |

| 2.2      | MARKING                                                    | 19 |

| 2.3      | ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES | 19 |

| 2.3.1    | Room Temperature Electrical Measurements                   | 19 |

| 2.3.2    | High and Low Temperatures Electrical Measurements          | 30 |

| 2.4      | PARAMETER DRIFT VALUES                                     | 30 |

| <b>ESCC</b> | Detail  | Spe | cification |

|-------------|---------|-----|------------|

|             | Dottail | Opo | onioanoi   |

ISSUE 3

PAGE 5

| 2.5      | INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS                    | 30 |

|----------|-----------------------------------------------------------------------|----|

| 2.6      | POWER BURN-IN CONDITIONS                                              | 31 |

| 2.6.1    | Electrical Test Conditions                                            | 31 |

| 2.6.2    | Environmental Test Conditions                                         | 31 |

| 2.6.3    | Burn-in Stimulus                                                      | 31 |

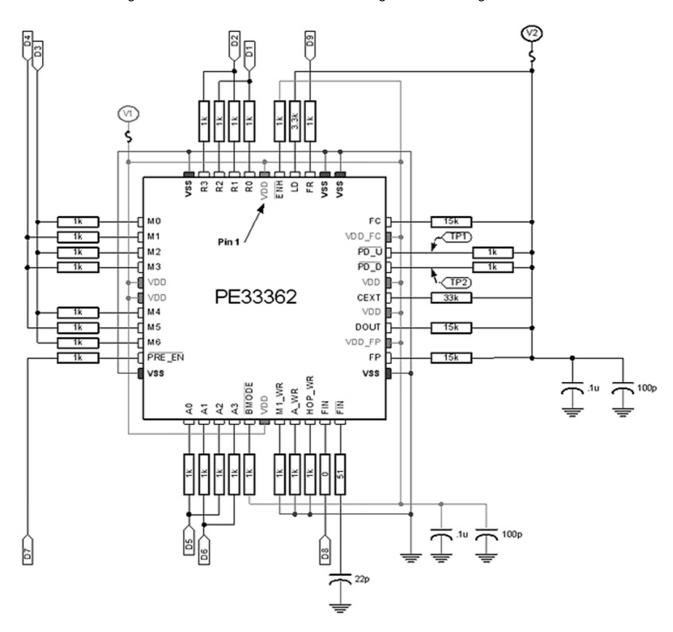

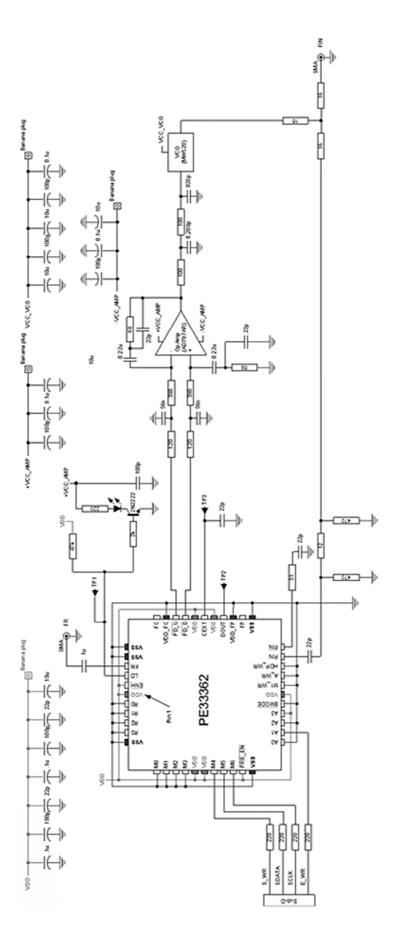

| 2.6.4    | Burn-in Schematic                                                     | 33 |

| 2.7      | OPERATING LIFE CONDITIONS                                             | 33 |

| 2.8      | TOTAL DOSE RADIATION TESTING                                          | 34 |

| 2.8.1    | Bias Conditions and Total Dose Level for Total Dose Radiation Testing | 34 |

| 2.8.2    | Electrical Measurements for Total Dose Radiation Testing              | 36 |

| APPENDIX | . 'A'                                                                 | 37 |

#### 1 **GENERAL**

#### 1.1 SCOPE

This specification details the ratings, physical and electrical characteristics and test and inspection data for the component type variants and/or the range of components specified below. It supplements the requirements of, and shall be read in conjunction with, the ESCC Generic Specification listed under Applicable Documents.

#### 1.2 APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:

- (a) ESCC Generic Specification No. 9000.

- (b) MIL-STD-883, Test Methods and Procedures for Microelectronics.

#### 1.3 TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESCC Basic Specification No. 21300 shall apply.

#### 1.4 THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS

#### 1.4.1 The ESCC Component Number

The ESCC Component Number shall be constituted as follows:

Example: 920207801R

Detail Specification Reference: 9202078Component Type Variant Number: 01

Total Dose Radiation Level Letter: R (as required)

## 1.4.2 <u>Component Type Variants</u>

The component type variants applicable to this specification are as follows:

| Variant<br>Number | Based on Type | Case     | Lead/Terminal<br>Material and Finish | Weight max g | Total Dose Radiation<br>Level Letter |

|-------------------|---------------|----------|--------------------------------------|--------------|--------------------------------------|

| 01                | PE33362       | CQFPJ-44 | G2                                   | 10           | R [100kRAD(Si)]                      |

The lead/terminal material and finish shall be in accordance with the requirements of ESCC Basic Specification No. 23500.

Total dose radiation level letters are defined in ESCC Basic Specification No. 22900. If an alternative radiation test level is specified in the Purchase Order the letter shall be changed accordingly.

#### 1.5 MAXIMUM RATINGS

The maximum ratings shall not be exceeded at any time during use or storage. Prolonged use of the device at the maximum ratings may reduce the device's overall reliability.

Maximum ratings shall only be exceeded during testing to the extent specified in this specification and when stipulated in Test Methods and Procedures of the ESCC Generic Specification.

| Characteristics                       | Symbols              | Maximum Ratings              | Units | Remarks   |

|---------------------------------------|----------------------|------------------------------|-------|-----------|

| Supply Voltage Range                  | $V_{DD}$             | -0.3 to 4                    | V     | Note 1    |

| Input Voltage Range                   | V <sub>IN</sub>      | -0.3 to V <sub>DD</sub> +0.3 | ٧     | Note 2    |

| DC Input Current Range                | I <sub>IN</sub>      | -10 to +10                   | mA    |           |

| DC Output Current Range               | I <sub>OUT</sub>     | -90 to +110                  | mA    | Note 3    |

| Device Power Dissipation (Continuous) | $P_{D}$              | 500                          | mW    |           |

| Operating Temperature Range           | T <sub>op</sub>      | -40 to +85                   | °C    | $T_{amb}$ |

| Storage Temperature Range             | T <sub>stg</sub>     | -65 to +150                  | °C    |           |

| Junction Temperature                  | Tj                   | +150                         | °C    |           |

| Thermal Resistance, Junction to Case  | R <sub>th(j-c)</sub> | 15                           | °C/W  |           |

| Soldering Temperature                 | T <sub>sol</sub>     | +260                         | °C    | Note 4    |

#### **NOTES:**

- 1. All voltages are with respect to  $V_{SS}$ . Device is functional for  $2.85 \le V_{DD} \le 3.45 V$ .

- 2. V<sub>DD</sub>+0.3V shall not exceed 4V.

- 3. The maximum output current of any single output for a maximum duration of 1 second.

- 4. Duration 10 seconds maximum at a distance of not less than 1.6mm from the device body and the same terminal shall not be re-soldered until 3 minutes have elapsed.

#### 1.6 <u>HANDLING PRECAUTIONS</u>

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are categorised as Class 1 per ESCC Basic Specification No. 23800 with a minimum Critical Path Failure Voltage of 1000 Volts.

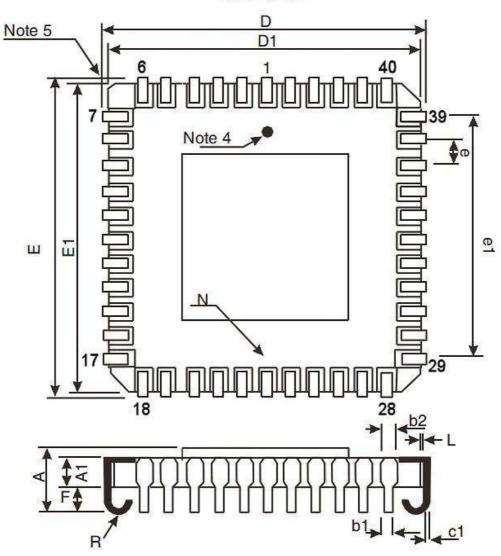

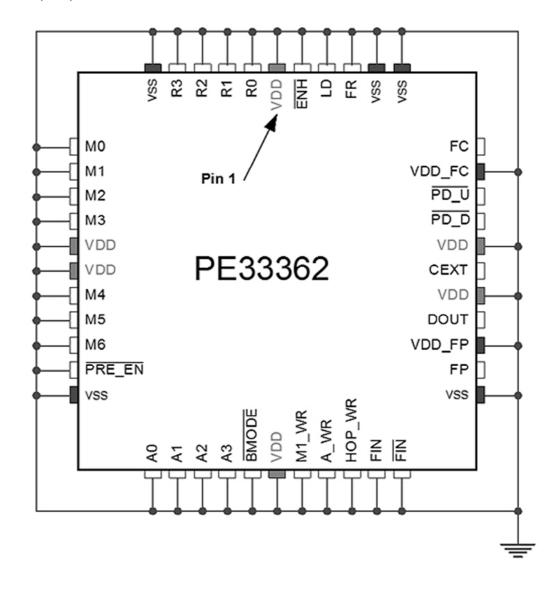

# 1.7 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

# 1.7.1 <u>Ceramic Quad Flat Package J-BEND (CQFPJ-44) – 44 Terminals</u>

# **TOP VIEW**

| Cumhala | Dimensi | Notes  |         |

|---------|---------|--------|---------|

| Symbols | Min     | Max    | - Notes |

| А       | 2.41    | 3.18   | 1       |

| A1      | 1.49    | 1.81   |         |

| b1      | 0.432 T | 1      |         |

| b2      | 0.762 T | YPICAL | 1       |

| c1      | 0.2     | 0.28   | 1       |

| D/E     | 17.27   | 17.78  |         |

| D1/E1   | 16.3    | 16.72  |         |

| Cymbala | Dimensi    | Notes |      |

|---------|------------|-------|------|

| Symbols | Min Max    |       |      |

| е       | 1.27       | 1, 2  |      |

| e1      | 12.49      | 12.91 | 3    |

| F       | 0.66       | 1.17  | 1    |

| L       | 0.508 T    | 1     |      |

| N       | 11 TERMINA | 3     |      |

| R       | 0.5        | 1.02  | 1, 6 |

#### NOTES:

- 1. Applies to all 44 terminals (11 per side).

- 2. 40 places. The true position pin spacing is 1.27mm between centrelines. Each pin centreline shall be located within ±0.13mm of its true longitudinal position relative to the package centrelines.

- 3. 4 places.

- 4. A terminal identification mark shall be located in the region of Pin 1 as shown. Terminal numbers shall increase counter clockwise when viewed as shown starting from the centre terminal (Pin 1).

- 5. Index corner: Terminal identification is specified by reference to the index corner as shown.

- 6. Radius.

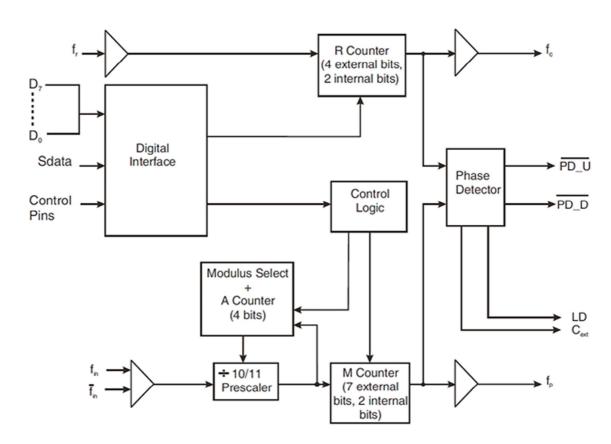

#### 1.8 <u>FUNCTIONAL DIAGRAM</u>

# 1.9 PIN ASSIGNMENT AND DESCRIPTION

The table below describes each pin's assignment, type and standard, plus a brief description of its functionality.

| Pin<br>No. | Pin Name        | Pin Type | Pin<br>Standard | Valid<br>Mode | Description                                             |

|------------|-----------------|----------|-----------------|---------------|---------------------------------------------------------|

| Top side   | е               |          |                 |               |                                                         |

| 1          | $V_{DD}$        | Power    | -               | -             | Power Supply (Note 1).                                  |

| 2          | $R_0$           | Input    | CMOS            | Direct        | R Counter, bit 0 (LSB).                                 |

| 3          | R <sub>1</sub>  | Input    | CMOS            | Direct        | R Counter, bit 1.                                       |

| 4          | $R_2$           | Input    | CMOS            | Direct        | R Counter, bit 2.                                       |

| 5          | $R_3$           | Input    | CMOS            | Direct        | R Counter, bit 3.                                       |

| 6          | V <sub>SS</sub> | Ground   | -               | -             | V <sub>SS</sub>                                         |

| Left-har   | nd side         |          |                 |               |                                                         |

| 7          | $D_0$           | Input    | CMOS            | Parallel      | Data bus, bit 0 (LSB).                                  |

|            | $M_0$           | Input    | CMOS            | Direct        | M Counter, bit 0 (LSB).                                 |

| 8          | $D_1$           | Input    | CMOS            | Parallel      | Data bus, bit 1.                                        |

|            | M <sub>1</sub>  | Input    | CMOS            | Direct        | M Counter, bit 1.                                       |

| 9          | D <sub>2</sub>  | Input    | CMOS            | Parallel      | Data bus, bit 2.                                        |

|            | M <sub>2</sub>  | Input    | CMOS            | Direct        | M Counter, bit 2.                                       |

| 10         | $D_3$           | Input    | CMOS            | Parallel      | Data bus, bit 3.                                        |

|            | $M_3$           | Input    | CMOS            | Direct        | M Counter, bit 3.                                       |

| 11         | $V_{DD}$        | Power    | -               |               | Power Supply (Note 1).                                  |

| 12         | $V_{DD}$        | Power    | -               |               | Power Supply (Note 1).                                  |

| 13         | S_WR            | Input    | CMOS            | Serial        | Serial load enable input.                               |

|            | D <sub>4</sub>  | Input    | CMOS            | Parallel      | Data bus, bit 4.                                        |

|            | M <sub>4</sub>  | Input    | CMOS            | Direct        | M Counter, bit 4.                                       |

| 14         | SDATA           | Input    | CMOS            | Serial        | Binary serial data input, input data entered MSB first. |

|            | $D_5$           | Input    | CMOS            | Parallel      | Data bus, bit 5.                                        |

|            | M <sub>5</sub>  | Input    | CMOS            | Direct        | M Counter, bit 5.                                       |

| 15         | SCLK            | Input    | CMOS            | Serial        | Serial Clock Input.                                     |

|            | D <sub>6</sub>  | Input    | CMOS            | Parallel      | Data bus, bit 6.                                        |

|            | M <sub>6</sub>  | Input    | CMOS            | Direct        | M Counter, bit 6.                                       |

| 16         | FSELS           | Input    | CMOS            | Serial        | Primary/secondary register selection.                   |

|            | D <sub>7</sub>  | Input    | CMOS            | Parallel      | Data bus, bit 7 (MSB).                                  |

|            | PRE_EN          | Input    | CMOS            | Direct        | Prescaler enable.                                       |

| 17         | V <sub>SS</sub> | Ground   | -               | -             | V <sub>SS</sub>                                         |

| Pin<br>No. | Pin Name            | Pin Type | Pin<br>Standard | Valid<br>Mode       | Description                                            |

|------------|---------------------|----------|-----------------|---------------------|--------------------------------------------------------|

| Bottom     | side                |          | 1               |                     |                                                        |

| 18         | FSELP               | Input    | CMOS            | Parallel            | Primary/secondary register selection.                  |

|            | $A_0$               | Input    | CMOS            | Direct              | A Counter, bit 0 (LSB).                                |

| 19         | E_WR                | Input    | CMOS            | Serial,<br>parallel | Enhancement register write.                            |

|            | A <sub>1</sub>      | Input    | CMOS            | Direct              | A Counter, bit 1.                                      |

| 20         | M <sub>2</sub> WR   | Input    | CMOS            | Parallel            | M <sub>2</sub> write.                                  |

|            | A <sub>2</sub>      | Input    | CMOS            | Direct              | A Counter, bit 2.                                      |

| 21         | SMODE               | Input    | CMOS            | Serial,<br>parallel | Serial/parallel interface mode selection.              |

|            | $A_3$               | Input    | CMOS            | Direct              | A Counter, bit 3 (MSB).                                |

| 22         | BMODE               | Input    | CMOS            | All                 | Direct interface mode selection.                       |

| 23         | $V_{DD}$            | Power    | -               | -                   | Power Supply (Note 1).                                 |

| 24         | M <sub>1</sub> _WR  | Input    | CMOS            | Parallel            | M <sub>1</sub> write.                                  |

| 25         | A_WR                | Input    | CMOS            | Parallel            | A write.                                               |

| 26         | HOP_WR              | Input    | CMOS            | Serial,<br>parallel | Hop write.                                             |

| 27         | FIN                 | Input    | RF              | All                 | Prescaler input.                                       |

| 28         | FIN                 | Input    | RF              | All                 | Prescaler complementary input.                         |

| Right-ha   | and side            |          |                 |                     |                                                        |

| 29         | $V_{SS}$            | Ground   | -               | -                   | V <sub>SS</sub>                                        |

| 30         | FP                  | Input    | CMOS            | All                 | Monitor pin (main divider).                            |

| 31         | V <sub>DD</sub> _FP | Power    | -               | -                   | V <sub>DD</sub> for FP (Note 1).                       |

| 32         | DOUT                | Output   | CMOS            | Serial,<br>parallel | Data out.                                              |

| 33         | $V_{DD}$            | Power    | -               | -                   | Power Supply (Note 1).                                 |

| 34         | CEXT                | Output   | CMOS            | All                 | External capacitor.                                    |

| 35         | $V_{DD}$            | Power    | -               | -                   | Power Supply (Note 1).                                 |

| -          | V <sub>SS</sub>     | Ground   | -               | -                   | V <sub>SS</sub>                                        |

| 36         | PD_D                | Output   | CMOS            | All                 | Pulses down when fp leads fc.                          |

| 37         | PD_U                | Output   | CMOS            | All                 | Pulses down when f <sub>c</sub> leads f <sub>p</sub> . |

| 38         | V <sub>DD</sub> _FC | Power    | -               | -                   | V <sub>DD</sub> for FC (Note 1).                       |

| 39         | FC                  | Output   | CMOS            | All                 | Monitor pin (reference divider).                       |

| Top side   | е                   |          |                 |                     |                                                        |

| 40         | V <sub>SS</sub>     | Ground   | -               | -                   | V <sub>SS</sub>                                        |

| 41         | V <sub>SS</sub>     | Ground   | -               | -                   | V <sub>SS</sub>                                        |

| 42         | FR                  | Input    | CMOS            | All                 | Reference frequency.                                   |

| Pin<br>No. | Pin Name | Pin Type | Pin<br>Standard | Valid<br>Mode       | Description       |

|------------|----------|----------|-----------------|---------------------|-------------------|

| 43         | LD       | Output   | Open drain      | All                 | Lock detect.      |

| 44         | ENH      | Input    | CMOS            | Serial,<br>parallel | Enhancement mode. |

#### NOTES:

- 1. All V<sub>DD</sub> pins are connected by diodes and must be supplied with the same positive voltage level. Pins 31 and 38 are used to enable test modes and should therefore be left floating or grounded.

- 2. All digital input pins (i.e. CMOS inputs of Group 1 below) have a  $70k\Omega$  pull-down resistor to ground.

The table below describes the pin groups to be tested.

| Group No. | Туре                        | Total No.<br>of Pins | Pin Numbers                                          |

|-----------|-----------------------------|----------------------|------------------------------------------------------|

| 1         | CMOS Input with Pull-down   | 21                   | 2 to 5, 7 to 10, 13 to 16, 18 to 22, 24 to 26 and 44 |

| 2         | CMOS Input                  | 1                    | 42 (FR)                                              |

| 3         | RF Input                    | 2                    | 27 (FIN) and 28 (FIN)                                |

| 4         | High Current CMOS Output    | 2                    | 36 (PD_D) and 37 (PD_U)                              |

| 5         | Low Current CMOS Output     | 3                    | 30 (FP), 32 (DOUT) and 39 (FC)                       |

| 6         | High Resistance CMOS Output | 1                    | 34 (CEXT)                                            |

| 7         | Open Drain Output           | 1                    | 43 (LD)                                              |

| 8         | Power                       | 8                    | 1, 11, 12, 23, 31(*), 33, 35 and 38(*)               |

| 9         | Ground                      | 5                    | 6, 17, 29, 40 and 41                                 |

<sup>(\*)</sup> See Note 1 above.

#### 1.10 FUNCTIONAL DESCRIPTION

#### 1.10.1 Overview

The PE33362 consists of a prescaler, several counters, a phase detector and control logic. The dual modulus prescaler divides the VCO frequency by either 10 or 11, depending on the value of the modulus select. Counters "R" and "M" divide the reference and prescaler outputs, respectively, by the integer values stored in a 20-bit register. An additional counter ("A") is used in the modulus select logic.

The phase-frequency detector generates up and down frequency control signals. The control logic includes a selectable chip interface. Data can be written via serial bus, parallel bus, or hardwired directly to the pins. There are also various operational and test modes and a lock detect output.

#### 1.10.2 Main Counter Chain

#### 1.10.2.1 Normal Operating Mode

In normal operation, the main counter chain divides the RF input frequency ( $f_{in}$ ) by an integer derived from the values in the "M" and "A" Counters. It is composed of the  $\div 10/11$  dual modulus prescaler, modulus select logic, and 9-bit M Counter. Setting  $\overline{PRE\_EN}$  "low" enables the  $\div 10/11$  prescaler. Setting  $\overline{PRE\_EN}$  "high" allows  $f_{in}$  to bypass the prescaler and powers down the prescaler.

The output from the main counter chain  $(f_p)$  is related to the VCO frequency  $(f_{in})$  by the following equation:

$$f_p = f_{in}/[10 \times (M + 1) + A]$$

(1)

Where  $A \le M + 1$ ,  $1 \le M \le 511$

When the loop is locked,  $f_{in}$  is related to the reference frequency  $(f_r)$  by the following equation:

$$f_{in} = [10 \times (M + 1) + A] \times (f_{r}/(R + 1))$$

(2)

Where  $A \le M + 1$ ,  $1 \le M \le 511$

A consequence of the upper limit on A is that  $f_{in}$  must be greater than or equal to 90 × ( $f_r$  / (R + 1)) to obtain contiguous channels.

Programming the M Counter with the minimum allowed value of "1" will result in a minimum M Counter divide ratio of "2".

In Direct Interface mode, the main counter inputs  $M_7$  and  $M_8$  are internally forced low. In this mode, the M value is limited to  $1 \le M \le 127$ .

#### 1.10.2.2 Prescaler Bypass Mode

Setting the frequency control register bit  $\overline{\text{PRE\_EN}}$  "high" allows  $f_{in}$  to bypass the  $\div 10/11$  prescaler. In this mode, the prescaler and A Counter are powered down, and the input VCO frequency is divided by the M Counter directly. The following equation relates  $f_{in}$  to the reference frequency ( $f_r$ ):

$$f_{in} = (M + 1) \times (f_r/(R + 1))$$

(3)

Where  $1 \le M \le 511$

In Direct Interface mode, the main counter inputs  $M_7$  and  $M_8$  are internally forced low. In this mode, the M value is limited to  $1 \le M \le 127$ .

#### 1.10.3 Reference Counter Chain

The reference counter chain divides the reference frequency ( $f_r$ ) down to the phase detector comparison frequency ( $f_c$ ).

The output frequency of the 6-bit R Counter is related to the reference frequency by the following equation:

$$f_c = f_r / (R + 1) \tag{4}$$

Where  $0 \le R \le 63$

Note that programming R with "0" will pass the reference frequency (f<sub>r</sub>) directly to the phase detector.

#### 1.10.4 Register Programming

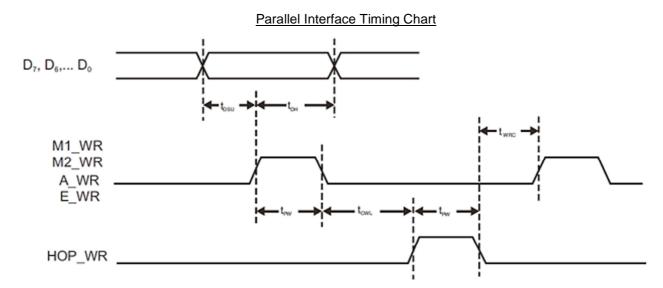

#### 1.10.4.1 Parallel Interface Mode

The Parallel Interface mode is selected by setting the  $\overline{\text{BMODE}}$  input "low" and the SMODE input "low".

Parallel input data (D<sub>7</sub>, D<sub>6</sub>,... D<sub>0</sub>) are latched in a parallel fashion into one of three 8-bit primary register sections on the rising edge of M1\_WR, M2\_WR, or A\_WR per the mapping shown in the table below. The contents of the primary register are transferred into a secondary register on the rising edge of HOP\_WR according to the timing chart shown below. Data is transferred to the counters as shown in the table below.

The secondary register acts as a buffer to allow rapid changes to the VCO frequency. This double buffering for "ping-pong" counter control is programmed via the FSELP input. When FSELP is "high", the primary register contents set the counter inputs. When FSELP is "low", the secondary register contents are utilised.

Parallel input data ( $D_7$ ,  $D_6$ ,...  $D_0$ ) are latched into the enhancement register on the rising edge of E\_WR according to the timing chart shown below. This data provides control bits as shown in the table below with bit functionality enabled by asserting the  $\overline{\text{ENH}}$  input "low".

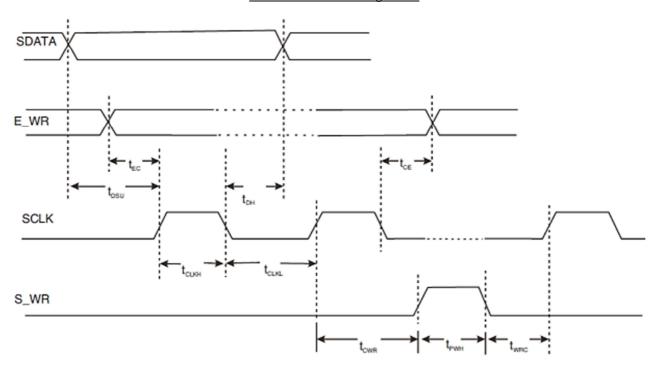

#### 1.10.4.2 Serial Interface Mode

The Serial Interface mode is selected by setting the  $\overline{\text{BMODE}}$  input "low" and the SMODE input "high".

While the E\_WR input is "low" and the S\_WR input is "low", serial input data (SDATA input),  $B_0$  to  $B_{19}$ , are clocked serially into the primary register on the rising edge of SCLK, MSB ( $B_0$ ) first. The contents from the primary register are transferred into the secondary register on the rising edge of either S\_WR or HOP\_WR according to the timing chart shown below. Data is transferred to the counters as shown in the table below.

The double buffering provided by the primary and secondary registers allows for "ping-pong" counter control using the FSELS input. When FSELS is "high", the primary register contents set the counter inputs. When FSELS is "low", the secondary register contents are utilised.

While the E\_WR input is "high" and the S\_WR input is "low", serial input data (SDATA input),  $B_0$  to  $B_7$ , are clocked serially into the enhancement register on the rising edge of SCLK, MSB ( $B_0$ ) first. The enhancement register is double buffered to prevent inadvertent control changes during serial loading, with buffer capture of the serially-entered data performed on the falling edge of E\_WR according to the timing chart shown below. After the falling edge of E\_WR, the data provides control bits as shown in the table below with bit functionality enabled by asserting the  $\overline{ENH}$  input "low".

#### Serial Interface Timing Chart

#### 1.10.4.3 Direct Interface Mode

The Direct Interface mode is selected by setting the BMODE input "high".

Counter control bits are set directly at the pins as shown in table below. In Direct Interface mode, the main counter inputs  $M_7$  and  $M_8$  and the R Counter inputs  $R_4$  and  $R_5$  are internally forced low ("0").

#### **Primary Register Programming**

| Interface<br>Mode | ENH | BMODE | SMODE | R <sub>5</sub> | R <sub>4</sub> | M <sub>8</sub> | M <sub>7</sub> | PRE_EN         | M <sub>6</sub> | M <sub>5</sub> | M <sub>4</sub> | Мз             | M <sub>2</sub> | M <sub>1</sub>  | M <sub>0</sub>  | R <sub>3</sub>  | R <sub>2</sub>  | R <sub>1</sub>  | R <sub>0</sub>  | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub>  | A <sub>0</sub>  |

|-------------------|-----|-------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Direct            | 1   | 1     | X     | 0              | 0              | 0              | 0              | PRE_EN         | M <sub>6</sub> | M <sub>5</sub> | $M_4$          | Мз             | M <sub>2</sub> | M <sub>1</sub>  | $M_0$           | $R_3$           | $R_2$           | $R_1$           | $R_0$           | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub>  | A <sub>0</sub>  |

| Serial (1)        | 1   | 0     | 1     | B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub> | B <sub>5</sub> | B <sub>6</sub> | B <sub>7</sub> | B <sub>8</sub> | B <sub>9</sub> | B <sub>10</sub> | B <sub>11</sub> | B <sub>12</sub> | B <sub>13</sub> | B <sub>14</sub> | B <sub>15</sub> | B <sub>16</sub> | B <sub>17</sub> | B <sub>18</sub> | B <sub>19</sub> |

| Parallel          | 1   | 0     | 0     | $D_3$          | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | $D_2$          | $D_1$           | $D_0$           | D <sub>7</sub>  | $D_6$           | $D_5$           | D <sub>4</sub>  | D <sub>3</sub>  | D <sub>2</sub>  | D <sub>1</sub>  | $D_0$           |

$\uparrow$  MSB (first in) LSB (last in)  $\uparrow$

#### **Enhancement Register Programming**

| Interface<br>Mode | ENH | BMODE | SMODE | Reserved       | Reserved       | FP<br>Output   | Power<br>Down  | Counter<br>Load | MSEL<br>Output | Prescaler<br>Output | FC, FP<br>OE   |

|-------------------|-----|-------|-------|----------------|----------------|----------------|----------------|-----------------|----------------|---------------------|----------------|

| Serial (2)        | 0   | 0     | 1     | B <sub>0</sub> | B <sub>1</sub> | B <sub>2</sub> | B <sub>3</sub> | B <sub>4</sub>  | B <sub>5</sub> | B <sub>6</sub>      | B <sub>7</sub> |

| Parallel          | 0   | 0     | 0     | D <sub>7</sub> | $D_6$          | D <sub>5</sub> | D <sub>4</sub> | $D_3$           | D <sub>2</sub> | D <sub>1</sub>      | $D_0$          |

↑ MSB (first in) LSB (last in) ↑

#### NOTES:

- 1. Serial data clocked serially on SCLK rising edge while E\_WR "low" and captured in secondary register on S\_WR rising edge.

- 2. Serial data clocked serially on SCLK rising edge while E\_WR "high" and captured in the double buffer on E\_WR falling edge.

## 1.10.4.4 Enhancement Register

The functions of the enhancement register bits are shown below with all bits active "high".

#### **Enhancement Register Programming Table**

| Bit Number | Bit Function        | Description                                                                                   |

|------------|---------------------|-----------------------------------------------------------------------------------------------|

| 0          | Reserved            | Reserve bit - program to 0.                                                                   |

| 1          | Reserved            | Reserve bit - program to 0.                                                                   |

| 2          | FP Output           | Drives the M Counter output onto the DOUT output.                                             |

| 3          | Power Down          | Power down of all functions except programming interface.                                     |

| 4          | Counter Load        | Immediate and continuous load of counter programming.                                         |

| 5          | MSEL Output         | Drives the internal dual modulus prescaler modulus select (MSEL) output onto the DOUT output. |

| 6          | Prescaler<br>Output | Drives the raw internal prescaler output (Fmain) onto the DOUT output.                        |

| 7          | FC, FP OE           | FP, FC outputs disabled.                                                                      |

#### 1.10.5 Phase Detector

The phase detector is triggered by rising edges from the main Counter ( $f_p$ ) and the reference Counter ( $f_c$ ). It has two outputs, namely  $\overline{PD\_U}$  and  $\overline{PD\_D}$ . If the divided VCO leads the divided reference in phase or frequency ( $f_p$  leads  $f_c$ ),  $\overline{PD\_D}$  pulses "low". If the divided reference leads the divided VCO in phase or frequency ( $f_c$  leads  $f_p$ ),  $\overline{PD\_U}$  pulses "low". The width of either pulse is directly proportional to phase offset between the two input signals,  $f_p$  and  $f_c$ . The phase detector gain is 430mV per radian.

PD\_U and PD\_D are designed to drive an active loop filter which controls the VCO tune voltage. PD\_U pulses cause an increase in VCO frequency and PD\_D pulses cause a decrease in VCO frequency, for a positive Kv VCO.

A "lock detect" output, LD, is also provided via the pin CEXT. CEXT is the logical "NAND" of  $\overline{PD\_U}$  and  $\overline{PD\_D}$  waveforms, which is driven through a serial  $2k\Omega$  resistor. Connecting CEXT to an external shunt capacitor provides low pass filtering of this signal. CEXT also drives the input of an internal inverting comparator with an open drain output. Thus LD is an "AND" function of  $\overline{PD\_U}$  and  $\overline{PD\_D}$ .

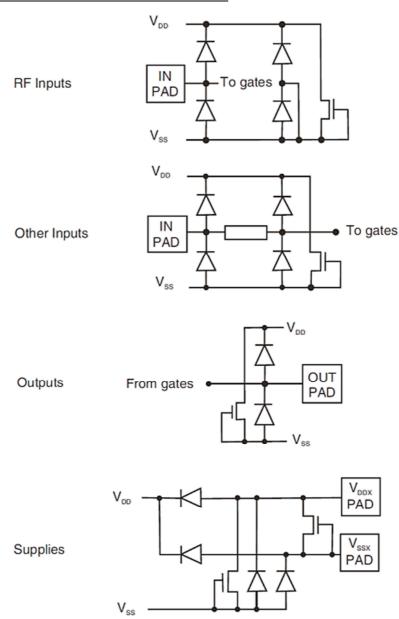

# 1.11 <u>INPUT AND OUTPUT PROTECTION NETWORKS</u>

#### 2 **REQUIREMENTS**

#### 2.1 GENERAL

The complete requirements for procurement of the components specified herein are as stated in this specification and the ESCC Generic Specification. Permitted deviations from the Generic Specification, applicable to this specification only, are listed below.

Permitted deviations from the Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESCC requirement and do not affect the component's reliability, are listed in the appendices attached to this specification.

#### 2.1.1 <u>Deviations from the Generic Specification</u>

#### 2.1.1.1 Deviations from Screening Tests - Chart F3

High Temperature Reverse Bias Burn-in and the subsequent Final Measurements for HTRB Burn-in shall be omitted.

#### 2.2 MARKING

The marking shall be in accordance with the requirements of ESCC Basic Specification No. 21700 and as follows.

The information to be marked on the component shall be:

- (a) Terminal identification.

- (b) The ESCC qualified components symbol (for ESCC qualified components only).

- (c) The ESCC Component Number.

- (d) Traceability information.

#### 2.3 <u>ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES</u>

Electrical measurements shall be performed at room, high and low temperatures.

#### 2.3.1 Room Temperature Electrical Measurements

The measurements shall be performed at  $T_{amb} = +22 \pm 3^{\circ}C$ .

| Characteristics                             | Symbols           | MIL-STD-883 | Test Conditions                                                                                                              | Lin  | nits | Units |

|---------------------------------------------|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|------|------|-------|

|                                             |                   | Test Method |                                                                                                                              | Min  | Max  |       |

| Input Clamp Voltage to V <sub>SS</sub>      | V <sub>ICL</sub>  | 3022        | Inputs: Pin Groups 1 to 3<br>Outputs: Pin Groups 4 to 7<br>$V_{DD} = V_{SS} = 0V$<br>$I_{IN} = 200\mu A$<br>Note 1           | -1.5 | -    | V     |

| Input Clamp Voltage to V <sub>DD</sub>      | V <sub>ICH</sub>  | 3022        | Inputs: Pin Groups 1 to 3<br>Outputs: Pin Groups 4 to 7<br>$V_{DD} = V_{SS} = 0V$<br>$I_{IN} = -200\mu A$<br>Note 1          | -    | 1.5  | V     |

| Shorts / Continuity<br>Check                | V <sub>SH</sub>   | -           | Inputs: Pin Groups 1 to 3<br>Outputs: Pin Groups 4 to 7<br>$V_{DD} = V_{SS} = 0V$<br>$I_{IN} = -200\mu A$<br>Note 1          | -    | 200  | mV    |

| Standby Supply<br>Current with<br>Prescaler | I <sub>DDQ1</sub> | 3005        | V <sub>DD</sub> = 3.45V, V <sub>SS</sub> = 0V<br>Use pattern <i>main_pattern</i> ,<br>stop at label <i>pdwn_sp</i><br>Note 3 | -    | 750  | μA    |

| Characteristics                                         | Symbols              | MIL-STD-883 | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                | Lin  | nits | Units |

|---------------------------------------------------------|----------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|

|                                                         |                      | Test Method |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Min  | Max  |       |

| Dynamic Supply<br>Current with<br>Prescaler             | I <sub>DDOPENA</sub> | 3005        | $\begin{split} &V_{DD}=3.45\text{V},\ V_{SS}=0\text{V}\\ &V_{IH}=3.45\text{V},\ V_{IL}=0\text{V}\ (\text{Pin}\\ &\text{Groups 1 to 3})\\ &V_{OH}=1.8\text{V},\ V_{OL}=1.3\text{V}\\ &I_{OL}=I_{OH}=0\text{A}\ (\text{Pin Groups 4}\\ &\text{to 6})\\ &I_{OL}=-1\text{mA}\ (\text{Pin Group 7})\\ &C_{LOAD}\!<\!62\text{pF}\\ &\text{Use pattern}\\ &\textit{main\_pattern}@10\text{MHz}\\ &\text{Loop from first to last vector}\\ &\text{Note 2} \end{split}$ | 30   | 52   | mA    |

| Dynamic Supply<br>Current without<br>Prescaler          | I <sub>DDOPDIS</sub> | 3005        | $\begin{split} &V_{DD}=3.45\text{V},V_{SS}=0\text{V}\\ &V_{IH}=3.45\text{V},V_{IL}=0\text{V}(\text{Pin}\\ &\text{Groups 1 to 3})\\ &V_{OH}=1.8\text{V},V_{OL}=1.3\text{V}\\ &I_{OL}=I_{OH}=0\text{A}(\text{Pin Groups 4 to 6})\\ &I_{OL}=-1\text{mA}(\text{Pin Group 7})\\ &C_{LOAD}\!<\!62\text{pF}\\ &\text{Use pattern}\\ &\textit{main\_pattern}@10\text{MHz}\\ &\text{Loop from first to last vector}\\ &\text{Note 2} \end{split}$                       | 8    | 23   | mA    |

| Functional Test,<br>Typical Voltage<br>(Relaxed Limits) | -                    | 3014        | $\begin{split} &V_{DD}=3.3V,V_{SS}=0V\\ &V_{IH}=3.3V,V_{IL}=0V(Pin\\ &Groups~1~to~3)\\ &V_{OH}=1.8V,V_{OL}=1.3V\\ &I_{OL}=I_{OH}=0A(Pin~Groups~4~to~6)\\ &I_{OL}=0A(Pin~Group~7)\\ &C_{LOAD}<62pF\\ &Use~pattern\\ &\textit{main\_pattern}@10MHz\\ &Note~4 \end{split}$                                                                                                                                                                                        | Go/N | NoGo | -     |

| Characteristics                                                                           | Symbols          | MIL-STD-883 | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Lim           | nits | Units    |

|-------------------------------------------------------------------------------------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|----------|

|                                                                                           |                  | Test Method |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Min           | Max  |          |

| Functional Test, Minimum Voltage (Specified Limits)                                       | -                | 3014        | $\begin{split} &V_{DD}=2.85\text{V},V_{SS}=0\text{V}\\ &V_{IH}=1.98\text{V},V_{IL}=870\text{mV}\\ &(\text{Pin Groups 1 and 2})\\ &V_{IH}=2.85\text{V},V_{IL}=0\text{V (Pin Group 3})\\ &V_{OH}=2.465\text{V},V_{OL}=385\text{mV}\\ &(\text{Pin Groups 4 to 7})\\ &I_{OL}/I_{OH}=-3\text{J}+6\text{mA (Pin Group 4})\\ &I_{OL}/I_{OH}=\pm200\mu\text{A (Pin Group 5})\\ &I_{OL}/I_{OH}=\pm100\mu\text{A (Pin Group 6})\\ &I_{OL}=-1\text{mA (Pin Group 7})\\ &C_{LOAD}<62\text{pF}\\ &U\text{se pattern }\textit{main\_pattern}\\ &@10\text{MHz}\\ &\text{Note 4} \end{split}$ | Go/NoGo       |      | -        |

| Functional Test,<br>Maximum Voltage<br>(Specified Limits)                                 | _                | 3014        | $V_{DD} = 3.45V, V_{SS} = 0V$ $V_{IH} = 2.4V, V_{IL} = 1.05V$ (Pin Groups 1 and 2) $V_{IH} = 3.45V, V_{IL} = 0V$ (Pin Group 3) $V_{OH} = 3.065V, V_{OL} = 385mV$ (Pin Groups 4 to 7) $I_{OL}/I_{OH} = -3 / +6mA$ (Pin Group 4) $I_{OL}/I_{OH} = \pm 200\mu A$ (Pin Group 5) $I_{OL}/I_{OH} = \pm 100\mu A$ (Pin Group 6) $I_{OL} = -1mA$ (Pin Group 7) $C_{LOAD} < 62pF$ Use pattern main_pattern @ 10MHz Note 4                                                                                                                                                              | Go/NoGo       |      | <u>-</u> |

| CMOS Input<br>Voltage, Low Level<br>(Minimum V <sub>DD</sub> )                            | V <sub>IL1</sub> | -           | Pin Groups 1 and 2<br>$V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>Use pattern <i>main_pattern</i><br>Note 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 855           | -    | mV       |

| CMOS Input<br>Voltage, High Level<br>(Minimum V <sub>DD</sub> )                           | V <sub>IH1</sub> | -           | Pin Groups 1 and 2<br>V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>Use pattern <i>main_pattern</i><br>Note 5                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - 1995<br>ern |      | mV       |

| CMOS Output<br>Voltage, Low Level<br>(High Current Buffer<br>at Minimum V <sub>DD</sub> ) | $V_{OL1\_H}$     | 3007        | Pin Group 4 - 400 $V_{DD}$ = 2.85V, $V_{SS}$ = 0V $I_{OL}$ = -6mA Use pattern main_pattern Note 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               | 400  | mV       |

| Characteristics                                                                                      | Symbols             | MIL-STD-883 | Test Conditions                                                                                                        | Lin  | nits | Units |

|------------------------------------------------------------------------------------------------------|---------------------|-------------|------------------------------------------------------------------------------------------------------------------------|------|------|-------|

|                                                                                                      |                     | Test Method |                                                                                                                        | Min  | Max  |       |

| CMOS Output<br>Voltage, Low Level<br>(Low Current Buffer<br>at Minimum V <sub>DD</sub> )             | V <sub>OL1_L</sub>  | 3007        | Pin Group 5<br>$V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$I_{OL}$ = -200 $\mu$ A<br>Use pattern main_pattern<br>Note 6        | -    | 400  | mV    |

| CMOS Output<br>Voltage, Low Level<br>(Buffer with Serial<br>Resistor at<br>Minimum V <sub>DD</sub> ) | V <sub>OL1_R</sub>  | 3007        | Pin Group 6<br>$V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$I_{OL}$ = -100 $\mu$ A<br>Use pattern <i>main_pattern</i><br>Note 6 | -    | 400  | mV    |

| CMOS Output<br>Voltage, Low Level<br>(Open Drain Buffer<br>at Minimum V <sub>DD</sub> )              | V <sub>OL1_OD</sub> | 3007        | Pin Group 7<br>$V_{DD} = 2.85V$ , $V_{SS} = 0V$<br>$I_{OL} = -1mA$<br>Use pattern main_pattern<br>Note 6               | -    | 400  | mV    |

| CMOS Output<br>Voltage, Low Level<br>(High Current Buffer<br>at Maximum V <sub>DD</sub> )            | V <sub>OL2_H</sub>  | 3007        | Pin Group 4<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$I_{OL} = -6mA$<br>Use pattern main_pattern<br>Note 6               | -    | 400  | mV    |

| CMOS Output<br>Voltage, Low Level<br>(Low Current Buffer<br>at Maximum V <sub>DD</sub> )             | V <sub>OL2_L</sub>  | 3007        | Pin Group 5<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$I_{OL} = -200\mu A$<br>Use pattern main_pattern<br>Note 6          | -    | 400  | mV    |

| CMOS Output<br>Voltage, Low Level<br>(Buffer with Serial<br>Resistor at<br>Maximum V <sub>DD</sub> ) | V <sub>OL2_R</sub>  | 3007        | Pin Group 6<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$I_{OL} = -100\mu A$<br>Use pattern main_pattern<br>Note 6          | -    | 400  | mV    |

| CMOS Output<br>Voltage, Low Level<br>(Open Drain Buffer<br>at Maximum V <sub>DD</sub> )              | V <sub>OL2_OD</sub> | 3007        | Pin Group 7<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$I_{OL} = -1mA$<br>Use pattern main_pattern<br>Note 6               | -    | 400  | mV    |

| CMOS Output<br>Voltage, High Level<br>(High Current Buffer<br>at Minimum V <sub>DD</sub> )           | V <sub>ОН1_Н</sub>  | 3006        | Pin Group 4<br>$V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$I_{OH}$ = 3mA<br>Use pattern <i>main_pattern</i><br>Note 6          | 2.45 | -    | V     |

| CMOS Output<br>Voltage, High Level<br>(Low Current Buffer<br>at Minimum V <sub>DD</sub> )            | V <sub>OH1_L</sub>  | 3006        | Pin Group 5<br>$V_{DD} = 2.85V$ , $V_{SS} = 0V$<br>$I_{OH} = 200\mu A$<br>Use pattern main_pattern<br>Note 6           | 2.45 | -    | V     |

| Characteristics                                                                                       | Symbols            | MIL-STD-883 | Test Conditions                                                                                                                      | Lin  | nits | Units    |

|-------------------------------------------------------------------------------------------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|

|                                                                                                       |                    | Test Method |                                                                                                                                      | Min  | Max  |          |

| CMOS Output<br>Voltage, High Level<br>(Buffer with Serial<br>Resistor at<br>Minimum V <sub>DD</sub> ) | V <sub>OH1_R</sub> | 3006        | Pin Group 6<br>$V_{DD} = 2.85V$ , $V_{SS} = 0V$<br>$I_{OH} = 100\mu A$<br>Use pattern <i>main_pattern</i><br>Note 6                  | 2.45 | -    | V        |

| CMOS Output<br>Voltage, High Level<br>(High Current Buffer<br>at Maximum V <sub>DD</sub> )            | $V_{OH2\_H}$       | 3006        | Pin Group 4<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$I_{OH} = 3mA$<br>Use pattern $main\_pattern$<br>Note 6                           | 3.05 | 1    | V        |

| CMOS Output<br>Voltage, High Level<br>(Low Current Buffer<br>at Maximum V <sub>DD</sub> )             | $V_{OH2\_L}$       | 3006        | Pin Group 5<br>$V_{DD}$ = 3.45V, $V_{SS}$ = 0V<br>$I_{OH}$ = 200 $\mu$ A<br>Use pattern <i>main_pattern</i><br>Note 6                | 3.05 | 1    | <b>V</b> |

| CMOS Output<br>Voltage, High Level<br>(Buffer with Serial<br>Resistor at<br>Maximum V <sub>DD</sub> ) | $V_{OH2\_R}$       | 3006        | Pin Group 6<br>$V_{DD}$ = 3.45V, $V_{SS}$ = 0V<br>$I_{OH}$ = 100 $\mu$ A<br>Use pattern <i>main_pattern</i><br>Note 6                | 3.05 | 1    | <b>V</b> |

| CMOS Input<br>Leakage Current,<br>Low Level (with<br>Pull-down)                                       | I <sub>IL_PD</sub> | 3009        | Pin Group 1<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$V_{IN}$ (Under Test) = 0V<br>$V_{IN}$ (Remaining Inputs) = 3.45V                 | -250 | 250  | nA       |

| CMOS Input<br>Leakage Current,<br>Low Level                                                           | I <sub>IL</sub>    | 3009        | Pin Group 2<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$V_{IN}$ (Under Test) = 0V<br>$V_{IN}$ (Remaining Inputs) = 3.45V                 | -15  | -50  | μА       |

| CMOS Input<br>Leakage Current,<br>High Level (with<br>Pull-down)                                      | I <sub>IH_PD</sub> | 3010        | Pin Group 1<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$V_{IN}$ (Under Test) = 3.45V<br>$V_{IN}$ (Remaining Inputs) = 0V                 | 30   | 75   | μΑ       |

| CMOS Input<br>Leakage Current,<br>High Level                                                          | I <sub>IH</sub>    | 3010        | Pin Group 2<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$V_{IN}$ (Under Test) = 3.45V<br>$V_{IN}$ (Remaining Inputs) = 0V                 | 15   | 50   | μΑ       |

| High-Impedance<br>Output Leakage<br>Current, High Level                                               | I <sub>OZH</sub>   | 3021        | Pin Group 7<br>$V_{DD} = 3.45V$ , $V_{SS} = 0V$<br>$V_{OUT} = 3.45V$<br>Use pattern main_pattern,<br>stop at label pdwn_sp<br>Note 7 | -    | 10   | μА       |

| Characteristics                                                                                  | Symbols           | MIL-STD-883 | Test Conditions                                                                                                                                          | Lin | nits | Units |

|--------------------------------------------------------------------------------------------------|-------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|

|                                                                                                  |                   | Test Method |                                                                                                                                                          | Min | Max  |       |

| Serial Clock<br>Minimum Pulse<br>Width High<br>(Minimum V <sub>DD</sub> )                        | t <sub>CLKH</sub> | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From posedge SCLK (↑#15)<br>to negedge SCLK (↓#15)<br>Use pattern <i>main_pattern</i><br>Note 10        | -   | 30   | ns    |

| Serial Clock<br>Minimum Pulse<br>Width Low<br>(Minimum V <sub>DD</sub> )                         | t <sub>CLKL</sub> | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From negedge SCLK<br>(↓#15) to posedge SCLK<br>(↑#15)<br>Use pattern <i>main_pattern</i><br>Note 10     | -   | 30   | ns    |

| Serial Data to Serial<br>Clock Setup Time<br>(Minimum V <sub>DD</sub> )                          | t <sub>DSU</sub>  | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From any edge of SDATA<br>(#14) to posedge SCLK<br>(†#15)<br>Use pattern <i>main_pattern</i><br>Note 10 | 1   | 10   | ns    |

| Serial Data to Serial<br>Clock Hold Time<br>(Minimum V <sub>DD</sub> )                           | t <sub>DH</sub>   | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From posedge SCLK (↑#15)<br>to any edge of SDATA<br>(#14)<br>Use pattern <i>main_pattern</i><br>Note 10 | 1   | 10   | ns    |

| Serial Load<br>Minimum Pulse<br>Width High<br>(Minimum V <sub>DD</sub> )                         | t <sub>PWH</sub>  | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From posedge S_WR<br>(↑#13) to negedge S_WR<br>(↓#13)<br>Use pattern <i>main_pattern</i><br>Note 10     | 1   | 30   | ns    |

| Serial Clock Rising<br>Edge to Serial Load<br>Rising Edge<br>(Minimum V <sub>DD</sub> )          | t <sub>CWR</sub>  | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From posedge SCLK (↑#15)<br>to posedge S_WR (↑#13)<br>Use pattern <i>main_pattern</i><br>Note 10        | -   | 30   | ns    |

| Serial Clock Falling<br>Edge to<br>Enhancement Write<br>Transition (Minimum<br>V <sub>DD</sub> ) | t <sub>CE</sub>   | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From negedge SCLK<br>(↓#15) to any edge of<br>E_WR (#19)<br>Use pattern <i>main_pattern</i><br>Note 10  | -   | 30   | ns    |

| Serial Load Falling<br>Edge to Serial Clock<br>Rising Edge<br>(Minimum V <sub>DD</sub> )         | t <sub>WRC</sub>  | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From negedge S_WR<br>(↓#13) to posedge SCLK<br>(↑#15)<br>Use pattern <i>main_pattern</i><br>Note 10     | -   | 30   | ns    |

| Characteristics                                                                        | Symbols              | MIL-STD-883 | Test Conditions                                                                                                                                         | Lin | nits | Units |

|----------------------------------------------------------------------------------------|----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|

|                                                                                        |                      | Test Method |                                                                                                                                                         | Min | Max  |       |

| Enhancement<br>Transition to Serial<br>Clock Rising Edge<br>(Minimum V <sub>DD</sub> ) | t <sub>EC</sub>      | 3003        | V <sub>DD</sub> = 2.85V, V <sub>SS</sub> = 0V<br>From any edge of E_WR<br>(#19) to posedge SCLK<br>(↑#15)<br>Use pattern <i>main_pattern</i><br>Note 10 | -   | 30   | ns    |

| MSEL Output Rising<br>Delay from FIN<br>Rising Edge<br>(Minimum V <sub>DD</sub> )      | t <sub>DOH</sub>     | 3003        | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>From posedge FIN (†#27)<br>to posedge DOUT (↓#32)<br>Use pattern <i>main_pattern</i><br>Note 10                      | -   | 30   | ns    |

| MSEL Output<br>Falling Delay from<br>FIN Rising Edge<br>(Minimum V <sub>DD</sub> )     | t <sub>DOL</sub>     | 3003        | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>From posedge FIN (†#27)<br>to negedge DOUT (↓#32)<br>Use pattern <i>main_pattern</i><br>Note 10                      | -   | 30   | ns    |

| Reference Clock<br>Input Sensitivity                                                   | S <sub>FR</sub>      | -           | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$f_{IN}$ = 100MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11                           | -   | -5   | dBm   |

| Prescaler Input<br>Sensitivity<br>(Minimum f <sub>IN</sub> )                           | S <sub>FIN250</sub>  | -           | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$f_{IN}$ = 250MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11                           | -   | -5   | dBm   |

| Prescaler Input<br>Sensitivity<br>(Medium 1 f <sub>IN</sub> )                          | S <sub>FIN300</sub>  | -           | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$f_{IN}$ = 300MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11                           | -   | -5   | dBm   |

| Prescaler Input<br>Sensitivity<br>(Medium 2 f <sub>IN</sub> )                          | S <sub>FIN500</sub>  | -           | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$f_{IN}$ = 500MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11                           | -   | -5   | dBm   |

| Prescaler Input<br>Sensitivity<br>(Medium 3 f <sub>IN</sub> )                          | S <sub>FIN1000</sub> | -           | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$f_{IN}$ = 1000MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11                          | -   | -5   | dBm   |

| Prescaler Input<br>Sensitivity<br>(Medium 4 f <sub>IN</sub> )                          | S <sub>FIN2000</sub> | -           | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$f_{IN}$ = 2000MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11                          | -   | -5   | dBm   |

| Characteristics                                                                             | Symbols              | MIL-STD-883 | Test Conditions                                                                                                                | Lin  | nits       | Units  |

|---------------------------------------------------------------------------------------------|----------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------|------|------------|--------|

|                                                                                             |                      | Test Method |                                                                                                                                | Min  | Max        |        |

| Prescaler Input<br>Sensitivity<br>(Medium 5 f <sub>IN</sub> )                               | S <sub>FIN3000</sub> | -           | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$f_{IN}$ = 3000MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11 | -    | -5         | dBm    |

| Prescaler Input<br>Sensitivity<br>(Maximum f <sub>IN</sub> )                                | S <sub>FIN3250</sub> | -           | $V_{DD}$ = 2.85V, $V_{SS}$ = 0V<br>$f_{IN}$ = 3250MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11 | -    | <b>-</b> 5 | dBm    |

| Prescaler Input<br>Sensitivity<br>(Maximum f <sub>IN</sub> ,<br>Typical V <sub>DD</sub> )   | S <sub>FIN3300</sub> | -           | $V_{DD} = 3.15V$ , $V_{SS} = 0V$<br>$f_{IN} = 3300MHz$<br>Use pattern <i>mode</i> , stop at label <i>mode_sp2</i><br>Note 11   | -    | 0          | dBm    |

| Prescaler Input<br>Sensitivity<br>(> Maximum f <sub>IN</sub> ,<br>Typical V <sub>DD</sub> ) | S <sub>FIN3550</sub> | -           | $V_{DD}$ = 3.15V, $V_{SS}$ = 0V<br>$f_{IN}$ = 3550MHz<br>Use pattern <i>mode</i> , stop at<br>label <i>mode_sp2</i><br>Note 11 | -    | 0          | dBm    |

| Supply Current<br>during Phase Noise<br>Measurements,<br>Typical Low V <sub>DD</sub>        | I <sub>DDOPPN1</sub> | 3005        | $V_{DD} = 3V$ , $V_{SS} = 0V$<br>Note 13                                                                                       | 5    | 80         | mA     |

| Supply Current<br>during Phase Noise<br>Measurements,<br>Typical High V <sub>DD</sub>       | I <sub>DDOPPN2</sub> | 3005        | $V_{DD} = 3.3V$ , $V_{SS} = 0V$<br>Note 13                                                                                     | 5    | 80         | mA     |

| Phase Noise @<br>100Hz Offset,<br>Typical Low V <sub>DD</sub>                               | PN <sub>100</sub> 1  | -           | $V_{DD} = 3V$ , $V_{SS} = 0V$<br>Note 12                                                                                       | -95  | -70        | dBc/Hz |

| Phase Noise @<br>1kHz Offset,<br>Typical Low V <sub>DD</sub>                                | PN <sub>1K</sub> 1   | -           | $V_{DD} = 3V$ , $V_{SS} = 0V$<br>Note 12                                                                                       | -101 | -81        | dBc/Hz |

| Phase Noise @<br>10kHz Offset,<br>Typical Low V <sub>DD</sub>                               | PN <sub>10K</sub> 1  | -           | $V_{DD} = 3V$ , $V_{SS} = 0V$<br>Note 12                                                                                       | -107 | -89        | dBc/Hz |

| Phase Noise @<br>100Hz Offset,<br>Typical High V <sub>DD</sub>                              | PN <sub>100</sub> 2  | -           | $V_{DD} = 3.3V$ , $V_{SS} = 0V$<br>Note 12                                                                                     | -95  | -83        | dBc/Hz |

| Phase Noise @<br>1kHz Offset,<br>Typical High V <sub>DD</sub>                               | PN <sub>1K</sub> 2   | -           | $V_{DD} = 3.3V$ , $V_{SS} = 0V$<br>Note 12                                                                                     | -101 | -91        | dBc/Hz |

| Phase Noise @<br>10kHz Offset,<br>Typical High V <sub>DD</sub>                              | PN <sub>10K</sub> 2  | -           | $V_{DD} = 3.3V$ , $V_{SS} = 0V$<br>Note 12                                                                                     | -107 | -96        | dBc/Hz |

#### **NOTES:**

#### Continuity test

Comparison limit value, no measurement value recorded.

#### 2. Dynamic current

For measurement of the dynamic current, the pattern  $main\_pattern$  is used and loops from first to last vector. Instantaneous current is measured and recorded (without any link to a specific vector number). Total combined current for all  $V_{DD}$  pins. During the test, outputs are loaded with a capacitive load < 62pF (tester load) but without active load. Comparators are disabled during this test.

#### 3. Quiescent current

During quiescent current test, outputs are loaded without active current load but with a capacitive load < 62 pF (tester load).

The measurement is performed with the device having been initialised using pattern mode, stopped at end of vector labelled  $pdwn_sp$ . Total combined current of all  $V_{DD}$  pins.

The measurement accuracy is better than 1µA.

#### 4. Functional test

During functional test, outputs are loaded with an active current load (when specified) and a capacitive load < 62pF (tester load). For the active current load, the threshold load switching is set to  $V_{DD}/2$ .

Output comparison is performed as "strobe comparison". Strobe is placed 5% before the end of the period. For the open-drain output (i.e. pin 43, LD), comparison to the "High-Impedance" state may be masked for some vectors.

#### Input voltages

During input voltage test, outputs are loaded with an active current load (when specified) and a capacitive load < 62pF (tester load). For the active current load, the threshold load switching is set to  $V_{DD}/2$ .

Measurements are performed using the test pattern *main\_pattern* (between the labels "main\_st" and "end\_u\_d"). The pattern is run with increasing or decreasing input voltage value of the pin under test until the first output fails. Remaining pins toggle with nominal input voltages.

All the values are tested and recorded for each input.

The measurement accuracy is better than 100mV.

#### 6. Output voltages

Measurements are performed using the test pattern main pattern.

The device is configured into correct state so that outputs are placed in high or low voltages. Output current is sourced/sinked and the resulting voltage is measured.

All the values are tested and recorded for each output.

#### 7. High impedance leakage current

The device is configured into the correct state using the pattern *main\_pattern* so that the pin under test is in high impedance conditions (i.e. stop at label "llzhh").

All the values are tested and recorded for each output.

#### Test patterns

Number of vectors (clock periods) for patterns used during test are:

- main\_pattern 4371 vectors @ 1MHz (period = 1000ns) and 10MHz (period = 100ns)

- mode 41 vectors @ 1 MHz (period = 1000ns)

#### 9. Timing generators

All inputs use DATA mode timing generators (i.e. NRZ mode with zero delay) unless otherwise specified. The table below describes the timing generators. All patterns use the same set of timing generators.

For a few timing generators, Pin Group 1 is split into the following subgroups:

- Subgroup 1.1  $R_0$  to  $R_3$ ,  $A_0$ ,  $A_1$ ,  $A_3$ ,  $\overline{BMODE}$  and  $\overline{ENH}$

- Subgroup 1.2 D<sub>0</sub> to D<sub>7</sub>

- Subgroup 1.3 A\_WR, M<sub>1</sub>\_WR, M<sub>2</sub>\_WR (or A<sub>2</sub>) and HOP\_WR

| Timing<br>Generator<br>Number | Period<br>(ns) | Pin Group                               | Delay<br>(ns) | Width<br>(ns) | Comp.<br>Start<br>(ns) | Comp.<br>Stop<br>(ns) | Format |

|-------------------------------|----------------|-----------------------------------------|---------------|---------------|------------------------|-----------------------|--------|

| 0                             | 1000           | 1 to 3                                  | 0             | -             | -                      | -                     | NRZ    |

|                               |                | 4 to 7                                  | -             | -             | -                      | 900                   | EDGE   |

| 1                             | 1000           | 1                                       | 0             | -             | -                      | -                     | NRZ    |

|                               |                | 2 and 3                                 | 100           | -             | -                      | -                     | NRZ    |

|                               |                | 4 to 7                                  | -             | -             | -                      | 950                   | EDGE   |

| 2                             | 1000           | 1 (except SCLK pin)                     | 0             | -             | -                      | -                     | NRZ    |

|                               |                | SCLK pin                                | 250           | -             | -                      | -                     | NRZ    |

|                               |                | 2 and 3                                 | 100           | -             | -                      | -                     | NRZ    |

|                               |                | 4 to 7                                  | -             | -             | -                      | 950                   | EDGE   |

| 3                             | 1000           | 1                                       | 0             | -             | -                      | -                     | NRZ    |

|                               |                | 2 and 3                                 | 100           | -             | -                      | -                     | NRZ    |

|                               |                | 4 to 7                                  | -             | -             | -                      | 950                   | EDGE   |

| 4                             | 1000           | 1                                       | 0             | -             | -                      | -                     | NRZ    |

|                               |                | 2 and 3                                 | 100           | -             | -                      | -                     | NRZ    |

|                               |                | 4 to 7                                  | -             | -             | -                      | 950                   | EDGE   |

| 5                             | 100            | 1 (except SCLK pin)                     | 0             | -             | -                      | -                     | NRZ    |

|                               |                | SCLK pin                                | 25            | -             | -                      | -                     | NRZ    |

|                               |                | 2 and 3                                 | 10            | -             | -                      | -                     | NRZ    |

|                               |                | 4 to 7                                  | -             | -             | -                      | 95                    | EDGE   |

| 6                             | 1000           | Subgroups 1.1 and 1.2                   | 5             | -             | -                      | -                     | NRZ    |

|                               |                | Subgroup 1.3                            | 300           | -             | -                      | -                     | NRZ    |

|                               |                | 2 and 3                                 | 100           | -             | -                      | -                     | NRZ    |

|                               |                | 4 and 7                                 | -             | -             | -                      | 950                   | EDGE   |

| 7                             | 1000           | 1 (except Subgroup<br>1.2 and E_WR pin) | 5             | -             | -                      | -                     | NRZ    |

|                               |                | Subgroup 1.2                            | 100           | -             | -                      | -                     | NRZ    |

|                               |                | E_WR pin                                | 300           | -             | -                      | -                     | NRZ    |

|                               |                | 2 and 3                                 | 500           | -             | -                      | -                     | NRZ    |

|                               |                | 4 and 7                                 | -             | -             | -                      | 950                   | EDGE   |

| Timing<br>Generator<br>Number | Period<br>(ns) | Pin Group                                   | Delay<br>(ns) | Width<br>(ns) | Comp.<br>Start<br>(ns) | Comp.<br>Stop<br>(ns) | Format |

|-------------------------------|----------------|---------------------------------------------|---------------|---------------|------------------------|-----------------------|--------|

| 8                             | 1000           | 1 (except S_WR,<br>S_CLK and SDATA<br>pins) | 0             | -             | -                      | -                     | NRZ    |

|                               |                | S_WR pin                                    | 600           | -             | ı                      | -                     | NRZ    |

|                               |                | SCLK pin                                    | 250           | -             | -                      | -                     | NRZ    |

|                               |                | SDATA pin                                   | 100           | -             | -                      | -                     | NRZ    |

|                               |                | 2 and 3                                     | 100           | -             | -                      | -                     | NRZ    |

|                               |                | 4 to 7                                      | -             | -             | -                      | 950                   | EDGE   |

| 10                            | 1000           | 1                                           | 0             | -             | -                      | -                     | NRZ    |