Page 1 of 28

# INTEGRATED CIRCUITS, SILICON MONOLITHIC, 10-BIT, 2.2GSPS, ANALOGUE TO DIGITAL CONVERTER

## BASED ON TYPE AT84AS008

ESCC Detail Specification No. 9407/004

| Issue 2 | August 2015 |

|---------|-------------|

Document Custodian: European Space Agency – see https://escies.org

PAGE 2

#### LEGAL DISCLAIMER AND COPYRIGHT

European Space Agency, Copyright © 2015. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

PAGE 3

### **DOCUMENTATION CHANGE NOTICE**

(Refer to https://escies.org for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION                                               |

|---------|------------------------------------------------------------------|

| 936     | Specification upissued to incorporate editorial changes per DCR. |

**ISSUE 2**

### TABLE OF CONTENTS

| 1       | GENERAL                                                               | 5  |

|---------|-----------------------------------------------------------------------|----|

| 1.1     | SCOPE                                                                 | 5  |

| 1.2     | APPLICABLE DOCUMENTS                                                  | 5  |

| 1.3     | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS                  | 5  |

| 1.4     | THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS                 | 5  |

| 1.4.1   | The ESCC Component Number                                             | 5  |

| 1.4.2   | Component Type Variants                                               | 5  |

| 1.5     | MAXIMUM RATINGS                                                       | 6  |

| 1.6     | HANDLING PRECAUTIONS                                                  | 7  |

| 1.7     | PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION                       | 7  |

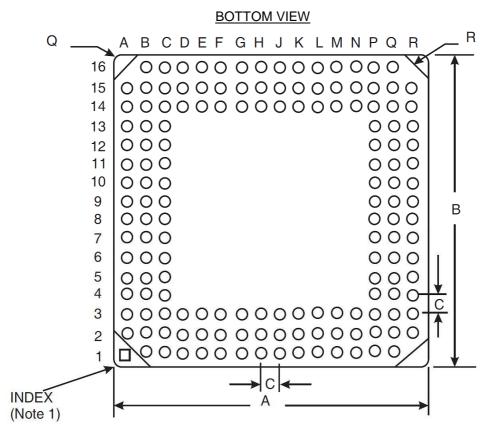

| 1.7.1   | Column Grid Array Package (CI-CGA152) - 152 columns                   | 7  |

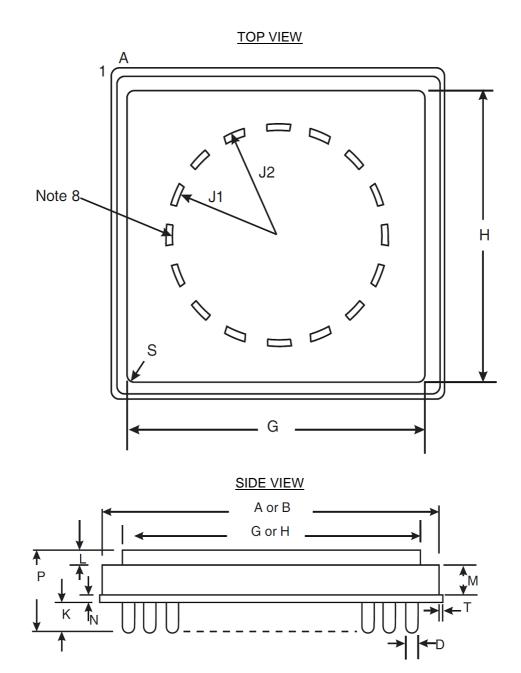

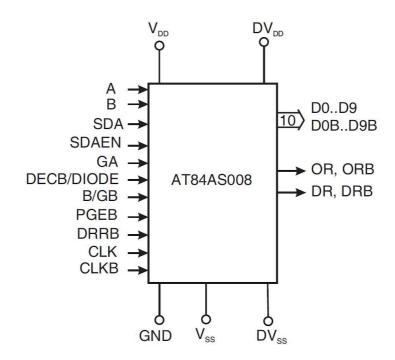

| 1.8     | FUNCTIONAL DIAGRAMS                                                   | 9  |

| 1.9     | PIN ASSIGNMENT AND DESCRIPTION                                        | 10 |

| 1.10    | TRUTH TABLE AND TIMING DIAGRAMS                                       | 12 |

| 1.11    | PROTECTION NETWORKS                                                   | 14 |

| 2       | REQUIREMENTS                                                          | 15 |

| 2.1     | GENERAL                                                               | 15 |

| 2.1.1   | Deviations from the Generic Specification                             | 15 |

| 2.1.1.1 | Deviations from Screening Tests - Chart F3                            | 15 |

| 2.2     | MARKING                                                               | 15 |

| 2.3     | ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES            | 15 |

| 2.3.1   | Room Temperature Electrical Measurements                              | 15 |

| 2.3.2   | High and Low Temperatures Electrical Measurements                     | 23 |

| 2.4     | PARAMETER DRIFT VALUES                                                | 23 |

| 2.5     | INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS                    | 25 |

| 2.6     | POWER BURN-IN CONDITIONS                                              | 25 |

| 2.7     | OPERATING LIFE CONDITIONS                                             | 25 |

| 2.8     | TOTAL DOSE RADIATION TESTING                                          | 26 |

| 2.8.1   | Bias Conditions and Total Dose Level for Total Dose Radiation Testing | 26 |

| 2.8.2   | Electrical Measurements for Total Dose Radiation Testing              | 26 |

**ISSUE 2**

#### 1 <u>GENERAL</u>

#### 1.1 <u>SCOPE</u>

This specification details the ratings, physical and electrical characteristics and test and inspection data for the component type variants and/or the range of components specified below. It supplements the requirements of, and shall be read in conjunction with, the ESCC Generic Specification listed under Applicable Documents.

#### 1.2 APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:

- (a) ESCC Generic Specification No. 9000

- (b) MIL-STD-883, Test Methods and Procedures for Microelectronics

#### 1.3 TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESCC Basic Specification No. 21300 shall apply.

#### 1.4 THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS

1.4.1 <u>The ESCC Component Number</u> The ESCC Component Number shall be constituted as follows:

940700401R

- Detail Specification Reference: 9407004

- Component Type Variant Number: 01

- Total Dose Radiation Level Letter: R

#### 1.4.2 <u>Component Type Variants</u>

The component type variants applicable to this specification are as follows:

| Variant | Based on  | Case      | Lead/Terminal       | Weight | Total Dose Radiation |

|---------|-----------|-----------|---------------------|--------|----------------------|

| Number  | Type      |           | Material and Finish | max g  | Level Letter         |

| 01      | AT84AS008 | CI-CGA152 | R1                  | 9.1    | R [100kRAD(Si)]      |

The lead/terminal material and finish shall be in accordance with the requirements of ESCC Basic Specification No. 23500.

The total dose radiation level letter shall be as defined in ESCC Basic Specification no. 22900. If an alternative radiation test level is specified in the Purchase Order the letter shall be changed accordingly.

PAGE 6

#### 1.5 MAXIMUM RATINGS

The maximum ratings shall not be exceeded at any time during use or storage.

Maximum ratings shall only be exceeded during testing to the extent specified in this specification and when stipulated in Test Methods and Procedures of the ESCC Generic Specification.

| Characteristics                              | Symbols                                  | Maximum Ratings                                                      | Units            | Remarks          |

|----------------------------------------------|------------------------------------------|----------------------------------------------------------------------|------------------|------------------|

| Analogue Positive Supply Voltage<br>Range    | V <sub>DD</sub>                          | GND to 6                                                             | V                | Note 1           |

| Analogue Negative Supply<br>Voltage Range    | V <sub>SS</sub>                          | GND to -5.5                                                          | V                | Note 1           |

| Digital Positive Supply Voltage<br>Range     | DV <sub>DD</sub>                         | GND -1.1 to 2                                                        | V                | Note 1           |

| Digital Negative Supply Voltage<br>Range     | DV <sub>SS</sub>                         | GND to -5.5                                                          | V                | Note 1           |

| Difference between Digital<br>Supplies       | DV <sub>DD</sub> - DV <sub>SS</sub>      | 7                                                                    | V                |                  |

| Difference between Negative<br>Supplies      | V <sub>SS</sub> - DV <sub>SS</sub>       | 0.3                                                                  | V                |                  |

| Analogue Input Voltage Range                 | V <sub>A</sub> , V <sub>B</sub>          | -1.5 to 1.5                                                          | V                |                  |

| Differential Analogue Input<br>Voltage Range | V <sub>A</sub> - V <sub>B</sub>          | -1.5 to 1.5                                                          | V                |                  |

| Clock Input Common Mode<br>Voltage Range     | (V <sub>CLK</sub> +V <sub>CLKB</sub> )/2 | -1.5 to 0.6                                                          | V                |                  |

| Differential Clock Input Voltage<br>Range    | V <sub>CLK</sub> - V <sub>CLKB</sub>     | -1 to 1                                                              | V <sub>p-p</sub> |                  |

| Static Input Voltage Range                   | V <sub>SI</sub>                          | -1 to 0.8                                                            | V                | Note 2           |

| Digital Input Voltage Range                  | V <sub>DI</sub>                          | -5 to +0.8                                                           | V                | Note 3           |

| Digital Output Voltage Range                 | V <sub>OD</sub>                          | $DV_{DD}$ min. operating<br>-2.2 to $DV_{DD}$ max.<br>operating +0.8 | V                |                  |

| Device Power Dissipation<br>(Continuous)     | P <sub>D</sub>                           | Note 4                                                               | W                | Note 5           |

| Operating Temperature Range                  | T <sub>op</sub>                          | -55 to +125                                                          | °C               | T <sub>amb</sub> |

| Storage Temperature Range                    | T <sub>stg</sub>                         | -65 to +150                                                          | °C               |                  |

| Soldering Temperature                        | T <sub>sol</sub>                         | +300                                                                 | °C               |                  |

| Junction Temperature                         | Tj                                       | +130                                                                 | °C               | Note 5           |

| Thermal Resistance Junction to Ambient       | R <sub>th(j-a)</sub>                     | 30                                                                   | °C/W             | Note 5           |

#### NOTES:

- 1. The maximum ratings are limiting values referenced to GND = 0V.

- 2. Applies to the GA and SDA inputs.

- 3. Applies to the SDAEN, DRRB, B/GB, PGEB and DECB inputs.

**ISSUE 2**

- 4. The maximum device dissipation shall be determined by the formula:  $P_{D} = |I_{DD}| \times |V_{DD}| + |I_{SS}| \times |V_{SS}| + |DI_{DD}| \times |DV_{DD}| + |DI_{SS}| \times |DV_{SS}|$

- 5. An external heatsink shall be used.

#### 1.6 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are categorised as Class 1 per ESCC Basic Specification No. 23800 with a Minimum Critical Path Failure Voltage of 750 Volts.

#### 1.7 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

1.7.1 Column Grid Array Package (CI-CGA152) - 152 columns

ESCC Detail Specification

No. 9407/004

PAGE 8

| Symbols | Dimensi  | Notes |       |

|---------|----------|-------|-------|

|         | Min      | Max   | noles |

| A, B    | 20.8     | 21.2  |       |

| С       | 1.27 BSC |       | 2     |

| D       | 0.79     | 0.99  | 3, 4  |

| G, H    | 18.32    | 18.68 |       |

| J1      | 6.5      | 6.9   | 5     |

| J2      | 6.8      | 7.2   | 5     |

| К       | 1.545    | 1.695 | 4, 9  |

**ESCC** Detail Specification

**ISSUE 2**

| Questo a la | Dimensi | Notoo |       |

|-------------|---------|-------|-------|

| Symbols     | Min     | Max   | Notes |

| L           | 0.71    | 0.89  |       |

| М           | 1.5     | 1.82  |       |

| Ν           | 0.25    | 0.35  |       |

| Р           | 4.02    | 4.82  |       |

| Q           | -       | 0.4   | 6     |

| R           | -       | 1.8   | 6     |

| S           | -       | 0.5   | 6     |

| Т           | -       | 0.2   | 7     |

#### NOTES:

- 1. Index Mark: a terminal identification mark shall be located in the A1 position and shall have no column attached.

- 152 columns. The true position column spacing is 1.27mm between centrelines. Each column shall be located within ±0.15mm of its true longitudinal position relative to A1 and the highest column or row number in each axis.

- 3. Diameter.

- 4. All columns.

- 5. Radius. J2 shall always be greater than J1.

- 6. Chamfer, applies to all four corners.

- 7. Nominal 0mm, applied all around the periphery.

- 8. Nickel Gold metallised marking that shall define the footprint for the external heatsink.

- 9. The column coplanarity shall not exceed 150µm.

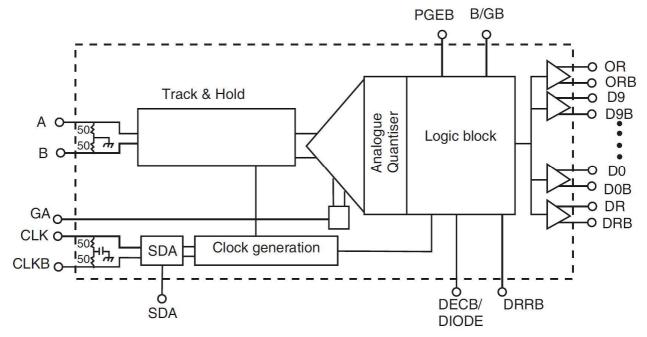

#### 1.8 <u>FUNCTIONAL DIAGRAMS</u>

**ISSUE 2**

#### 1.9 PIN ASSIGNMENT AND DESCRIPTION

| Name             | Pin number                                                                                                                                                                                                                               | Description                                                  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| POWER SUPPLIES   |                                                                                                                                                                                                                                          |                                                              |

| V <sub>DD</sub>  | K1, K2, J3, K3, B6, C6, A7, B7, C7,<br>P8, Q8, R8                                                                                                                                                                                        | 5V analogue supply (connected to<br>same power supply plane) |

| GND              | B1, C1, D1, G1, M1, Q1, B2, C2,<br>D2, E2, F2, G2, N2, P2, Q2, A3, B3,<br>D3, E3, F3, G3, N3, P4, Q4, R4, A5,<br>P5, Q5, P6, Q6, P7, Q7, R7, B9,<br>B10, B11, R11, P12, A14, B14,<br>C14, G14, K14, P14, Q14, R14,<br>B15, Q15, B16, Q16 | Analogue ground                                              |

| V <sub>SS</sub>  | H1, J1, L1, H2, J2, L2, M2, C3, H3,<br>L3, M3, P3, Q3, R3, A4, B4, C4, B5,<br>C5, A8, B8, C8, C9, P9, Q9, C10,<br>Q10, R10                                                                                                               | -5V analogue supply (connected to same power supply plane)   |

| DV <sub>DD</sub> | P10, C11, P11, Q11, A12, B12,<br>C12, Q12, R12, D14, E14, F14,<br>L14, M14, N14                                                                                                                                                          | Digital positive supply                                      |

| DV <sub>SS</sub> | A13, B13, C13, P13, Q13, R13,<br>H14, J14                                                                                                                                                                                                | -5V or -2.2V Digital negative supply                         |

PAGE 11

| Name                                                   | Pin number                                          | Description                                                                                                                                                                                                                                                                                                                          |  |

|--------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ANALOGUE INPUTS                                        |                                                     |                                                                                                                                                                                                                                                                                                                                      |  |

| A                                                      | R5                                                  | In-phase (+) analogue input signal<br>of the differential Sample & Hold<br>preamplifier                                                                                                                                                                                                                                              |  |

| В                                                      | R6                                                  | Inverted phase (-) analogue input<br>signal of the differential Sample &<br>Hold preamplifier                                                                                                                                                                                                                                        |  |

| CLOCK INPUTS                                           |                                                     |                                                                                                                                                                                                                                                                                                                                      |  |

| CLK                                                    | E1                                                  | In-phase (+) clock input                                                                                                                                                                                                                                                                                                             |  |

| CLKB                                                   | F1                                                  | Inverted phase (-) clock input                                                                                                                                                                                                                                                                                                       |  |

| DIGITAL OUTPUTS                                        |                                                     | •                                                                                                                                                                                                                                                                                                                                    |  |

| D0, D1, D2, D3, D4, D5,<br>D6, D7, D8, D9              | D16, E16, F16, G16, J16, K16, L16,<br>M16, N16, P16 | In-phase (+) digital outputs<br>D0 is the LSB, D9 is the MSB                                                                                                                                                                                                                                                                         |  |

| D0B, D1B, D2B, D3B,<br>D4B, D5B, D6B, D7B,<br>D8B, D9B | D15, E15, F15, G15, J15, K15, L15,<br>M15, N15, P15 | Inverted phase (-) digital outputs                                                                                                                                                                                                                                                                                                   |  |

| OR                                                     | C16                                                 | In-phase (+) Out-of-Range output                                                                                                                                                                                                                                                                                                     |  |

| ORB                                                    | C15                                                 | Inverted phase (-) Out-of-Range output                                                                                                                                                                                                                                                                                               |  |

| DR                                                     | H16                                                 | In-phase (+) Data Ready signal<br>output                                                                                                                                                                                                                                                                                             |  |

| DRB                                                    | H15                                                 | Inverted phase (-) Data Ready signal output                                                                                                                                                                                                                                                                                          |  |

| ADDITIONAL FUNCTIO                                     | NS                                                  |                                                                                                                                                                                                                                                                                                                                      |  |

| B/GB                                                   | A11                                                 | <ul> <li>Binary or Gray select output format control</li> <li>Binary output format if B/GB is floating or connected to GND</li> <li>Gray output format if B/GB is connected to V<sub>SS</sub></li> </ul>                                                                                                                             |  |

| DECB / DIODE                                           | A10                                                 | <ul> <li>Decimation Function Enable or Die<br/>junction temperature measurement:</li> <li>Decimation active when LOW<br/>(Die junction temperature<br/>monitoring is then NOT<br/>POSSIBLE);</li> <li>Normal mode when HIGH or<br/>left floating</li> <li>Die Junction temperature monitoring<br/>when current is applied</li> </ul> |  |

**ISSUE 2**

| Name           | Pin number       | Description                                                                                                                                                                                                                                                                        |  |  |  |

|----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PGEB           | A9               | <ul> <li>Active low Pattern Generator<br/>Enable</li> <li>Digitised input delivered at<br/>outputs according to B/GB if<br/>PGEB is floating or connected<br/>to GND</li> <li>Checker Board pattern<br/>delivered at outputs if PGEB is<br/>connected to V<sub>SS</sub></li> </ul> |  |  |  |

| DRRB           | N1               | Asynchronous Data Ready Reset<br>function (active at ECL low level)                                                                                                                                                                                                                |  |  |  |

| GA             | R9               | Gain Adjust.                                                                                                                                                                                                                                                                       |  |  |  |

| SDA            | A6               | Sampling delay adjust                                                                                                                                                                                                                                                              |  |  |  |

| SDAEN          | P1               | Sampling delay adjust enable<br>inactive if floating or connected to<br>GND<br>active if connected to V <sub>SS</sub>                                                                                                                                                              |  |  |  |

| UNUSED COLUMNS | UNUSED COLUMNS   |                                                                                                                                                                                                                                                                                    |  |  |  |

| NC             | A2, A15, R2, R15 | Not connected but may be<br>connected to GND                                                                                                                                                                                                                                       |  |  |  |

#### 1.10 TRUTH TABLE AND TIMING DIAGRAMS

Logic Level Definitions: 1 = Digital High Level, 0 = Digital Low Level, MSB = Most Significant Bit, LSB = Least Significant Bit.

| Differential   | Voltage Level                        | Digital Output                     |                  |              |                     |  |

|----------------|--------------------------------------|------------------------------------|------------------|--------------|---------------------|--|

| Analogue Input |                                      | Binary (B/GB = GND or<br>floating) |                  | Gray (B/GB = | = V <sub>SS</sub> ) |  |

|                |                                      | MSBLSB                             | Out-of-<br>Range | MSBLSB       | Out-of-<br>Range    |  |

| > +250.25 mV   | > Top end of full-scale + 1/2 LSB    | 1111111111                         | 1                | 100000000    | 1                   |  |

| +250.25 mV     | Top end of full-scale + 1/2 LSB      | 1111111111                         | 0                | 100000000    | 0                   |  |

| +249.75 mV     | Top end of full scale - 1/2 LSB      | 1111111110                         | 0                | 100000001    | 0                   |  |

| +125.25 mV     | 3/4 full-scale + 1/2 LSB             | 1100000000                         | 0                | 101000000    | 0                   |  |

| +124.75 mV     | 3/4 full-scale - 1/2 LSB             | 1011111111                         | 0                | 1110000000   | 0                   |  |

| +0.25 mV       | Midscale + 1/2 LSB                   | 1000000000                         | 0                | 1100000000   | 0                   |  |

| -0.25 mV       | Midscale -1/2 LSB                    | 0111111111                         | 0                | 010000000    | 0                   |  |

| -124.75 mV     | 1/4 full-scale +1/2 LSB              | 0100000000                         | 0                | 0110000000   | 0                   |  |

| -124.25 mV     | 1/4 full-scale - 1/2 LSB             | 0011111111                         | 0                | 001000000    | 0                   |  |

| -249.75 mV     | Bottom end of full-scale + 1/2 LSB   | 000000001                          | 0                | 000000001    | 0                   |  |

| -250.25 mV     | Bottom end of full-scale - 1/2 LSB   | 0000000000                         | 0                | 0000000000   | 0                   |  |

| < -250.25 mV   | < Bottom end of full-scale - 1/2 LSB | 0000000000                         | 1                | 0000000000   | 1                   |  |

PAGE 13

ISSUE 2

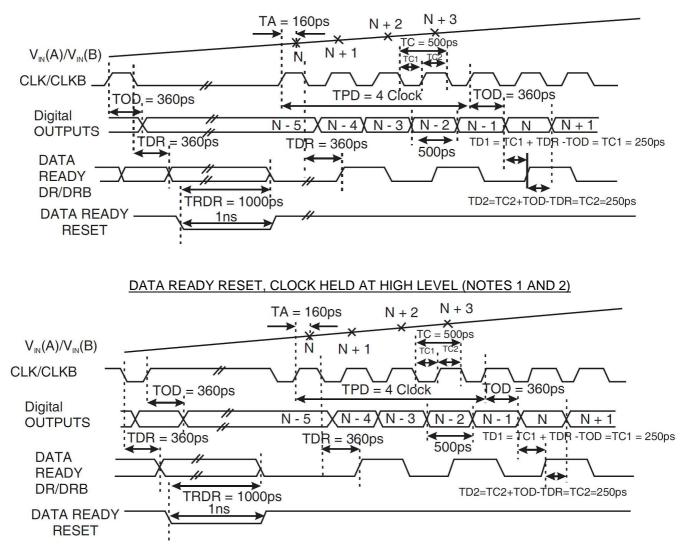

#### DATA READY RESET, CLOCK HELD AT LOW LEVEL (NOTES 1 AND 2)

#### NOTES:

- 1. 2 Gsps Clock Rate

- 2. Definition of terms:

- TA: Aperture Delay, TA is the delay between the rising edge of the differential clock inputs (CLK, CLKB) (zero crossing point) and the time at which (A or B input) is sampled.

- TC: Encoding clock period. TC = TC1 + TC2.

- TC1: Minimum clock pulse width (high)

- TC2: Minimum clock pulse width (low).

- TPD: Pipeline Delay. The number of clock cycles between the sampling edge of an input data and the associated output data being made available (not taking into account the TOD).

- TOD: Digital data Output Delay. TOD is the delay from the falling edge of the differential clock inputs (CLK, CLKB) (zero crossing point) to the next point of change in the differential output data (zero crossing) with specified load.

- TDR: Time delay from Clock to Data Ready. TDR is the time from the falling edge of the differential clock inputs (CLK, CLKB) to the next point of change in the differential output Data Ready outputs.

**ESCC** Detail Specification

PAGE 14

No. 9407/004

- TD1: Time delay from Data to Data Ready. TD1 is the time difference between Data and Data Ready. General expression is TD1 = TC1 + TDR TDO with TC = TC1 + TC2 = 1 encoding clock period.

- TD2: Time delay from Data Ready to Data. General expression is TD2 = TC2 + TDR TOD with TC = TC1 + TC2 =1 encoding clock period.

- TRDR: Time delay from Reset to Data Ready. When the pin DRRB is used as a reset pin, TRDR is the delay between the falling edge of the DRRB input and the corresponding falling edge of the Data Ready output.

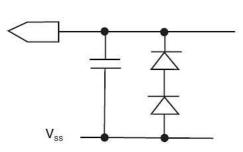

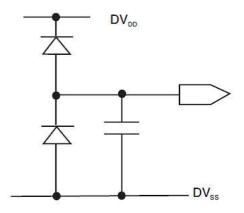

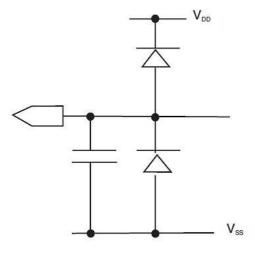

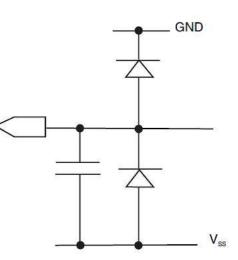

- 1.11 PROTECTION NETWORKS

Analogue and Clock Inputs

ADC Gain Adjust Input

DRRB, B/GB and PGEB Inputs

#### 2 <u>REQUIREMENTS</u>

#### 2.1 <u>GENERAL</u>

The complete requirements for procurement of the components specified herein are as stated in this specification and the ESCC Generic Specification. Permitted deviations from the Generic Specification, applicable to this specification only, are listed below.

Permitted deviations from the Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESCC requirement and do not affect the component's reliability, are listed in the appendices attached to this specification.

#### 2.1.1 <u>Deviations from the Generic Specification</u>

#### 2.1.1.1 Deviations from Screening Tests - Chart F3

- (a) High Temperature Reverse Bias Burn-in shall not be performed.

- (b) High and Low Temperature Electrical Measurement failures shall not be counted for Lot Failure.

#### 2.2 MARKING

The marking shall be in accordance with the requirements of ESCC Basic Specification No. 21700 and as follows.

The information to be marked on the component shall be:

- (a) Terminal identification.

- (b) The ESCC qualified components symbol (for ESCC qualified components only).

- (c) The ESCC Component Number.

- (d) Traceability information.

#### 2.3 <u>ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES</u> Electrical measurements shall be performed at room, high and low temperatures.

#### 2.3.1 <u>Room Temperature Electrical Measurements</u>

The measurements shall be performed at  $T_{amb} = +22 \pm 3^{\circ}C$ .

| Characteristics                        | Symbols          | MIL-STD-883 | Test Conditions<br>Note 1                                                                                                            |     |     | nits | Units |

|----------------------------------------|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

|                                        |                  | Test Method |                                                                                                                                      | Min | Max |      |       |

| Functional Test                        | -                | 3014        | Verify Truth Table<br>$f_{IN} = 695MHz$<br>$f_{CLK} = 1.4Gsps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$V_{DD} = 1.45V$<br>$DV_{SS} = -5V$ | -   | -   | -    |       |

| Low Level Input<br>Current, B/GB Input | I <sub>IL1</sub> | 3009        | $V_{IN} (B/GB) = -5V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$                | 500 | 800 | μA   |       |

| Characteristics                                  | Symbols          | MIL-STD-883 | Test Conditions                                                                                                         | Lin | nits | Units |

|--------------------------------------------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|-------|

|                                                  |                  | Test Method | Note 1                                                                                                                  | Min | Max  |       |

| Low Level Input<br>Current,<br>DECB/DIODE Input  | I <sub>IL2</sub> | 3009        | $V_{IN} (DIODE) = -5V$ $V_{IN} (CLK) = Open$ $V_{DD} = 5V, V_{SS} = -5V$ $DV_{DD} = 1.45V$ $DV_{SS} = -5V$              | 1   | 2.5  | mA    |

| Low Level Input<br>Current, PGEB<br>Input        | I <sub>IL3</sub> | 3009        | $V_{IN} (PGEB) = -5V$ $V_{IN} (CLK) = Open$ $V_{DD} = 5V, V_{SS} = -5V$ $DV_{DD} = 1.45V$ $DV_{SS} = -5V$               | 500 | 800  | μA    |

| Low Level Input<br>Current, DRRB<br>Input        | I <sub>IL4</sub> | 3009        | $V_{IN} (DRRB) = -1.8V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$ | 100 | 600  | μA    |

| Low Level Input<br>Current, SDAEN<br>Input       | I <sub>IL5</sub> | 3009        | $V_{IN} (SDAEN) = -5V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$  | 500 | 800  | μA    |

| Low Level Input<br>Current, GA Input             | I <sub>IL6</sub> | 3009        | $V_{IN} (GA) = -0.5V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$   | 0   | 4    | μA    |

| Low Level Input<br>Current, SDA Input            | I <sub>IL7</sub> | 3009        | $V_{IN} (SDA) = -0.5V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$  | 0   | 4    | μA    |

| High Level Input<br>Current, B/GB Input          | I <sub>IH1</sub> | 3010        | $V_{IN} (B/GB) = 0V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$    | 100 | 500  | μA    |

| High Level Input<br>Current,<br>DECB/DIODE Input | I <sub>IH2</sub> | 3010        | $V_{IN} (DIODE) = 0V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$   | -2  | 500  | μA    |

| High Level Input<br>Current, PGEB<br>Input       | I <sub>IH3</sub> | 3010        | $V_{IN} (PGEB) = 0V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$    | 100 | 500  | μA    |

| Characteristics                                                           | Symbols          | MIL-STD-883 | Test Conditions                                                                                                                                                                               | Lin  | nits | Units |

|---------------------------------------------------------------------------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|

|                                                                           |                  | Test Method | Note 1                                                                                                                                                                                        | Min  | Max  |       |

| High Level Input<br>Current, DRRB<br>Input                                | I <sub>IH4</sub> | 3010        | $V_{IN} (DRRB) = 0V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$                                                                          | -50  | 200  | μA    |

| High Level Input<br>Current, SDAEN<br>Input                               | I <sub>IH5</sub> | 3010        | $V_{IN} (SDAEN) = 0V$ $V_{IN} (CLK) = Open$ $V_{DD} = 5V, V_{SS} = -5V$ $DV_{DD} = 1.45V$ $DV_{SS} = -5V$                                                                                     | 100  | 500  | μA    |

| High Level Input<br>Current, GA Input                                     | I <sub>IH6</sub> | 3010        | $V_{IN} (GA) = 0.5V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$                                                                          | 0    | 4    | μA    |

| High Level Input<br>Current, SDA Input                                    | I <sub>IH7</sub> | 3010        | $V_{IN} (SDA) = 0.5V$<br>$V_{IN} (CLK) = Open$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$                                                                         | 0    | 10   | μΑ    |

| V <sub>IN</sub> Input Resistance                                          | R <sub>IN</sub>  | -           | $V_{IN} (A) = 250 \text{mV}$<br>$V_{IN} (B) = 0 \text{V via } 50 \Omega$<br>Resistor<br>$V_{DD} = 5 \text{V}, V_{SS} = -5 \text{V}$<br>$D V_{DD} = 1.45 \text{V}$<br>$D V_{SS} = -5 \text{V}$ | 45   | 55   | Ω     |

| ECL Mode Low<br>Level Output<br>Voltage, D0 to D9<br>and OR Outputs       | V <sub>OL1</sub> | 3007        | $V_{IN} (A) = -0.3V (DC)$<br>$f_{CLK} = 390Msps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = -0.8V$<br>$DV_{SS} = -5V$<br>Note 2                                                             | -    | -1.1 | V     |

| ECL Mode Low<br>Level Output<br>Voltage, D0B to<br>D9B and ORB<br>Outputs | V <sub>OL2</sub> | 3007        | $V_{IN}(A) = -0.3V (DC)$<br>$f_{CLK} = 390Msps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = -0.8V$<br>$DV_{SS} = -5V$<br>Note 2                                                              | -    | -1.1 | V     |

| LVDS Mode Low<br>Level Output<br>Voltage, D0 to D9<br>and OR Outputs      | V <sub>OL3</sub> | 3007        | $V_{IN} (A) = -0.3V (DC)$<br>$f_{CLK} = 390Msps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$<br>Note 2                                                             | 0.75 | 1.18 | V     |

| Characteristics                                                             | Symbols          | MIL-STD-883 | Test Conditions                                                                                                                   | Lin   | nits  | Units |

|-----------------------------------------------------------------------------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|

|                                                                             |                  | Test Method | Note 1                                                                                                                            | Min   | Max   |       |

| LVDS Mode Low<br>Level Output<br>Voltage, D0B to<br>D9B and ORB<br>Outputs  | V <sub>OL4</sub> | 3007        | $V_{IN} (A) = -0.3V (DC)$<br>$f_{CLK} = 390Msps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$<br>Note 2 | 0.75  | 1.18  | V     |

| ECL Mode High<br>Level Output<br>Voltage D0 to D9<br>and OR Outputs         | V <sub>OH1</sub> | 3006        | $V_{IN} (A) = -0.3V (DC)$<br>$f_{CLK} = 390Msps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = -0.8V$<br>$DV_{SS} = -5V$<br>Note 2 | -0.99 | -     | V     |

| ECL Mode High<br>Level Output<br>Voltage, D0B to<br>D9B and ORB<br>Outputs  | V <sub>OH2</sub> | 3006        | $V_{IN}(A) = -0.3V (DC)$<br>$f_{CLK} = 390Msps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = -0.8V$<br>$DV_{SS} = -5V$<br>Note 2  | -0.99 | -     | V     |

| LVDS Mode High<br>Level Output<br>Voltage, D0 to D9<br>and OR Outputs       | V <sub>OH3</sub> | 3006        | $V_{IN} (A) = -0.3V (DC)$<br>$f_{CLK} = 390Msps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$<br>Note 2 | 1.18  | 1.425 | V     |

| LVDS Mode High<br>Level Output<br>Voltage, D0B to<br>D9B and ORB<br>Outputs | V <sub>OH4</sub> | 3006        | $V_{IN}(A) = -0.3V (DC)$<br>$f_{CLK} = 390Msps$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$<br>Note 2  | 1.18  | 1.425 | V     |

| ECL Mode<br>Differential Output<br>Voltage Swing<br>(Signed Value)          | V <sub>OD1</sub> | -           | Note 3                                                                                                                            | 200   | 300   | mV    |

| LVDS Mode<br>Differential Output<br>Voltage Swing<br>(Signed Value)         | V <sub>OD2</sub> | -           | Note 3                                                                                                                            | 200   | 450   | mV    |

| ECL Mode Common<br>Mode Output<br>Voltage                                   | V <sub>CM1</sub> | -           | Note 3                                                                                                                            | -1.15 | -0.95 | V     |

| LVDS Mode<br>Common Mode<br>Output Voltage                                  | V <sub>CM2</sub> | -           | Note 3                                                                                                                            | 0.95  | 1.275 | V     |

| Characteristics                                    | Symbols            | MIL-STD-883 | Test Conditions                                                                                                                        | Lin | nits | Units |

|----------------------------------------------------|--------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|

|                                                    |                    | Test Method | Note 1                                                                                                                                 | Min | Max  |       |

| ECL Mode<br>Analogue Positive<br>Supply Current 1  | I <sub>DD1</sub>   | 3005        | $f_{IN} = 20MHz$<br>$f_{CLK} = 43.75MHz$<br>$V_{DD} = 5.25V$<br>$V_{SS} = -5.25V$<br>$DV_{DD} = -0.8V$<br>$DV_{SS} = -5.25V$<br>Note 2 | 40  | 150  | mA    |

| ECL Mode<br>Analogue Negative<br>Supply Current 1  | I <sub>SS1</sub>   | 3005        | $f_{IN} = 20MHz$<br>$f_{CLK} = 43.75MHz$<br>$V_{DD} = 5.25V$<br>$V_{SS} = -5.25V$<br>$DV_{DD} = -0.8V$<br>$DV_{SS} = -5.25V$<br>Note 2 | 450 | 750  | mA    |

| ECL Mode Digital<br>Positive Supply<br>Current 1   | I <sub>DVDD1</sub> | 3005        | $f_{IN} = 20MHz$<br>$f_{CLK} = 43.75MHz$<br>$V_{DD} = 5.25V$<br>$V_{SS} = -5.25V$<br>$DV_{DD} = -0.8V$<br>$DV_{SS} = -5.25V$<br>Note 2 | 50  | 200  | mA    |

| ECL Mode Digital<br>Negative Supply<br>Current 1   | I <sub>DVSS1</sub> | 3005        | $f_{IN} = 20MHz$<br>$f_{CLK} = 43.75MHz$<br>$V_{DD} = 5.25V$<br>$V_{SS} = -5.25V$<br>$DV_{DD} = -0.8V$<br>$DV_{SS} = -5.25V$<br>Note 2 | 50  | 200  | mA    |

| LVDS Mode<br>Analogue Positive<br>Supply Current 2 | I <sub>DD2</sub>   | 3005        | $f_{IN} = 20MHz$<br>$f_{CLK} = 43.75MHz$<br>$V_{DD} = 5.25V$<br>$V_{SS} = -5.25V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5.25V$<br>Note 2 | 40  | 150  | mA    |

| LVDS Mode<br>Analogue Negative<br>Supply Current 2 | I <sub>SS2</sub>   | 3005        | $f_{IN} = 20MHz$<br>$f_{CLK} = 43.75MHz$<br>$V_{DD} = 5.25V$<br>$V_{SS} = -5.25V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5.25V$<br>Note 2 | 450 | 750  | mA    |

| LVDS Mode Digital<br>Positive Supply<br>Current 2  | I <sub>DVDD2</sub> | 3005        | $f_{IN} = 20MHz$<br>$f_{CLK} = 43.75MHz$<br>$V_{DD} = 5.25V$<br>$V_{SS} = -5.25V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5.25V$<br>Note 2 | 50  | 300  | mA    |

No. 9407/004

| Characteristics                                   | Symbols            | MIL-STD-883 | Test Conditions                                                                                                                        | Lin   | nits  | Units |

|---------------------------------------------------|--------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|

|                                                   |                    | Test Method | Note 1                                                                                                                                 | Min   | Max   |       |

| LVDS Mode Digital<br>Negative Supply<br>Current 2 | I <sub>DVSS2</sub> | 3005        | $f_{IN} = 20MHz$<br>$f_{CLK} = 43.75MHz$<br>$V_{DD} = 5.25V$<br>$V_{SS} = -5.25V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5.25V$<br>Note 2 | 50    | 300   | mA    |

| ECL Mode Power<br>Consumption                     | P <sub>ECL</sub>   | -           | Note 4                                                                                                                                 | 3     | 4.9   | W     |

| LVDS Mode Power<br>Consumption                    | P <sub>LVDS</sub>  | -           | Note 4                                                                                                                                 | 3     | 6     | W     |

| Data Ready<br>Frequency with<br>Decimation by 32  | f <sub>DRD</sub>   | -           | $f_{CLK} = 1.4GHz$<br>$V_{IN} (DIODE) = -4V$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$                    | 21.87 | 21.88 | MHz   |

| Decimation Factor<br>32                           | DF <sub>32</sub>   | -           |                                                                                                                                        | 31.96 | 32.04 | -     |

| Data Ready<br>Frequency Without<br>Decimation     | f <sub>DR</sub>    | -           | $f_{CLK} = 43.75MHz$<br>$V_{IN} (DIODE) = 0V$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$                   | 21.87 | 21.88 | MHz   |

| Decimation Factor 1                               | DF <sub>1</sub>    | -           | $f_{CLK} = 43.75MHz$<br>$V_{IN} (DIODE) = 0V$<br>$V_{DD} = 5V, V_{SS} = -5V$<br>$DV_{DD} = 1.45V$<br>$DV_{SS} = -5V$                   | 0.96  | 1.04  | -     |

| Functional Test-<br>Pattern Generator             | -                  | 3014        |                                                                                                                                        | -     | -     | -     |

| Gain at Nominal<br>Amplification                  | G <sub>typ</sub>   | -           |                                                                                                                                        | 0.9   | 1.1   | -     |

| Characteristics                                          | Symbols           | MIL-STD-883 | Test Conditions | Lin    | Units |     |

|----------------------------------------------------------|-------------------|-------------|-----------------|--------|-------|-----|

|                                                          |                   | Test Method | Note 1          | Min    | Max   |     |

| Minimum Gain                                             | G <sub>MIN</sub>  | -           |                 | -      | 0.995 | -   |

| Maximum Gain                                             | G <sub>MAX</sub>  | -           |                 | 1.0015 | -     | -   |

| ECL Mode Effective<br>Number of Bits,<br>Gray Output 1   | ENOB <sub>1</sub> | -           |                 | 7.3    | -     | Bit |

| LVDS Mode<br>Effective Number of<br>Bits, Gray Output 2  | ENOB <sub>2</sub> | -           |                 | 7      | -     | Bit |

| ECL Mode Signal to<br>Noise Ratio, Gray<br>Output        | SNR               | -           |                 | 49     | -     | dBc |

| ECL Mode Total<br>Harmonic Distortion,<br>Gray Output 1  | THD₁              | -           |                 | 46     | -     | dBc |

| LVDS Mode Total<br>Harmonic Distortion,<br>Gray Output 2 | THD₂              | -           |                 | 46     | -     | dBc |

| Characteristics                                               | Symbols            | MIL-STD-883 | Test Conditions                                                                                                    | Lin | nits | Units |

|---------------------------------------------------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------|-----|------|-------|

|                                                               |                    | Test Method | Note 1                                                                                                             | Min | Max  |       |

| ECL Mode Spurious<br>Free Dynamic<br>Range, Gray Output<br>1  | SFDR <sub>1</sub>  | -           |                                                                                                                    | 48  | -    | dBc   |

| LVDS Mode<br>Spurious Free<br>Dynamic Range,<br>Gray Output 2 | SFDR <sub>2</sub>  | -           | $f_{CLK} = 1.4Gsps f_{IN} = 695MHz P_{IN} = -1dBFS V_{DD} = 5V, V_{SS} = -5V DV_{DD} = 1.45V DV_{SS} = -5V Note 2$ | 50  | -    | dBc   |

| Minimum<br>Differential Non-<br>Linearity                     | DNL <sub>MIN</sub> | -           |                                                                                                                    | -1  | -    | LSB   |

| Maximum<br>Differential Non-<br>Linearity                     | DNL <sub>MAX</sub> | -           |                                                                                                                    | -   | 1.5  | LSB   |

| RMS Differential<br>Non-Linearity                             | DNL <sub>rms</sub> | -           | $f_{CLK} = 390Msps f_{IN} = 100MHz V_{DD} = 5V, V_{SS} = -5V DV_{DD} = 1.45V DV_{SS} = -5V Note 2$                 | -   | 0.3  | LSB   |

| Minimum Integral<br>Non-Linearity                             | INL <sub>MIN</sub> | -           | $f_{CLK} = 390Msps f_{IN} = 100MHz V_{DD} = 5V, V_{SS} = -5V DV_{DD} = 1.45V DV_{SS} = -5V Note 2$                 | -4  | -    | LSB   |

| Maximum Integral<br>Non-Linearity                             | INL <sub>MAX</sub> | -           | $f_{CLK} = 390Msps f_{IN} = 100MHz V_{DD} = 5V, V_{SS} = -5V DV_{DD} = 1.45V DV_{SS} = -5V Note 2$                 | -   | 4    | LSB   |

No. 9407/004

**ISSUE 2**

| Characteristics      | Symbols         |                    |                                                                                                                                                                       | Lin | nits | Units |

|----------------------|-----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|

|                      |                 | Test Method Note 1 | Note 1                                                                                                                                                                | Min | Max  |       |

| Input Offset Voltage | V <sub>IO</sub> |                    | $      f_{CLK} = 1.4Gsps             f_{IN} = 695MHz             V_{DD} = 5V, V_{SS} = -5V             DV_{DD} = 1.45V             DV_{SS} = -5V             Note 2 $ | -9  | 9    | mV    |

#### NOTES:

- 1. Unless otherwise specified all inputs and outputs shall be tested for each characteristic, inputs not under test shall be  $V_{IN} = V_{SS}$  or  $V_{DD}$  and outputs not under test shall be open.

- 2. All outputs are  $50\Omega$  Transmission Lines differentially terminated into  $100\Omega$  (2 ×  $50\Omega$ ) via 47pF capacitors to 0V.

- 3. Calculated from the  $V_{OH}$  and  $V_{OL}$  measurements.

- 4. Calculated from the Supply Current measurements.

- 5. This limit is defined by correlation and not tested, due to test equipment limitation.

2.3.2 <u>High and Low Temperatures Electrical Measurements</u> The measurements shall be performed at  $T_{amb} = +125 (+0.5)^{\circ}C$  and  $T_{amb} = -55 (+5.0)^{\circ}C$ .

The characteristics, test methods, conditions and limits shall be the same as specified for Room Temperature Electrical Measurements, except that the Low Level Input Current DECB/DIODE Input ( $I_{IL2}$ ) shall only be tested at Room Temperature.

#### 2.4 PARAMETER DRIFT VALUES

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$  = +22 ±3°C.

The test methods and test conditions shall be as per the corresponding test defined in Room Temperature Electrical Measurements.

The drift values ( $\Delta$ ) shall not be exceeded for each characteristic specified. The corresponding absolute limit values for each characteristic shall not be exceeded.

| Characteristics                                              | Symbols          |            | Units    |      |    |

|--------------------------------------------------------------|------------------|------------|----------|------|----|

| Note 1                                                       |                  | Drift      | Absolute |      |    |

|                                                              |                  | Value<br>Δ | Min      | Max  |    |

| ECL Mode Low Level Output<br>Voltage, D0 Output              | V <sub>OL1</sub> | +0.02, -0  | -        | -1.1 | V  |

| ECL Mode Low Level Output<br>Voltage, D0B Output             | V <sub>OL2</sub> | +0.02, -0  | -        | -1.1 | V  |

| ECL Mode High Level Output<br>Voltage, D0 Output             | V <sub>OH1</sub> | -0.02, +0  | -0.99    | -    | V  |

| ECL Mode High Level Output<br>Voltage, D0B Output            | V <sub>OH2</sub> | -0.02, +0  | -0.99    | -    | V  |

| ECL Mode Differential Output<br>Voltage Swing (Signed Value) | V <sub>OD1</sub> | ±20        | 200      | 300  | mV |

**ISSUE 2**

| Characteristics                                               | Symbols            |            | Limits |       | Units |

|---------------------------------------------------------------|--------------------|------------|--------|-------|-------|

| Note 1                                                        |                    | Drift      | Abs    | olute |       |

|                                                               |                    | Value<br>Δ | Min    | Max   |       |

| ECL Mode Common Mode<br>Output Voltage, D0 and D0B<br>Outputs | V <sub>CM1</sub>   | ±0.02      | -1.15  | -0.95 | V     |

| ECL Mode Analogue Positive<br>Supply Current 1                | I <sub>DD1</sub>   | ±5%        | 40     | 150   | mA    |

| ECL Mode Analogue Negative<br>Supply Current 1                | I <sub>SS1</sub>   | ±5%        | 450    | 750   | mA    |

| ECL Mode Digital Positive Supply<br>Current 1                 | I <sub>DVDD1</sub> | ±5%        | 50     | 200   | mA    |

| ECL Mode Digital Negative<br>Supply Current 1                 | I <sub>DVSS1</sub> | ±5%        | 50     | 200   | mA    |

| ECL Mode Power Consumption                                    | P <sub>ECL</sub>   | ±5%        | 3      | 4.9   | W     |

| Gain at Nominal Amplification                                 | $G_{TYP}$          | ±5%        | 0.9    | 1.1   | -     |

| ECL Mode Effective Number of<br>Bits, Gray Output             | ENOB <sub>1</sub>  | +0.4, +0   | 7.3    | -     | Bit   |

| LVDS Mode Effective Number of<br>Bits, Gray Output            | ENOB <sub>2</sub>  | +0.4, +0   | 7      | -     | Bit   |

| ECL Mode Signal to Noise Ratio                                | SNR                | -4, +0     | 49     | -     | dBc   |

| ECL Mode Total Harmonic<br>Distortion, Gray Output            | THD₁               | -4, +0     | 46     | -     | dBc   |

| LVDS Mode Total harmonic<br>Distortion, Gray Output           | THD <sub>2</sub>   | -4, +0     | 46     | -     | dBc   |

| ECL Mode Spurious Free<br>Dynamic Range, Gray Output          | SFDR <sub>1</sub>  | -4, +0     | 48     | -     | dBc   |

| LVDS Mode Spurious Free<br>Dynamic Range, Gray Output         | SFDR <sub>1</sub>  | -4, +0     | 50     | -     | dBc   |

| Minimum Differential Non-<br>Linearity                        |                    | -0.5, +0   | -1     | -     | LSB   |

| Maximum Differential Non-<br>Linearity                        | DNL <sub>MAX</sub> | +0.5, +0   | -      | 1.5   | LSB   |

| RMS Differential Non-Linearity                                | DNL <sub>rms</sub> | +0.5, +0   | -      | 0.3   | LSB   |

| Minimum Integral Non-Linearity                                | INL <sub>MIN</sub> | -0.5, +0   | -4     | -     | LSB   |

| Maximum Integral Non-Linearity                                | INL <sub>MAX</sub> | +0.5, +0   | -      | 4     | LSB   |

| Input Offset Voltage                                          | V <sub>IO</sub>    | ±5         | -9     | 9     | mV    |

**NOTES:** 1. Unless otherwise specified all inputs and outputs shall be tested for each characteristic.

**ISSUE 2**

# 2.5 INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$  = +22 ±3°C.

The characteristics, test methods, conditions and limits shall be as specified for Room Temperature Electrical Measurements.

#### 2.6 POWER BURN-IN CONDITIONS

| Characteristics                     | Symbols            | Test Conditions | Units |

|-------------------------------------|--------------------|-----------------|-------|

| Junction Temperature                | TJ                 | +125 (-5 +10)   | °C    |

| Clock Frequency                     | $f_{CLK,}f_{CLKB}$ | 625             | kHz   |

| Input Voltage, A Input              | V <sub>A</sub>     | ±250            | mV    |

| Input Frequency, A Input            | f <sub>IN</sub>    | 312             | kHz   |

| Input Voltage, B Input              | V <sub>B</sub>     | 0               | V     |

| Analogue Positive Supply Voltage    | $V_{DD}$           | 5.3             | V     |

| Analogue Negative Supply<br>Voltage | $V_{SS}$           | -5.3            | V     |

| Digital Positive Supply Voltage     | $DV_{DD}$          | 1.5             | V     |

| Digital Negative Supply Voltage     | $DV_{SS}$          | -5.3            | V     |

#### NOTES:

- 1. The SDA, DRRB, SDAEN and GA inputs shall be connected to ground via  $50\Omega$  resistors.

- 2. All outputs shall be connected to ground via  $50\Omega$  Loads.

- 3. Decoupling capacitors of 100pF in parallel with 10nF shall be connected to all supplies at each burn-in position.

- 4. Decoupling capacitors of 1µF in parallel with 10nF shall be connected to all supplies on each burn-in board.

- 5. The PGEB input shall be connected to ground.

- 6. The B/GB and DECB/DIODE inputs shall be open circuit.

- 7. The CLK, CLKB and B inputs shall have  $50\Omega$  input protection resistors.

- 8. The A input shall have a series 100nF capacitor and a  $50\Omega$  input resistor.

#### 2.7 OPERATING LIFE CONDITIONS

The conditions shall be as specified for Power Burn-in, performed without the Solder Column Interposer (SCI).

#### 2.8 TOTAL DOSE RADIATION TESTING

2.8.1 <u>Bias Conditions and Total Dose Level for Total Dose Radiation Testing</u> Continuous bias shall be applied during radiation testing as specified below.

The total dose level applied shall be as specified in the component type variant information herein or in the Purchase Order.

| Characteristics                     | Symbols          | Test Conditions | Units |

|-------------------------------------|------------------|-----------------|-------|

| Ambient Temperature                 | $T_{amb}$        | +22 ±3          | °C    |

| Clock Frequency                     | f <sub>CLK</sub> | 625             | kHz   |

| Input Voltage, A Input              | V <sub>A</sub>   | ±250            | mV    |

| Input Frequency, B Input            | f <sub>IN</sub>  | 312             | kHz   |

| Analogue Positive Supply Voltage    | V <sub>DD</sub>  | 5.25            | V     |

| Analogue Negative Supply<br>Voltage | $V_{SS}$         | -5.25           | V     |

| Digital Positive Supply Voltage     | $DV_{DD}$        | 2.4             | V     |

| Digital Negative Supply Voltage     | $DV_{SS}$        | -5.25           | V     |

#### NOTES:

1. The same bias configuration as the Power Burn-in shall apply.

#### 2.8.2 <u>Electrical Measurements for Total Dose Radiation Testing</u>

Prior to radiation testing the devices shall successfully meet Room Temperature Electrical Measurements specified herein.

Unless otherwise stated the measurements shall be performed at  $T_{amb} = 22 \pm 3^{\circ}C$ .

The test methods and test conditions shall be as per the corresponding test defined in electrical measurements at Room Temperature.

The parameters to be measured during and on completion of radiation testing are shown below. Unless otherwise specified all inputs and outputs shall be tested for each characteristic.

| Characteristics                                           | Symbol           | Limits |      | Units |

|-----------------------------------------------------------|------------------|--------|------|-------|

|                                                           |                  | Min.   | Max. |       |

| Input Resistance, A Input                                 | R <sub>INA</sub> | 45     | 55   | Ω     |

| ECL Mode Low Level Output<br>Voltage, D7 to D9 Outputs    | V <sub>OL1</sub> | -      | -1.1 | V     |

| ECL Mode Low Level Output<br>Voltage, D7B to D9B Outputs  | V <sub>OL2</sub> | -      | -1.1 | V     |

| LVDS Mode Low Level Output<br>Voltage, D7 to D9 Outputs   | V <sub>OL3</sub> | 0.75   | 1.18 | V     |

| LVDS Mode Low Level Output<br>Voltage, D7B to D9B Outputs | V <sub>OL4</sub> | 0.75   | 1.18 | V     |

| Characteristics                                           | Symbol             | Limits |       | Units |

|-----------------------------------------------------------|--------------------|--------|-------|-------|

|                                                           |                    | Min.   | Max.  |       |

| ECL Mode High Level Output<br>Voltage, D7 to D9 Outputs   | V <sub>OH1</sub>   | -0.99  | -     | V     |

| ECL Mode High Level Output<br>Voltage, D7B to D9B Outputs | V <sub>OH2</sub>   | -0.99  | -     | V     |

| LVDS Mode High Level Output<br>Voltage, D7 to D9 Outputs  | V <sub>OH3</sub>   | 1.18   | 1.425 | V     |

| LVDS Mode High Level Output Voltage, D7B to D9B Outputs   | V <sub>OH4</sub>   | 1.18   | 1.425 | V     |

| ECL Mode Analogue Positive<br>Supply Current 1            | I <sub>DD1</sub>   | 40     | 150   | mA    |

| ECL Mode Analogue Negative<br>Supply Current 1            | I <sub>SS1</sub>   | 450    | 750   | mA    |

| ECL Mode Digital Positive Supply<br>Current 1             | I <sub>DVDD1</sub> | 50     | 200   | mA    |

| ECL Mode Digital Negative<br>Supply Current 1             | I <sub>DVSS1</sub> | 50     | 200   | mA    |

| LVDS Mode Analogue Positive<br>Supply Current 2           | I <sub>DD2</sub>   | 40     | 150   | mA    |

| LVDS Mode Analogue Negative<br>Supply Current 2           | I <sub>SS2</sub>   | 450    | 750   | mA    |

| LVDS Mode Digital Positive<br>Supply Current 2            | I <sub>DVDD2</sub> | 50     | 300   | mA    |

| LVDS Mode Digital Negative<br>Supply Current 2            | I <sub>DVSS2</sub> | 50     | 300   | mA    |

| ECL Mode Power Consumption                                | $P_{ECL}$          | 3      | 4.9   | W     |

| LVDS Mode Power Consumption                               | $P_{LDVS}$         | 3      | 6     | W     |

| ECL Mode Effective Number of<br>Bits, Gray Output 1       | ENOB <sub>1</sub>  | 7.3    | -     | Bit   |

| LVDS Mode Effective Number of<br>Bits, Gray Output 2      | ENOB <sub>2</sub>  | 7      | -     | Bit   |

| ECL Mode Signal to Noise Ratio,<br>Gray Output            | SNR                | 49     | -     | dBc   |

| ECL Mode Total Harmonic<br>Distortion, Gray Output 1      | THD₁               | 46     | -     | dBc   |

| LVDS Mode Total Harmonic<br>Distortion, Gray Output 2     | THD <sub>2</sub>   | 46     | -     | dBc   |

| ECL Mode Spurious Free<br>Dynamic Range, Gray Output 1    | SFDR <sub>1</sub>  | 48     | -     | dBc   |

| LVDS Mode Spurious Free<br>Dynamic Range, Gray Output 2   | SFDR <sub>2</sub>  | 50     | -     | dBc   |

| Minimum Differential Non-<br>Linearity                    | DNL <sub>MIN</sub> | -1     | -     | LSB   |

ESCC Detail Specification

ISSUE 2

PAGE 28

| Characteristics                        | Symbol             | Limits |      | Units |

|----------------------------------------|--------------------|--------|------|-------|

|                                        |                    | Min.   | Max. |       |

| Maximum Differential Non-<br>Linearity | DNL <sub>MAX</sub> | -      | 1.5  | LSB   |

| RMS Differential Non-Linearity         | DNL <sub>rms</sub> | -      | 0.3  | LSB   |

| Minimum Integral Non-Linearity         | INL <sub>MIN</sub> | -4     | -    | LSB   |

| Maximum Integral Non-Linearity         | INL <sub>MAX</sub> | -      | 4    | LSB   |