Page i

# ELECTROSTATIC DISCHARGE SENSITIVITY TEST METHOD

**ESCC Basic Specification No. 23800**

## ISSUE 1 October 2002

#### **ESCC Basic Specification**

PAGE ii

ISSUE 1

#### **LEGAL DISCLAIMER AND COPYRIGHT**

European Space Agency, Copyright © 2002. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or allleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Ageny and provided that it is not used for a commercial purpose, may be:

- copied in whole in any medium without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

## european space agency agence spatiale européenne

Pages 1 to 20

# ELECTROSTATIC DISCHARGE SENSITIVITY TEST METHOD

ESA/SCC Basic Specification No. 23800

## space components coordination group

|            |             | Approved by   |                                    |

|------------|-------------|---------------|------------------------------------|

| issue/Rev. | Date        | SCCG Chairman | ESA Director General or his Deputy |

| Issue 1    | August 1987 | -             | -                                  |

| Revision A | July 1989   | _             | ~                                  |

| Revision B | June 1991   | Tommens       | u cez                              |

|            |             | ·             |                                    |

Rev. 'B'

PAGE 2

ISSUE 1

#### **DOCUMENTATION CHANGE NOTICE**

|                |              | DOCUMENTATION CHANGE NOTICE                                                                                                                                                                                                                                                                                 |                                                                              |

|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Rev.<br>Letter | Rev.<br>Date | CHANGE<br>Reference Item                                                                                                                                                                                                                                                                                    | Approved DCR No.                                                             |

| 'A'            | Jul. '89     | P1. Cover page P2. DCN P3. Table of Contents: New Para. 5.1 added : Old Para. 5.1 renumbered "5.1.1" P13. Para. 5.1: New Para. 5.1 added Para. 5.1.1: Old Para. 5.1 renumbered "5.1.1" P15. Para. 5.2.3: Second sentence amended P17. Para. 5.2.5: New Para. 5.2.5 added Para. 5.2.6: New Para. 5.2.6 added | None<br>None<br>22635<br>22635<br>22635<br>22635<br>22635/<br>22713<br>22635 |

| 'B'            | Jun. '91     | P1. Cover page P2. DCN P14. Figure 1 : In HVPS definition, "15 000" replaced by "20 000"                                                                                                                                                                                                                    | None<br>None<br>23444                                                        |

|                |              | This document has been transferred from hardcopy to electronic format. The content is unchanged but minor differences in presentation exist.                                                                                                                                                                |                                                                              |

Rev. 'A'

PAGE 3

ISSUE 1

#### **TABLE OF CONTENTS**

|                |                                                      | <u>Page</u> |

|----------------|------------------------------------------------------|-------------|

| 1.             | SCOPE                                                | 4           |

| 1.1            | General                                              | 4           |

| 1.2            | Purpose                                              | 4           |

| 1.3            | Applicability                                        | 4           |

| 2.             | APPLICABLE DOCUMENTS                                 | 4           |

| 2.1            | ESA/SCC Specifications                               | 4           |

| 2.2            | Other (Reference) Documents                          | 5           |

| 3.             | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS | 5           |

| 4.             | CAUSES AND EFFECTS OF STATIC ELECTRICITY             | 5           |

| 4.1            | Nature of Static Electricity                         | 5           |

| 4.2            | Typical Charge Sources                               | 6           |

| 4.3            | Typical Electrostatic Voltage                        | 8           |

| 4.4            | Electrostatic Discharge Sensitive Components         | 8           |

| 4.5            | Failure Mechanisms                                   | 12          |

| 5.             | ELECTROSTATIC DISCHARGE TEST                         | 13          |

| 5.1            | General                                              | 13          |

| 5.1.1          | Human ESD Model                                      | 13          |

| 5.2            | ESD Classification Procedure                         | 15          |

| 5.2.1          | Component Functional Test                            | 15          |

| 5.2.2          | Component Failure Definition                         | 15          |

| 5.2.3          | Determination of Critical Failure Path               | 15          |

| 5.2.4          | ESD Classification Testing                           | 16<br>17    |

| 5.2.5<br>5.2.6 | Critical Path Failure Voltage Test<br>ESD Warning    | 17          |

| TABLE          | ES .                                                 |             |

| Ī              | Typical Prime Charge Sources                         | 7           |

| II             | Typical Electrostatic Voltages                       | 9           |

| III            | List of ESDS Components                              | 10          |

| IV             | Failure Mechanisms                                   | 12          |

| V              | Pin Combinations for ESD Testing                     | 18          |

| CHAR           |                                                      |             |

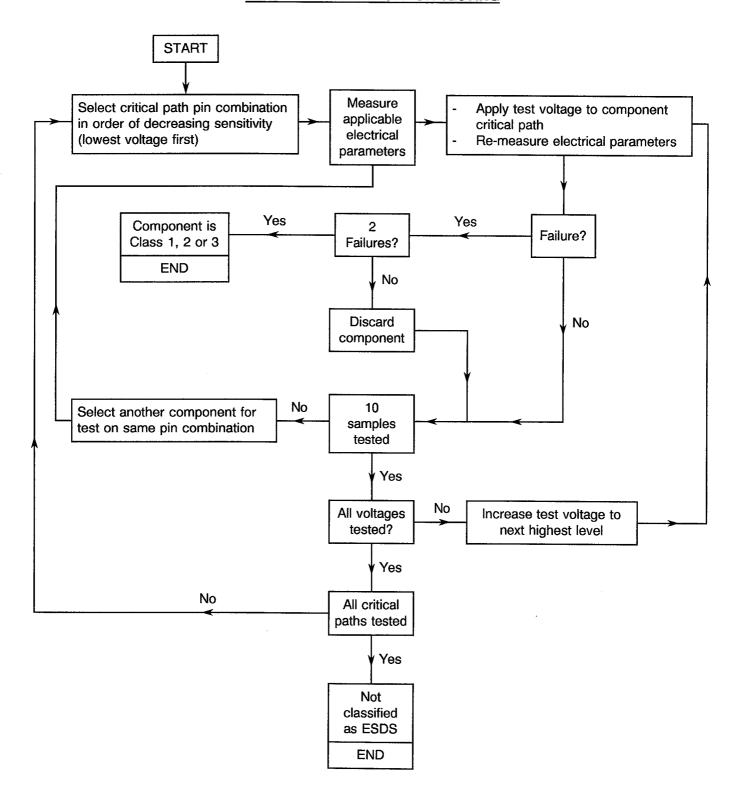

| I              | Critical Path Determination                          | 19          |

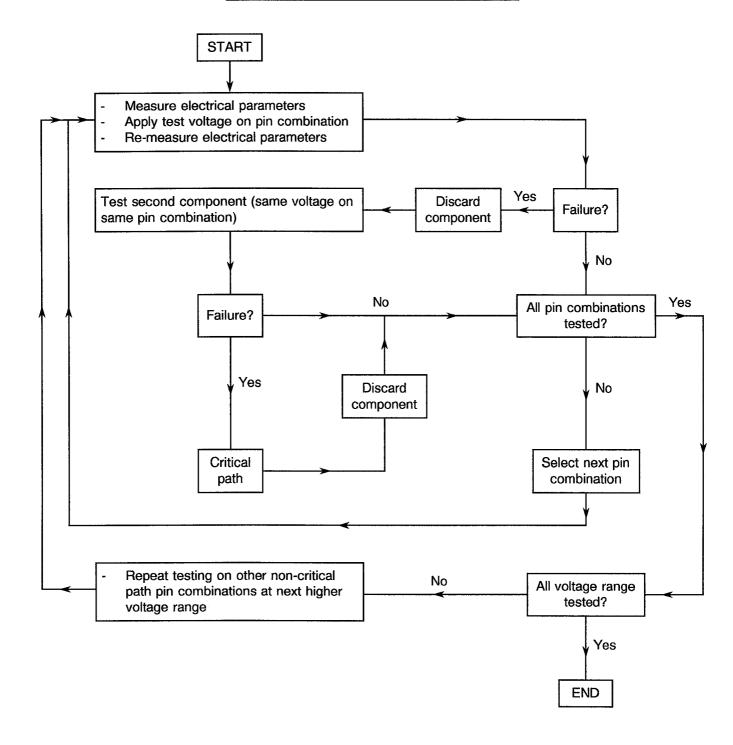

| II             | Classification Testing                               | 20          |

| FIGUE          |                                                      |             |

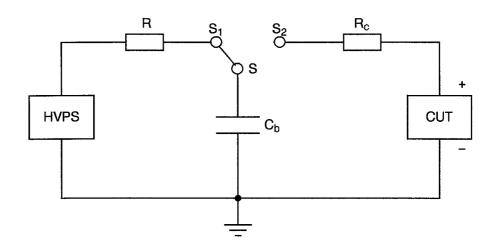

| T              | Human Body Model Test Circuit                        | 14          |

PAGE

ISSUE 1

#### 1. SCOPE

#### 1.1 GENERAL

This specification defines the basic requirements applicable to electrostatic susceptibility tests of electrostatic discharge sensitive (ESDS) components suitable for space application.

The electrostatic discharge sensitivity test method is considered to be destructive. Detailed requirements applicable to individual component types shall be specified in the relevant test plan and/or applicable ESA/SCC Detail Specification.

#### 1.2 PURPOSE

The purpose of this specification is to define the requirements for testing ESDS devices, including discrete semiconductors and integrated circuits, for definition of the electrostatic discharge susceptibility voltage range.

#### 1.3 APPLICABILITY

The ESDS items subject to this specification are listed in Tables III-A, III-B and III-C.

#### 2. APPLICABLE DOCUMENTS

#### 2.1 ESA/SCC SPECIFICATIONS

The following documents form part of, and shall be read in conjunction with, this specification. The relevant issues shall be those in effect on the date of placing the purchase order or contract.

- (a) ESA/SCC Basic Specification No. 20600, Preservation, Packaging and Despatch of SCC Electronic Components.

- (b) ESA/SCC Basic Specification No. 21300, Terms, Definitions, Abbreviations, Symbols and Units.

PAGE

ISSUE -

#### 2.2 OTHER (REFERENCE) DOCUMENTS

DOD-HDBK-263, Military Handbook,

Electrostatic Discharge Control Handbook for Protection of Electrical and Electronic Parts,

Assemblies and Equipment (Excluding Electrically Initiated Explosive Devices).

DOD-STD-1686, Appendix B, Electrostatic Discharge Control Programme for Protection of Electrical and Electronic Parts, Assemblies and Equipment (Excluding Electrically Initiated Explosive Devices) - Classification Testing.

#### 3. TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

The terms, definitions, abbreviations, symbols and units specified in ESA/SCC Basic Specification No. 21300 shall apply. For the purpose of this specification, the following additional definitions shall be applicable:-

#### **ESDS**

Electro Static Discharge Sensitive.

#### **CRITICAL FAILURE PATH**

When the application of a test voltage to a given pin combination results in a failure on 2 consecutive similar components, that pin combination is a critical failure path.

#### 4. CAUSES AND EFFECTS OF STATIC ELECTRICITY

#### 4.1 NATURE OF STATIC ELECTRICITY

Static electricity is electrical charge at rest. The electrical charge is due to the transfer of electrons within a body (polarisation) or from one body to another (conductive charging). The transfer occurs due to interaction of charged bodies or uncharged bodies. The magnitude of the charge is primarily dependent on the size, shape, composition and electrical properties of the substances which make up the bodies.

Some substances readily give up electrons while others tend to accumulate excess electrons. A body having an excess of electrons is charge negatively; a body having an electron deficit is charged positively.

PAGE

ISSUE 1

6

#### 4.2 TYPICAL CHARGE SOURCES

Typical prime charge sources commonly encountered in a manufacturing facility are listed in Table I. These prime sources are essentially insulators and are typically synthetic materials. Electrostatic voltage levels generated with these insulators can be extremely high since they are not readily distributed over the entire surface of the substance or conducted to another contacting substance.

The conductivity of some insulating materials is increased by absorption of moisture under high humidity conditions onto the otherwise insulating surface, creating a slightly conductive humid layer which tends to distribute static charges over the material surface. The generation of 15000 Volts from common plastics in a typical manufacturing facility is usual.

PAGE 7

ISSUE 1

#### **TABLE I - TYPICAL PRIME CHARGE SOURCES**

| Object or Process                            | Material or Activity                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Work Surfaces                                | <ul><li>Waxed, painted or varnished surfaces</li><li>Common vinyl or plastics</li></ul>                                                                                                                                                                                                                                                                             |

| Floors                                       | <ul> <li>Sealed concrete</li> <li>Waxed, finished wood</li> <li>Common vinyl tile or sheeting</li> </ul>                                                                                                                                                                                                                                                            |

| Clothes                                      | - Common clean room smocks - Common synthetic personnel garments - Non-conductive shoes - Virgin cotton (1)                                                                                                                                                                                                                                                         |

| Chairs                                       | - Finished wood<br>- Vinyl<br>- Fibreglass                                                                                                                                                                                                                                                                                                                          |

| Packaging and Handling                       | <ul> <li>Common plastic - bags, wraps, envelopes</li> <li>Common bubble pack, foam</li> <li>Common plastic trays, plastic tote boxes, vials, parts bins</li> </ul>                                                                                                                                                                                                  |

| Assembly, Cleaning, Test and<br>Repair Areas | <ul> <li>Spray cleaners</li> <li>Common plastic solder suckers</li> <li>Solder irons with ungrounded tips</li> <li>Solvent brushes (synthetic bristles)</li> <li>Cleaning or drying by fluid or evaporation</li> <li>Temperature chambers</li> <li>Cryogenic sprays</li> <li>Heat guns and blowers</li> <li>Sand-blasting</li> <li>Electrostatic copiers</li> </ul> |

#### NOTES

1. Virgin cotton can be a static source at low relative humidities such as below 30%.

PAGE 8

ISSUE 1

#### 4.3 TYPICAL ELECTROSTATIC VOLTAGE

Table II shows typical electrostatic voltages generated by personnel in a manufacturing facility.

#### 4.4 ELECTROSTATIC DISCHARGE SENSITIVE COMPONENTS

Numerous components are susceptible to damage when ESD occurs across their terminals or when these components are exposed to electrostatic fields. ESDS components can be destroyed by an ESD when one pin is connected to a high voltage source and other pins are ungrounded.

A hard ground connection is not required to destroy an ESDS component. MOS large-scale integrated components in hermetic packages with non-conductive lids could be damaged for instance by spraying the lid with canned coolant despite there being no ground path connected to the component.

ESDS components installed in assemblies normally have their leads connected to a sufficient mass of conductive material such as printed wiring boards and wiring which may provide the required ground to result in damage from ESD. In such cases, however, the voltages required are normally higher than those needed when one or more pins or the component case is grounded. Components susceptible to ESA include:

- Microelectronic Components.

- Discrete Semiconductors.

- Film Resistors.

- Resistor Chips.

- Other Thick and Thin Film Components.

- Piezoelectric Crystals.

Known ESDS component types and their relative sensitivities are listed in Table III. Table III component sensitivity is based upon 100pF,  $1500\Omega$  test circuit applying 1 discharge pulse. These sensitivity levels will vary for different test circuits and generally will be substantially less where multiple discharge pulses are applied.

PAGE 9

ISSUE 1

#### TABLE II - TYPICAL ELECTROSTATIC VOLTAGES

| Means of Static Generation               | Electrostatic Voltages      |                             |  |

|------------------------------------------|-----------------------------|-----------------------------|--|

| Means of Static Generation               | 10 to 20% Relative Humidity | 65 to 90% Relative Humidity |  |

| Worker at bench                          | 6 000                       | 100                         |  |

| Vinyl envelopes for work instructions    | 7 000                       | 600                         |  |

| Walking over vinyl floor                 | 12 000                      | 250                         |  |

| Work chair padded with polyurethane foam | 18 000                      | 1 500                       |  |

| Common poly bag picked up from bench     | 20 000                      | 1 200                       |  |

| Walking across carpet                    | 35 000                      | 1 500                       |  |

PAGE 10

ISSUE <sup>-</sup>

#### **TABLE III - LIST OF ESDS COMPONENTS**

#### TABLE III-A - CLASS 1: SENSITIVITY RANGE 0 TO ≤1000 VOLTS

- Metal Oxide Semiconductor (MOS) devices, including C, D, N, P, V and other MOS technology without protective circuitry, or protective circuitry having Class 1 sensitivity.

- Surface Acoustic Wave (SAW) devices.

- Operational Amplifiers (OP AMP) with unprotected MOS capacitors.

- Junction Field Effect Transistors (JFET's).

- Silicon Controlled Rectifiers (SCR's) with lo <0.175 amperes at +100° Celsius (°C) ambient temperature.

- Precision Voltage Regulator Microcircuits: Line or Load Voltage Regulation < 0.5%.</li>

- Microwave and Ultra-High Frequency Semiconductors and Microcircuits: Frequency > 1.0 gigahertz.

- Thin Film Resistors (Type RN) with tolerance of ≤0.1%; power >0.05 watt.

- Thin Film Resistors (Type RN) with tolerance of >0.1%; power ≤0.05 watt.

- Large-Scale Integrated (LSI) Microcircuits, including microprocessors and memories without protective circuitry, or protective circuitry having Class 1 sensitivity.

- (Note: LSI devices usually have 2 to 3 layers of circuitry with metallisation cross-overs and small geometry active elements).

- Hybrids utilising Class 1 parts.

PAGE 11

ISSUE 1

#### TABLE III - LIST OF ESDS COMPONENTS (CONTINUED)

#### TABLE III-B - CLASS 2: SENSITIVITY RANGE > 1000 TO ≤ 4000 VOLTS

- MOS devices or devices containing MOS constituents including C, D, N, P, V or other MOS technology with protective circuitry having Class 2 sensitivity.

- Schottky diodes.

- Precision Resistor Networks (Type RZ).

- High Speed Emitter Coupled Logic (ECL) Microcircuits with propagation delay ≤1 nanosecond.

- Transistor-Transistor Logic (TTL) Microcircuits (Schottky, low power, high speed, and standard).

- Operational Amplifiers (OP AMP) with MOS capacitors with protective circuitry having Class 2 sensitivity.

- LSI with input protection having Class 2 sensitivity.

- Hybrids utilising Class 2 parts.

#### TABLE III-C - CLASS 3: SENSITIVITY RANGE >4000 TO ≤15 000 VOLTS

- Low Power Chopper Transistors.

- Resistor Chips.

- Small Signal Diodes with power ≤ 1.0 watt, excluding Zeners.

- General Purpose Silicon Rectifier Diodes and Fast Recovery Diodes.

- Low Power Silicon Transistors with power <5.0 watts at +25°C.

- All other Microcircuits not included in Class 1 or Class 2.

- Piezoelectric Crystals.

- Hybrids utilising Class 3 parts.

PAGE 12

ISSUE 1

#### 4.5 <u>Failure Mechanisms</u>

Various ESD failure mechanisms can occur within microelectronic and semiconductor devices. These failure mechanisms are power or voltage dependent as shown in Table IV.

#### **TABLE IV - FAILURE MECHANISMS**

|    | Failure Mechanism           | Power | Voltage |

|----|-----------------------------|-------|---------|

| a. | Thermal secondary breakdown | ×     |         |

| b. | Metallisation melt          | ×     |         |

| c. | Dielectric breakdown        |       | ×       |

| d. | Gaseous arc discharge       |       | X       |

| e. | Surface breakdown           |       | Х       |

| f. | Bulk breakdown              | ×     |         |

All the above mentioned failure mechanisms can be observed on semiconductors and other components. Failure mechanisms (b) and (d) are evident for film resistors and failure mechanism (f) for piezoelectric crystals.

Besides these catastrophic failure mechanisms, unencapsulated chips and LSI MOS integrated circuits have exhibited temporary failure due to failure mechanism (d) from positive charges deposited on the chip as a by-product of gaseous arc discharge within the package between the lid and the substrate.

Rev. 'A'

PAGE 13

ISSUE 1

#### 5. <u>ELECTROSTATIC DISCHARGE TEST</u>

#### 5.1 GENERAL

The purpose of ESD testing is to determine the susceptibility of a component to damage from ESD by establishing a sensitivity Class in accordance with Chart II of this specification and ascertaining the minimum voltage at which critical path failure occurs.

ESD testing shall be performed ideally as part of the Evaluation Test Programme (E.T.P.) for the component under examination.

Where an E.T.P. has been completed without performance of an ESD Test, retrospective testing shall be performed on component types listed in Tables III-A, III-B and III-C of this specification if the sensitivity Class and the Minimum Critical Path Failure Voltage, as above, are unknown.

#### 5.1.1 Human ESD Model

Human beings are main sources of ESD for damaging components. The test circuits used for ESD testing is therefore based upon a human discharge model. Electrostatic discharges generated by rubbing or separating materials are readily transmitted to a person's conductive humid skin causing that person to be charged. When a charged person handles, or comes in close proximity of, an ESDS component, this person can damage that component from direct discharge by touching the component or by subjecting the component to an electrostatic field. ESD from a person can be reasonably simulated for test purposes by means of the test circuit shown in Figure I.

Test voltages are measured across the capacitance. The capacitor shall be discharged through the series resistor into the component under test by maintaining the bounceless switch to the discharge position for a time no shorter than required to decay the capacitor voltage to less than 1.0% of the test voltage or 5 seconds, whichever is less. Power supply voltage shall be within a tolerance of  $\pm 5.0\%$  of test voltage.

#### **CAUTION NOTE**

ESD testing should be considered to be destructive. Components subjected to ESD testing should not be used as deliverable hardware due to the possibility of component degradation or latent defects.

Rev. 'B'

PAGE 14

ISSUE 1

#### FIGURE I - HUMAN BODY MODEL TEST CIRCUIT

HVPS = High Voltage Power Supply 0 to 20 000 Volts.

= Current Limiting Resistor.

= Bounceless High Voltage Switch.

R S S<sub>1</sub> = Charge Position. = Discharge Position.

= Source Body Capacitance 100pF ±5.0%.  $C_{\mathsf{b}}$ R<sub>c</sub> CUT = Non-inductive Resistance 1.5k $\Omega$  ±5.0%.

= Component Under Test.

Rev. 'A'

PAGE 15

ISSUE 1

#### 5.2 <u>ESD CLASSIFICATION PROCEDURE</u>

#### 5.2.1 Component Functional Test

The electrical parameters of a component, applicable to the component pin combination being tested (Table V) shall be measured and recorded prior to and after the performance of ESD testing.

#### 5.2.2 Component Failure Definition

A component shall be considered failed when the component functional test performed after ESD testing indicates that one or more electrical parameters do not meet the limits of the applicable ESA/SCC Detail Specification.

A failed component shall not be used in further testing since the failure could affect electrical parameters of other pin combinations.

#### 5.2.3 Determination of Critical Failure Path

The critical failure path shall be determined according to Chart I using the pin combinations listed in Table V. In addition to the pin combinations of Table V, where metallisation cross-overs exist in microelectronic devices, the pin combinations which could result in puncture of the dielectric between these cross-overs should also be tested.

If the component's classification is unknown, start at Para. (a) below.

If the component is Class 1 and the intention is to reclassify the component as Class 2 or 3, start at Para. (d) below.

If the component is Class 2 and the intention is to reclassify the component as Class 3, start at Para. (e) below.

#### Class 1, Sensitivity Range: 0 to 1000 Volts

(a) Measure electrical parameters applicable to the pin combinations shown in Table V. With the test circuit of Figure I apply a test voltage of 1250 Volts to each pin combination shown in Table V.

Re-measure electrical parameters after testing each pin combination. Test until a failure occurs or until all pin combinations have been tested without a failure.

If a failure occurs, proceed to (b); if no failure occurs, proceed to (d).

PAGE 16

ISSUE 1

(b) Repeat (a) for a second component using the same pin combination in which the first failure occurred, using the same voltage.

If a second failure occurs, the pin combination tested shall be designated as a critical path.

(c) Continue with (a), using a new component (or the component used for (b) if no failure occurs) for the remaining pin combinations to determine whether other critical paths exist.

#### Class 2, Sensitivity Range: 1000 to 4000 Volts

(d) Repeat (a) followed by (b) and (c) if applicable, for pin combinations that were not previously found to be critical paths, using 5000 Volts in place of 1250 Volts and a new component if necessary.

#### Class 3, Sensitivity Range: 4000 to 15000 Volts

- (e) Repeat (d), but using 18750 Volts in place of 5000 Volts and a new component if necessary.

- (f) Rank critical paths in ascending order of their voltage sensitivity as determined by (a) to (e).

- (g) Proceed to the testing specified in Para. 5.2.4 if a critical path has been found.

#### 5.2.4 ESD Classification Testing

The test procedure shall be in accordance with the Chart II using a sample size of 10 components.

The components shall be tested using the test circuit of Figure I for each critical path determined in Para. 5.2.3. Continue testing until 10 components have been tested or until 2 components have failed on the same critical path at a given voltage level. Start with the lowest voltage ranked critical path.

Rev. 'A'

PAGE 17

ISSUE 1

- If the critical path was determined in Para. 5.2.3(a) and (b), use 1000 Volts as the test voltage.

- If the critical path was determined in Para. 5.2.3(d), use 4000 Volts as the test voltage.

- If the critical path was determined in Para. 5.2.3(e), use 15000 Volts as the test voltage.

Using this procedure, components will be classified into ESD sensitivity class 1, 2 or 3 or unclassified if not more than 1 failure occurs for a given critical path.

#### 5.2.5 Critical Path Failure Voltage Testing

When the classification procedure detailed in Para. 5.2.4 has been completed, the value of the Minimum Critical Path Failure Voltage shall be found for components which have been categorised into one of the three sensitivity classes. The test procedure shall be as given below, using components from Para. 5.2.4 on which no critical path failures have been found.

Using the test circuit in Figure 1, the value shall be established by increasing the test voltage applied to the critical path under test from the minimum voltage for the class into which the failure falls, upwards, until such time as failure occurs.

The increase in voltage shall be made on a "stepped" basis until the value of the failure voltage has been determined. A "voltage step" shall be approximately 10% of the maximum test voltage for the class.

Where more than one critical path is to be tested for a component type, the lowest value measured shall be the Critical Path Failure Voltage.

#### 5.2.6 ESD Warning

If an ESD classification is allocated to a component, the classification number and the minimum critical path failure voltage, as determined using Paras 5.2.3 and 5.2.5, shall be included into an ESD Warning paragraph to be inserted into Section 1 of the Detail Specification.

The warning paragraph shall take the following form:-

#### 1.x HANDLING PRECAUTIONS

These components are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, shipment and any handling.

These components are categorised as Class X with a Minimum Critical Path Failure Voltage of XXXXX Volts.

PAGE 18

ISSUE 1

#### TABLE V - PIN COMBINATIONS FOR ESD TESTING

| Component Types       | Pin Combinations                                                                                                                       |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| All components        | <ul> <li>All pins tied together (+) to top centre of case (-)</li> <li>All pins tied together (-) to top centre of case (+)</li> </ul> |

| Resistors             | - Terminal (+) to terminal (-)                                                                                                         |

| Diodes                | - Anode (+) to cathode (-) - Anode (-) to cathode (+)                                                                                  |

| Transistors           | - Emitter to base (1) - Base to collector (1)                                                                                          |

| Digital Microcircuits | - Input (+) to common (-) (2) - Output (-) to common (+) (2) - Input (+) to output (-) - V+ (-) to common (+)                          |

| Linear Microcircuits  | - Input (+) to common (-) - Input (+) to input (-) - Output (-) to common (+) - V+ (-) to common (+)                                   |

| MOS FET's and JFET's  | - Gate to source (1) - Gate to drain (1)                                                                                               |

#### **NOTES**

- 1. Both polarity (+) to (-) and (-) to (+).

- Common

For NPN technology microcircuits, common is the most negative terminal (i.e. V – or GND). For PNP technology, common is GND.

PAGE 19

ISSUE 1

#### **CHART I - CRITICAL PATH DETERMINATION**

PAGE 20 ISSUE 1

#### **CHART II - CLASSIFICATION TESTING**