Page 1 of 17

# TRANSISTORS, POWER, MOSFET, P-CHANNEL, RAD-HARD

# **BASED ON TYPE STRH40P10**

ESCC Detail Specification No. 5205/025

Issue 8 November 2021

Document Custodian: European Space Agency – see https://escies.org

#### **LEGAL DISCLAIMER AND COPYRIGHT**

European Space Agency, Copyright © 2021. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

# **DOCUMENTATION CHANGE NOTICE**

(Refer to https://escies.org for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION                                     |

|---------|--------------------------------------------------------|

| 1463    | Specification upissued to incorporate changes per DCR. |

# ESCC Detail Specification

PAGE 4

No. 5205/025

ISSUE 8

# TABLE OF CONTENTS

| 1       | GENERAL                                                               | 5  |

|---------|-----------------------------------------------------------------------|----|

| 1.1     | SCOPE                                                                 | 5  |

| 1.2     | APPLICABLE DOCUMENTS                                                  | 5  |

| 1.3     | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS                  | 5  |

| 1.4     | THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS                 | 5  |

| 1.4.1   | The ESCC Component Number                                             | 5  |

| 1.4.2   | Component Type Variants                                               | 5  |

| 1.5     | MAXIMUM RATINGS                                                       | 6  |

| 1.6     | HANDLING PRECAUTIONS                                                  | 7  |

| 1.7     | PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION                       | 8  |

| 1.8     | FUNCTIONAL DIAGRAM                                                    | 9  |

| 1.9     | MATERIALS AND FINISHES                                                | 9  |

| 2       | REQUIREMENTS                                                          | 9  |

| 2.1     | GENERAL                                                               | 9  |

| 2.1.1   | Deviations from the Generic Specification                             | 9  |

| 2.1.1.1 | Deviations from Screening Tests - Chart F3                            | 9  |

| 2.2     | WAFER LOT ACCEPTANCE                                                  | 10 |

| 2.3     | MARKING                                                               | 10 |

| 2.4     | CASE ISOLATION                                                        | 10 |

| 2.5     | TERMINAL STRENGTH                                                     | 10 |

| 2.6     | ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES            | 10 |

| 2.6.1   | Room Temperature Electrical Measurements                              | 10 |

| 2.6.2   | High and Low Temperatures Electrical Measurements                     | 11 |

| 2.6.3   | Notes to Room, High and Low Electrical Measurements                   | 12 |

| 2.7     | PARAMETER DRIFT VALUES                                                | 12 |

| 2.8     | INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS                    | 13 |

| 2.9     | HIGH TEMPERATURE REVERSE BIAS BURN-IN CONDITIONS                      | 13 |

| 2.10    | HIGH TEMPERATURE FORWARD BIAS BURN-IN CONDITIONS                      | 14 |

| 2.11    | OPERATING LIFE CONDITIONS                                             | 14 |

| 2.12    | TOTAL DOSE RADIATION TESTING                                          | 14 |

| 2.12.1  | Bias Conditions and Total Dose Level for Total Dose Radiation Testing | 14 |

| 2.12.2  | Electrical Measurements for Total Dose Radiation Testing              | 15 |

| APPEND  | IX 'A'                                                                | 16 |

#### 1 GENERAL

#### 1.1 SCOPE

This specification details the ratings, physical and electrical characteristics and test and inspection data for the component type variants and/or the range of components specified below. It supplements the requirements of, and shall be read in conjunction with, the ESCC Generic Specification listed under Applicable Documents.

#### 1.2 APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:

- (a) ESCC Generic Specification No. 5000

- (b) MIL-STD-750, Test Methods and Procedures for Semiconductor Devices

#### 1.3 TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESCC Basic Specification No. 21300 shall apply.

#### 1.4 THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS

#### 1.4.1 The ESCC Component Number

The ESCC Component Number shall be constituted as follows:

Example: 520502501R

Detail Specification Reference: 5205025

Component Type Variant Number: 01 (as required)Total Dose Radiation Level Letter: R (as required)

#### 1.4.2 <u>Component Type Variants</u>

The component type variants applicable to this specification are as follows:

| Variant<br>Number | Based on Type | Case     | Lead Material and Finish | Weight<br>max g | Total Dose Radiation<br>Level Letter |

|-------------------|---------------|----------|--------------------------|-----------------|--------------------------------------|

| 01                | STRH40P10     | TO-254AA | S14                      | 10              | R [100kRAD(Si)]                      |

| 02                | STRH40P10     | TO-254AA | S4                       | 10              | R [100kRAD(Si)]                      |

The lead material and finish shall be in accordance with the requirements of ESCC Basic Specification No. 23500.

Total dose radiation level letters are defined in ESCC Basic Specification No. 22900. If an alternative radiation test level is specified in the Purchase Order the letter shall be changed accordingly.

1.5

#### MAXIMUM RATINGS

The maximum ratings shall not be exceeded at any time during use or storage.

Maximum ratings shall only be exceeded during testing to the extent specified in this specification and when stipulated in Test Methods and Procedures of the ESCC Generic Specification.

| Characteristics                              | Symbols              | Maximum<br>Ratings | Unit | Remarks                                                                        |

|----------------------------------------------|----------------------|--------------------|------|--------------------------------------------------------------------------------|

| Drain-Source Voltage                         | V <sub>D</sub> s     | -100               | V    | Over T <sub>op</sub> , V <sub>GS</sub> = 0V<br>Note 2                          |

| Gate-Source Voltage                          | V <sub>G</sub> s     | ±20                | V    | Over T <sub>op</sub>                                                           |

| Drain Current                                | Ips                  | -34                | А    | Continuous, At T <sub>case</sub> ≤ +25°C<br>Note 1                             |

|                                              |                      | -21                | Α    | Continuous, At T <sub>case</sub> > +100°C<br>Note 1                            |

| Drain Current (Pulsed)                       | I <sub>DM</sub>      | -136               | Α    | Note 2                                                                         |

| Power Dissipation                            | P <sub>tot</sub>     | 176                | W    | At T <sub>case</sub> ≤ +25°C<br>Note 1                                         |

| Avalanche Energy<br>(Single Pulse)           | Eas                  |                    | mJ   | V <sub>DS</sub> = -50V, I <sub>A</sub> = -17A                                  |

| (Onigio i dioo)                              |                      | 1133<br>332        |      | $T_j$ = +25 ±3°C<br>$T_j$ = +110 (+0 -5)°C                                     |

| Avalanche Energy<br>(Repetitive Pulse)       | Ear                  |                    | mJ   | V <sub>DS</sub> = -50V, I <sub>A</sub> = -17A, f = 100kHz,<br>Duty Cycle = 10% |

|                                              |                      | 25<br>8            |      | $T_j$ = +25 ±3°C<br>$T_j$ = +110 (+0 -5)°C                                     |

| Operating Temperature Range                  | Тор                  | -55 to +150        | °C   | Note 3                                                                         |

| Junction Temperature                         | Tj                   | +150               | °C   |                                                                                |

| Storage Temperature Range                    | $T_{stg}$            | -55 to +150        | °C   | Note 3                                                                         |

| Soldering Temperature                        | T <sub>sol</sub>     | +260               | °C   | Note 4                                                                         |

| Thermal Resistance,<br>Junction-to-Heat Sink | R <sub>th(j-s)</sub> | 0.71               | °C/W | Note 5                                                                         |

| Thermal Resistance,<br>Junction-to-Ambient   | $R_{th(j-a)}$        | 48                 | °C/W | Note 2                                                                         |

#### **NOTES:**

1.  $I_{DS}$  and  $P_{tot}$  ratings are in accordance with  $R_{th(j-s)}$ . The maximum theoretical  $I_D$  limit at  $T_{case} > +25^{\circ}C$  can be obtained by using the following formula ( $I_D$  is limited by the package and device construction):

$$I_D = \sqrt{\frac{T_j(max) - T_{case}}{R_{th(j-s)} \times \left(r_{DS(on)} \text{ at } T_j(max)\right)}}$$

Where  $r_{DS(on)}$  at  $T_j(max) = 150m\Omega$ .

For  $T_{case} > +25$ °C, the power dissipation derates linearly to 0W at  $T_{case} = +150$ °C.

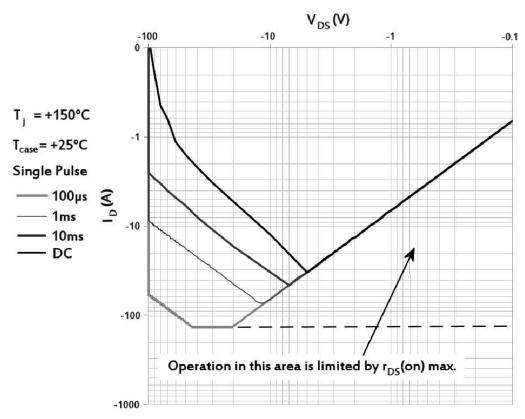

#### 2. Safe Operating Area applies as follows:

#### **MAXIMUM SAFE OPERATING AREA**

- 3. For Variants with hot solder dip lead finish, all testing and any handling performed at  $T_{amb} > +125$ °C shall be carried out in a 100% inert atmosphere.

- 4. Duration 10 seconds maximum at a distance of not less than 1.5mm from the device body and the same lead shall not be resoldered until 3 minutes have elapsed.

- 5. Package is mounted on an infinite heatsink.

#### 1.6 HANDLING PRECAUTIONS

These components are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, shipment and any handling.

These components are categorised as Class 3 per ESCC Basic Specification No. 23800 with a Minimum Critical Path Failure Voltage of 7600 Volts.

The TO-254AA package contains Beryllium Oxide (BeO) and therefore it must not be ground, machined, sandblasted or subjected to any mechanical operation which will produce dust. The case must not be subjected to any chemical process (e.g. etching) which will produce fumes.

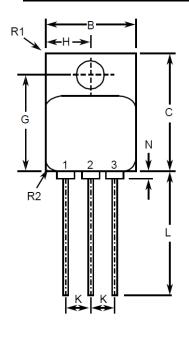

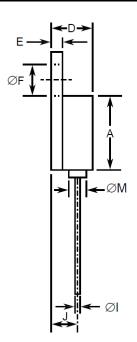

# 1.7 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

# METAL FLANGE MOUNT PACKAGE (TO-254AA) - 3 LEAD

| Symbols | Dimensi | ons mm | Notes |

|---------|---------|--------|-------|

|         | Min     | Max    |       |

| Α       | 13.59   | 13.84  |       |

| В       | 13.59   | 13.84  |       |

| С       | 20.07   | 20.32  |       |

| D       | 6.3     | 6.7    |       |

| Е       | 1       | 1.35   |       |

| ØF      | 3.5     | 3.9    |       |

| G       | 16.89   | 17.4   |       |

| Н       | 6.86    | BSC    |       |

| ØI      | 0.89    | 1.14   | 2     |

| J       | 3.81    | BSC    |       |

| K       | 3.81    | BSC    |       |

| L       | 12.95   | 14.5   |       |

| ØM      | 3.05 T  | 2      |       |

| N       | -       | 0.71   | 2     |

| R1      | -       | 1      | 3     |

| R2      | 1.65 T  | ypical | 4     |

# NOTES:

1. The terminal identification is specified by the component's geometry. See Para. 1.8 Functional Diagram for the terminal connections.

2. 3 places.

- 3. Radius of heatsink flange corner, 4 places.

- 4. Radius of body corner, 4 places.

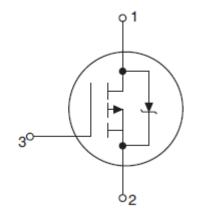

#### 1.8 <u>FUNCTIONAL DIAGRAM</u>

Terminal 1: Drain Terminal 2: Source

Terminal 3: Gate

#### NOTES:

1. The case is not connected to any lead.

#### 1.9 MATERIALS AND FINISHES

Materials and finishes shall be as follows:

- (a) Case

- The case shall be hermetically sealed and have a metal body. The leads pass through ceramic eyelets brazed into the frame and the lid shall be welded.

- (b) Leads

As specified in Para. 1.4.2.

#### 2 **REQUIREMENTS**

#### 2.1 GENERAL

The complete requirements for procurement of the components specified herein are as stated in this specification and the ESCC Generic Specification. Permitted deviations from the Generic Specification, applicable to this specification only, are listed below.

Permitted deviations from the Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESCC requirement and do not affect the component's reliability, are listed in the appendices attached to this specification.

#### 2.1.1 <u>Deviations from the Generic Specification</u>

#### 2.1.1.1 Deviations from Screening Tests - Chart F3

- (a) Verification of Safe Operating Area

The Safe Operating Area shall be verified by performing the ΔV<sub>SD</sub> test specified in

Para. 2.6.1 Room Temperature Electrical Measurements (Thermal Resistance,

Junction-to-Heat Sink).

- (b) A High Temperature Forward Bias test shall be performed instead of Power Burn-in.

#### 2.2 WAFER LOT ACCEPTANCE

A SEM inspection shall be performed as specified in the ESCC Generic Specification.

#### 2.3 MARKING

The marking shall be in accordance with the requirements of ESCC Basic Specification No. 21700 and as follows.

The information to be marked on the component shall be:

- (a) The ESCC Qualified Component symbol (for ESCC qualified components only).

- (b) The ESCC Component Number.

- (c) Traceability information.

- (d) Warning sign for Beryllium Oxide.

#### 2.4 CASE ISOLATION

Case Isolation shall be performed as specified in the ESCC Generic Specification and as follows:

- Test Conditions:

- o Test voltage: 500Vdc

- Duration of application of test voltage: 1s

- Points of application of test voltage: between case metal tab and all terminals connected together.

- Maximum leakage current: 10nA

#### 2.5 <u>TERMINAL STRENGTH</u>

The test conditions for terminal strength, tested as specified in the ESCC Generic Specification, shall be as follows:

Test Condition: A, tension, with an applied force of 10N for a duration of 10s.

#### 2.6 <u>ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES</u>

Electrical measurements shall be performed at room, high and low temperatures. Consolidated notes are given after the tables in Para. 2.6.3.

#### 2.6.1 Room Temperature Electrical Measurements

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$  = +22 ±3°C.

| Characteristics                      | Symbols MIL-STD-750  |             | Test Conditions                                       | Limits |      | Units |

|--------------------------------------|----------------------|-------------|-------------------------------------------------------|--------|------|-------|

|                                      |                      | Test Method |                                                       | Min    | Max  |       |

| Drain-to-Source<br>Breakdown Voltage | V <sub>(BR)DSS</sub> | 3407        | $V_{GS} = 0V$ ,<br>$I_D = -1mA$<br>Bias condition C   | -100   | -    | V     |

| Gate-to-Source<br>Leakage Current 1  | I <sub>GSS1</sub>    | 3411        | $V_{GS}$ = -20V,<br>$V_{DS}$ = 0V<br>Bias condition C | -      | -100 | nA    |

| Gate-to-Source<br>Leakage Current 2  | I <sub>GSS2</sub>    | 3411        | $V_{GS} = 20V,$<br>$V_{DS} = 0V$<br>Bias condition C  | 100    | -    | nA    |

ISSUE 8

| Characteristics                              | Symbols MIL-STD-750 Test Conditions Test Method |      | Test Conditions                                                                   | Limits |      | Units |

|----------------------------------------------|-------------------------------------------------|------|-----------------------------------------------------------------------------------|--------|------|-------|

|                                              |                                                 |      | Min                                                                               | Max    |      |       |

| Drain Current                                | I <sub>DSS</sub>                                | 3413 | $V_{DS}$ = -80V,<br>$V_{GS}$ = 0V<br>Bias condition C                             | -      | -10  | μΑ    |

| Gate-to-Source<br>Threshold Voltage          | V <sub>GS(th)</sub>                             | 3403 | V <sub>DS</sub> ≥ V <sub>GS</sub><br>I <sub>D</sub> = -1mA                        | -2     | -4.5 | V     |

| Static Drain-to-Source<br>On Resistance      | r <sub>DS(on)</sub>                             | 3421 | V <sub>GS</sub> = -12V, I <sub>D</sub> = -17A<br>Note 1                           | -      | 75   | mΩ    |

| Source-to-Drain Diode<br>Forward Voltage     | V <sub>SD</sub>                                 | 4011 | V <sub>GS</sub> = 0V, I <sub>SD</sub> = -34A<br>Note 1                            | -      | -1.5 | V     |

| Thermal Resistance,<br>Junction-to-Heat Sink | R <sub>th(j-s)</sub>                            | 3161 | Note 2                                                                            | -      | 0.71 | °C/W  |

| Input Capacitance                            | C <sub>iss</sub>                                | 3431 | $V_{GS} = 0V, V_{DS} = -25V$                                                      | 3710   | 5570 | pF    |

| Output Capacitance                           | Coss                                            | 3453 | f = 1MHz                                                                          | 510    | 760  | pF    |

| Reverse Transfer<br>Capacitance              | Crss                                            | 3433 |                                                                                   | 204    | 306  | pF    |

| Total Gate Charge                            | Qg                                              | 3471 | V <sub>GS</sub> = -12V, V <sub>DS</sub> = -50V                                    | 130    | 194  | nC    |

| Gate-to-Source Charge                        | Qgs                                             |      | $I_D = -34A$                                                                      | 14     | 22   | nC    |

| Gate-to-Drain Charge                         | $Q_{gd}$                                        |      |                                                                                   | 32     | 48   | nC    |

| Turn-on Delay Time                           | t <sub>d(on)</sub>                              | 3472 | V <sub>GS</sub> = -12V, V <sub>DS</sub> = -50V                                    | 15     | 33   | ns    |

| Rise Time                                    | tr                                              |      | $I_D = -17A$<br>$R_G = 4.7\Omega$                                                 | 19     | 43   | ns    |

| Turn-off Delay Time                          | $t_{\sf d(off)}$                                |      | 1.1.22                                                                            | 98     | 147  | ns    |

| Fall Time                                    | t <sub>f</sub>                                  |      |                                                                                   | 34     | 58   | ns    |

| Reverse Recovery Time                        | t <sub>rr</sub>                                 | 3473 | $V_{DS} = -12V$ , $I_{SD} = -34A$<br>di/dt = 40A/ $\mu$ s<br>$T_j = +25 \pm 3$ °C | 276    | 414  | ns    |

# 2.6.2 <u>High and Low Temperatures Electrical Measurements</u>

| Characteristics                     | Symbols | MIL-STD-750 | Test Conditions                                                                     | Limits |      | Units |

|-------------------------------------|---------|-------------|-------------------------------------------------------------------------------------|--------|------|-------|

|                                     |         | Test Method | Note 3                                                                              | Min    | Max  |       |

| Gate-to-Source<br>Leakage Current 1 | Igss1   | 3411        | $V_{GS}$ = -20V,<br>$V_{DS}$ = 0V<br>Bias condition C<br>$T_{case}$ = +125 (+0-5)°C | -      | -200 | nA    |

| Gate-to-Source<br>Leakage Current 2 | lgss2   | 3411        | $V_{GS} = 20V,$ $V_{DS} = 0V$ Bias condition C $T_{case} = +125 (+0-5)^{\circ}C$    | 200    | -    | nA    |

| Drain Current                       | IDSS    | 3413        | $V_{DS}$ = -80V,<br>$V_{GS}$ = 0V<br>Bias condition C<br>$T_{case}$ = +125 (+0-5)°C | -      | -100 | μА    |

| Characteristics                          | Symbols MIL-STD-750 Test Method |              | Test Conditions<br>Note 3                                                              | Limits |       | Units |

|------------------------------------------|---------------------------------|--------------|----------------------------------------------------------------------------------------|--------|-------|-------|

|                                          |                                 | 1 est Method | Note 3                                                                                 | Min    | Max   |       |

| Gate-to-Source<br>Threshold Voltage      | V <sub>GS(th)</sub>             | 3403         | $V_{DS} \ge V_{GS}$<br>$I_D = -1mA$<br>$T_{case} = +125 (+0-5)^{\circ}C$               | -1.6   | -3.7  | V     |

|                                          |                                 |              | $V_{DS} \ge V_{GS}$<br>$I_D = -1 \text{mA}$<br>$T_{case} = -55 (+5-0)^{\circ}\text{C}$ | -2.3   | -5.2  | V     |

| Static Drain-to-Source<br>On Resistance  | r <sub>DS(on)</sub>             | 3421         | $V_{GS}$ = -12V, $I_{D}$ = -17A<br>$T_{case}$ = +125 (+0-5)°C<br>Note 1                | -      | 140   | mΩ    |

| Source-to-Drain Diode<br>Forward Voltage | V <sub>SD</sub>                 | 4011         | $V_{GS} = 0V$ , $I_{SD} = -34A$<br>$T_{case} = +125 (+0-5)^{\circ}C$<br>Note 1         | -      | -1.25 | V     |

#### 2.6.3 Notes to Room, High and Low Electrical Measurements

- 1. Pulsed measurement: Pulse Width ≤ 680µs, Duty Cycle ≤ 2%.

- 2. The  $R_{th(j-s)}$  limit is guaranteed by performing a  $\Delta V_{SD}$  (go-no-go) test. The following test conditions and limits shall apply:

- V<sub>DS</sub> = -8V

- $I_D = -17.94A$

- I<sub>cal</sub> = -26mA

- t<sub>pulse</sub> = 20ms

- t<sub>cal</sub> = 50μs

- V<sub>SD</sub> = -80mV minimum, -180mV maximum

- 3. Read and record measurements shall be performed on a sample of 5 components with 0 failures allowed. Alternatively a 100% inspection may be performed.

#### 2.7 PARAMETER DRIFT VALUES

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$  = +22 ±3°C

The test methods and test conditions shall be as per the corresponding test defined in Para. 2.6.1 Room Temperature Electrical Measurements.

The drift values ( $\Delta$ ) shall not be exceeded for each characteristic specified. The corresponding absolute limit values for each characteristic shall not be exceeded.

| Characteristics                     | Symbols           |                        | Units |       |    |

|-------------------------------------|-------------------|------------------------|-------|-------|----|

|                                     |                   | Drift Absolute         |       | olute |    |

|                                     | Value<br>Δ        |                        | Min   | Max   |    |

| Gate-to-Source Leakage<br>Current 1 | I <sub>GSS1</sub> | ±50<br>or (1)<br>±100% | -     | -100  | nA |

| Gate-to-Source Leakage<br>Current 2 | I <sub>GSS2</sub> | ±50<br>or (1)<br>±100% | 100   | -     | nA |

| Drain Current                       | I <sub>DSS</sub>  | ±4<br>or (1)<br>±100%  | -     | -10   | μA |

| Characteristics                      | Symbols             |                |     |      | Units |

|--------------------------------------|---------------------|----------------|-----|------|-------|

|                                      |                     | Drift<br>Value |     |      |       |

|                                      |                     | ναίμε<br>Δ     | Min | Max  |       |

| Gate-to-Source Threshold<br>Voltage  | V <sub>GS(th)</sub> | ±5%            | -2  | -4.5 | V     |

| Static Drain-to-Source On Resistance | r <sub>DS(on)</sub> | ±10%           | -   | 75   | mΩ    |

#### NOTES:

#### 2.8 <u>INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS</u>

Unless otherwise specified, the measurements shall be performed at T<sub>amb</sub> = +22 ±3°C.

The test methods and test conditions shall be as per the corresponding test defined in Para. 2.6.1 Room Temperature Electrical Measurements.

The limit values for each characteristic shall not be exceeded.

| Characteristics                      | Symbols             | Limits |      | Units |

|--------------------------------------|---------------------|--------|------|-------|

|                                      |                     | Min    | Max  |       |

| Drain Current                        | I <sub>DSS</sub>    | -      | -10  | μΑ    |

| Gate-to-Source Threshold Voltage     | V <sub>GS(th)</sub> | -2     | -4.5 | V     |

| Static Drain-to-Source On Resistance | r <sub>DS(on)</sub> | -      | 75   | mΩ    |

#### 2.9 <u>HIGH TEMPERATURE REVERSE BIAS BURN-IN CONDITIONS</u>

HTRB Burn-in shall be performed in accordance with MIL-STD-750, Test Method 1042, Test Condition A with the following conditions:

| Characteristics         | Symbols          | Test Conditions | Units |

|-------------------------|------------------|-----------------|-------|

| Ambient Temperature     | T <sub>amb</sub> | +150 (+0-5)     | °C    |

| Drain-to-Source Voltage | V <sub>DS</sub>  | -80             | V     |

| Gate-to-Source Voltage  | V <sub>G</sub> S | 0               | V     |

| Duration                | t                | 240 minimum     | Hours |

<sup>1.</sup> Whichever is the greater referred to the initial value.

#### 2.10 HIGH TEMPERATURE FORWARD BIAS BURN-IN CONDITIONS

HTFB Burn-in shall be performed in accordance with MIL-STD-750, Test Method 1042, Test Condition B with the following conditions:

| Characteristics         | Symbols          | Test Conditions | Units |

|-------------------------|------------------|-----------------|-------|

| Ambient Temperature     | T <sub>amb</sub> | +150 (+0-5)     | °C    |

| Drain-to-Source Voltage | V <sub>DS</sub>  | 0               | V     |

| Gate-to-Source Voltage  | $V_{GS}$         | -16             | V     |

| Duration                | t                | 48 minimum      | Hours |

#### 2.11 OPERATING LIFE CONDITIONS

Operating Life shall consist of High Temperature Reverse Bias in accordance with MIL-STD-750, Test Method 1042, Test Condition A, followed by High Temperature Forward Bias in accordance with MIL-STD-750, Test Method 1042, Test Condition B. The test conditions are as follows:

#### HIGH TEMPERATURE REVERSE BIAS CONDITIONS

| Characteristics         | Symbols Test Conditions |              | Units |

|-------------------------|-------------------------|--------------|-------|

| Ambient Temperature     | T <sub>amb</sub>        | +150 (+0-5)  | °C    |

| Drain-to-Source Voltage | V <sub>DS</sub>         | -80          | V     |

| Gate-to-Source Voltage  | V <sub>G</sub> S        | 0            | V     |

| Duration                | t                       | 1000 minimum | Hours |

#### HIGH TEMPERATURE FORWARD BIAS CONDITIONS

| Characteristics         | Symbols          | Test Conditions | Units |

|-------------------------|------------------|-----------------|-------|

| Ambient Temperature     | T <sub>amb</sub> | +150 (+0-5)     | °C    |

| Drain-to-Source Voltage | V <sub>DS</sub>  | 0               | V     |

| Gate-to-Source Voltage  | V <sub>G</sub> S | -16             | V     |

| Duration                | t                | 1000 minimum    | Hours |

#### 2.12 TOTAL DOSE RADIATION TESTING

All lots shall be irradiated in accordance with ESCC Basic Specification No. 22900, standard dose rate (window 1: 3.6kRAD to 36kRAD per hour).

#### 2.12.1 Bias Conditions and Total Dose Level for Total Dose Radiation Testing

The following bias condition (worst-case) shall be used for Total Dose Radiation Testing at  $T_{amb}$  = +22 ±3°C:

With  $V_{GS}$  bias = -15V and  $V_{DS}$  = 0V during irradiation.

The total dose level applied shall be as specified in the component type variant information herein or in the Purchase Order.

#### 2.12.2 <u>Electrical Measurements for Total Dose Radiation Testing</u>

Prior to irradiation testing the devices shall have successfully met Room Temperature Electrical Measurements specified herein (Para. 2.6.1).

Unless otherwise stated the measurements shall be performed at  $T_{amb}$  = +22 ±3°C.

Unless otherwise specified the test methods and test conditions shall be as per the corresponding test defined in Para. 2.6.1 Room Temperature Electrical Measurements.

The parameters to be measured during irradiation testing, on completion of irradiation testing, after 24 hours anneal at Room Temperature and after 168 hours anneal at  $\pm 3^{\circ}$ C are shown below.

| Characteristics                          | Symbols             | Limits        |          |      | Units |

|------------------------------------------|---------------------|---------------|----------|------|-------|

|                                          | Drift Values        |               | Absolute |      |       |

|                                          |                     | Δ             | Min      | Max  |       |

| Drain-to-Source Voltage<br>Note 1        | V <sub>DSS</sub>    | +5%<br>Note 2 | N        | /A   | V     |

| Gate-to-Source Leakage<br>Current 1      | I <sub>GSS1</sub>   | -1.5          | -        | -100 | nA    |

| Gate-to-Source Leakage<br>Current 2      | I <sub>GSS2</sub>   | +1.5          | 100      | -    | nA    |

| Drain Current                            | I <sub>DSS</sub>    | -1            | -        | -10  | μA    |

| Gate-to-Source Threshold Voltage         | V <sub>GS(th)</sub> | +150%         | -2       | -4.5 | V     |

| Static Drain-to-Source On Resistance     | r <sub>DS(on)</sub> | -4% / +35%    | -        | 75   | mΩ    |

| Source-to-Drain Diode<br>Forward Voltage | V <sub>SD</sub>     | ±5%           | -        | -1.5 | V     |

#### **NOTES:**

- 1. Drain-to-Source Voltage measurements shall be made in accordance with MIL-STD-750, Test Method 3405, with  $V_{GS} = 0V$  and  $I_D = -1mA$ .

- 2. Referred to an initial Drain-to-Source Voltage measurement made prior to the commencement of Total Dose Radiation Testing.

# APPENDIX 'A' AGREED DEVIATIONS FOR STMICROELECTRONICS (F)

| ITEMS AFFECTED                                                                                        | DESCRIPTION OF DEVIATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Para. 2.1.1, Deviations from<br>the Generic Specification:<br>Para. 8, Test Methods and<br>Procedures | <ul> <li>For qualification and qualification maintenance, or procurement of qualified or unqualified components, the following replacement test method specifications shall be used instead of the following ESCC Basic Specifications:         <ul> <li>No. 20500, External Visual Inspection: replaced by MIL-STD-750 Test Method 2071.</li> </ul> </li> <li>No. 20900, Radiographic Inspection of Electronic Components: replaced by MIL-STD-750 Test Method 2076.</li> <li>No. 21400, Scanning Electron Microscope Inspection of Semiconductor Dice: replaced by MIL-STD-750 Test Method 2077.</li> </ul>                                                                                                                                                                                                                                   |

| Para. 2.6.1 Room<br>Temperature Electrical<br>Measurements                                            | The AC characteristics C <sub>iss</sub> , C <sub>oss</sub> , C <sub>rss</sub> , Q <sub>g</sub> , Q <sub>gs</sub> , Q <sub>gd</sub> , t <sub>d(on)</sub> , t <sub>r</sub> , t <sub>d(off)</sub> , t <sub>f</sub> and t <sub>rr</sub> may be considered guaranteed but not tested if successful pilot lot testing has been performed on the wafer lot in accordance with STMicroelectronics "wafers acceptation" internal procedure as specified in the PID, which includes AC (C <sub>iss</sub> , C <sub>oss</sub> , C <sub>rss</sub> , Q <sub>g</sub> , Q <sub>gs</sub> , Q <sub>gd</sub> , t <sub>d(on)</sub> , t <sub>r</sub> , t <sub>d(off)</sub> , t <sub>f</sub> and t <sub>rr</sub> ) characteristic measurements per the Detail Specification.  A summary of the pilot lot testing shall be provided if required by the Purchase Order. |

| Para. 2.1.1.1 Deviations from Screening Tests - Chart F3                                              | Solderability is not applicable unless specifically stipulated in the Purchase Order.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### ADDITIONAL DATA - STMICROELECTRONICS (F)

(a) Derating for Space Application

These components are susceptible to Single Event Gate Rupture if operated in a space environment unless the following derating is applied:

$V_{DS} \ge -60V$  when  $V_{GS} = 2V$  $V_{DS} \ge -20V$  when  $V_{GS} = 15V$

The derating for space applications was originally obtained on STRH40P10 devices under the following test conditions. The testing was performed in a vacuum:

For V<sub>GS</sub> = 2V; location = RADEF (Jyväskylä, Finland):

Ion used = Kr

LET =  $32 \text{MeV/(mg/cm}^2)$

Energy = 768MeV Range = 94 $\mu$ m

For V<sub>GS</sub> = 15V; location = UCL (Louvain-la-Neuve, Belgium):

Ion used = Kr

LET =  $32.4 \text{MeV/(mg/cm}^2)$

Energy = 756MeV Range = 92µm