Page 1 of 22

# INTEGRATED CIRCUITS, MONOLITHIC, CMOS AND HBT ON SiGe:C, 1.6 TO 12 GHz FREQUENCY SYNTHESIZER WITH INTEGRATED SIGMA DELTA MODULATOR FRACTIONAL-N PLL

# **BASED ON TYPE NOV1G14**

ESCC Detail Specification No. 9202/085

Issue 2 June 2025

Document Custodian: European Space Agency - see https://escies.org

## **LEGAL DISCLAIMER AND COPYRIGHT**

European Space Agency, Copyright © 2025. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

# **DOCUMENTATION CHANGE NOTICE**

(Refer to https://escies.org for ESCC DCR content)

| DCR No. | CHANGE DESCRIPTION                                     |

|---------|--------------------------------------------------------|

| 1734    | Specification upissued to incorporate changes per DCR. |

# ESCC Detail Specification

No. 9202/085

PAGE 4

ISSUE 2

# **TABLE OF CONTENTS**

| 1       | GENERAL                                                               | 5  |

|---------|-----------------------------------------------------------------------|----|

| 1.1     | SCOPE                                                                 | 5  |

| 1.2     | APPLICABLE DOCUMENTS                                                  | 5  |

| 1.3     | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS                  | 5  |

| 1.4     | THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS                 | 5  |

| 1.4.1   | The ESCC Component Number                                             | 5  |

| 1.4.2   | Component Type Variants                                               | 5  |

| 1.5     | MAXIMUM RATINGS                                                       | 6  |

| 1.6     | HANDLING PRECAUTIONS                                                  | 6  |

| 1.7     | PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION                       | 7  |

| 1.8     | FUNCTIONAL DIAGRAM                                                    | 8  |

| 1.9     | PIN ASSIGNMENT AND DESCRIPTION                                        | 8  |

| 1.10    | FUNCTIONAL DESCRIPTION                                                | 11 |

| 1.10.1  | Overview                                                              | 11 |

| 1.10.2  | Register Programming                                                  | 12 |

| 1.11    | PROTECTION NETWORKS                                                   | 15 |

| 2       | REQUIREMENTS                                                          | 15 |

| 2.1     | GENERAL                                                               | 15 |

| 2.1.1   | Deviations from the Generic Specification                             | 16 |

| 2.1.1.1 | Deviations from Screening Tests - Chart F3                            | 16 |

| 2.2     | MARKING                                                               | 16 |

| 2.3     | ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES            | 16 |

| 2.3.1   | Room Temperature Electrical Measurements                              | 16 |

| 2.3.2   | High and Low Temperatures Electrical Measurements                     | 19 |

| 2.4     | PARAMETER DRIFT VALUES                                                | 20 |

| 2.5     | INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS                    | 21 |

| 2.6     | POWER BURN-IN CONDITIONS                                              | 21 |

| 2.7     | OPERATING LIFE CONDITIONS                                             | 21 |

| 2.8     | TOTAL DOSE RADIATION TESTING                                          | 21 |

| 2.8.1   | Bias Conditions and Total Dose Level for Total Dose Radiation Testing | 21 |

| 2.8.2   | Electrical Measurements for Total Dose Radiation Testing              | 21 |

| APPEND  | IX A                                                                  | 22 |

#### 1 GENERAL

#### 1.1 <u>SCOPE</u>

This specification details the ratings, physical and electrical characteristics and test and inspection data for the component type variants and/or the range of components specified below. It supplements the requirements of, and shall be read in conjunction with, the ESCC Generic Specification listed under Applicable Documents.

#### 1.2 APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:

- (a) ESCC Generic Specification No. 9000.

- (b) MIL-STD-883, Test Methods and Procedures for Microelectronics.

# 1.3 TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESCC Basic Specification No. 21300 shall apply.

#### 1.4 THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS

#### 1.4.1 The ESCC Component Number

The ESCC Component Number shall be constituted as follows:

Example: 920208501R

Detail Specification Reference: 9202085Component Type Variant Number: 01

• Total Dose Radiation Level Letter: R (as required)

#### 1.4.2 <u>Component Type Variants</u>

The component type variants applicable to this specification are as follows:

| /ariant<br>lumber | Based on Type | Case    | Terminal Finish | Weight<br>max q | Total Dose Radiation<br>Level Letter |

|-------------------|---------------|---------|-----------------|-----------------|--------------------------------------|

| 01                | NOV1G14       | CQFN-32 | 14              | 0.2             | R [100krad(Si)]                      |

The terminal finish shall be in accordance with the requirements of ESCC Basic Specification No. 23500.

The total dose radiation level letter shall be as defined in ESCC Basic Specification No. 22900. If an alternative radiation test level is specified in the Purchase Order the letter shall be changed accordingly.

#### 1.5 MAXIMUM RATINGS

The maximum ratings shall not be exceeded at any time during use or storage.

Maximum ratings shall only be exceeded during testing to the extent specified in this specification and when stipulated in Test Methods and Procedures of the ESCC Generic Specification.

| Characteristics                       | Symbols              | Maximum Ratings       | Units | Remarks                                      |

|---------------------------------------|----------------------|-----------------------|-------|----------------------------------------------|

| V <sub>DDA</sub> Supply Voltage       | $V_{DDA}$            | 0 to 3.5              | V     | Note 1                                       |

| V <sub>DDB</sub> Supply Voltage       | $V_{DDB}$            | 0 to 5.4              | V     | Note 2                                       |

| Input Voltage Range                   | Vin                  | 0 to V <sub>DDA</sub> | V     | Inputs: SPI_*, Reset_ext, Fine_in, Coarse_in |

| Device Power Dissipation (Continuous) | $P_D$                | 2.2                   | W     | Maximum DC power                             |

| Reference Input Power (Continuous)    | P <sub>REF</sub>     | +13                   | dBm   |                                              |

| External RF Input Power (Continuous)  | P <sub>RF</sub>      | +13                   | dBm   |                                              |

| Operating Temperature Range           | Тор                  | -55 to +125           | °C    | T <sub>case</sub> , package backside; Note 3 |

| Storage Temperature Range             | $T_{stg}$            | -65 to +150           | °C    |                                              |

| Junction Temperature                  | Tj                   | +150                  | °C    |                                              |

| Thermal Resistance, Junction to Case  | R <sub>th(j-c)</sub> | 15                    | °C/W  |                                              |

| Soldering Temperature                 | T <sub>sol</sub>     | +260                  | °C    | Note 4                                       |

#### NOTES:

- All voltages are with respect to GND. Device is functional for 3.1V ≤ V<sub>DDA</sub> ≤ 3.5V.

- 2. All voltages are with respect to GND. Device is functional for 4.8V ≤ V<sub>DDB</sub> ≤ 5.4V.

- 3. Device is functional at temperatures between T<sub>case</sub> = -40°C<sup>(\*)</sup> to +85°C.

(\*) Operation below room temperature (see Para. 2.3.1) requires an external 3.5V VCO voltage supply (connection of VCO Ido and VCO Idox via 24O to AMP Ido is recommended; see

- supply (connection of VCO\_ldo and VCO\_ldox via  $24\Omega$  to AMP\_ldo is recommended; see Para. 1.9).

- 4. Duration 10 seconds maximum at a distance of not less than 1.6mm from the device body and the same terminal shall not be re-soldered until 3 minutes have elapsed.

#### 1.6 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are categorised as Class 1 per ESCC Basic Specification No. 23800 with a Minimum Critical Path Failure Voltage of 200 Volts.

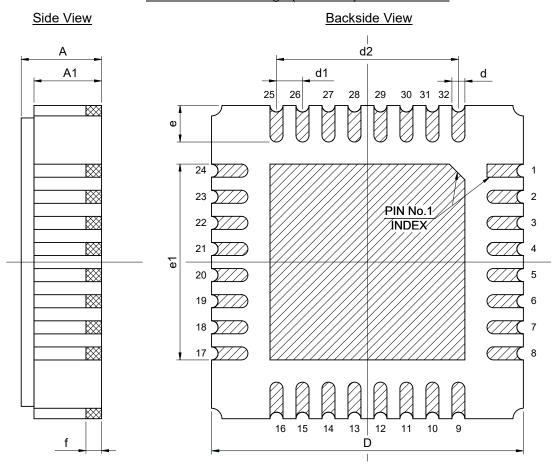

# 1.7 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

# Ceramic Quad Package (CQFN-32) – 32 Terminals

| Symbols | Dimensions (mm) |        | Remarks                                        |

|---------|-----------------|--------|------------------------------------------------|

|         | Min             | Max    |                                                |

| Α       | 1.4             | 1.77   | Overall thickness including soldered lid       |

| A1      | 1.17            | 1.43   | Package thickness without lid                  |

| D       | 5.85 6.2        |        | Overall package width and length (Note 4)      |

| d       | 0.25 TYPICAL    |        | Terminal pad width (Note 2)                    |

| d1      | 0.50 BSC        |        | Terminal pad spacing (Note 3)                  |

| d2      | 3.37            | 3.63   | Overall terminal pad spacing (Notes 2, 4)      |

| е       | 0.70 TYPICAL    |        | Terminal pad length (Note 2)                   |

| e1      | 3.65 3.85       |        | Exposed terminal pad width and length (Note 2) |

| f       | 0.30 T          | /PICAL | Side metallization (Note 2)                    |

#### **NOTES:**

- 1. Terminal identification is specified by reference to the index corner mark on the bottom of the package and the Pin No. 1 index, as shown. Terminal numbers increase counter clockwise if viewed from top of the package.

- 2. Applies to all 32 terminals (8 per side).

- 3. 28 places.

- 4. The overall terminal pad spacing centrelines on each of the 4 sides shall be located within ±0.15mm of the applicable package centreline.

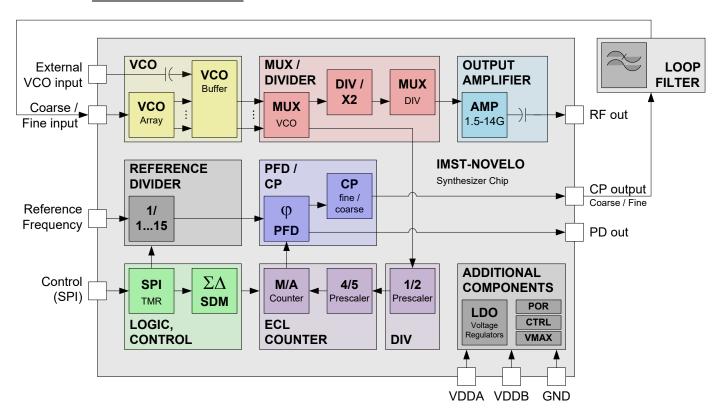

#### 1.8 FUNCTIONAL DIAGRAM

# 1.9 PIN ASSIGNMENT AND DESCRIPTION

The table below describes each pin's assignment, type and standard, plus a brief description of its functionality.

| Pin<br>No. | Pin Name | Pin Type         | Pin<br>Standard<br>(Note 1) | Description                                                                                                                         |

|------------|----------|------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 1          | PD_up    | Output<br>(CMOS) | ESD                         | Phase detection output UP. Turns from HIGH to LOW if reference frequency is ahead of feedback frequency. Maximum load $500\Omega$ . |

| 2          | PD_down  | Output<br>(CMOS) | ESD                         | Phase detection output DOWN. Turns to LOW if feedback frequency is ahead of reference frequency. Maximum load = $500\Omega$ .       |

| 3          | CP_vcc   | Input<br>(Power) | VDD                         | External supply voltage (type V <sub>DDA</sub> , I <sub>max</sub> = 20mA). Note 2.                                                  |

| 4          | CP_ldo   | Output<br>(DC)   | VDD                         | LDO voltage regulator output (+2.7V, generated on-chip).<br>LDOA domain. Note 2.                                                    |

| 5          | REF_in   | Input<br>(CMOS)  | RF                          | External reference clock frequency (100MHz nominal). The input is DC coupled, an external decoupling capacitor (1nF) is necessary.  |

| 6          | SPI_clk  | Input<br>(CMOS)  | ESD                         | Clock for Serial Peripheral Interface (SPI, readout frequency max = 4KHz, write frequency max = 1MHz).                              |

| Pin | Pin Name                    | Pin Type                          | Pin                  | Description                                                                                                                                                                                                                                                                                               |

|-----|-----------------------------|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. |                             | ,,                                | Standard<br>(Note 1) | ·                                                                                                                                                                                                                                                                                                         |

| 7   | SPI_data_in                 | Input<br>(CMOS)                   | ESD                  | SPI data input.                                                                                                                                                                                                                                                                                           |

| 8   | SPI_data_out                | Output<br>(CMOS)                  | ESD                  | SPI data output (low current)                                                                                                                                                                                                                                                                             |

| 9   | Reset_ext                   | Input<br>(CMOS)                   | ESD                  | External reset (LOW active, HIGH at normal operation).                                                                                                                                                                                                                                                    |

| 10  | SPI_enable                  | Input<br>(CMOS)                   | ESD                  | SPI enable (LOW active, HIGH at normal operation).                                                                                                                                                                                                                                                        |

| 11  | LockDetect_A (LockDetect_D) | Output<br>(Output,<br>CMOS)       | ESD                  | Analog PFD lock detect output voltage (0 to 2.5V). (Alternative: Digital lock detect output; also provided via SPI)                                                                                                                                                                                       |

| 12  | CMOS_ldo                    | Output<br>(DC)                    | VDD                  | LDO voltage regulator output (+2.5V, generated on-chip). LDOC domain. Note 2.                                                                                                                                                                                                                             |

| 13  | CMOS_vcc                    | Input<br>(Power)                  | VDD                  | External supply voltage (type $V_{DDA}$ , $I_{max} = 30 \text{mA}$ ). Note 2.                                                                                                                                                                                                                             |

| 14  | CNTR_ldo                    | Output<br>(DC)                    | VDD                  | LDO voltage regulator output (+2.7V, generated on-chip). LDOA domain. Note 2.                                                                                                                                                                                                                             |

| 15  | CNTR_vcc                    | Input<br>(Power)                  | VDD                  | External supply voltage (type V <sub>DDA</sub> , I <sub>max</sub> = 170mA). Note 2.                                                                                                                                                                                                                       |

| 16  | DIV_vcc                     | Input<br>(Power)                  | VDD                  | External supply voltage (type V <sub>DDA</sub> , I <sub>max</sub> = 20mA). Note 2.                                                                                                                                                                                                                        |

| 17  | DIV_ldo                     | Output<br>(DC)                    | VDD                  | LDO voltage regulator output (+2.7V, generated on-chip). LDOA domain. Note 2.                                                                                                                                                                                                                             |

| 18  | VCOx_ldo                    | Output* (DC)  * Input if required | VDD                  | LDO voltage regulator output for VCOs 1, 3, and 5; (+4.0V, generated on-chip*). Supply voltage for VCOx-LDO provided via AMP_vcc. *) Disabled output and external input of 3.5V is required if full temperature range usage is intended (connection via 24Ω to AMP_ldo recommended). LDOB domain. Note 2. |

| 19  | AMP_vcc                     | Input<br>(Power)                  | VDD                  | External supply voltage (type V <sub>DDB</sub> , I <sub>max</sub> = 100mA).  Note 2.                                                                                                                                                                                                                      |

| 20  | AMP_ldo                     | Output<br>(DC)                    | VDD                  | LDO voltage regulator output (+4.0V, generated on-chip). Additional VCO voltage supply possible (3.5V, via $24\Omega$ resistor, connected to VCO_ldo and VCOx_ldo). LDOB domain. Note 2.                                                                                                                  |

| 21  | RF_outN                     | Output                            | RF                   | Differential RF output (N), AC coupled to on-chip voltages, but $1K\Omega$ to GND for ESD protection.                                                                                                                                                                                                     |

| Pin<br>No.  | Pin Name   | Pin Type            | Pin<br>Standard | Description                                                                                                                                                                          |

|-------------|------------|---------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |            |                     | (Note 1)        |                                                                                                                                                                                      |

| 22          | RF_outP    | Output              | RF              | Differential RF output (P), AC coupled to on-chip voltages, but $1K\Omega$ to GND for ESD protection.                                                                                |

|             |            |                     |                 | Single ended output possible, but termination of the unused port via $50\Omega$ load required to avoid RF distribution inside the package.                                           |

| 23          | BUF_ldo    | Output<br>(DC)      | VDD             | LDO voltage regulator output (+2.7V, generated on-chip).<br>LDOA domain. Note 2.                                                                                                     |

| 24          | BUF_vcc    | Input<br>(Power)    | VDD             | External supply voltage (type V <sub>DDA</sub> , I <sub>max</sub> = 30 mA).<br>Note 2.                                                                                               |

| 25          | VCO_vcc    | Input<br>(Power)    | VDD             | External supply voltage (type V <sub>DDB</sub> , I <sub>max</sub> = 30 mA).<br>Note 2.                                                                                               |

| 26          | VCO_extN   | Input               | RF              | Differential external RF input (N),                                                                                                                                                  |

|             |            |                     |                 | AC coupled to on-chip voltages, but $1K\Omega$ to GND for ESD protection. Single ended input with limited functionality. Termination of the unused port with $50\Omega$ recommended. |

| 27          | VCO_extP   | Input               | RF              | Differential external RF input (P),                                                                                                                                                  |

|             |            |                     |                 | AC coupled to on-chip voltages, but $1K\Omega$ to GND for ESD protection. Single ended input with limited functionality. Termination of the unused port with $50\Omega$ recommended. |

| 28          | VCO_ldo    | Output*<br>(DC)     | VDD             | LDO voltage regulator output for VCOs 2, 4, 6, and 7; (+4.0V, generated on-chip*)                                                                                                    |

|             |            | , ,                 |                 | *) Disabled output and external input of 3.5V is required if                                                                                                                         |

|             |            | * Input if required |                 | full temperature range usage is intended (connection via $24\Omega$ to AMP_ldo recommended).                                                                                         |

|             |            | ·                   |                 | LDOA domain. Note 2.                                                                                                                                                                 |

| 29          | Fine_in    | Input               | ESD             | Fine voltage control input for on-chip VCOs (0 to 2.7V). External connection to Fine_out via filter needed.                                                                          |

| 30          | Coarse_in  | Input               | ESD             | Coarse voltage control input for on-chip VCOs (0 to 2.7V). External connection to Fine_out via filter needed.                                                                        |

| 31          | Fine_out   | Output              | ESD             | Fine charge pump output current.                                                                                                                                                     |

| 32          | Coarse_out | Output              | ESD             | Coarse charge pump output current.                                                                                                                                                   |

| Exp.<br>Pad | global_gnd | Ground              | GND             | Exposed ground (GND) pad for DC and RF; Provides good thermal contact for heat dissipation. Note 3                                                                                   |

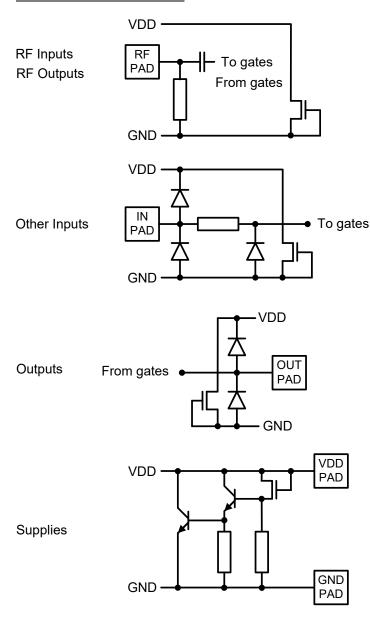

# NOTES:

- 1. Where:

- ESD = ESD protected pins

- VDD = Supply related pins

- RF = RF input/output pins

- 2. The following off-chip shunt capacitors are required to be used at all voltage supply and LDO ports: 100pF, as close as possible to the chip package; 100nF and 2.2μF.

- 3. Power Dissipation of the device is specified in Para. 1.5.

#### 4. The following table below defines the pin groups applied during testing:

| Pin Group<br>No. | Туре                      | Total No.<br>of Pins | Pin Numbers                          |

|------------------|---------------------------|----------------------|--------------------------------------|

| 1                | CMOS Input                | 4                    | 6, 7, 9, 10 (SPI*, Reset_ext)        |

| 2                | Reference Frequency Input | 1                    | 5 (REF_in)                           |

| 3                | RF Input                  | 2                    | 26, 27 (VCO_extN, VCO_extP)          |

| 4                | High Current CMOS Output  | 2                    | 1, 2 (PD_up, PD_down)                |

| 5                | Low Current CMOS Output   | 1                    | 8 (SPI_data_out)                     |

| 6                | RF Output                 | 2                    | 21, 22 (RF_outN, RF_outP)            |

| 7                | DC Supply                 | 7                    | 3, 13, 15, 16, 19, 24, 25 (*vcc)     |

| 8                | DC Regulated Output       | 8                    | 4, 12, 14, 17, 18, 20, 23, 28 (*ldo) |

| 9 (1)            | Charge Pump Outputs       | 2                    | 31, 32 (Coarse_out, Fine_out)        |

| 10 (1)           | Charge Pump Inputs        | 2                    | 29, 30 (Fine_in, Coarse_in)          |

| 11 (1)           | Analog Lock Detect Output | 1                    | 11 (LockDetect*)                     |

| 12 (1)           | Ground                    | 1                    | Exposed pad (global_gnd)             |

<sup>(1)</sup> Included for information only; these pin groups are not included in testing.

#### 1.10 <u>FUNCTIONAL DESCRIPTION</u>

#### 1.10.1 Overview

NOV1G14 is a full functional fractional-N synthesizer. The frequency generation is performed internally, by an array of voltage-controlled oscillators with 7 VCOs covering the frequency range between 6 and 12GHz. By means of RF dividers, the covered frequency range is extended down to 1.6GHz. With limited functionality, this frequency range can be extended to about 14GHz by using an internal times two frequency multiplier. Also, an external RF source can be used for frequency generation.

Via a multiplexer, either the buffered, direct VCO path or the divider/multiplier outputs are connected to the output amplifier. The feedback path with prescaler (divide-by-two circuit) and ECL based 4/5 dual modulus divider in combination with a master and assistant (M/A) counter is fed directly from the VCO multiplexer. The ECL-counter output is connected to a phase frequency detector (PFD), which generates voltage up- and down-pulses depending on the down-divided signal phase compared to the reference frequency phase. The following charge pump (CP) converts these pulses into up- and down-currents, charging external loop filter capacitances. The voltages across the capacitances regulate the VCO output frequency; the loop (PLL) is closed.

The synthesizer can be operated in two modes, integer and fractional. During integer mode, a fixed divider ratio is applied to the divider chain. This way, the output frequency can be adjusted to a multiple of divider ratio and reference frequency (e.g. 2 x 45 x 100MHz = 9GHz). To obtain frequencies smaller than the integer frequency steps, fractional mode is applied. In this case, via a programmable sigma delta modulator (SDM) based on CMOS logic, dynamic changes of the main divider factor N are performed (Gauss distribution). This results in a fractional main divider factor Q with the possibility to access frequencies down to 1 Hz step size at moderate spur and quantization noise levels.

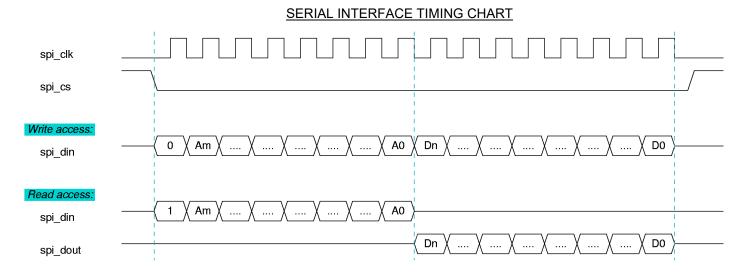

# 1.10.2 Register Programming

In write mode (according to the figure below), the data sent over the SPI starts with a leading '0', followed by the address of the desired control register with 7 bit length. The current status of the register can be read also, with a leading '1' for read access. Each register has a width of two bytes, which leads to a total width of three bytes.

#### **REGISTER MAP**

# Control Registers (address range "0x00" to "0x09"; registers are read-write).

| Address   | Bit  | Name           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                 | Default |

|-----------|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 0x00      | 150  | divisor(35:20) | M/A-counter divisor bits 70, -18                                                                                                                                                                                                                                                                                                                                                                                                         | 0x2D00  |

| Divisor 0 |      |                | Integer divider values between 24 and 255 are possible (default is 45). Fractional digits are programmed via the 28 remaining bits of the three divisor registers. The M/A settings are calculated from the programmable integer divider value D with: $D = 5A + 4(M + 1 - A) \text{ and } A \leq M + 1$ A is calculated from the two LSB of D (max 3). For example, results the default divider setting with D = 45 in M = 10 and A = 1 |         |

| 0x01      | 150  | divisor(19:4)  | Divisor bits -924                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x0000  |

| Divisor 1 |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 0x02      | 1512 | divisor(3:0)   | Divisor bits -2528                                                                                                                                                                                                                                                                                                                                                                                                                       | "0000"  |

| Divisor 2 | 110  | unused         |                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| Address | Bit  | Name          | Function                                                                                                                | Default |

|---------|------|---------------|-------------------------------------------------------------------------------------------------------------------------|---------|

| 0x03    | 158  | unused        |                                                                                                                         |         |

| Config  | 7    | reset_sd      | Low-active reset for Sigma Delta Modulator (SDM). "0" integer mode, fixed divider ratio;                                | "0"     |

|         |      |               | "1" fractional mode                                                                                                     |         |

|         | 65   | sd_mux        | Number of SDM accumulator stages:                                                                                       | "00"    |

|         |      |               | "00" 1 stage, "01" 2 stages, "10" 3 stages, "11" 4 stages.  Example: 3 stages lead to a max. divider ratio variation of |         |

|         |      |               | 8 (23; from -3 to +4) around the integer part of the divisor                                                            |         |

|         | 4    | ref_div_      | Enable for reference clock bypass switch                                                                                | "0"     |

|         |      | bypass_en     |                                                                                                                         |         |

|         | 30   | ref_div_ctrl  | Divisor for reference clock divider (015).                                                                              | "0000"  |

|         |      |               | "0" activates the divider bypass within the reference divider. "1" divides by one.                                      |         |

| 0x04    | 150  | preload       | Preloads first accumulator bits -116                                                                                    | 0x0000  |

| Preload |      |               |                                                                                                                         |         |

| 0x05    | 1514 | unused        |                                                                                                                         |         |

| CP      | 1312 | cp_test       | Test modus for charge pump currents.                                                                                    | "00"    |

|         |      |               | PFD switched to constant outputs.                                                                                       |         |

|         |      |               | "00" Test mode disabled                                                                                                 |         |

|         |      |               | "01" UP current and PD_up active                                                                                        |         |

|         |      |               | "10" DOWN current and PD_down active                                                                                    |         |

|         |      |               | "11" UP and DOWN activated                                                                                              |         |

|         | 11   | cp_fine_en    | Enable for charge pump fine current                                                                                     | "1"     |

|         | 10   | cp_coarse_en  | Enable for charge pump coarse current                                                                                   | "1"     |

|         |      |               | Coarse charge current is 500µA                                                                                          |         |

|         | 95   | cp_fine       | Charge pump fine current (lcpf ) settings.                                                                              | "01000" |

|         |      |               | Binary addition of 8mA (MSB), 4mA, 2mA, 1mA,                                                                            |         |

|         |      |               | 500μA (LSB)                                                                                                             |         |

|         | 40   | unused        |                                                                                                                         |         |

| 0x06    | 1510 | unused        |                                                                                                                         |         |

| Offset  | 95   | offset_fine   | Fine offset current adjustment                                                                                          | "00001" |

|         |      |               | losf = n*lcpf/50; n 031                                                                                                 |         |

|         | 40   | offset_coarse | Coarse offset current setting losc = n*100µA; n 031                                                                     | "00001" |

| 0x07    | 158  | unused        |                                                                                                                         |         |

| VCO     | 7    | ldo_vco_en    | Enable for VCO LDO                                                                                                      | "1"     |

|         | 63   | vco_band_ctrl | Band selection for internal VCO arrays.                                                                                 | "0001"  |

|         |      |               | In the current configuration, 8 bands are used from "0000" (lowest) to "0111" (highest).                                |         |

|         | 20   | vco_ctrl      | VCO control. "001" to "111" enables internal VCOs 1-7. "0" enables external VCO path                                    | "110"   |

| Address | Bit  | Name                   | Function                                                                                                                                                                                                              | Default |

|---------|------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 80x0    | 1512 | unused                 |                                                                                                                                                                                                                       |         |

| 8 7     | 119  | div_path_en            | Enable for 1 out of 7 divider paths or none "000". Selectable paths: "001" direct path, "010" divide by 2, "011" divide by 4 and "100" multiply by 2                                                                  | "001"   |

|         | 8    | lock_detect_<br>dig_en | Enable for digital lock detect output                                                                                                                                                                                 | "0"     |

|         | 7    | lock_detect_<br>ana_en | Enable for analog lock detect buffer                                                                                                                                                                                  | "0"     |

|         | 6    | ldo_div_en             | Enable for pre-divider and RF divider chain LDO                                                                                                                                                                       | "1"     |

|         | 5    | ldo_buf_en             | Enable for VCO output chain LDO                                                                                                                                                                                       | "1"     |

|         | 4    | ldo_amp_en             | Enable for output power amplifier LDO                                                                                                                                                                                 | "1"     |

|         | 3    | pfd_vout_en            | Enable for external PD up/down voltage output                                                                                                                                                                         | "0"     |

|         | 2    | pfd_en                 | Enable for PFD                                                                                                                                                                                                        | "1"     |

|         | 1    | div_fb_en              | Enable for feedback clock pre-divider                                                                                                                                                                                 | "1"     |

|         | 0    | clk_fb_out_en          | Enable for feedback clock test output (optional)                                                                                                                                                                      | "0"     |

| 0x09    | 158  | unused                 | General purpose outputs with default "1"                                                                                                                                                                              | "1"     |

| GPO     | 73   | unused                 | General purpose outputs with default "0"                                                                                                                                                                              | "0"     |

|         | 2    | rf_mode                | RF mode enable for output amplifier                                                                                                                                                                                   | "0"     |

|         | 1    | ecl_thres_ctrl         | M-counter related threshold to define the feedback clock duty cycle (4 or 2 counter periods on 'HIGH'). "0" threshold 4 (min. div. ratio 32, consider SDM state). "1" enables T2 (needed for divider ratios below 32) | "0"     |

|         | 0    | ecl_ctrl_en            | Enable for ECL counter                                                                                                                                                                                                | "0"     |

# Status Registers (address range "0x40" to "0x41"; registers are read-only).

| Address | Bit | Name        | Function               | Default |

|---------|-----|-------------|------------------------|---------|

| 0x40    | 159 | Unused      |                        |         |

| Status  | 8   | lock_detect | PLL lock detect        | "1"     |

|         | 74  | version     | Version number (1)     | "0001"  |

|         | 30  | subversion  | Subversion number (5)  | "0101"  |

| 0x41    | 150 | Unused      | General-purpose inputs |         |

| GPI_reg |     |             |                        |         |

# 1.11 PROTECTION NETWORKS

# 2 **REQUIREMENTS**

# 2.1 GENERAL

The complete requirements for procurement of the components specified herein are as stated in this specification and the ESCC Generic Specification. Permitted deviations from the Generic Specification, applicable to this specification only, are listed below.

Permitted deviations from the Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESCC requirement and do not affect the component's reliability, are listed in the appendices attached to this specification.

# 2.1.1 <u>Deviations from the Generic Specification</u>

#### 2.1.1.1 Deviations from Screening Tests - Chart F3

(a) High Temperature Reverse Bias Burn-in and the subsequent Final Measurements for HTRB Burn-in shall be omitted.

# 2.2 MARKING

The marking shall be in accordance with the requirements of ESCC Basic Specification No. 21700 and as follows.

As a minimum the information to be marked on the component or the primary package shall be:

- (a) The ESCC qualified components symbol (for ESCC qualified components only).

- (b) The ESCC Component Number (see Para. 1.4.1).

- (c) Traceability information.

#### 2.3 ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES

Electrical measurements shall be performed at room, high and low temperatures.

# 2.3.1 Room Temperature Electrical Measurements

The measurements shall be performed at  $T_{case} = +22 \pm 3$ °C.

| Characteristics                            | Symbols          | MIL-STD-883 | Test Conditions                                                                      | Limits |     | Units      |

|--------------------------------------------|------------------|-------------|--------------------------------------------------------------------------------------|--------|-----|------------|

|                                            |                  | Test Method |                                                                                      | Min    | Max |            |

| V <sub>DDA</sub> Dynamic Supply<br>Current | I <sub>DDA</sub> | 3005        | Pin Group 7, Note 1<br>V <sub>DDA</sub> = 3.5V, V <sub>DDB</sub> =<br>5.4V, GND = 0V | 1      | 300 | mA         |

| V <sub>DDB</sub> Dynamic Supply<br>Current | I <sub>DDB</sub> | 3005        | Pin Group 7, Note 1<br>V <sub>DDA</sub> = 3.5V, V <sub>DDB</sub> =<br>5.4V, GND = 0V | -      | 200 | mA         |

| V <sub>DDA</sub> Standby Supply<br>Current | Iddaq            | 3005        | Pin Group 7, Note 2<br>V <sub>DDA</sub> = 3.5V, V <sub>DDB</sub> =<br>5.4V, GND = 0V | -      | 50  | mA         |

| V <sub>DDB</sub> Standby Supply<br>Current | IDDBQ            | 3005        | Pin Group 7, Note 2<br>V <sub>DDA</sub> = 3.5V, V <sub>DDB</sub> =<br>5.4V, GND = 0V | -      | 10  | m <b>A</b> |

| Characteristics                                                   | Symbols             | MIL-STD-883 | Test Conditions                                                                       | Limits |       | Units |

|-------------------------------------------------------------------|---------------------|-------------|---------------------------------------------------------------------------------------|--------|-------|-------|

|                                                                   |                     | Test Method |                                                                                       | Min    | Max   |       |

| Functional Test,<br>Typical Voltage<br>(Relaxed Limits)           | -                   | 3014        | V <sub>DDA</sub> = 3.3V, Note 3<br>V <sub>DDB</sub> = 5.1V, GND = 0V                  | Go/N   | No-Go | -     |

| Functional Test,<br>Minimum Voltage<br>(Specified Limits)         | -                   | 3014        | $V_{DDA} = 3.1V$ , Note 3<br>$V_{DDB} = 4.8V$ , GND = 0V                              | Go/N   | No-Go | -     |

| Functional Test,<br>Maximum Voltage<br>(Specified Limits)         | -                   | 3014        | $V_{DDA} = 3.5V$ , Note 3<br>$V_{DDB} = 5.4V$ , GND = 0V                              | Go/N   | No-Go | -     |

| LDO Minimum Voltage<br>Test (LDOA Domain)                         | V <sub>LLDOAx</sub> | -           | Pin Group 8, Note 4,<br>V <sub>DDA</sub> = 3.1V, V <sub>DDB</sub> =<br>4.8V, GND = 0V | 2.6    | 2.8   | V     |

| LDO Maximum Voltage<br>Test (LDOA Domain)                         | VHLDOAx             | -           | Pin Group 8, Note 4,<br>V <sub>DDA</sub> = 3.5V, V <sub>DDB</sub> =<br>5.4V, GND = 0V | 2.6    | 2.8   | V     |

| LDO Minimum Voltage<br>Test (LDOB Domain)                         | V <sub>LLDOBx</sub> | -           | Pin Group 8, Note 4,<br>V <sub>DDA</sub> = 3.1V, V <sub>DDB</sub> =<br>4.8V, GND = 0V | 3.9    | 4.1   | V     |

| LDO Maximum Voltage<br>Test (LDOB Domain)                         | VHLDOBX             | -           | Pin Group 8, Note 4,<br>V <sub>DDA</sub> = 3.5V, V <sub>DDB</sub> =<br>5.4V, GND = 0V | 3.9    | 4.1   | V     |

| LDO Minimum Voltage<br>Test (LDOC Domain)                         | VLLDOCX             | -           | Pin Group 8, Note 4,<br>V <sub>DDA</sub> = 3.1V, V <sub>DDB</sub> =<br>4.8V, GND = 0V | 2.4    | 2.6   | V     |

| LDO Maximum Voltage<br>Test (LDOC Domain)                         | VHLDOCx             | -           | Pin Group 8, Note 4,<br>V <sub>DDA</sub> = 3.5V, V <sub>DDB</sub> =<br>5.4V, GND = 0V | 2.4    | 2.6   | V     |

| CMOS Min. Input<br>Voltage, Low Level<br>(Min V <sub>DDA</sub> )  | VILSPI              | -           | Pin Group 1, Note 5<br>V <sub>DDA</sub> = 3.1 V, GND = 0V                             | 2.5    | -     | V     |

| CMOS Min. Input<br>Voltage, High Level<br>(Max V <sub>DDA</sub> ) | V <sub>IHSPI</sub>  | -           | Pin Group 1, Note 5<br>V <sub>DDA</sub> = 3.5 V, GND = 0V                             | 2.5    | -     | V     |

| CMOS SPI Clock Maximum Input Frequency (SPI_clk)                  | f <sub>HSPIR</sub>  | -           | Read                                                                                  | -      | 3     | kHz   |

| CMOS SPI Clock<br>Maximum Input<br>Frequency (SPI_clk)            | f <sub>HSPIW</sub>  | -           | Write                                                                                 | -      | 1     | MHz   |

| CMOS Output Voltage,<br>High Level (High Current<br>Buffer)       | VOHPFD              | 3006        | Pin Group 4, Note 6                                                                   | 2.25   | -     | V     |

| Characteristics                                    | Symbols            | MIL-STD-883 | Test Conditions                                    | Lin  | Units |        |

|----------------------------------------------------|--------------------|-------------|----------------------------------------------------|------|-------|--------|

|                                                    |                    | Test Method |                                                    | Min  | Max   |        |

| Analog Lock Detect<br>Voltage                      | -                  | 3014        | Note 3                                             | Go/N | No-Go | -      |

| Reference Clock Input<br>Sensitivity (Min. Power)  | P <sub>LREF</sub>  | -           | Pin Group 2, Note 7<br>f <sub>INREF</sub> = 105MHz | -12  | -     | dBm    |

| External RF Input<br>Sensitivity (Min. Power)      | PLEXTL             | -           | Pin Group 3, Note 8<br>f <sub>EXT</sub> = 6.0GHz   | -    | -15   | dBm    |

| External RF Input<br>Sensitivity (Min. Power)      | P <sub>LEXTN</sub> | -           | Pin Group 3, Note 8<br>f <sub>EXT</sub> = 9.8GHz   | -    | -10   | dBm    |

| External RF Input<br>Sensitivity (Min. Power)      | P <sub>LEXTH</sub> | -           | Pin Group 3, Note 8<br>f <sub>EXT</sub> = 12.0GHz  | -    | -5    | dBm    |

| External RF Input<br>Frequency<br>(Min. Frequency) | f <sub>LEXT</sub>  | -           | Pin Group 3, Note 8 PEXT = -15dBm                  | 6.0  | -     | GHz    |

| External RF Input<br>Frequency<br>(Max. Frequency) | f <sub>HEXT</sub>  | -           | Pin Group 3, Note 8 PEXT = -5dBm                   | -    | 12.0  | GHz    |

| RF Output<br>(Min. Frequency)                      | fьоит              | -           | Pin Group 6, Note 9                                | 1.6  | -     | GHz    |

| RF Output<br>(Max. Frequency)                      | f <sub>ноит</sub>  | -           | Pin Group 6, Note 9                                | -    | 12.0  | GHz    |

| RF Output<br>(Min. Frequency Overlap)              | f <sub>DOUT</sub>  | -           | Pin Group 6, Note 9<br>fout = 6.0 to 12.0GHz       | 8    | -     | MHz    |

| RF Output (Min. Power)                             | PLOUT              | -           | Pin Group 6, Note 9<br>fout = 1.6 to 12.0GHz       | -10  | -     | dBm    |

| Phase Noise at 1kHz<br>Offset                      | PN <sub>1K</sub>   | -           | Pin Group 6, Note 10 fout = 9.8GHz                 | -    | -87   | dBc/Hz |

| Phase Noise at 10kHz<br>Offset                     | PN <sub>10K</sub>  | -           | Pin Group 6, Note 10 fout = 9.8GHz                 | -    | -92   | dBc/Hz |

| Phase Noise at 100kHz<br>Offset                    | PN <sub>100K</sub> | -           | Pin Group 6, Note 10 fout = 9.8GHz                 | -    | -98   | dBc/Hz |

| Phase Noise at 1MHz<br>Offset                      | PN <sub>1M</sub>   | -           | Pin Group 6, Note 10 fout = 9.8GHz                 | -    | -110  | dBc/Hz |

| Phase Noise at 10MHz<br>Offset                     | PN <sub>10M</sub>  | -           | Pin Group 6, Note 10 fout = 9.8GHz                 | -    | -130  | dBc/Hz |

# **NOTES:**

- 1. Dynamic current: For measurement of the dynamic current, supply voltages are set to maximum

- 2. Standby current: During standby current test, on-chip LDOs and ECL are set to off-mode.

- 3. Functional test: During functional test, synthesizer is programmed in typical operation mode.

- 4. LDO voltage output test: Output voltage of each LDO is measured. The measurement accuracy shall be better than 50mV.

- Input voltages: Maximum SPI input voltage according to applied V<sub>DDA</sub> voltage. Tests of read/write at the given minimum SPI input voltage shall be performed at the given minimum frequencies. During this test, the complete pin group 1 is tested and the resulting voltage values shall be recorded.

- 6. PFD output voltages: Output voltage tested at maximum output load (500 $\Omega$ ). During measurements, output voltage shall be monitored and recorded.

- REF measurements: Nominal reference frequency is 100MHz. During the reference frequency input test, the synthesizer is programmed at minimum power level and frequency above nominal.

- 8. External RF input: Measurement in differential mode. Monitoring of the divided frequency output signal.

- 9. RF measurements: Test on internal VCO array and the VCO sub-bands. Single ended measurement of output power and frequency for the main octave and the divided output signal at RF<sub>OUTN</sub>. RF<sub>OUTP</sub> terminated by 50Ω and connected to on-board power detect diode. Frequency overlap versus adjacent bands is determined by measuring the low and high corner of each VCO sub-band. Measurement accuracy shall be better than 100KHz and 1dB.

- Phase Noise measurements: Phase Noise measurements shall be performed at 9.8GHz (single sideband), reference frequency input set to 100MHz and 13dBm, with individual charge pump settings.

#### 2.3.2 <u>High and Low Temperatures Electrical Measurements</u>

The measurements shall be performed at  $T_{case} = +85 (+0.5)^{\circ}C$  and  $T_{case} = -40 (+5.0)^{\circ}C$ .

The characteristics, test methods, conditions and limits shall be the same as specified in Para. 2.3.1, Room Temperature Electrical Measurements, except as follows:

| Characteristics                                              | Symbols            | Test Conditions                                                                                              |     | Limits |     |

|--------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------|-----|--------|-----|

|                                                              |                    | (Note 1)                                                                                                     | Min | Max    |     |

| External RF Input Sensitivity (Min. Power)                   | PLEXTL             | As per Para. 2.3.1                                                                                           | -   | -10    | dBm |

| External RF Input Sensitivity (Min. Power)                   | PLEXTN             | As per Para. 2.3.1                                                                                           | -   | 0      | dBm |

| External RF Input Sensitivity (Min. Power)                   | PLEXTH             | As per Para. 2.3.1                                                                                           | -   | 10     | dBm |

| RF Output<br>(Frequency Overlap fout at<br>Low Temperature)  | f <sub>LTOUT</sub> | Pin Group 6, As per Para. 2.3.1<br>fout = 6.0 to 12.0GHz, T <sub>case</sub> = -40°C<br>Note 2                | 4   | -      | MHz |

| RF Output<br>(Frequency Overlap fout at<br>High Temperature) | fнтоит             | Pin Group 6, As per Para. 2.3.1 f <sub>OUT</sub> = 6.0 to 12.0GHz, T <sub>case</sub> = +85°C                 | 4   | -      | MHz |

| RF Output<br>(Frequency Overlap fоит<br>Delta Temperature)   | f <sub>DTOUT</sub> | Pin Group 6, As per Para. 2.3.1 fout = 6.0 to 12.0GHz, between T <sub>case</sub> = -40 and +85°C, Notes 2, 3 | 4   | -      | MHz |

| Characteristics             | Symbols | Test Conditions                                        | Lin | nits | Units |

|-----------------------------|---------|--------------------------------------------------------|-----|------|-------|

|                             |         | (Note 1)                                               | Min | Max  |       |

| RF Output (Min. Power fou⊤) | Рьтоит  | Pin Group 6, As per Para. 2.3.1                        | -20 | -    | dBm   |

|                             |         | $f_{OUT}$ = 1.6 to 12.0GHz, $T_{case}$ = +85°C, Note 4 |     |      |       |

## **NOTES:**

- 1. RF output frequency and phase noise measurements: Measurement procedure for temperature-based RF measurements will be identical to the measurements in Para. 2.3.1.

- 2. See Para. 1.5 Note 3.

- 3. Temperature range frequency overlap: Overlap calculation is based on frequency measurements at high and low temperature corners ( $T_{case} = -40$  and  $+85^{\circ}$ C). Worst case frequency overlap is calculated from measurement results of adjacent bands (maximum vs. minimum frequency) at opposite temperature corners.

- 4. RF power measurements: Worst case at maximum frequency in combination with high temperature.

#### 2.4 PARAMETER DRIFT VALUES

Unless otherwise specified, the parameter drift value measurements shall be performed at  $T_{case}$  = +22 ±3°C.

The test methods and test conditions shall be as per the corresponding test defined in Para. 2.3.1 Room Temperature Electrical Measurements.

The drift values ( $\Delta$ ) shall not be exceeded for each characteristic specified. The corresponding absolute limit values for each characteristic shall not be exceeded.

| Characteristics                         | Symbols             | Limits     |      |      | Units |

|-----------------------------------------|---------------------|------------|------|------|-------|

|                                         |                     | Drift      | Abs  |      |       |

|                                         |                     | Value<br>Δ | Min  | Max  |       |

| V <sub>DDA</sub> Dynamic Supply Current | I <sub>DDA</sub>    | ±70        | -    | 300  | mA    |

| V <sub>DDB</sub> Dynamic Supply Current | I <sub>DDB</sub>    | ±70        | 1    | 200  | mA    |

| LDO Minimum Voltage Test (LDOA Domain)  | $V_{LLDOAx}$        | ±100       | 2600 | 2800 | mV    |

| LDO Maximum Voltage Test (LDOA Domain)  | $V_{HLDOAx}$        | ±100       | 2600 | 2800 | mV    |

| LDO Minimum Voltage Test (LDOB Domain)  | $V_{LLDOBx}$        | ±100       | 3900 | 4100 | mV    |

| LDO Maximum Voltage Test (LDOB Domain)  | $V_{\text{HLDOBx}}$ | ±100       | 3900 | 4100 | mV    |

| LDO Minimum Voltage Test (LDOC Domain)  | V <sub>LLDOCx</sub> | ±100       | 2400 | 2600 | mV    |

| LDO Maximum Voltage Test (LDOC Domain)  | V <sub>HLDOCx</sub> | ±100       | 2400 | 2600 | mV    |

# 2.5 <u>INTERMEDIATE AND END-POINT E</u>LECTRICAL MEASUREMENTS

Unless otherwise specified, the measurements shall be performed at  $T_{case}$  = +22 ±3°C.

The characteristics, test methods, conditions and limits shall be the same as specified in Para. 2.3.1, Room Temperature Electrical Measurements.

#### 2.6 POWER BURN-IN CONDITIONS

| Characteristics                 | Symbols           | Test Conditions       | Units |

|---------------------------------|-------------------|-----------------------|-------|

| Ambient Temperature             | T <sub>case</sub> | +125 (+0 -5) (Note 1) | °C    |

| V <sub>DDA</sub> Supply Voltage | $V_{DDA}$         | 3.3 (±5%)             | V     |

| V <sub>DDB</sub> Supply Voltage | $V_{DDB}$         | 5.1 (±5%)             | V     |

| Operating Conditions            | -                 | See Note 2            | -     |

#### NOTES:

- 1.  $T_{amb}$  shall be adjusted to achieve  $T_{case} = +125$ °C. Additional variation of  $T_{case}$  by  $\pm 2$ °C due to varying sockets,  $R_{th}$  and DUT power dissipation, is permitted.

- 2. During Power Burn-in using a suitable test set-up, the components shall be connected to the supply voltages, and programmed with a typical operation mode. The overall current consumption shall be traced. For verification of component functionality, monitoring of register settings and the equivalent DC voltage level of the RF output power (1.6GHz) shall be performed during testing, on all components.

#### 2.7 OPERATING LIFE CONDITIONS

The conditions shall be as specified in Para. 2.6 for Power Burn-in.

# 2.8 TOTAL DOSE RADIATION TESTING

# 2.8.1 Bias Conditions and Total Dose Level for Total Dose Radiation Testing

Bias shall be applied during irradiation testing as specified below.

The total dose level applied shall be as specified in Para. 1.4.2 or in the Purchase Order.

In unbiased condition (OFF), all component inputs related to the two supply voltage domains ( $V_{DDA}$ ,  $V_{DDB}$ ) will be short-circuited to ground (GND).

In biased condition (ON), using a suitable test set-up, the components shall be connected to the voltage supplies, and programmed with a typical operation mode. Functionality during the test shall be verified by monitoring the RF outputs of the components.

#### 2.8.2 <u>Electrical Measurements for Total Dose Radiation Testing</u>

Prior to irradiation testing the devices shall have successfully met Para. 2.3.1, Room Temperature Electrical Measurements specified herein.

Unless otherwise stated the measurements shall be performed at  $T_{case}$  = +22 ±3°C.

The characteristics, test methods, conditions and limits to be measured during and on completion of irradiation testing shall be the same as specified in Para. 2.3.1, Room Temperature Electrical Measurements.

# <u>APPENDIX A</u> AGREED DEVIATIONS FOR IMST GmbH (D)

| ITEMS AFFECTED                                                             | DESCRIPTION OF DEVIATIONS                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Para. 2.1.1 Deviations from the Generic Specification                      | Qualification and Qualification Maintenance Requirements on a Manufacturer: Single Phase Qualification (SPQ): Component Assessment: Package Assessment: For information, Mounting Capability test conditions and results for the Novelo CQFN-32 package are given in the IMST Document No. 63.1504.017.66NOT, issue C     |

|                                                                            | Test summary: PCB: 4 layers, Thickness 788µm; CTE RT Duorid 6002: 16ppm/K; CTE Component: 7.7 ppm/K.  Thermal Cycling performed from -40°C to 100°C; 400 cycles successfully passed.                                                                                                                                      |

| Para. 2.8.2 Electrical<br>Measurements for Total<br>Dose Radiation Testing | Electrical measurements during irradiation testing, at intermediate points and at the end of exposure, may be performed on selected characteristics.  Note: On completion of irradiation testing, final electrical measurements as specified in Para. 2.3.1, Room Temperature Electrical Measurements shall be performed. |