Page i

# INTEGRATED CIRCUITS, MONOLITHIC, SILICON ON SAPPHIRE, CMOS VIRTUAL CHANNEL ASSEMBLER, BASED ON TYPE 12399 ESCC Detail Specification No. 9544/005

# ISSUE 1 October 2002

#### **ESCC Detail Specification**

| PAGE  | ii |

|-------|----|

| ISSUE | 1  |

#### **LEGAL DISCLAIMER AND COPYRIGHT**

European Space Agency, Copyright © 2002. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or allleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Ageny and provided that it is not used for a commercial purpose, may be:

- copied in whole in any medium without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

# european space agency agence spatiale européenne

Pages 1 to 85

INTEGRATED CIRCUITS, MONOLITHIC,

SILICON ON SAPPHIRE, CMOS VIRTUAL

CHANNEL ASSEMBLER,

BASED ON TYPE 12399

ESA/SCC Detail Specification No. 9544/005

# space components coordination group

|              |                | Approved by   |                                       |

|--------------|----------------|---------------|---------------------------------------|

| Issue/Rev.   | Date           | SCCG Chairman | ESA Director General or his Deputy    |

| Issue 1      | September 1995 | Ponomical     | Hoom                                  |

| Revision 'A' | January 1997   | Sannott       | Alor                                  |

|              |                |               | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

|              |                |               |                                       |

Rev. 'A'

PAGE 2 ISSUE 1

# **DOCUMENTATION CHANGE NOTICE**

|                | DOCUMENTATION CHANGE NOTICE |                                                                                                  |                                                                                                                                                                                                       |                                                                  |

|----------------|-----------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Rev.<br>Letter | Rev.<br>Date                | Reference                                                                                        | CHANGE<br>Item                                                                                                                                                                                        | Approved DCR No.                                                 |

| 'A'            | Jan. '97                    | P1. Cover page P2. DCN P4. T of C P5. Para. 1.1 P67. Figure 5(b) P77. Figure 6 P84. Appendix 'A' | : Part Number amended : Appendix 'A' entry amended : In the first sentence, Part Number amended : Part Number amended : Part Number amended : Title amended : For Para. 4.2.3 entry, Item "(b)" added | 221376<br>None<br>221376<br>221376<br>221376<br>221376<br>221376 |

PAGE 3

ISSUE 1

# **TABLE OF CONTENTS**

| 1.    | GENERAL                                                               | <u>Page</u> <b>5</b> |

|-------|-----------------------------------------------------------------------|----------------------|

| 1.1   | Scope                                                                 | 5                    |

| 1.2   | Component Type Variants                                               | 5                    |

| 1.3   | Maximum Ratings                                                       | 5                    |

| 1.4   | Parameter Derating Information                                        | 5                    |

| 1.5   | Physical Dimensions                                                   | 5                    |

| 1.6   | Pin Assignment                                                        | 5                    |

| 1.7   | Truth Table                                                           | 5                    |

| 1.8   | Circuit Description                                                   | 5                    |

| 1.9   | Functional Diagram                                                    | 5                    |

| 1.10  | Handling Precautions                                                  | 5                    |

| 1.11  | Input/Output Protection Networks                                      | 5                    |

| 2.    | APPLICABLE DOCUMENTS                                                  | 27                   |

| 3.    | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS                  | 27                   |

| 4.    | REQUIREMENTS                                                          | 27                   |

| 4.1   | General                                                               | 27                   |

| 4.2   | Deviations from Generic Specification                                 | 27                   |

| 4.2.1 | Deviations from Special In-process Controls                           | 27                   |

| 4.2.2 | Deviations from Final Production Tests                                | 27                   |

| 4.2.3 | Deviations from Burn-in and Electrical Measurements                   | 27                   |

| 4.2.4 | Deviations from Qualification Tests                                   | 27                   |

| 4.2.5 | Deviations from Lot Acceptance Tests                                  | 27                   |

| 4.3   | Mechanical Requirements                                               | 28                   |

| 4.3.1 | Dimension Check                                                       | 28                   |

| 4.3.2 | Weight                                                                | 28                   |

| 4.3.3 | Terminal Strength                                                     | 28                   |

| 4.4   | Materials and Finishes                                                | 28                   |

| 4.4.1 | Case                                                                  | 28                   |

| 4.4.2 | Lead Material and Finish                                              | 28                   |

| 4.5   | Marking                                                               | 28                   |

| 4.5.1 | General                                                               | 28                   |

| 4.5.2 | Lead Identification                                                   | 28                   |

| 4.5.3 | The SCC Component Number                                              | 29                   |

| 4.5.4 | Traceability Information                                              | 29                   |

| 4.6   | Electrical Measurements                                               | 29                   |

| 4.6.1 | Electrical Measurements at Room Temperature                           | 29                   |

| 4.6.2 | Electrical Measurements at High and Low Temperatures                  | 29                   |

| 4.6.3 | Circuits for Electrical Measurements                                  | 29                   |

| 4.7   | Burn-in Tests                                                         | 29                   |

| 4.7.1 | Parameter Drift Values                                                | 29                   |

| 4.7.2 | Conditions for H.T.R.B. Burn-in                                       | 29                   |

| 4.7.3 | Conditions for Power Burn-in                                          | 29                   |

| 4.7.4 | Electrical Circuits for H.T.R.B. Burn-in                              | 29                   |

| 4.7.5 | Electrical Circuits for Power Burn-in                                 | 29                   |

| 4.8   | Environmental and Endurance Tests                                     | 68                   |

| 4.8.1 | Electrical Measurements on Completion of Environmental Tests          | 68                   |

| 4.8.2 | Electrical Measurements at Intermediate Points during Endurance Tests | 68                   |

| 4.8.3 | Electrical Measurements on Completion of Endurance Tests              | 68                   |

Rev. 'A'

PAGE 4

ISSUE 1

| 404            | Conditions for Operation Life Tests                                                       | Page 00  |

|----------------|-------------------------------------------------------------------------------------------|----------|

| 4.8.4<br>4.8.5 | Conditions for Operating Life Tests                                                       | 68       |

| 4.8.6          | Electrical Circuits for Operating Life Tests Conditions for High Temperature Storage Test | 68<br>68 |

| 4.0.0          | Total Dose Irradiation Testing                                                            | 68       |

| 4.9.1          | Application                                                                               | 68       |

| 4.9.2          | Bias Conditions                                                                           | 68       |

| 4.9.3          | Electrical Measurements                                                                   | 68       |

| TABLI          | <u>ES</u>                                                                                 |          |

| 1(a)           | Type Variants                                                                             | 6        |

| 1(b)           | Maximum Ratings                                                                           | 6        |

| 2              | Electrical Measurements at Room Temperature - d.c. Parameters                             | 30       |

|                | Electrical Measurements at Room Temperature - a.c. Parameters                             | 35       |

| 3(a)           | Electrical Measurements at High Temperature - d.c. Parameters                             | 40       |

| - 4 \          | Electrical Measurements at High Temperature - a.c. Parameters                             | 45       |

| 3(b)           | Electrical Measurements at Low Temperature - d.c. Parameters                              | 50       |

|                | Electrical Measurements at Low Temperature - a.c. Parameters                              | 55       |

| 4              | Parameter Drift Values                                                                    | 64       |

| 5(a)           | Conditions for High Temperature Reverse Bias Burn-in                                      | 65       |

| 5(b)           | Conditions for Power Burn-in and Operating Life Tests                                     | 65       |

| 6              | Electrical Measurements on Completion of Environmental Tests and                          | 69       |

| 7              | at Intermediate Points and on Completion of Endurance Testing                             | 70       |

|                | Electrical Measurements During and on Completion of Irradiation Testing                   | 78       |

| FIGUE          | <u>RES</u>                                                                                |          |

| 1              | Parameter Derating Information                                                            | 6        |

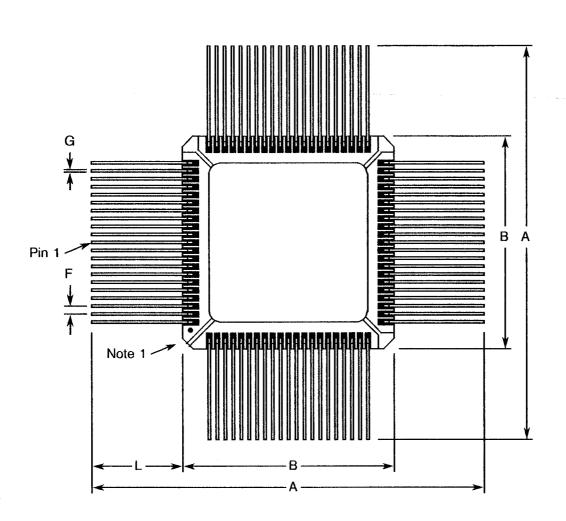

| 2(a)           | Physical Dimensions                                                                       | 7        |

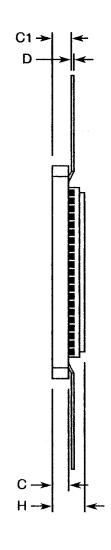

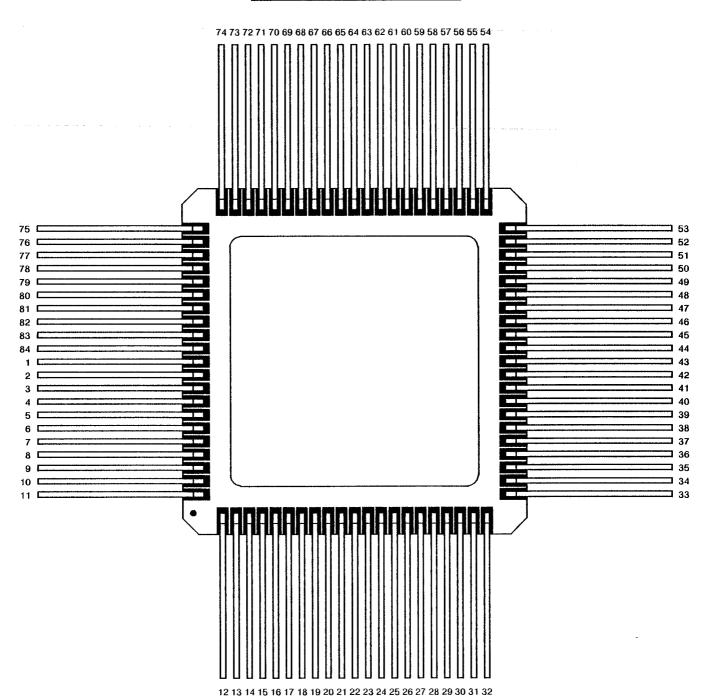

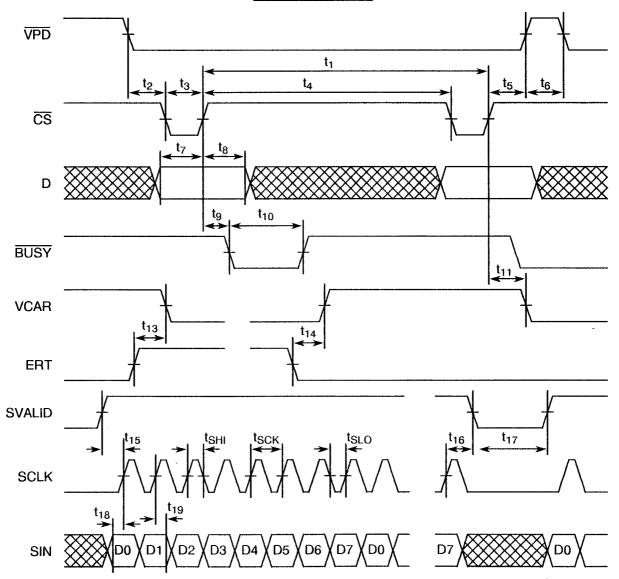

| 3(a)<br>3(b)   | Pin Assignment<br>Truth Table                                                             | 9<br>12  |

| 3(c)           | Circuit Description                                                                       | 14       |

| 3(d)           | Functional Diagram                                                                        | 26       |

| 3(e)           | Input/output Protection Networks                                                          | 26<br>26 |

| 4              | Circuits for Electrical Measurements                                                      | 60       |

| 5(a)           | Electrical Circuit for High Temperature Reverse Bias Burn-in                              | 67       |

| 5(b)           | Electrical Circuit for Power Burn-in and Operating Life Tests                             | 67       |

| 6              | Bias Conditions for Irradiation Testing                                                   | 75       |

| APPEI          | NDICES (Applicable to specific Manufacturers only)                                        |          |

| 'A'            | Agreed Deviations for MITEL (S)                                                           | 84       |

|                |                                                                                           |          |

Rev. 'A'

PAGE 5

ISSUE 1

#### 1. **GENERAL**

#### 1.1 SCOPE

This specification details the ratings, physical and electrical characteristics, test and inspection data for a monolithic, Silicon on Sapphire CMOS Virtual Channel Assembler, based on Type 12399. It shall be read in conjunction with ESA/SCC Generic Specification No. 9000, the requirements of which are supplemented herein.

#### 1.2 COMPONENT TYPE VARIANTS

Variants of the basic type integrated circuits specified herein, which are also covered by this specification, are given in Table 1(a).

#### 1.3 MAXIMUM RATINGS

The maximum ratings, which shall not be exceeded at any time during use or storage, applicable to the integrated circuits specified herein, are as scheduled in Table 1(b).

#### 1.4 PARAMETER DERATING INFORMATION (FIGURE 1)

Not applicable.

#### 1.5 PHYSICAL DIMENSIONS

As per Figure 2.

#### 1.6 PIN ASSIGNMENT

As per Figure 3(a).

#### 1.7 TRUTH TABLE

As per Figure 3(b).

#### 1.8 CIRCUIT DESCRIPTION

As per Figure 3(c).

#### 1.9 FUNCTIONAL DIAGRAM

As per Figure 3(d).

#### 1.10 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are categorised as Class 2 with a Minimum Critical Path Failure Voltage of 1500Volts.

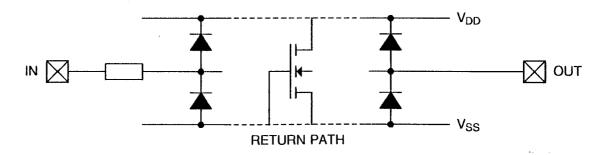

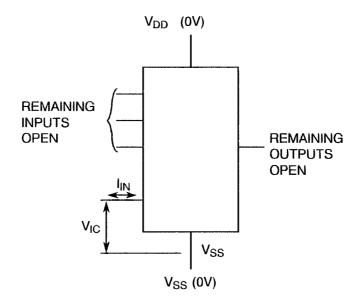

#### 1.11 <u>INPUT/OUTPUT PROTECTION NETWORKS</u>

Protection networks shall be incorporated into each input and output as shown in Figure 3(e).

PAGE 6

ISSUE 1

## TABLE 1(a) - TYPE VARIANTS

| VARIANT | CASE | FIGURE | LEAD MATERIAL<br>AND FINISH |

|---------|------|--------|-----------------------------|

| 01      | FLAT | 2(a)   | D2                          |

## **TABLE 1(b) - MAXIMUM RATINGS**

| No. | CHARACTERISTICS                    | SYMBOL           | MAXIMUM RATINGS                | UNIT | REMARKS          |

|-----|------------------------------------|------------------|--------------------------------|------|------------------|

| 1   | Supply Voltage                     | V <sub>DD</sub>  | -0.5 to +7.0                   | ٧    | -                |

| 2   | Input Voltage                      | V <sub>IN</sub>  | – 0.5 to V <sub>DD</sub> + 0.5 | ٧    | -                |

| 3   | DC Input Current                   | IN               | 20                             | mA   | -                |

| 4   | DC Output Current                  | Гоит             | 10                             | mA   | Note 1           |

| 5   | Device Dissipation<br>(Continuous) | P <sub>D</sub>   | 200                            | mWdc | -                |

| 6   | Output Dissipation                 | P <sub>DSO</sub> | 50                             | mWdc | Note 1           |

| 7   | Operating Temperature<br>Range     | Тор              | – 55 to + 125                  | °C   | T <sub>amb</sub> |

| 8   | Storage Temperature<br>Range       | T <sub>stg</sub> | - 65 to + 150                  | °C   | -                |

| 9   | Soldering Temperature              | T <sub>sol</sub> | + 260                          | ۰C   | Note 2           |

#### **NOTES**

- 1. Single output.

- 2. Duration 5 seconds maximum at a distance of not less than 1.0mm from the device body and the same lead shall not be resoldered until 3 minutes have elapsed.

# FIGURE 1 - PARAMETER DERATING INFORMATION

Not applicable.

PAGE

ISSUE

# FIGURE 2 - PHYSICAL DIMENSIONS

FIGURE 2(a) - FLAT PACKAGE, 84-PIN

| SYMBOL   | MILLIMETRES |      | NOTES |

|----------|-------------|------|-------|

| STIVIBUL | MIN         | MAX  | NOTES |

| Α        | 33.5        | 35.0 |       |

| В        | 16.2        | 16.7 |       |

| С        | 1.0         | 1.5  |       |

| C1       | 1.2         | 1.7  | 2, 5  |

| D        | 0.1         | 0.2  |       |

| F        | 0.5         | 0.7  | 3, 4  |

| G        | 0.2         | 0.3  | 2     |

| н .      | 1.9         | 2.4  |       |

| L        | 8.2         | 9.5  | 2     |

PAGE 8

ISSUE 1

## FIGURE 2 - PHYSICAL DIMENSIONS (CONTINUED)

#### NOTES TO FIGURE 2(a)

- 1. Index area; the index shall be as defined in Figure 2(a).

- 2. All leads.

- 3. 80 spaces for flat packages.

- 4. The true position pin spacing is 0.635mm between centre lines. Each pin centreline shall be located within ± 0.1mm of its true longitudinal position relative to Pin 1 and the highest pin number.

- 5. The dimension shall be measured at the point of exit of the lead from the body.

PAGE

ISSUE 1

9

#### FIGURE 3(a) - PIN ASSIGNMENT

PAGE 10

ISSUE 1

# FIGURE 3(a) - PIN ASSIGNMENT (CONTINUED)

# PIN DESCRIPTION

| SYMBOL            | FUNCTION                                  | DESCRIPTION           | PIN NUMBER |

|-------------------|-------------------------------------------|-----------------------|------------|

| $V_{\mathrm{DD}}$ | Input                                     | Positive Supply       | 1          |

| D5                | Data Input, Parallel Interface            | TTL Input             | 2          |

| D6                | Data Input, Parallel Interface            | TTL Input             | 3          |

| V <sub>SS</sub>   | Input                                     | Negative Supply       | 4          |

| D7                | Data Input, Parallel Interface            | TTL Input             | 5          |

| BUSY              | VCA Busy                                  | Output                | 6          |

| VCAR              | VCA Ready                                 | Output                | 7          |

| SCLK              | Clock, Serial Interface                   | CMOS Input            | 8          |

| SIN               | Data Input, Serial Interface              | CMOS Input            | 9          |

| SVALID            | Data Valid, Serial Interface              | CMOS Input            | 10         |

| SMODE             | Mode Selection                            | CMOS Input            | 11         |

| RESET             | Master Reset                              | Schmitt Trigger Input | 12         |

| CLK               | Clock                                     | CMOS Input            | 13         |

| NC                | Not Connected                             | -                     | 14         |

| ERR               | Internal Error                            | Output                | 15         |

| TEST1             | Test Control                              | CMOS Input            | 16         |

| TEST0             | Test Control                              | CMOS Input            | 17         |

| PROG2             | Poll Programme                            | CMOS Input            | 18         |

| PROG1             | Poll Programme                            | CMOS Input            | 19         |

| PROG0             | Poll Programme                            | CMOS Input            | 20         |

| $V_{ m DD}$       | Input                                     | Positive Supply       | 21         |

| $V_{SS}$          | Input                                     | Negative Supply       | 22         |

| OPCF              | Operational Control Field                 | CMOS Input            | 23         |

| FECW              | Frame Error Control Word                  | CMOS Input            | 24         |

| LEN1              | Transfer Frame Length                     | CMOS Input            | 25         |

| LEN0              | Transfer Frame Length                     | CMOS Input            | 26         |

| SYNCF             | Synchronisation Flag                      | CMOS Input            | 27         |

| PKTVER            | Packet Version for Idle Telemetry Packets | CMOS Input            | 28         |

| SECHEAD           | Secondary Header Flag                     | CMOS Input            | 29         |

| LSEG1             | Segmentation Length Identifier            | CMOS Input            | 30         |

| LSEG0             | Segmentation Length Identifier            | CMOS Input            | 31         |

| PKTORD            | Packet Order Flag                         | CMOS Input            | 32         |

| RANDOM            | Pseudo-Random Data                        | Output                | 33         |

| IFILL             | Idle Fill Data                            | CMOS Input            | 34         |

| TMODE3            | Timing Strobe Mode                        | CMOS Input            | 35         |

| TMODE2            | Timing Strobe Mode                        | CMOS Input            | 36         |

| TMODE1            | Timing Strobe Mode                        | CMOS Input            | 37         |

| TMODE0            | Timing Strobe Mode                        | CMOS Input            | 38         |

PAGE 11

ISSUE 1

# FIGURE 3(a) - PIN ASSIGNMENT (CONTINUED)

## PIN DESCRIPTION (CONTINUED)

| SYMBOL            | FUNCTION                  | DESCRIPTION      | PIN NUMBER |

|-------------------|---------------------------|------------------|------------|

| V <sub>SS</sub>   | Input                     | Negative Supply  | 39         |

| TESTOUT           | Production Test Output    | Output           | 40         |

| TIME              | Time Sampling Strobe      | Output           | 41         |

| CLKMODE           | Clock Mode                | CMOS Input       | 42         |

| BITCLK            | Bit Clock                 | CMOS Input       | 43         |

| RTS               | Ready To Send             | Output           | 44         |

| PVCF              | Partial Virual Frame Data | Output           | 45         |

| CTS               | Clear To Send             | CMOS Input       | 46         |

| POLL              | Device Poll               | CMOS Input       | 47         |

| $V_{\mathrm{DD}}$ | Input                     | Positive Supply  | 48         |

| ERT               | External RAM Test         | CMOS Input       | 49         |

| RD3               | RAM Data                  | TTL Input/Output | 50         |

| RD4               | RAM Data                  | TTL Input/Output | 51         |

| RD2               | RAM Data                  | TTL Input/Output | 52         |

| RD1               | RAM Data                  | TTL Input/Output | 53         |

| RD5               | RAM Data                  | TTL Input/Output | 54         |

| RD0               | RAM Data                  | TTL Input/Output | 55         |

| RD6               | RAM Data                  | TTL Input/Output | 56         |

| V <sub>SS</sub>   | Input                     | Negative Supply  | 57         |

| RA0               | RAM Address               | Output           | 58         |

| RD7               | RAM Data                  | TTL Input/Output | 59         |

| RA1               | RAM Address               | Output           | 60         |

| RCS               | RAM Chip Select           | Output           | 61         |

| RA2               | RAM Address               | Output           | 62         |

| RA10              | RAM Address               | Output           | 63         |

| V <sub>SS</sub>   | Input                     | Negative Supply  | 64         |

| $V_{\mathrm{DD}}$ | Input                     | Positive Supply  | 65         |

| RA3               | RAM Address               | Output           | 66         |

| ŌĒ                | RAM Output Enable Control | Output           | 67         |

| RA4               | RAM Address               | Output           | 68         |

| RA11              | RAM Address               | Output           | 69         |

| RA5               | RAM Address               | Output           | 70         |

| RA9               | RAM Address               | Output           | 71         |

| RA6               | RAM Address               | Output           | 72         |

| RA8               | RAM Address               | Output           | 73         |

| $V_{SS}$          | Input                     | Negative Supply  | 74         |

| RA7               | RAM Address               | Output           | 75         |

| RA12              | RAM Address               | Output           | 76         |

PAGE 12

ISSUE 1

## FIGURE 3(a) - PIN ASSIGNMENT (CONTINUED)

# PIN DESCRIPTION (CONTINUED)

| SYMBOL    | FUNCTION                                 | DESCRIPTION | PIN NUMBER |

|-----------|------------------------------------------|-------------|------------|

| R/W       | RAM Read/Write Control                   | Output      | 77         |

| VPD       | Valid Packet Data for Parallel Interface | TTL Input   | 78         |

| <u>CS</u> | Chip Select, Parallel Interface          | TTL Input   | 79         |

| D0        | Data Input, Parallel Interface           | TTL Input   | 80         |

| D1        | Data Input, Parallel Interface           | TTL Input   | 81         |

| D2        | Data Input, Parallel Interface           | TTL Input   | 82         |

| D3        | Data Input, Parallel Interface           | TTL Input   | 83         |

| D4        | Data Input, Parallel Interface           | TTL Input   | 84         |

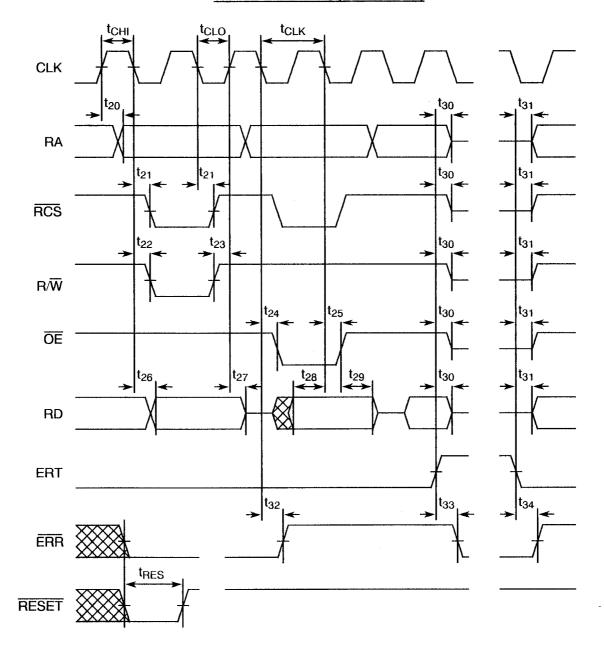

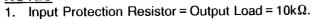

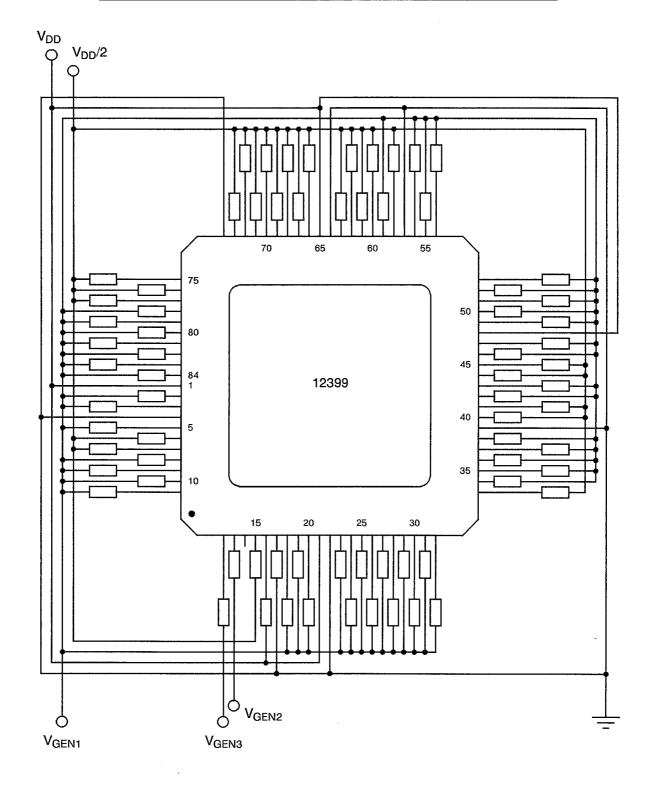

## FIGURE 3(b) - TRUTH TABLE

## **TIMING DIAGRAMS**

PAGE 13

ISSUE 1

# FIGURE 3(b) - TRUTH TABLE (CONTINUED)

# TIMING DIAGRAMS (CONTINUED)

PAGE 14

ISSUE 1

# FIGURE 3(b) - TRUTH TABLE (CONTINUED)

# **TIMING DIAGRAMS (CONTINUED)**

PAGE 15

ISSUE

#### FIGURE 3(c) - CIRCUIT DESCRIPTION

#### **SUMMARY OF OPERATION**

After reset and the optional self-test, the VCA provides the following functions:

- Reception of data from the OBDH system, which is stored in an external RAM together with header data.

- When requested by the VCM, a partial Transfer Frame is output, consisting of the PVCF Header, optionally including a Secondary Header, and the Transfer Frame Data Field.

- If enough data is not available, a partial Idle Transfer Frame is output instead.

- Optional generation of Idle Telemetry Packets to fill up incomplete Transfer Frames.

- Generation of Pseudo-random Idle Fill data, used for the generation of partial Idle Telemetry Packets and Idle Transfer Frames.

- Generation of a Time sampling strobe.

In order to complete the Transfer Frame the VCM performs the following functions:

- Generation of the 32 bit Synchronisation Marker.

- Generation of the first three octets of the Transfer Frame Primary Header.

- Feed-through of the PVCF data as part of the Transfer Frame.

- Generation of an optional Transfer Frame Trailer.

- Optionally leaving space for a Reed-Solomon code check block.

#### **FUNCTIONS NOT INCLUDED IN THE VCA**

The VCA does not perform segmentation of Source Packets, which should be done by the data source. The VCA can handle Telemetry Packets and data blocks longer than 8k octets, though only a part of the data will reside in the external RAM at a time.

The VCA does not check the contents or the format of the Telemetry Packets provided by the source. Thus the VCA is independent of the Telemetry Packet format and any data structure can be used. The only exception is the Idle Telemetry Packets that can be optionally generated by the VCA itself, which have a predefined structure.

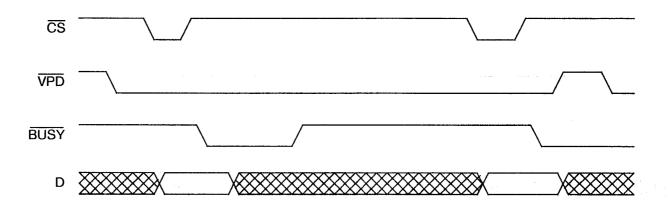

#### **PARALLEL INPUT INTERFACE**

The parallel interface, shown in Figure I, is active when SMODE = "0". The serial interface inputs SCLK, SVALID and SIN are then disabled but should be held to a defined logic level.

The main functions of the parallel input interface are:

- To latch data from the input bus and into the VCA.

- To inform the data source that the VCA has space in the external RAM.

- To detect the beginning of Telemetry Packets or data blocks being sent from the source and to set the First Header Pointer accordingly.

PAGE 16

ISSUE 1

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

#### FIGURE I - PARALLEL INPUT INTERFACE

Data is input from the data source using the eight-bit-wide data bus (D0 - D7), and the chip select,  $\overline{CS}$ . The interface is asynchronous. Data is latched into the VCA on the rising  $\overline{CS}$  edge, as shown in Figure I.

#### N.B. D0 is the MSB.

The active low Valid Packet Data ( $\overline{VPD}$ ) input defines when a new Telemetry Packet (data block in asynchronous mode) starts. The VCA stores data latched by the input interface when the  $\overline{VPD}$  input is enabled ( $\overline{VPD}$  = "0"). The  $\overline{VPD}$  input should be continuously enabled while a Telemetry Packet is being input. The timing of  $\overline{VPD}$  is shown in Figure I.  $\overline{VPD}$  is also used to set the First Header Pointer.

Data may be supplied at any rate up to one octet transfer every four CLK cycles, allowing a maximum peak input data rate of 25MBit/s when operating at the maximum clock frequency of 12.5MHz. If data is input at a higher rate, data could be lost.

In the case of using Telemetry Packets with a limited length (LSEG≠"11"), the VCA Ready (VCAR) output is enabled when there is room for at least one maximum-length Telemetry Packet in the external RAM. Otherwise the VCAR output is enabled when there is room for at least one Transfer Frame Data Field.

This output is enabled (= "1") when the VCA has place to store data in the external RAM, as defined below. VCAR changes state on the falling CLK edge. VCAR is also disabled when ERT is enabled (= "1") since the RAM is not then accessible. The values correspond to one maximum length packet or data field, respectively.

| SYNCF | LSEG0 | LSEG1 | VCAR Threshold                       |

|-------|-------|-------|--------------------------------------|

| 0     | 0     | 0     | ≥262 (256 + 6)                       |

| 0     | 0     | 1     | ≥518 (512+6)                         |

| 0     | 1     | 0     | ≥ 1030 (1024 + 6)                    |

| 0     | 1     | . 1   | ≥Length of Transfer Frame Data Field |

| 1     | -     | -     | ≥Length of Transfer Frame Data Field |

#### **NOTES**

1. Logic Level Definitions: 0 = Low Level, 1 = High Level.

PAGE 17

ISSUE :

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

Since VCAR is enabled when there is room for a predefined amount of data (one maximum-length Telemetry Packet or alternatively one Transfer Frame Data Field), this data can be transferred in its entirety without needing to check VCAR again.

The BUSY (VCA Busy) output is enabled (BUSY = "0") immediately after an octet has been written into the VCA (i.e. the rising CS edge). BUSY is disabled at the next falling CLK edge three CLK cycles after the rising CS edge. Since CS may be asynchronous, the actual duration of BUSY enabled can vary between three and four CLK cycles. BUSY is also enabled when there is no space for more octets in the external RAM. If CS is enabled while BUSY is enabled, no data will be latched.

The VCAR output alone can be used together with data sources that provide data with a transfer rate which is less than the maximum possible, while the BUSY output can be used with fast data sources that need acknowledgement on the octet level, such as a CPU.

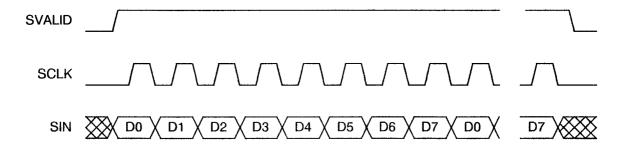

#### **SERIAL INPUT INTERFACE**

The serial input interface, shown in Figure II, is enabled when SMODE = "1". The parallel interface inputs  $\overline{CS}$ ,  $\overline{VPD}$  and D0 - D7 are disabled, but should be held to a defined logic level. The VCAR and  $\overline{BUSY}$  outputs and all other functions of the VCA behave the same as for the parallel input interface, although they are probably less useful for the serial interface.

#### FIGURE II - SERIAL INPUT INTERFACE

Serial data is clocked in on the rising SCLK edge, when SVALID = "1". The serial data is assembled in a shift register and when eight bits have been input, the resulting octet is internally forwarded to the parallel interface. Data should consist of multiples of eight bits otherwise the last bits will be lost.

The input signal SVALID is used to delimit Telemetry Packets (data blocks in asynchronous mode), in the same way as  $\overline{\text{VPD}}$  is used for the parallel interface. It shall be enabled while a Telemetry Packet (data block) is being input. In addition, SVALID defines the octet boundaries in the input data stream, the first octet explicitly and the following octets each subsequent eight SCLK cycles; the first bit received after SVALID has been enabled is bit 0. SVALID shall be enabled when data is input.

SCLK is asynchronous and thus need not be correlated to the CLK, except for the maximum input data transfer rate (one octet per four CLK cycles).

PAGE 18

ISSUE -

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

#### STORAGE OF DATA IN EXTERNAL RAM

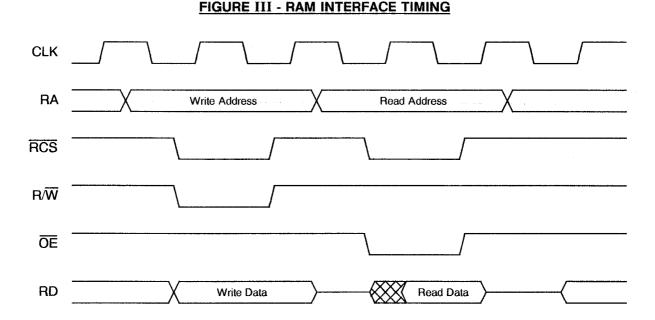

The VCA interfaces to an external 8k×8 static RAM to store PVCF data until the VCM requests it. The VCA RAM interface is shown in Figure III. The interface timing ensures that no bus collisions occur due to the VCA and RAM driving output data at the same time and this also applies for consecutive read and write cycles. The VCA can be used with RAMs such as MA9264 from GEC Plessey Semiconductors and HM65664 from Matra MHS, among others.

The VCA is capable of storing a variable number of PVCFs, ranging from 7 of the maximum length PVCFs to 36 of minimum length. Table I shows the relationship between the Transfer Frame length and the maximum number of PVCFs that can be stored.

TABLE I - TRANSFER FRAME LENGTH VERSUS MAXIMUM NUMBER OF PVCFs STORED

| TRANSFER FRAME LENGTH | MAXIMUM NUMBER OF PVFCs THAT CAN BE STORED |

|-----------------------|--------------------------------------------|

| 223                   | 36                                         |

| 446                   | 18                                         |

| 892                   | 9                                          |

| 1115                  | 7                                          |

The VCA generates the RAM address (RA0 - RA12), the Chip Select ( $\overline{RCS}$ ), the Read/Write strobe ( $\overline{R/W}$ ) and the Output Enable ( $\overline{OE}$ ). Data is transferred to and from the RAM over the bidirectional data bus (RD0 - RD7). The duration of the read and write cycles generated by the VCA is two CLK cycles. When the VCA does not access the RAM, the RD data bus is still driven to ensure that the bus is not left floating.

PAGE 19

ISSUE 1

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

Once a PVCF transfer to the VCM has started, the VCA continues to output the PVCF data without interruption. Therefore, during the output of a PVCF to the VCM, the VCA reads PVCF data from the RAM once every eight CLK cycles (BITCLK cycles, when CLKMODE = "1").

The maximum input data rate is one octet every four CLK cycles, and thus the VCA may be required to write input data to the RAM once every four CLK cycles. In addition, Transfer Frame Header data and Idle Telemetry Packets are written to the RAM without disturbing the above RAM accesses.

#### **VIRTUAL CHANNEL FRAME COUNTER**

To verify that all Virtual Channel Frames have been received and in the correct order, the VCA has a 32 bit wrap-around Virtual Channel Frame Counter, which is incremented for each PVCF, normal and idle.

The VCA assigns the eight LSBs of the Virtual Channel Frame Counter to the Virtual Channel Frame Count field in the Primary Header. When the Secondary Header is present (SECHEAD = "1") the VCA assigns the 24 MSBs of the Virtual Channel Frame Counter to the Secondary Header Data field.

| MSB | 32-bit Virtual Ch     | nannel Fram | e Counte | er e e e e e e e e e e e e e e e e e e | LSB |

|-----|-----------------------|-------------|----------|----------------------------------------|-----|

| 0   |                       | 23          | 24       |                                        | 31  |

| MSB | Secondary Header Data | LSB         | MSB      | VC Frame Count                         | LSB |

| 0   |                       | 23          | 0        |                                        | 7   |

#### FIRST HEADER POINTER

The First Header Pointer is required for the Telemetry Packet chaining process during Telemetry Packet de-multiplexing at the ground (Earth). The VCA generates partial Transfer Frames in one of two possible states; active or idle, as defined in RD1. The data contained in an active Transfer Frame can be either Telemetry Packets (SYNCF = "0") or non-packet data delimited into data blocks (SYNCF = "1"). Telemetry Packets are referred to as synchronous data in RD1 whereas non-packet data is referred to as asynchronous data.

In the active state, Telemetry Packets may be of varying lengths. It is unlikely that an integer number of Telemetry Packets will be exactly contained within a Transfer Frame, so some Telemetry Packets will be split between two Transfer Frames. The VCA calculates the position of the first octet of the first Telemetry Packet to be placed in each Transfer Frame, in accordance with RD1, then inserts this value into the header of the PVCF.

For the VCA, the above also applies to non-packet data, allowing data blocks to be identified in the data stream. This is an extension to RD1, permitting the First Header Pointer also to be set for non-packet data in the same way as it is set for Telemetry Packets. This feature is activated by using the  $\overline{\text{VPD}}$  signal for the parallel interface (SVALID signal for the serial interface) to delimit data blocks, in the same way as for delimiting Telemetry Packets. For serial input mode, SVALID has the same functions as  $\overline{\text{VPD}}$  in parallel input mode.

PAGE 20

ISSUE

# FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

The First Header Pointer is initiated to "all ones" at reset, allowing the VCA to operate in full compliance with RD1 for non-packet data by permanently connecting VPD to logic "0" (SVALID to logic "1" when SMODE = "1"). This means that when using Telemetry Packets (or when using the First Header Pointer for non-packet data), the VPD input should be held at logic "1" (SVALID at logic "0" when SMODE = "1") until six CLK cycles after RESET has been disabled, to be disabled before writing the first Telemetry Packet or data block. Otherwise the First Header Pointer for the first transmitted non-Idle Transfer Frame after reset would have the First Header Pointer set to "all ones" instead of "all zeros".

IF  $\overline{\text{VPD}}$  (SVALID when SMODE = "1") was not disabled while all the data filling up a Transfer Frame was input, e.g. if a Telemetry Packet or data block is longer than the data field of the Transfer Frame, the First Header Pointer is set to "all ones"; First Header Pointer = "111111111111".

In the idle state, the VCA sends a partial Idle Transfer Frame and the First Header Pointer is set to the predefined Idle First Header Pointer code. This code is the same both for Telemetry Packets and non-packet data; First Header Pointer = "11111111111111".

The VCA fully supports the First Header Pointer and has therefore no requirements on aligning the data with the Transfer Frame boundary, contrary to other implementations.

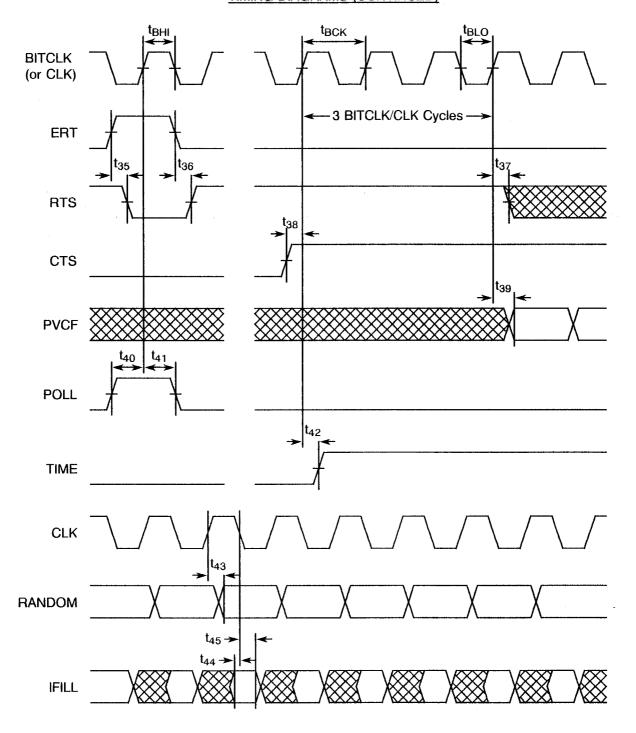

#### **VCA/VCM INTERFACE**

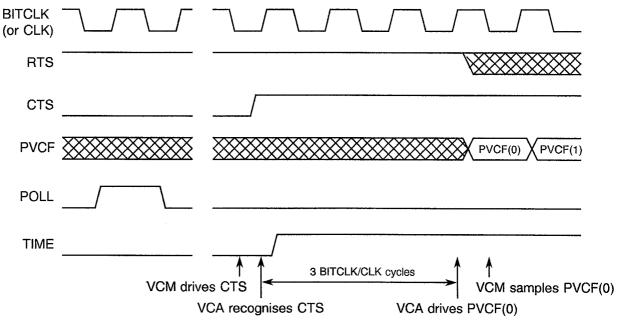

The VCA/VCM interface, shown in Figure IV, is for the serial transfer of partial Transfer Frames to the VCM. The VCA relates its operations to the rising CLK edge (rising BITCLK edge, when CLKMODE = "1"), whereas the VCM relates its operations to the falling BITCLK edge, to minimise potential skew problems. The VCA has a Clear To Send (CTS) and a device POLLed (POLL) input, and a Ready To Send (RTS) and a Partial Virtual Channel Frame data (PVCF) output.

#### FIGURE IV - TIMING OF VCA/VCM INTERFACE

#### NOTES

- 1. The RTS signal will stay asserted if there are more PVCFs available.

- 2. If there are no more PVCFs the RTS signal will be de-asserted.

- 3. PVCF(1) = Bit 1 of PVCF.

PAGE 21

ISSUE -

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

The VCA/VCM interface can operate relative to the BITCLK signal for bit rates up to 3MBit/s or relative to the CLK signal for bit rates up to 12.5MBit/s. When CLKMODE = "0", the VCA/VCM interface uses the CLK signal; when CLKMODE = "1", the interface uses the asynchronous BITCLK signal. BITCLK is then sampled internally by the VCA generating an internal enable signal when the rising BITCLK edge is detected. This signal enables the interface signals (RTS, POLL, CTS, PVCF) to be sampled/driven during the next CLK cycle.

Using the BITCLK signal enables the VCA to operate at a higher clock frequency than the VCM, allowing a bit rate independent of input data rate. In addition, the RAM power dissipation might decrease due to the chip select being enabled for a shorter time, depending on the RAM device used.

The VCA enables the output signal RTS when it has stored a complete PVCF in RAM. RTS will remain enabled as long as there is one or more complete PVCFs in RAM, excluding a PVCF currently being output. When the VCM is ready to receive data from the VCA, it enables the CTS signal. Three CLK (or BITCLK) cycles after the VCA has detected the enabled CTS input, it will start to output PVCF data. The PVCF data is output at the rate of one bit per CLK (or BITCLK) cycle without interrupt until the complete PVCF has been output. The CTS input shall be enabled for a minimum of 16 CLK cycles, and it shall be disabled before the end of the PVCF.

If the VCM enables the CTS signal when the VCA has not enabled RTS, the VCA outputs an Idle PVCF.

#### **IDLE TRANSFER TIMES**

An Idle PVCF, which will be finalised into an Idle Transfer Frame by the VCM, will be produced when the VCA has not stored a complete PVCF in RAM, when CTS is enabled. Idle PVCFs are not stored in RAM but generated while being output. The timing and the length of an Idle PVCF is identical to a normal PVCF. Idle Transfer Frames should not be confused with Idle Telemetry Packets.

The Idle PVCF Data Field contains no useful data. It will be filled with data from the Idle Fill data input (IFILL). One bit per CLK cycle (BITCLK cycle, when CLKMODE = "1") is sampled and used for Idle PVCF data.

#### **IDLE TELEMETRY PACKET INSERTION**

The VCA can optionally generate and insert Idle Telemetry Packets, to fill up an incomplete Transfer Frame. This ensures that Telemetry Packets do not remain inaccessible due to an incomplete Transfer Frame being resident in the RAM. This feature is only available when the VCA is operating with Telemetry Packets, referred to as synchronous data in RD1. Idle Telemetry Packets should not be confused with Idle Transfer Frames.

The Idle Telemetry Packet insertion process starts when all of the following conditions are met:

- The VCA operates with Telemetry Packets (SYNCF = "0").

- The source is not sending a Telemetry Packet (VPD = "1" or SVALID = "0", respectively).

- The VCA is not Ready To Send data (RTS = "0").

- An incomplete PVCF (containing non-Idle Telemetry Packets or part of a non-Idle Telemetry Packet) is resident in the external RAM.

- The value of the Poll Programme inputs, PPROG0 to PPROG2, is not equal to "111".

- The appropriate number of device polls have been counted by the Poll Counter.

PAGE 22

ISSUE 1

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

When the Idle Telemetry Packet insertion process has filled the PVCF, the VCA enables the RTS output. The Idle Telemetry Packet insertion process stops after the last Idle Telemetry Packet has been stored in the RAM. In the case that the last Idle Telemetry Packet spilled over, it will be written to the next PVCF. The time required for the VCA to complete a PVCF with Idle Telemetry Packets depends on how much space there is left to be filled. The worst case is when the longest possible data field in a Transfer Frame of 1115 octets contains only one octet of Telemetry Packet data, which will take less than 12 000 CLK cycles to complete the PVCF data field.

Should VPD (SVALID when SMODE = "1") be enabled after the Idle Telemetry Packet insertion process has started, the current Idle Telemetry Packet is completed in parallel with the storing of Telemetry Packet data and then the Idle Telemetry Packet insertion process is suspended. As soon as VPD (SVALID) is disabled, indicating the end of the normal Telemetry Packet, the Idle Telemetry Packet insertion process resumes and continues until the PVCF has been completed (it will not stop due to a new Telemetry Packet being received) unless the PVCF was already completely filled with normal Telemetry Packets.

The VCA is able to receive Telemetry Packets and send PVCFs simultaneously with the insertion of an Idle Telemetry Packet.

When a Transfer Frame contains no Telemetry packets or when it contains only part of an Idle Telemetry Packet, the Idle Telemetry Packet insertion process will not start. The situation where a PVCF contains only part of an Idle Telemetry Packet occurs when an Idle Packet spilled over from the previous Transfer Frame and it is the only data in the Transfer Frame.

#### **POLL COUNTER**

In the previous section, six conditions were listed for the Idle Telemetry Packet insertion process to commence. When the VCA detects that the first five conditions are met, it enables the Poll Counter. The Poll Counter is reset and disabled when either of the following conditions is met:

- The source asserts VPD or SVALID in preparation for sending Telemetry Packets, OR

- The Idle Telemetry Packet insertion process is active.

When the Poll Counter is enabled, it increments by one at every rising CLK edge (rising BITCLK edge, when CLKMODE = "1") when the POLL input is enabled. The VCM asserts POLL every time it checks the RTS signal of the VCA, while selecting which VCA to output the next PVCF. The Poll Counter increments until it reaches the number of programmed polls, ranging from 1 to 1024, as indicated by the value of PPROG0 to PPROG2 and then it enables the Idle Telemetry Packet insertion process.

The Poll Counter is enabled when:

- (SYNCF = "0") AND,

- (VPD = "1") or SVALID = "0", respectively) AND,

- (RTS = "0") AND,

- ("000" < PPROG[0...2] < "111") AND,

- (The incomplete PVCF contains non-Idle Telemetry Packet data) AND,

- (The Idle Telemetry Packet insertion process is not active),

otherwise the Poll Counter is reset and disabled.

PAGE 23

ISSUE 1

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

The Poll Counter is incremented by one at every rising CLK edge (rising BITCLK edge, when CLKMODE = "1") when:

- (Poll Counter enabled) AND (POLL = "1").

The Idle Telemetry Packet insertion process starts when:

- [(POLL Counter enabled) AND,

- (POLL Counter = Threshold value as defined in Table II)] OR,

- [(PPROG[0...2] = "000") AND,

- (SYNCF = "0") AND,

- (VPD = "1") AND,

- (RTS = "0") AND,

- (The incomplete PVCF contains non-ldle Telemetry Packet data)).]

The Idle Telemetry Packet insertion process stops when:

- The PVCF is complete and the remainder of the last Idle Telemetry Packet has been stored in the next PVCF, if the Idle Telemetry Packet spills over from the last PVCF.

The relationship between the signals POLL and VPD or SVALID has to allow for internal synchronisation of the signals in the VCA.

#### **TABLE II - POLL COUNTER THRESHOLD**

|    | PPROG2 | PPROG1 | PPROG0 | Poll Counter Threshold                                      |

|----|--------|--------|--------|-------------------------------------------------------------|

| ÷> | 0      | 0      | 0      | Immediate Idle Telemetry Packet Insertion (1)               |

|    | 0      | 0      | 1      | 1 device poll                                               |

|    | 0      | 1      | 0      | 4 device polls                                              |

|    | 0      | 1      | 1      | 16 device polls                                             |

|    | 1      | 0      | 0      | 64 device polls                                             |

|    | 1      | 0      | 1      | 256 device polls                                            |

|    | 1      | 1      | 0      | 1024 device polls                                           |

|    | 1      | 1      | 1      | Idle Telemetry Packet insertion process will not be started |

#### **NOTES**

1. Idle Telemetry Packet insertion process starts when all relevant conditions are met.

#### **IDLE TELEMETRY PACKET**

The VCA generates the Idle Telemetry Packet Header and inserts the pre-defined values into the appropriate fields.

The data field of an Idle Telemetry Packet is filled with data from the Idle Fill data input (IFILL). One bit per CLK cycle is sampled and used for Idle Telemetry Packet data.

PAGE 24

ISSUE 1

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

#### **PSEUDO-RANDOM IDLE FILL DATA**

The Pseudo-random Idle Fill data is generated to provide fill data for the data fields of Idle Telemetry Packets and Idle PVCFs. The pseudo-random data generator generates the RANDOM output signal, which can be connected to the Idle Fill data input pin (IFILL). The data output rate is one bit per CLK cycle. The pseudo-random Data generator is free-running, and will not be initialised by any event except reset ( $\overline{RESET}$  = "0"). The pseudo-random data generator polynomial is  $x^9 + x^5 + 1$ .

The design of the generator ensures that a Single Event Upset (SEU) or any other spurious event will not cause the generator to jump to an invalid state and produce a continuous output of ones or zeros.

#### TIME SAMPLING STROBE

The VCA provides the active high TIME strobe for sampling the on-board time according to Section 7.4 of RD1. TIME is enabled one CLK cycle (two CLK cycles after the rising BITCLK edge, when CLKMODE = "1") after CTS has been asserted, when the eight LSBs of the Virtual Channel Frame Counter for the partial Transfer Frame to be sent out contain the value(s) selected by the four TMODE pins. This allows all intervals defined in RD1 to be selected. TIME will remain asserted for 128 CLK cycles, regardless of the CLKMODE value.

This means that the TIME strobe will be enabled 51 CLK cycles (51 BITCLK plus two CLK cycles after the rising BITCLK edge, when CLKMODE = "1") after the leading edge of the Synchronisation Marker has been output from the VCM. This can be regarded as compliant with the requirements of RD1 since the delay relative to the rising edge of the first bit of the Synchronisation Marker is fixed and known.

If it nevertheless is required to sample the on-board time exactly at the rising edge of the Synchronisation Marker, the time can be sampled at this edge for every Transfer Frame generated but only read out when the TIME strobe is asserted.

The TIME strobe from the VCA associated with Virtual Channel 0 should be used for sampling the on-board spacecraft time.

#### **TEST**

The VCA features Built-in Self Test (BIST) with a fault coverage of 89.5%. The BIST runs for 4996 CLK cycles after RESET has been released. The BIST result does not depend on the state of any of the inputs. The BIST can be disabled by connecting the TEST0 input to logic "1"; after releasing RESET, the VCA will be reset but no BIST will be performed.

If an error is detected by the BIST, the  $\overline{ERR}$  output remains enabled ( $\overline{ERR}$  = "0"), until the next reset occurs. The VCA will try to continue to operate in normal mode. If no internal error was detected, the  $\overline{ERR}$  output is disabled, and the VCA starts working in normal mode.

When RESET is enabled and during BIST, the RCS, OE and R/W outputs are driven to logic "1" and all other outputs except RANDOM are driven to logic "0" so as not to trigger connected devices. The RD data bus is driven to logic "0" to ensure that it is not left floating. Due to design reasons, the RANDOM pin outputs pseudo-random data also during BIST.

PAGE 25

ISSUE

#### FIGURE 3(c) - CIRCUIT DESCRIPTION (CONTINUED)

The active high input External Ram Test (ERT) can be used to 3-state <u>all</u> outputs from the VCA to the external RAM, to allow for RAM test. When ERT is enabled the outputs <u>ERR</u>, VCAR and RTS are held at logic "0" since the VCA can no longer control the RAM. When ERT is disabled, control of the RAM interface, VCAR, RTS and <u>ERR</u> is returned to the VCA. ERT is asynchronous and only disables the outputs, without any other impact on the VCA.

The production test for the VCA has a fault coverage higher then 96%, and is performed at a CLK frequency of 10MHz. The TEST1 input is used for the production test and shall be tied to logic "0" during normal operation.

The fault coverage figures are based on stuck-at-0/1 faults at the gate level, faulting all nets (gate outputs).

#### STATE AFTER RESET

After reset, or after reset and completion of BIST, the VCA is initialised as follows:

- The Virtual Channel Frame Counter has the value 0.

- The First Header Pointer is initialised to "all ones".

- The Poll Counter has the value 0.

Since the VCA BIST takes fewer CLK cycles than the VCM BIST, the VCA will always be ready when the VCM requires the first Transfer Frame (except for the unrealistic case when the VCA performs BIST and the VCM does not).

PAGE 26

ISSUE 1

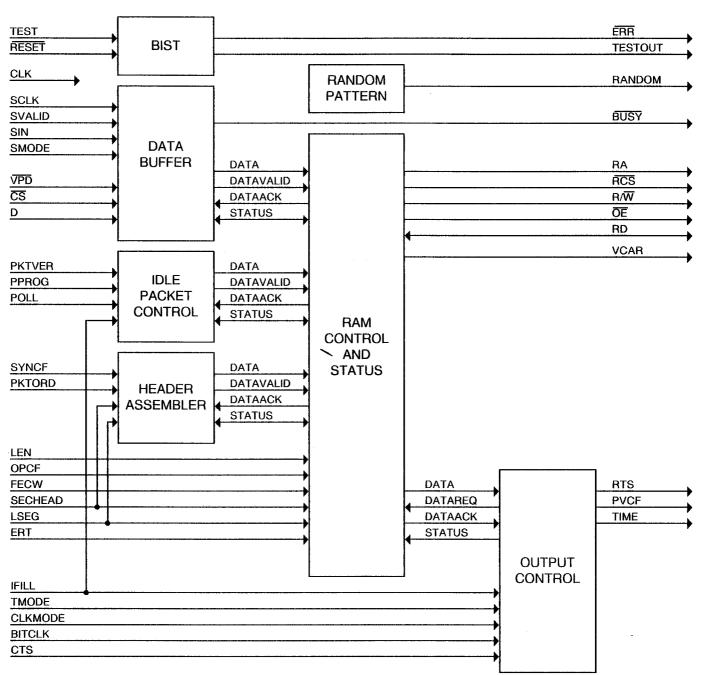

#### FIGURE 3(d) - FUNCTIONAL DIAGRAM

#### FIGURE 3(e) - INPUT/OUTPUT PROTECTION NETWORKS

PAGE 27

ISSUE 1

#### 2. APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:-

- (a) ESA/SCC Generic Specification No. 9000 for Integrated Circuits.

- (b) MIL-STD-883, Test Methods and Procedures for Micro-electronics.

- (c) ESA PSS-04-106, Packet Telemetry Standard.

- (d) ESA PSS-04-107, Packet Telecommand Standard.

#### 3. TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESA/SCC Basic Specification No. 21300 shall apply. In addition, the following abbreviation is used:-

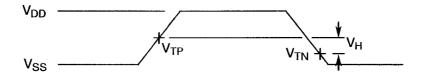

V<sub>IC</sub> - Input/Output Clamp Voltage.

#### 4. REQUIREMENTS

#### 4.1 GENERAL

The complete requirements for procurement of the integrated circuits specified herein are stated in this specification and ESA/SCC Generic Specification No. 9000 for Integrated Circuits. Deviations from the Generic Specification, applicable to this specification only, are listed in Para. 4.2.

Deviations from the applicable Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESA/SCC requirements and do not affect the components' reliability, are listed in the appendices attached to this specification.

#### 4.2 <u>DEVIATIONS FROM GENERIC SPECIFICATION</u>

#### 4.2.1 <u>Deviations from Special In-process Controls</u>

- (a) Para. 5.2.2, Total Dose Irradiation Testing: Shall be performed during qualification and maintenance of qualification.

- (b) Para. 5.2.2, Total Dose Irradiation Testing: Shall be performed during procurement on a lot acceptance basis at the total dose irradiation level specified in the Purchase Order.

#### 4.2.2 Deviations from Final Production Tests (Chart II)

None.

#### 4.2.3 Deviations from Burn-in and Electrical Measurements (Chart III)

(a) Para. 7.1.1(a), "High Temperature Reverse Bias" test and subsequent electrical measurements related to this test shall be omitted.

#### 4.2.4 Deviations from Qualification Tests (Chart IV)

None.

#### 4.2.5 Deviations from Lot Acceptance Tests (Chart V)

None.

PAGE 28

ISSUE 1

#### 4.3 <u>MECHANICAL REQUIREMENTS</u>

#### 4.3.1 <u>Dimension Check</u>

The dimensions of the integrated circuits specified herein shall be checked. They shall conform to those shown in Figure 2.

#### 4.3.2 Weight

The maximum weight of the integrated circuits specified herein shall be 5.0 grammes.

#### 4.3.3 Terminal Strength

The requirements for terminal strength testing are specified in Section 9 of ESA/SCC Basic Specification No. 9000. The test conditions shall be as follows:-

Applied Force: 1.0 ± 0.1 Newtons, 3 bends at 45°.

#### 4.4 MATERIALS AND FINISHES

The materials and finishes shall be as specified herein. Where a definite material is not specified, a material which will enable the integrated circuits specified herein to meet the performance requirements of this specification shall be used. Acceptance or approval of any constituent material does not guarantee acceptance of the finished product.

#### 4.4.1 Case

The case shall be hermetically sealed and have a ceramic body and the lids shall be pre-form soldered.

#### 4.4.2 Lead Material and Finish

The material shall be Type 'D' with Type '2' finish in accordance with the requirements of ESA/SCC Basic Specification No. 23500. (See Table 1(a) for Type Variants).

#### 4.5 MARKING

#### 4.5.1 General

The marking of all components delivered to this specification shall be in accordance with the requirements of ESA/SCC Basic Specification No. 21700. Each component shall be marked in respect of:-

- (a) Lead Identification.

- (b) The SCC Component Number.

- (c) Traceability Information.

#### 4.5.2 <u>Lead Identification</u>

An index shall be located at the top of the package in the position defined in Note 1 to Figure 2 or, alternatively, a tab may be used to identify Pin No. 1. The pin numbering must be read with the index or tab on the left-hand side.

PAGE 29

ISSUE 1

05440050400

#### 4.5.3 The SCC Component Number

Each component shall bear the SCC Component Number which shall be constituted and marked as follows:

|                                                                            | 904400001DD | į |

|----------------------------------------------------------------------------|-------------|---|

| Detail Specification Number                                                |             |   |

| Type Variant (see Table 1(a))                                              |             |   |

| Testing Level (B or C, as applicable) ———————————————————————————————————— |             |   |

| Total Dose Irradiation Level (if applicable)                               |             |   |

The Total Dose Irradiation Level designation shall be added for those devices for which a sample has been successfully tested to the level in question. For these devices, a code shall be added in accordance with the requirements of ESA/SCC Basic Specification No. 22900.

#### 4.5.4 Traceability Information

Each component shall be marked in respect of traceability information in accordance with the requirements of ESA/SCC Basic Specification No. 21700.

#### 4.6 <u>ELECTRICAL MEASUREMENTS</u>

#### 4.6.1 Electrical Measurements at Room Temperature

The parameters to be measured in respect of electrical characteristics are scheduled in Table 2. Unless otherwise specified, the measurements shall be performed at  $T_{amb}$  = +22 ±3 °C.

#### 4.6.2 Electrical Measurements at High and Low Temperatures

The parameters to be measured at high and low temperatures are scheduled in Table 3. The measurements shall be performed at  $T_{amb} = +125(+0-5)$  °C and -55(+5-0) °C respectively.

#### 4.6.3 <u>Circuits for Electrical Measurements</u>

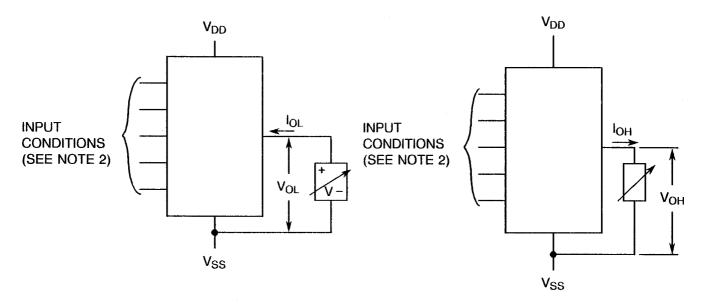

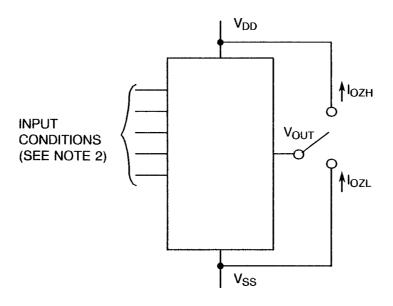

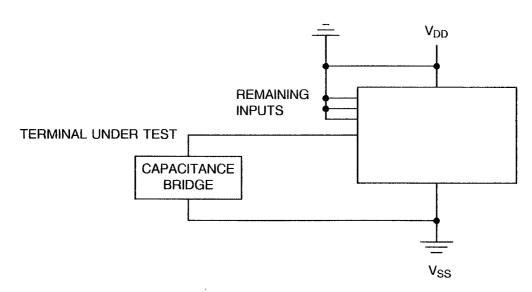

Circuits for use in performing electrical measurements listed in Tables 2 and 3 of this specification are shown in Figure 4.

#### 4.7 BURN-IN TESTS

#### 4.7.1 Parameter Drift Values

The parameter drift values applicable to burn-in are specified in Table 4 of this specification. Unless otherwise stated, measurements shall be performed at  $T_{amb}$  = +22 ±3 °C. The parameter drift values ( $\Delta$ ) applicable to the parameters scheduled, shall not be exceeded. In addition to these drift value requirements, the appropriate limit value specified for a given parameter in Table 2 shall not be exceeded.

#### 4.7.2 Conditions for H.T.R.B. Burn-in

Not applicable.

#### 4.7.3 Conditions for Power Burn-in

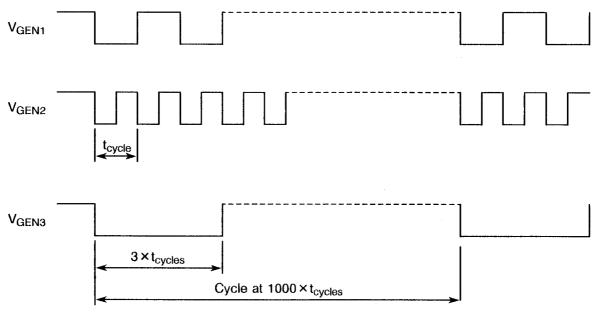

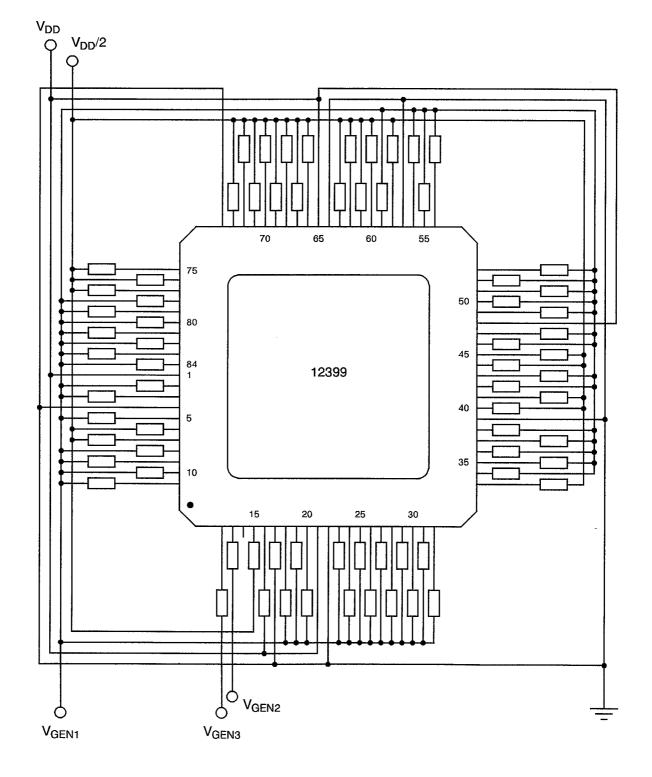

The requirements for Power Burn-in are specified in Section 7 of ESA/SCC Generic Specification No. 9000. The conditions for Power Burn-in shall be as specified in Table 5(b) of this specification.

#### 4.7.4 <u>Electrical Circuits for H.T.R.B. Burn-in</u>

Not applicable.

#### 4.7.5 Electrical Circuits for Power Burn-in

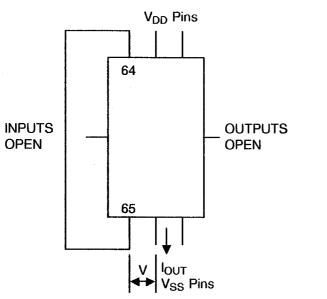

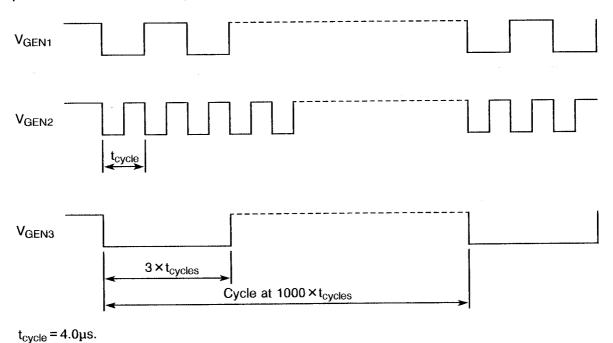

A circuit for use in performing the Power Burn-in test is shown in Figure 5(b) of this specification.

PAGE 30

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS

| No.     | CHARACTERISTICS                                   | SYMBOL          | TEST<br>METHOD | TEST | TEST CONDITIONS                                                                                                                                                                                                        | LIM        | ITS | UNIT |

|---------|---------------------------------------------------|-----------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|------|

| 140.    | CHARACTERISTICS                                   | STWIDOL         | MIL-STD<br>883 | FIG. | (PINS UNDER TEST)                                                                                                                                                                                                      | MIN        | MAX | ONIT |

| to<br>8 | V <sub>SS</sub> and V <sub>DD</sub><br>Continuity | <u>.</u>        | •              | 4(a) | $I_{OUT} = 10\mu$ A<br>$V_{DD} = V_{SS} = 0V$<br>(Pins 1-4-21-22-39-48-57-74<br>to 64 + 65)                                                                                                                            | •          | 100 | mV   |

| 9       | Functional Test 1<br>(Basic)                      | <b>-</b>        | 3014           | •    | Verify Device Operation with Load $V_{IL} = 0V, \ V_{IH} = 5.0V$ $V_{OL} = 1.0V, \ V_{OH} = 4.0V$ $I_{OUT} = \pm 2.0mA$ $C_L = 100pF \pm 20\%$ $V_{DD} = 5.0V, \ V_{SS} = 0V$ $Pattern = Note \ 1$                     | •          | •   | -    |

| 10      | Functional Test 2<br>(Nominal Voltage)            | -               | 3014           | -    | Verify Device Operation with Load $V_{IL}$ , $V_{IH}$ = Note 2 $V_{OL}$ = 1.0V, $V_{OH}$ = 4.0V $I_{OUT}$ = $\pm$ 2.0mA $C_L$ = 100pF $\pm$ 20% $V_{DD}$ = 5.0V, $V_{SS}$ = 0V Pattern = Note 2                        | -          | -   | -    |

| 11      | Functional Test 3<br>(High Voltage)               | -               | 3014           | -    | Verify Device Operation with Load $V_{IL},\ V_{IH} = \text{Note 2}$ $V_{OL} = 1.0V,\ V_{OH} = 4.5V$ $I_{OUT} = \pm 2.0\text{mA}$ $C_L = 100\text{pF} \pm 20\%$ $V_{DD} = 5.5V,\ V_{SS} = 0V$ $Pattern = \text{Note 2}$ |            | -   | -    |

| 12      | Functional Test 4<br>(Low Voltage)                | -               | 3014           | -    | Verify Device Operation with Load $V_{IL}$ , $V_{IH}$ = Note 2 $V_{OL}$ = 1.0V, $V_{OH}$ = 3.5V $I_{OUT}$ = $\pm$ 2.0mA $C_L$ = 100pF $\pm$ 20% $V_{DD}$ = 4.5V, $V_{SS}$ = 0V Pattern = Note 2                        | -          | -   | -    |

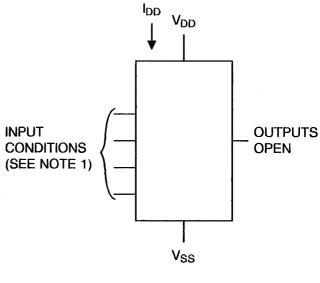

| 13      | Quiescent Current                                 | I <sub>DD</sub> | 3005           | 4(b) | $V_{IL} = 0V$ , $V_{IH} = 5.5V$<br>$V_{DD} = 5.5V$ , $V_{SS} = 0V$<br>All Outputs Open<br>Note 3<br>(Pins 1 + 21 + 48 + 65)                                                                                            | . <b>-</b> | 0.5 | mA   |

PAGE 31

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS (CONT'D)

| No               | CHARACTERISTICS                | CVAADOL          | TEST<br>METHOD | TEST | TEST CONDITIONS                                                                                                                                                                                                                                                                   | LIM | ITS  | LINUT    |

|------------------|--------------------------------|------------------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|----------|

| No.              | CHARACTERISTICS                | SYMBOL           | MIL-STD<br>883 | FIG. | (PINS UNDER TEST)                                                                                                                                                                                                                                                                 | MIN | MAX  | UNIT     |

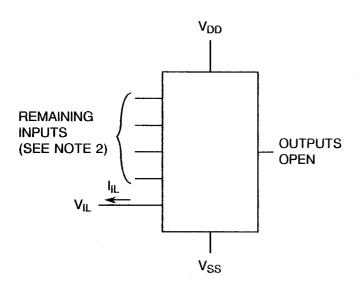

| 14<br>to<br>54   | Input Current<br>Low Level     | Ę                | 3009           | 4(c) | $\begin{split} &V_{IN} \text{ (Under Test)} = 0V \\ &V_{IN} \text{ (Remaining Inputs)} = 5.5V \\ &V_{DD} = 5.5V, V_{SS} = 0V \\ &(\text{Pins 2-3-5-8-9-10-11-12-13-16-17-18-19-20-23-24-25-26-27-28-29-30-31-32-34-35-36-37-38-42-43-46-47-49-78-79-80-81-82-83-84)} \end{split}$ | -   | -1.0 | μΑ       |

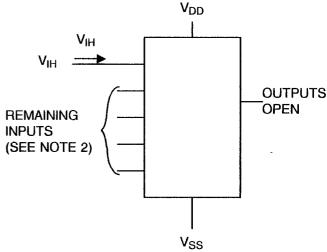

| 55<br>to<br>95   | Input Current<br>High Level    | Ин               | 3009           | 4(d) | $V_{IN}$ (Under Test) = 5.5V $V_{IN}$ (Remaining Inputs) = 0V $V_{DD}$ = 5.5V, $V_{SS}$ = 0V (Pins 2-3-5-8-9-10-11-12-13-16-17-18-19-20-23-24-25-26-27-28-29-30-31-32-34-35-36-37-38-42-43-46-47-49-78-79-80-81-82-83-84)                                                         | -   | 1.0  | μΑ       |

| 96<br>to<br>127  | Output Voltage<br>Low Level    | V <sub>OL</sub>  | 3007           | 4(e) | $V_{IL}$ , $V_{IH}$ = Note 2<br>$I_{OL}$ = 4.0mA<br>$V_{DD}$ = 4.5V, $V_{SS}$ = 0V<br>Note 4<br>(Pins 6-7-15-33-40-41-44-45-50-51-52-53-54-55-56-58-59-60-61-62-63-66-67-68-69-70-71-72-73-75-76-77)                                                                              | -   | 0.4  | <b>V</b> |

| 128<br>to<br>159 | Output Voltage<br>High Level 1 | V <sub>ОН1</sub> | 3006           | 4(f) | $V_{IL}$ , $V_{IH}$ = Note 2<br>$I_{OL}$ = -4.0mA<br>$V_{DD}$ = 4.5V, $V_{SS}$ = 0V<br>Note 4<br>(Pins 6-7-15-33-40-41-44-45-50-51-52-53-54-55-56-58-59-60-61-62-63-66-67-68-69-70-71-72-73-75-76-77)                                                                             | 3.9 | -    | >        |

| 160<br>to<br>191 | Output Voltage<br>High Level 2 | V <sub>OH2</sub> | 3006           | 4(f) | $\begin{split} &V_{IL},\ V_{IH} = \text{Note 2} \\ &I_{OL} = -0.5\text{mA} \\ &V_{DD} = 4.5\text{V},\ V_{SS} = 0\text{V} \\ &\text{Note 4} \\ &(\text{Pins 6-7-15-33-40-41-44-45-50-51-52-53-54-55-56-58-59-60-61-62-63-66-67-68-69-70-71-72-73-75-76-77)} \end{split}$           | 4.2 | -    | >        |

PAGE 32

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS (CONT'D)

| No.              | CHARACTERISTICS                                                 | SYMBOL            | TEST<br>METHOD | TEST | TEST CONDITIONS                                                                                                                                            | LIM | ITS | UNIT        |

|------------------|-----------------------------------------------------------------|-------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------|

| NO.              | CHARACTERISTICS                                                 | STIVIBUL          | MIL-STD<br>883 | FIG. | (PINS UNDER TEST)                                                                                                                                          | MIN | MAX | UNIT        |

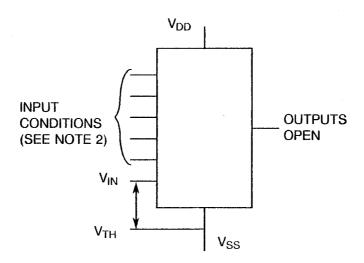

| 192<br>to<br>209 | Threshold Voltage<br>Low Level 1<br>(TTL Inputs)                | V <sub>THN1</sub> | -              | 4(g) | V <sub>DD</sub> = 4.5V, V <sub>SS</sub> = 0V<br>(Pins 2-3-5-50-51-52-53-54-<br>55-56-59-78-79-80-81-82-83-<br>84)                                          | 0.8 | 1   | V           |

| 210<br>to<br>227 | Threshold Voltage<br>High Level 1<br>(TTL Inputs)               | V <sub>THP1</sub> | •              | 4(g) | V <sub>DD</sub> = 4.5V, V <sub>SS</sub> = 0V<br>(Pins 2-3-5-50-51-52-53-54-<br>55-56-59-78-79-80-81-82-83-<br>84)                                          | -   | 2.0 | ٧           |

| 228<br>to<br>257 | Threshold Voltage<br>Low Level 2<br>(CMOS Inputs)               | V <sub>THN2</sub> | •              | 4(g) | $V_{DD}$ = 4.5V, $V_{SS}$ = 0V<br>(Pins 8-9-10-11-13-16-17-18-19-20-23-24-25-26-27-28-29-30-31-32-34-35-36-37-38-42-43-46-47-49)                           | 1.3 | -   | <b>V</b>    |

| 258<br>to<br>287 | Threshold Voltage<br>High Level 2<br>(CMOS Inputs)              | V <sub>THP2</sub> | -              | 4(g) | V <sub>DD</sub> = 4.5V, V <sub>SS</sub> = 0V<br>(Pins 8-9-10-11-13-16-17-18-<br>19-20-23-24-25-26-27-28-29-<br>30-31-32-34-35-36-37-38-42-<br>43-46-47-49) | -   | 3.2 | ٧           |

| 288              | Threshold Voltage<br>Low Level 3<br>(SCHMITT Trigger<br>Input)  | V <sub>THN3</sub> | -              | 4(g) | V <sub>DD</sub> = 4.5V, V <sub>SS</sub> = 0V<br>(Pin 12)                                                                                                   | 1.0 | 2.8 | V           |

| 289              | Threshold Voltage<br>High Level 3<br>(SCHMITT Trigger<br>Input) | V <sub>THP3</sub> | -              | 4(g) | $V_{DD} = 4.5V$ , $V_{SS} = 0V$ (Pin 12)                                                                                                                   | 1.5 | 3.3 | <b>&gt;</b> |

| 290              | Hysteresis Voltage                                              | V <sub>H</sub>    | -              | 4(h) | $V_{DD} = 4.5V, V_{SS} = 0V$<br>Note 5<br>(Pin 12)                                                                                                         | 0.5 | ı   | ٧           |

| 291<br>to<br>308 | Threshold Voltage<br>Low Level 4<br>(TTL Inputs)                | V <sub>THN4</sub> | -              | 4(g) | V <sub>DD</sub> = 5.5V, V <sub>SS</sub> = 0V<br>(Pins 2-3-5-50-51-52-53-54-<br>55-56-59-78-79-80-81-82-83-<br>84)                                          | 0.8 | •   | V           |

| 309<br>to<br>326 | Threshold Voltage<br>High Level 4<br>(TTL Inputs)               | V <sub>THP4</sub> | •              | 4(g) | V <sub>DD</sub> = 5.5V, V <sub>SS</sub> = 0V<br>(Pins 2-3-5-50-51-52-53-54-<br>55-56-59-78-79-80-81-82-83-<br>84)                                          | -   | 2.0 | V           |

PAGE 33

ISSUE 1

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS (CONT'D)

| No               | CHARACTERISTICS                                                 | SYMBOL            | TEST<br>METHOD | TEST | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LIM | ITS      | UNIT |

|------------------|-----------------------------------------------------------------|-------------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|------|

| No.              | CHARACTERISTICS                                                 | STIMBOL           | MIL-STD<br>883 | FIG. | (PINS UNDER TEST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MIN | MAX      | UNIT |

| 327<br>to<br>366 | Threshold Voltage<br>Low Level 5<br>(CMOS Inputs)               | V <sub>THN5</sub> | -              | 4(g) | V <sub>DD</sub> = 5.5V, V <sub>SS</sub> = 0V<br>(Pins 8-9-10-11-13-16-17-18-<br>19-20-23-24-25-26-27-28-29-<br>30-31-32-34-35-36-37-38-42-<br>43-46-47-49)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.7 | •<br>• • | V    |