# ESA-QCA9950T-C

MATRA MARCONI SPACE

Ref :AUT/PRO/940/97 Issue : 01 Rev. :

Date : 20/10/97 Page : i

# EUROPEAN SPACE AGENCY CONTRACT REPORT

The work described in this report was done under ESA contract.

Responsibility for the contents resides in the author or organization that prepared it.

Title

MT4LC4M4B1DJ-6, 16 MBIT DRAM FROM MICRON

# TOTAL IONISING DOSE CHARACTERIZATION TEST REPORT

# ESA/ESTEC Contract No. 11755/95/NL/NB-WO1/CO1

| . 22                        | Name and Function                             | Date     | Signature |

|-----------------------------|-----------------------------------------------|----------|-----------|

| Prepared by :               | SALMINEN A. Project manager                   | 20/10/97 | Sto falin |

| Verified by :               | DOUGN B. (MMS)                                | 01112197 | Be        |

| Approved by :               | CARLOTTI C (MMS)                              | 2/12/57  |           |

| Authorized by:              | HARBOE SØRENSEN R.<br>ESTEC Technical Officer |          |           |

| Application authorized by : |                                               |          |           |

| Document type | Nb WBS | Summary: Low voltage memories were tested under total ionising dose irradiation to study the effect of supply voltage |

|---------------|--------|-----------------------------------------------------------------------------------------------------------------------|

|               |        | on the radiation sensitivity. This report presents the results obtained on 16 Mbit Micron DRAMs.                      |

Ref :AUT/PRO/940/97

Issue :01 Rev. : Date :20/10/97

Page :ii

### SUMMARY OF RESULTS

## **Test sample characteristics:**

| Part Name:     | MT4LC4M4B1DJ-6       | <b>Function:</b> | 4 M x 4 DRAM          |

|----------------|----------------------|------------------|-----------------------|

| Technology:    | CMOS, 0.5 μm         | Package:         | 24/26-pin plastic SOJ |

| Manufacturer : | Micron               | Location:        | USA                   |

| Sample size :  | 3 (4.5 V), 3 (3.3 V) | Date Code :      | 9640                  |

# **TID test results**

### Functional test

The following table summarises the failure doses at the first error and at the 100th error:

| S/N   | $V_{CC}$ | Dose at 1st error | Error | Dose at 100th error | % of |

|-------|----------|-------------------|-------|---------------------|------|

| . 61* | v        | krad(Si)          | mode  | krad(Si)            | 0→1  |

| 15    | 4.5      | 59.8              | 1→0   | >61.6               | -    |

| 16    | 4.5      | 47.0              | 1→0   | 53.0                | 75   |

| 17    | 4.5      | 46.4              | 0→1   | 53.0                | 74   |

| 33    | 3.3      | 49.0              | 0→1   | 58.1                | 61   |

| 34    | 3.3      | 53.1              | 1→0   | >59.9               | -    |

| 35    | 3.3      | 58.4              | 0→1   | >59.9               | -    |

No device recovered functionally in the high temperature annealing of 168 h at 85°C.

### Functional test conclusion

The results of these experiments demonstrate that on the average 16 Mbit DRAM MT4LC4M4B1DJ-6 (60ns) from Micron, when biased at 4.5 V, is more sensitive to ionising radiation than biased at 3.3 V in terms of the first error detected. This correlates with the average dose at 100th error: biased at 3.3 V the better radiation tolerance is reached compared to the 4.5 V biasing mode.

Ref :AUT/PRO/940/97 Issue :01 Rev. :

Issue :01 Rev. : Date :20/10/97

Page :iii

## Parametric test

The following table summarises the average dose levels for both bias at which sensitive parameters have drifted 20%:

| Parameter                | Dose Level<br>V <sub>CC</sub> = 4.5 V | Dose Level $V_{CC} = 3.3 \text{ V}$ |  |

|--------------------------|---------------------------------------|-------------------------------------|--|

| Standby supply current   | 35 krad(Si)                           | 40 krad(Si)                         |  |

| Operating supply current | >60 krad(Si)                          | >60 krad(Si)                        |  |

## Parametric test conclusion

The results of these experiments demonstrate that 16 Mbit DRAM MT4LC4M4B1DJ-6 (60ns) from Micron biased at 4.5 V is more sensitive to ionising radiation than at 3.3 V bias.

Ref

:AUT/PRO/940/97

Issue Date :01 Rev. : :20/10/97

Page :iv

# DOCUMENT CHANGE LOG

| Issue/<br>Revision | Date     | Modification Nb | Modified pages | Observations     |

|--------------------|----------|-----------------|----------------|------------------|

| 1                  | 20/10/97 |                 |                | Original Edition |

|                    |          |                 |                |                  |

|                    |          |                 |                | •                |

|                    |          |                 |                |                  |

|                    |          |                 |                |                  |

|                    |          |                 |                |                  |

|                    |          |                 |                |                  |

|                    |          |                 |                |                  |

| ,                  |          |                 |                |                  |

|                    | -        |                 |                |                  |

|                    |          |                 |                |                  |

|                    |          |                 |                |                  |

|                    |          |                 |                |                  |

|                    |          |                 |                | ·                |

|                    |          |                 |                |                  |

|                    |          |                 |                |                  |

|                    |          |                 |                |                  |

|                    |          |                 | ·              |                  |

|                    |          |                 |                |                  |

Ref :AUT/PRO/940/97

Issue :01 Rev. : Date :20/10/97

Page :v

# PAGE ISSUE RECORD

Issue of this document comprises the following pages at the issue shown

| Page | Issue/<br>Revision |

|------|--------------------|------|--------------------|------|--------------------|------|--------------------|------|--------------------|------|--------------------|

| All  | 1                  |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    | i    |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      | 1                  |      |                    |      |                    |      |                    |      |                    |

|      | . 221              |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    |      |                    |      |                    |      |                    |      |                    |

|      |                    |      |                    | ļ    |                    |      |                    |      |                    |      |                    |

Ref Issue :AUT/PRO/940/97

Date

:01 Rev. : :20/10/97

Page :vi

# **DISTRIBUTION LIST**

|                    |     | Overal | Summary            |   |

|--------------------|-----|--------|--------------------|---|

|                    |     | Action | Action Information |   |

| R. HARBOE-SØRENSEN | ESA | X      |                    |   |

| B. DOUCIN          | MMS |        | X                  |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

| • ser              |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    | • |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

|                    |     |        |                    |   |

Ref

: AUT/PRO/940/97

Issue : 01 Rev. : Date : 20/10/97

age : 1

# TABLE OF CONTENTS

| 1. INTRODUCTION                             | 2  |

|---------------------------------------------|----|

| 2. REFERENCE DOCUMENTS                      | 2  |

| 3. PART DETAILS                             | 3  |

| 3.1. DEVICE IDENTIFICATION                  | 3  |

| 3.2. TECHNICAL INFORMATION                  | 4  |

| 4. TEST DESCRIPTION                         | 5  |

| 4.1. IRRADIATION FACILITY                   | 5  |

| 4.2. TID TEST SET-UP                        | 5  |

| 5. TOTAL IONISING DOSE EXPERIMENTAL RESULTS | 8  |

| 5.1. TID IRRADIATION TEST SEQUENCE          | 8  |

| 5.2. TID TEST RESULTS                       | 9  |

| 6 CONCLUSION                                | 11 |

Ref : AUT/PRO/940/97

Issue : 01 Rev. : Date : 20/10/97

Page: 2

### 1. INTRODUCTION

The aim of this work is to investigate radiation effects in low voltage technologies. The study is focused on memory devices, which require lower voltage to achieve higher integration. Parts selected consists of SRAMs (1 Mbit, 2 types), DRAMs (16 Mbit, 2 types), and FLASH memories (8 Mbit, 2 types).

The object of this document is to describe the irradiations performed on the Micron 16 Mbit MT4LC4M4B1DJ-6 (60ns), in order to measure the influence of two different supply voltage levels on the total ionising dose sensitivity.

Irradiations were performed in March 1997 (10<sup>th</sup>-17<sup>th</sup>) according to the procedures referenced in the following paragraph.

This work was performed in the frame of the WO1/CO1 for ESTEC Contract n°11755/95/NL/NB.

# 2. REFERENCE DOCUMENTS

- [1] ESA/SCC 22900-4 ESA Basic Specification for Total Dose Steady-State Irradiation

- [2] Micron Manufacturer Data Sheet

- [3] Description of the VTT memory tester, AUT/PRO/76/96 (in Finnish)

- [4] "Radiation effects in 5V and advanced lower voltage DRAMs" D.C. Shaw, IEEE Trans. On Nucl. Sci., Dec. 94, No6, p2452.

Ref

AUT/PRO/940/97

Issue Date : 01 Rev.: : 20/10/97

Page

: 3

#### 3. PART DETAILS

3.1. DEVICE IDENTIFICATION

3.1.1. References

Type

MT4LC4M4B1DJ-6

Manufacturer:

Micron USA

Place Packaging

24/26-pin plastic SOJ

3.1.2. Function

4 M x 4 bit DRAM (60 ns)

3.1.3. Technology

CMOS (See next page for further details)

3.1.4. Part Procurement

Origin

VTT Automation, Finland

Level

: Standard Level

Temperature range

-25°C, +85°C (Industrial)

Date code

9640

Screening

: /

Sample size

3 (biased at 4.5 V), 3 (biased at 3.3 V)

Manufacturer Marking

MT4LC4M4B1DJ-6 9640 F USA CR67

Detailed specifications

Manufacturer Data sheet

### 3.1.5. Previous TID details/history

No radiation data on this device. Another 16 Mbit version from Micron was proviously tested, and exhibited a lower Total Dose tolerance (functional failure at 30 krad), but the tests were performed at high dose rate (>72 krad/h) [4].

Ref : AUT/PRO/940/97

Issue : 01 Rev.: Date : 20/10/97

Page: 4

### 3.2. TECHNICAL INFORMATION

The 16 Mbit MT4LC4M4B1DJ-6 DRAM from Micron is a device that can be operated at 3.3V or at 4.5V.

The functionality and the parametric integrity of the devices were examined prior to irradiation. No screening nor burn-in were carried out during this study.

#### **General** information

| Name                   | Micron MT4LC4M4B1DJ-6          |  |  |

|------------------------|--------------------------------|--|--|

| Package Marking        | MT4LC4M4B1DJ-6 9640 F USA CR67 |  |  |

| Access time/ns at 4.5V | 60                             |  |  |

| Temperature range/°C   | -25, +85                       |  |  |

| Organisation           | 4 M x 4                        |  |  |

| Supply Voltage/V       | 3.0 - 4.6                      |  |  |

### Technology ...

| Name            | Micron MT4LC4M4B1DJ-6 |  |  |  |

|-----------------|-----------------------|--|--|--|

| CMOS            | yes                   |  |  |  |

| Mask            | D28                   |  |  |  |

| Epitaxial layer | No (bulk)             |  |  |  |

| Design rules    | 0.35 μ                |  |  |  |

| Die size        | 5.6 mm x 10.2 mm      |  |  |  |

| Cell size       | 0.875 μm x 1.75 μm    |  |  |  |

<sup>\*</sup> The missing information was unsuccessfully required from the manufacturer.

<sup>\*</sup> Two other versions followed the D28 version: D42 and D52 (0.3  $\mu m$ ). The D28 version is no longer commercialized.

Issue : 01 Rev.: Date : 20/10/97

Page: 5

#### 4. TEST DESCRIPTION

4.1. IRRADIATION FACILITY

Name

MMS Cobalt 60-source, model Shepherd 484

Location

Matra Marconi Space France

37, avenue Louis Bréguet

78146 VELIZY-VILLACOUBLAY Cedex

France

Activity

< 8.9 curies.

Calibration

10/03/97.

#### 4.2. TID TEST SET-UP

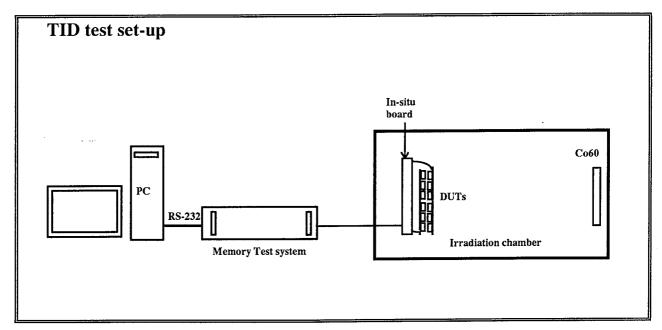

Fig 4.1. Description of the TID test set-up.

The DUTs were soldered on small PCB's with pin headers. They were mounted on the two large PCB's that were biased at 4.5 V and 3.3 V. The distance between 4.5 V and 3.3 V devices were 2 mm from package to package. The difference in dose rates was taken into account when computing the doses received by the devices.

The device under test was selected by a chip select logic located in the In-situ board. The supply voltage was provided by the memory tester. A complete description of the memory tester is given in [3].

The test flow chart is given in fig. 4.2.

Issue : 01 Rev. : Date : 20/10/97

Page: 6

# Test sequence for DRAM Write sequence Set address=0 Set parameters of selected DUT Refresh one row Write DUT with CB-pattern Write pattern to address Increase address Read DUT and compare with CB-pattern. . No End of DUT? Yes Write DUT with Continue test /CB-pattern Read sequence Set address=0 Read DUT and compare with /CB-pattern Refresh one row Continue test for another Read current address DUT and compare it Yes Error? Reread current address No Write correct pattern Increase address Read current address Νo End of DUT? Store error to logfile Yes

Fig. 4.2. The test flow chart of an individual device with write and read sequencies.

Continue test

Issue : 01 Rev. : Date : 20/10/97

Page: 7

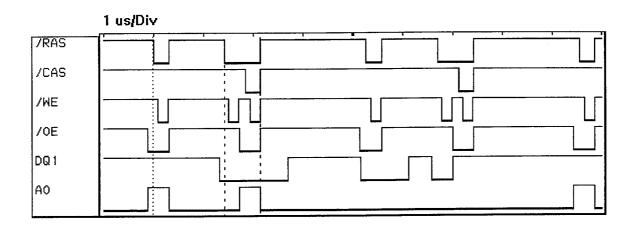

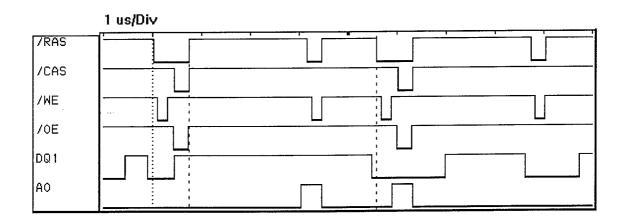

The write and read cycles during functional test were as follows:

Fig. 4.3. Write Cycle of MICRON DRAM during functional test.

Fig. 4.4. Read Cycle of MICRON DRAM during functional test.

Issue : 01 Rev. : Date : 20/10/97

Page: 8

### 5. TOTAL IONISING DOSE EXPERIMENTAL RESULTS

### 5.1. TID IRRADIATION TEST SEQUENCE

During irradiations all the devices were functionally tested 3 times per hour automatically in the exposure chamber, and the results were stored on a hard disk of the measuring computer. The memory test started with the write of a CB (checkerboard) pattern to the memory device. Thereafter the memory contents of the device was read and it was compared to the original pattern. After this the memory was tested with a complementaly CB pattern in an identical way. During the irradiation, the memory contents was the complementaly CB pattern. Therefore, this represents the worst case testing.

If errors were encountered, the corrupted data was immediately reread and rewritten with the original pattern. The write operation was verified with another read. In this way peripheral circuitry errors, memory cell errors, write errors and stuck bits can be indicated. Due to the limitation of the measuring computer, the maximum number of recorded corrupted bytes was set to 100. TTL levels were applied in control, address and data signals. 4.5 V bias was applied to devices s/n 15-17 and 3.3 V bias was applied to devices s/n 33-35.

In the time between the irradiations, the parameters were measured remotely at the end of each step within two hours with the VTT parametric tester in another room. Except the measurement, the devices were unbiased during this time. The resolution of the voltage measurements was 1.2 mV. The irradiation was accomplished in seven steps. The average dose rates were 420 rad(Si)/h and 410 rad(Si)/h for 4.5 V and 3.3 V devices, correspondingly. The dose rates and cumulative doses with durations of each irradiation are given in table 5.1.

Table 5.1. Dose rates, durations and cumulative doses for 4.5 V and 3.3 V Micron DRAMs.

| Step | Dose rate 4.5 V<br>rad(Si)/h | Dose rate 3.3 V<br>rad(Si)/h | Duration<br>h | Total Dose 4.5 V<br>krad(Si) | Total Dose 3.3 V<br>krad(Si) |

|------|------------------------------|------------------------------|---------------|------------------------------|------------------------------|

| 1    | 262.0                        | 258.1                        | 20.00         | 5.2                          | 5.1                          |

| 2    | 327.5                        | 317.3                        | 19.00         | 11.5                         | 11.2                         |

| 3    | 471.6                        | 458.1                        | 8.00          | 15.2                         | 14.8                         |

| 4    | 471.6                        | 458.1                        | 12.00         | 20.9                         | 20.4                         |

| 5    | 471.6                        | 458.1                        | 19.17         | 29.9                         | 29.1                         |

| 6    | 471.6                        | 458.1                        | 7.18          | 33.3                         | 32.4                         |

| 7    | 471.6                        | 458.1                        | 60.00         | 61.6                         | 59.9                         |

After the last irradiation step and parametric measurement, the devices were put into a heat chamber for an annealing period of 168 h at 85°C. The devices were functionally tested 3 times per hour. The test set-up for the Micron DRAMs was the same one as during irradiation.

Issue : 01 Rev.: Date : 20/10/97

Page: 9

#### 5.1.1. Problems encountered/Discussion

No specific problem was encountered during irradiations.

#### 5.2. TID TEST RESULTS

#### **Functional** test

The following table summarises the failure doses in the functional test:

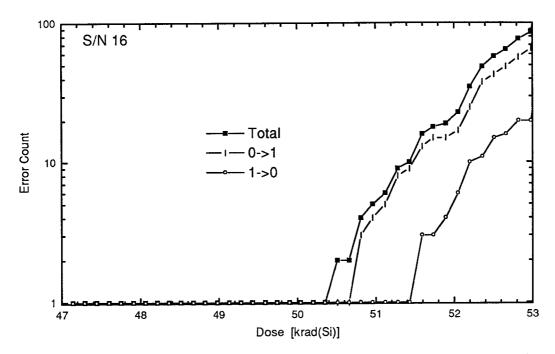

Table 5.2. Failure doses at first and 100th errors with error modes.

| S/N | V <sub>cc</sub> | Dose at 1 error | Error | Dose at 100th error | % of | Annealing              | Remarks            |

|-----|-----------------|-----------------|-------|---------------------|------|------------------------|--------------------|

|     | v               | krad(Si)        | mode  | krad(Si)            | 0→1  |                        |                    |

| 15  | 4.5             | 59.8            | 1→0   | >61.6               |      | No functional recovery | 1 error: 1→0       |

| 16  | 4.5             | 47.0            | 1→0   | 53.0                | 75   | No functional recovery |                    |

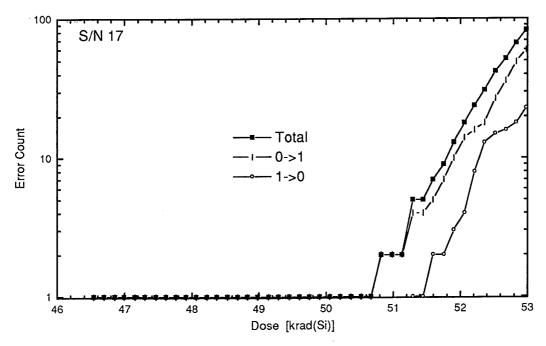

| 17  | 4.5             | 46.4            | 0→1   | 53.0                | 74   | No functional recovery |                    |

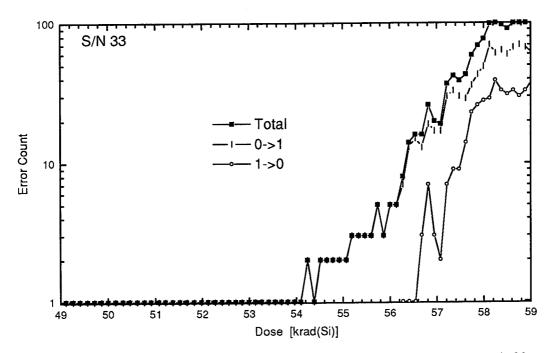

| 33  | 3.3             | 49.0            | 0→1   | 58.1                | 61   | No functional recovery |                    |

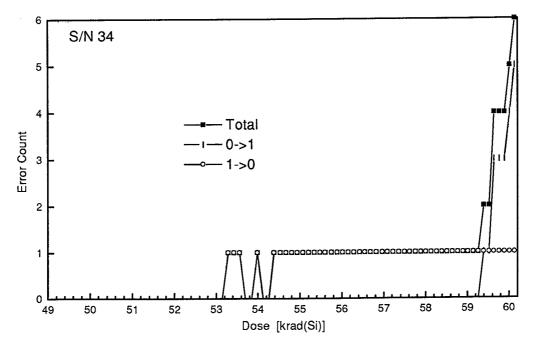

| 34  | 3.3             | 53.1            | 1→0   | >59.9               |      | No functional recovery | 6 errors; 5: 0→1   |

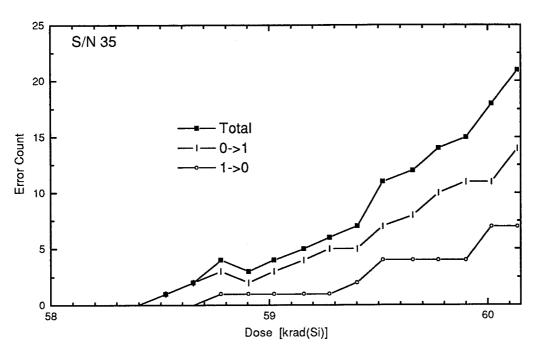

| 35  | 3.3             | 58.4            | 0→1   | >59.9               |      | No functional recovery | 21 errors; 14: 0→1 |

The average first error dose was 53.5 krad(Si) for 3.3 V bias and 51.1 krad(Si) for 4.5 V bias. One device of 4.5 V bias and two devices of 3.3 V bias did not fail within the maximum dose. The lower bias tends to increase to dose tolerance at both error level.

At 4.5 V bias the first error mode was the transition  $1\rightarrow0$  in two devices. At 3.3 V bias the first error mode was the transition  $0\rightarrow1$  in two devices.

All devices failed in the parametric test after the last irradiation step. No device recovered functionally in the high temperature annealing of 168 h at 85°C.

Detailed functional test results are given in appendices 1 and 2.

#### **Functional test conclusion**

The results of these experiments demonstrate that on the average 16 Mbit DRAM MT4LC4M4B1DJ-6 (60ns) from Micron, when biased at 4.5 V, is more sensitive to ionising radiation than biased at 3.3 V in terms of the first error detected. This correlates with the average dose at 100th error: biased at 3.3 V the better radiation tolerance is reached compared to the 4.5 V biasing mode.

Ref

AUT/PRO/940/97

Issue Date 01 Rev.: 20/10/97

age : 10

#### Parametric test

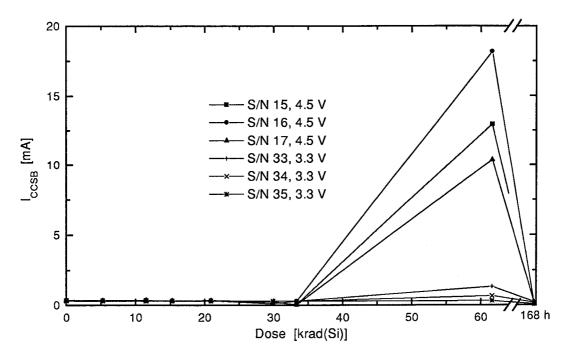

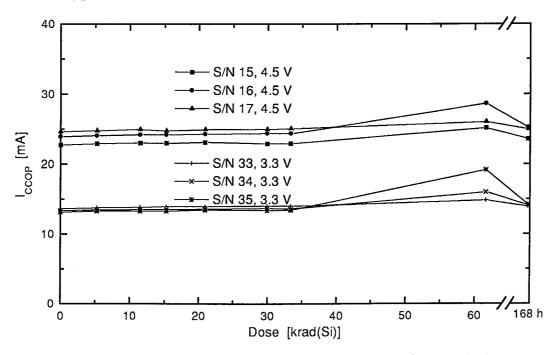

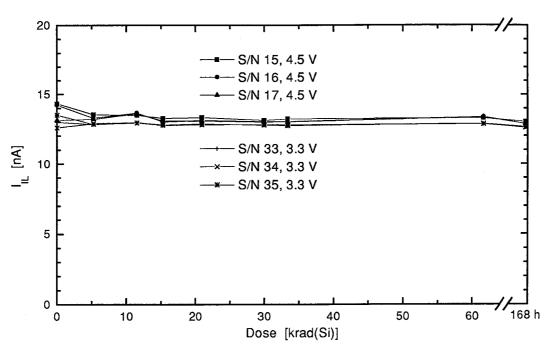

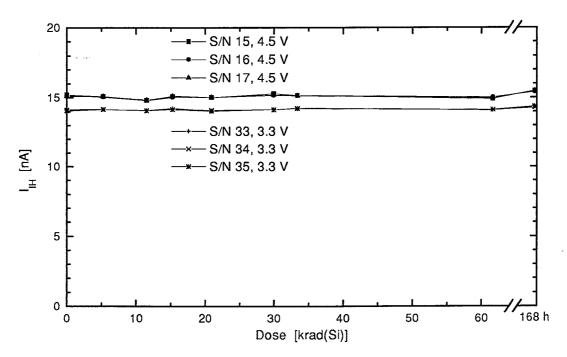

The table 5.3 summarises the average dose levels at which parameters have drifted 20% and the average relative recovered values after 168 h at 85°C annealing for both bias. The average relative recovery indicates the recovered value after annealing divided by the preirradiated value.

Table 5.3. Average dose levels at 20% drift and relative recovery after annealing.

| Symbol            | Parameter                                                   | Dose Leve                    | el/krad(Si)                  | Parametric recovery      |                          |

|-------------------|-------------------------------------------------------------|------------------------------|------------------------------|--------------------------|--------------------------|

|                   |                                                             | $V_{\rm CC} = 4.5 \text{ V}$ | $V_{\rm CC} = 3.3 \text{ V}$ | $V_{CC} = 4.5 \text{ V}$ | $V_{CC} = 3.3 \text{ V}$ |

| I <sub>CCSB</sub> | Standby Supply Current                                      | 35                           | 40                           | 0.2                      | 0.5                      |

| I <sub>CCOP</sub> | Operating Supply Current                                    | >60                          | >60                          | 1.0                      | 1.0                      |

| $I_{IL}$          | Input Current Low Level                                     | >60                          | >60                          | 0.9                      | 1.0                      |

| $I_{\mathrm{IH}}$ | Input Current High Level                                    | >60                          | >60                          | 1.0                      | 1.0                      |

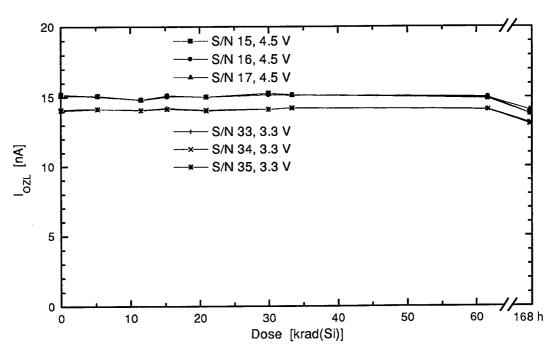

| I <sub>OZL</sub>  | Output Leakage Current High<br>Impedance Low level Applied  | >60                          | >60                          | 0.9                      | 0.9                      |

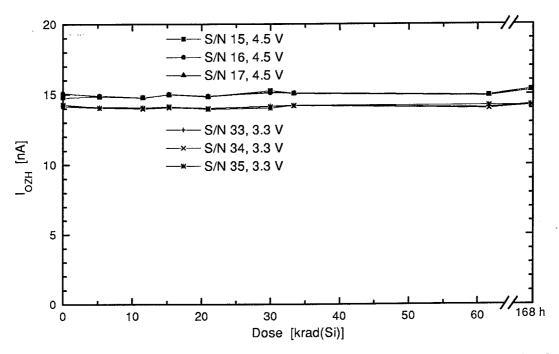

| I <sub>OZH</sub>  | Output Leakage Current High<br>Impedance High Level Applied | >60                          | >60                          | 1.0                      | 1.0                      |

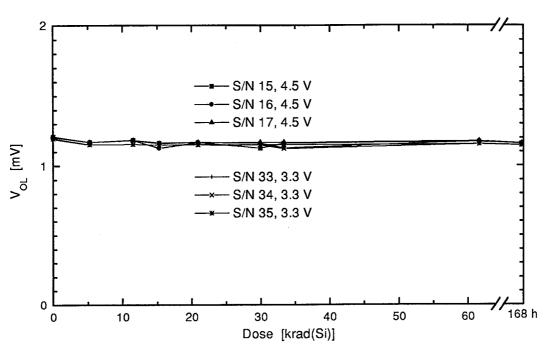

| V <sub>OL</sub>   | Output Voltage Low Level                                    | >60                          | >60                          | 1.0                      | 1.0                      |

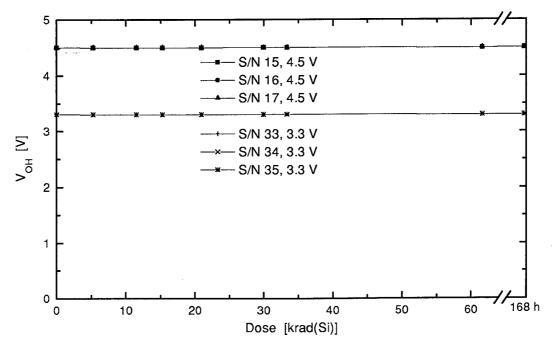

| V <sub>OH</sub>   | Output Voltage High Level                                   | >60                          | >60                          | 1.0                      | 1.0                      |

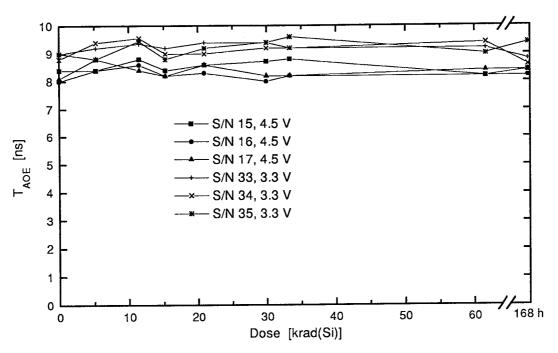

| T <sub>AOE</sub>  | Output Enable Access Time                                   | >60                          | >60                          | 1.0                      | 1.0                      |

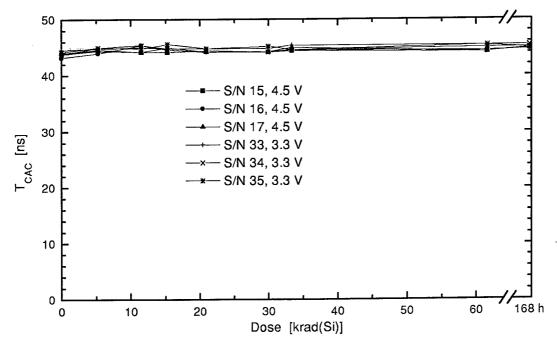

| T <sub>ACS</sub>  | Chip Select Access Time                                     | >60                          | >60                          | 1.0                      | 1.0                      |

The parameters were very stable to 30 krad at both bias modes. Except  $I_{CCSB}$ , the parameters are almost insensitive to total dose up to the maximum dose. 3.3 V bias slightly increases the tolerance compared to the higher one.

After annealing,  $I_{\text{CCSB}}$  recovered to a value less than the preirradiated one at both bias modes.

Parametric test results are given as graphs in appendix 3.

#### Parametric test conclusion

The results of these experiments demonstrate that 16 Mbit DRAM MT4LC4M4B1DJ-6 (60ns) from Micron DRAM biased at 4.5 V is more sensitive to ionising radiation than when biased at 3.3 V.

Ref :

AUT/PRO/940/97

Issue : 01 Rev. : Date : 20/10/97

age : 11

#### 6. CONCLUSION

Ionising dose tests were performed on the 16 Mbit DRAM MT4LC4M4B1DJ-6 from Micron with 3.3 V and 4.5 V bias. The dose tolerance of the device is good.

The results of the functional tests demonstrate that MT4LC4M4B1DJ-6, when biased at 4.5 V, is more sensitive to ionising radiation than biased at 3.3 V in terms of the first error detected. The results of the parametric tests indicate that MT4LC4M4B1DJ-6, when biased at 4.5 V, is more sensitive to ionising radiation than biased at 3.3 V in terms of the parametric drifts.

Issue : 01 Rev. : Date : 20/10/97 Page : 12

## APPENDIX 1. Functional test results for 4.5 V Micron devices.

Fig. 1. Error count with modes  $0\rightarrow1$  and  $1\rightarrow0$  versus dose in 4.5 V Micron DRAM s/n 16.

Fig. 2. Error count with modes  $0\rightarrow 1$  and  $1\rightarrow 0$  versus dose in 4.5 V Micron DRAM s/n 17.

Issue : 01 Rev. : Date : 20/10/97

Page : 13

## APPENDIX 2. Functional test results for Micron 3.3 V devices.

Fig. 1. Error count with modes  $0\rightarrow1$  and  $1\rightarrow0$  versus dose in 3.3 V Micron DRAM s/n 33.

Fig. 2. Error count with modes  $0\rightarrow 1$  and  $1\rightarrow 0$  versus dose in 3.3 V Micron DRAM s/n 34.

Issue : 01 Rev. : Date : 20/10/97 Page : 14

Fig. 3. Error count with modes  $0\rightarrow 1$  and  $1\rightarrow 0$  versus dose in 3.3 V Micron DRAM s/n 35.

Issue : 01 Rev.: Date : 20/10/97

Page : 15

### APPENDIX 3. Parametric test results for Micron DRAM devices.

Fig. 1. Standby supply current versus dose and after annealing for Micron DRAMs.

Fig. 2. Operating supply current versus dose and after annealing for Micron DRAMs.

Issue : 01 Rev.: Date : 20/10/97

Page : 16

Fig. 3. Input current low level versus dose and after annealing for Micron DRAMs.

Fig. 4. Input current high level versus dose and after annealing for Micron DRAMs.

Issue : 01 Rev. : Date : 20/10/97 Page : 17

Fig. 5. Output leakage current third state low level applied versus dose and after annealing for Micron DRAMs.

Fig. 6. Output leakage current third state high level applied versus dose and after annealing for Micron DRAMs.

Issue : 01 Rev. : Date : 20/10/97

Page : 18

Fig. 7. Output voltage low level versus dose and after annealing for Micron DRAMs.

Fig. 8. Output voltage high level versus dose and after annealing for Micron DRAMs.

Issue : 01 Rev.: Date : 20/10/97 Page : 19

Fig. 9. Output enable access time versus dose and after annealing for Micron DRAMs.

Fig. 10. CAS access time versus dose and after annealing for Micron DRAMs.