# SOI-CMOS TECHNOLOGY FOR THIN FILM SENSORS ON MEMBRANES

Benoit Olbrechts<sup>(1)</sup>, Jean Laconte<sup>(1)</sup>, Céline Castadot<sup>(1)</sup>, Denis Flandre<sup>(1)</sup> and Jean-Pierre Raskin<sup>(1)</sup>

(1) Research Centre in Micro and Nanoscopic materials and Electronic Devices (CeRMiN),

Université catholique de Louvain (UCL), Place du Levant 3,

B-1348 Louvain-la-Neuve, Belgium

Email: olbrechts@emic.ucl.ac.be

#### **ABSTRACT**

Silicon-on-Insulator (SOI) technology is emerging as a major contender for heterogeneous microsystems applications. In this work, we focus on the its advantages for realizing thin film sensors on membranes (gas-composition, gas-flow and pressure sensors). We demonstrate its simplicity by actual validated co-integrated realizations in CMOS-SOI technology.

## INTRODUCTION

SOI (Silicon-on-Insulator) technology has now been widely demonstrated and recognized to be a mature and viable alternative to mainstream bulk silicon (Si) for the realization of high-speed, low-power digital [1] and analog/RF [2] CMOS circuits, as well as niche applications under extreme high temperature [3] or radiation operating conditions [4].

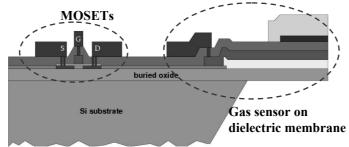

In this work, based on an extensive review of research results on the material, process and component properties, we aim at demonstrating that and how SOI processes can advantageously be used to directly co-integrate sensors on membranes with CMOS circuits on the same silicon die, targeting the development of single-chip harsh environment microsystems (Fig. 1). Such dielectric membranes are required as starting material to achieve a great thermal insulation of microheater based gas-flow sensors. It was demonstrated that thin dielectric membranes, only 1  $\mu$ m thick, constitute the best option to consume very low heating power in order to be integrated in low-power smart gas sensors [5].

# **SOI TECHNOLOGY**

Silicon-on-Insulator (SOI) substrate is likely the best way to overcome the limitations of bulk technology. The insulating layer blocks charges transport between the active layer and the substrate, featuring this technology as the best one for radiation and high temperature environments, like outer space, military or industrial and automotive sectors. In addition, the reduction of parasitic capacitances and leakage currents allow better high-frequency performances and lower power consumption when compared to silicon bulk process.

Recently, SOI technology has also been applied to Micro-Electro-Mechanical Sensors (MEMS) [6, 7]. The buried oxide present in the SOI material can be very successfully used as an etch-stop layer for both the wet and dry bulk micromachining, either from the back or from the front side of the wafer. When releasing the silicon substrate from the backside of the wafer for instance, a stacked buried-oxide/silicon membrane can be obtained. The high quality of the top crystalline silicon film enables semiconductor devices such as temperature sensors, microheaters, MOSFETs, microwave circuits to be built within the membrane in order to get a better thermal or electrical insulation. This membrane can also play the role of support for mechanical sensors to sense pressure for instance.

Fig. 1. Cross-section of the co-integration of MOS devices and gas sensor on dielectric membrane in SOI CMOS technology.

The use of SOI thereby appears as the best approach in processing of either circuits or sensors. In addition, it offers the unique advantage to save a great deal of design time and efforts in fabrication of microsystems, combining the electronics and the sensors on the same chip.

### MEMBRANE MICROMACHINING

The materials chosen for the membrane of the microhotplate have to combine low thermal conductivity (i.e. small thickness) with high mechanical strength (i.e. large thickness) [8]. While insuring compatibility with a micronic fully depleted (FD) SOI-CMOS process of interest for micropower or high-temperature applications [9], the 400-nm-thick buried thermal oxide of the SOI substrate can advantageously constitute the first part of the membrane. A second part of the membrane stack is composed of the densified PECVD oxide layer related to the interconnect dielectric between the polysilicon and aluminium layers of the CMOS process. For mechanical robustness, a nitride layer must be added and the thickness must be chosen to carefully compensate the high residual stresses of the deposited films. The thermal oxide usually shows a compressive residual stress of about 250 MPa and nitride a tensile residual stress of about 1.2 GPa. The total stress of the sandwich layer is calculated by (1) where  $t_{\rm ox}$  and  $t_{\rm nit}$  are the thicknesses of oxide and nitride, respectively.

$$\sigma_{\text{tot}} = \frac{t_{\text{ox}}\sigma_{\text{ox}} + t_{\text{nit}}\sigma_{\text{nit}}}{\sigma_{\text{ox}} + \sigma_{\text{nit}}}$$

(1)

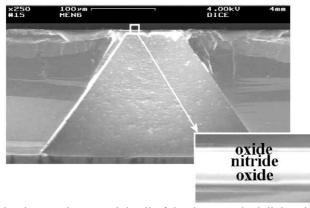

The equation shows that the ratio between the two thicknesses would be 4 to have a strain-free membrane. But, in practice, the best choice is to take a ratio of about 2 to have a slightly tensile membrane and to take into account its high critical lengthening (7.8x10<sup>-3</sup>) [10]. In practice, based on stress measurements (Tab. 1), we selected thicknesses of 300 nm for the LPCVD nitride layer and 290 nm for the PECVD oxide layer for a total thickness of around 1 µm with low residual stress (80 MPa) and low stress gradient (0.78 %). Fig. 2 shows that with these parameters, we obtained an almost strain-free membrane (i.e., with no visible ripples).

Membranes were released at the end of the SOI CMOS process by etching silicon using a Tetramethylammonium Hydroxide (TMAH) based solution. In comparison with EDP and KOH alternatives, TMAH achieves CMOS compatibility and is easy to handle due to its low toxicity. Moreover, high selectivity is achievable versus all dielectrics

| Layer          | Average<br>stress<br>[MPa] | Strain<br>gradient<br>[%/µm] | Stress<br>gradient<br>[MPa/µm] | curvature |

|----------------|----------------------------|------------------------------|--------------------------------|-----------|

| Thermal oxide  | -331                       | 0.24                         | 170                            | +         |

| LPCVD nitride  | 860                        | negligible                   | negligible                     | /         |

| PECVD oxide    | -172                       | negligible                   | negligible                     | /         |

| Sandwich O-N   | 174                        | 1.01                         | /                              | +         |

| Sandwich O-N-O | 80                         | 0.78                         | /                              | +         |

Tab. 1. Summary of our stress measurements in mono and multi-layers.

Fig. 2. Cavity profile under the membrane and detail of the three-stacked dielectric layers of the membrane.

(and aluminum after optimization). All these characteristics make this etchant very attractive to perform the final backside micromachining without special care to the integrated circuits on front side. In particular, selectivity versus aluminum is achieved when an appropriate amount of silicon powder (to decrease the pH of the solution) and diammonium peroxydisulfate (or APS, as oxidizer to improve the surface quality) are added into the solution. By this way, only 3 hours were needed to release clean membrane from 200 µm thick silicon wafers using a TMAH 10% solution heated at 90°C and doped with 35 g/l of silicon powder and 15 g/l of APS.

## MICROHOTPLATE DESIGN

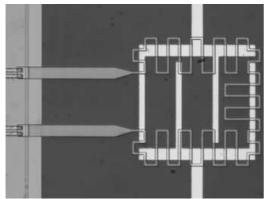

The design chosen for the heater is a loop-shaped phosphorous doped polysilicon resistor (Fig. 1) optimized by finite element method (ANSYS software) to achieve low power consumption and high thermal uniformity. A 340-nm thick phosphorous doped polysilicon is used for the heater because it is the common material and thickness for the gate in CMOS and SOI-CMOS fabrication. The doping level is imposed by the IC process to have a resistivity of around  $25\Omega$ /square (the material resistivity expressed in /square is obtained by dividing the material resistivity in  $\Omega$ .m divided by its thickness). Nevertheless, this value is a good trade-off between thermal uniformity and low-power consumption. In this case, the temperature coefficient of resistance (TCR) is positive and unfortunately leads to hot spots formation. At the opposite, a lower doping level would involve a more uniform temperature distribution but, due to the higher resistivity, the power consumption would increase.

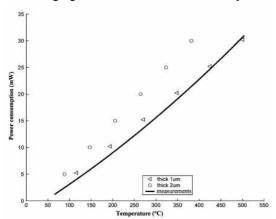

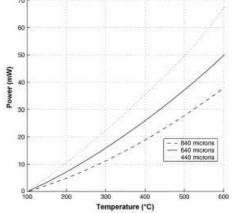

Besides, the membrane dimensions have also a strong influence on the microheater performances. Increasing its thickness by a factor 2 will increase the power consumption by 30% at  $400^{\circ}$ C (Fig. 3), while using a membrane thinner than 1  $\mu$ m leads to decrease in power, thermal uniformity and also in membrane robustness. On the other hand, large surface membranes allow a high thermal insulation (Fig. 4) but are also detrimental to their robustness. The active area of our membranes can be heated to working temperatures of  $400^{\circ}$ C with 25 mW, which is a competitive result in comparison with other recently published microheaters [5]. Thermal uniformity was confirmed by thermo-reflectometry measurements. Thermal ageing and reliability tests (deformation, high frequency switching and high temperature) were performed to validate the great robustness of the membrane.

### **GAS-FLOW SENSORS**

# Microheater Based Gas-Flow Sensors Design and Fabrication

This novel loop-shape polysilicon microheater was integrated on top of our optimized membrane in order to implement the basic heating cell of new simple SOI CMOS compatible gas-flow sensors. For gas-composition measurements, a gas sensitive layer (typically a metal oxide) as well as interdigitated electrodes need to be deposited on top of the microheater to sense the concentration of ambient gases, through the variation of the sensing layer conductivity (Fig. 5). For this purpose, the microheater needs to feature high thermal uniformity, high thermal insulation and maximum working temperatures. After packaging, an on-chip annealing is performed at 700°C for gas sensing film activation without damaging the associated electronic components.

Fig. 3. Influence of the membrane thickness on the microheater power consumption versus membrane temperature ( $\Delta$  and o are simulations results).

Fig. 4. DC Power consumption versus temperature elevation measurements for three different sizes of square membranes (840 μm, 640 μm and 440 μm on one side).

To achieve flow velocity measurements, the microheater needs to be integrated between thermopiles (such as Al/PolySi) to build a calorimetric flow sensor (Fig. 7). Many gas-flow sensors reported in literature were said "CMOS compatible" [11] but most of them used layers or processing steps which are not inherent in standard IC fabrication. Furthermore, only a few have been actually produced in standard CMOS processes. The originality of our design is that it is actually compatible with a standard SOI CMOS process, on the same wafer than integrated circuits. On the other hand, many different flow sensing principles can be found in literature and impose a difficult choice between low power consumption, high airflow rate range, sufficient flow rate sensitivity and compatibility with IC processes. Our sensor challenges most recent realizations by providing attractive trade-offs between these parameters for a large range of applications.

The sensor fabrication process was optimized in order to be integrated in intermediate- and postprocessing of a standard IC SOI CMOS fabrication. In comparison with the standard SOI-CMOS process, only 2 more masks are necessary for the intermediate processing: the first one to pattern silicon on the membrane location and the second one to etch the nitride layer (Fig. 1). This process therefore also requires 2 more photolithographies, 1 more deposition (LPCVD nitride layer) and 2 more etching (silicon film and nitride layer).

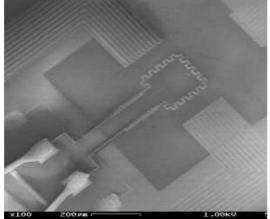

The standard and intermediate process steps are followed by the postprocessing steps. Pt/Ti interdigitated electrodes (200 nm thick) are first deposited by evaporation on the PECVD oxide layer on top of the microhotplate and patterned by lift-off (Fig. 5). It is well known that e-beam evaporation induces X-rays which introduce positive charges in the gate oxide and damage the electrical properties of integrated electronics. Forming gas annealing at 432°C during 30 minutes is therefore performed in order to remove the trapped charges and return electrical characteristics to normal.

Fig. 5. Zoom on the gas sensor active zone before the gas sensitive layer deposition. Interdigitated electrodes can be seen on top of the microhotplate.

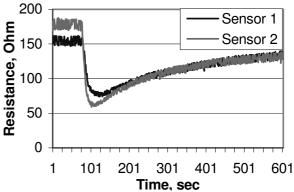

Fig. 6. Time response to ethanol of SnO2 drop-coated sensors

Fig. 7. Calorimetric flow sensor with one direction of detection.

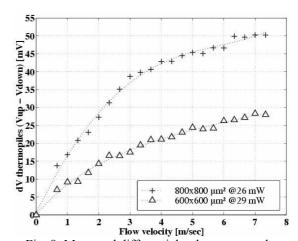

Fig. 8. Measured differential voltage across the thermopiles vs. the applied flow velocity for 2 membrane sizes.

The backside wafer is then thinned and mechanically polished to reach a thickness of 200  $\mu$ m, more appropriate to a silicon wet etching. A 500 nm aluminum layer is evaporated on backside before its patterning using double side alignment. This layer advantageously plays the role of back gate contact for the integrated circuits and of mask to protect silicon during TMAH etching. This step is followed by the full immersion of the processed wafers into the doped TMAH solution during 3 hours. Finally, 600 nm thick sputtered gas sensing films (such as SnO2 and WO3) are deposited before the dicing and packaging while drop coated films (around 10  $\mu$ m thick) are deposited on packaged sensors. Thanks to the great robustness of our membranes, dies with membranes as large as 800x800  $\mu$ m<sup>2</sup> were packaged with a very good yield (around 97 %).

#### Measurement results

Measurements in presence of nitrogen flow revealed a good sensitivity on a large airflow rate range (0 to 8 m/s) for the flow transducer (Fig. 8). In comparison with recent published results, our design firstly offers the advantage to reach high temperature at very low power consumption, as well as a good response time (25 ms), which contributes to provide a great sensitivity to flows [12]. Unfortunately, our p++-PolySi/Al thermopiles do not feature sufficient sensitivity, but have the advantage to make our design simple and easy to integrate in a standard SOI CMOS process. A better sensitivity could be provided by doping the thermopiles and the microheater differently, using a second implantation mask. In comparison with the CMOS compatible sensors we can find in literature, our devices offer good results for a very simple design thanks to the great performances of our 1 µm thin dielectric membrane. Therefore, our flow sensor seems to present attractive trade-offs between the above-mentioned parameters for a large range of applications.

Finally, measurements in presence of gas revealed a good sensitivity to gases such as ethanol (Fig. 6), ammonia and nitrogen dioxide for the gas transducer [13].

#### **CO-INTEGRATION VALIDATION**

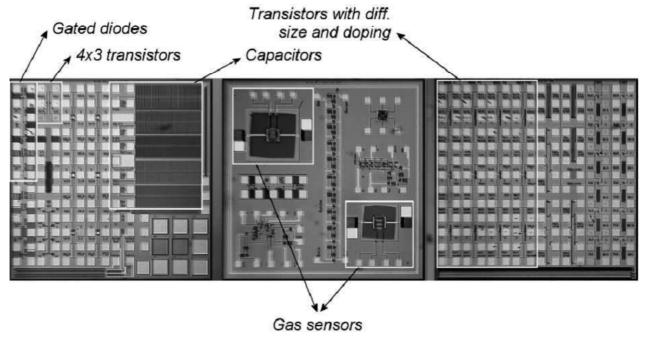

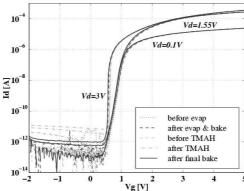

Various transistors (in size, type and doping levels), MOS capacitors and gated diodes were integrated on the same chip as the sensors and therefore processed in same time (Fig. 9). Measurements of these circuits after each post-processing steps allowed for validating the whole CMOS compatibility of our optimized SOI CMOS process as can be verified in Fig. 10.

Fig. 9. Co-integration of integrated circuits and gas sensors in SOI CMOS technology.

Fig. 10. Measured Id/Vg characteristic during the post-processing steps for 4x3 μm² n-transistors (back gate at 0V).

Finally, transistors integrated in small silicon islands located in the middle of our dielectric membranes were successfully fabricated as a concluding demonstrator of the co-integration in SOI technology. Such devices open the door to many new applications (such as gas FET and transistor-based pressure sensors) where integrated circuits and sensors are merged for higher performance in harsh environments.

### PRESSURE SENSORS

We have recently demonstrated the great possibility to build transistors on released membranes starting from a SOI wafers and using a classical SOI MOS process. This new approach is now used to build pressure sensors: disposing transistors directly on membranes and using them as sensitive elements. Indeed, under mechanical constraints the membrane underlying the devices deflects and affects the mobility of electrons and holes in the SOI thin film. Replacing standard polysilicon piezoresistors by active devices will probably bring an easier signal processing and increase the sensor sensitivity.

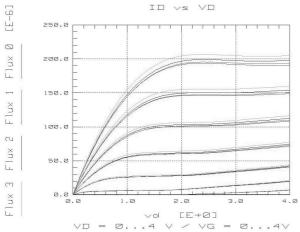

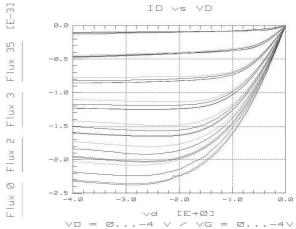

As a first study we applied a vertical nitrogen flow just above devices placed at the centre of membranes. The strain induced by the dynamic pressure involves a deflection of the membrane resulting in an increase of the saturation current as well for n-type transistors as for p-type devices (Fig. 11 and 12).

Due to the centred position of the measured transistors, they where submitted to bi-axial constraints. According to Tab. 2, n-MOS transistor piezoresistive coefficients along both directions have the same negative sign. Therefore, they both have a positive influence on electron mobility in Si lattice. On the other hand, the centroid-shaped p-MOS transistor is also placed at the centre of the membrane. Hence, the strain applied on its channel has a central symmetry. The high increase of the saturated current let us think that this strain is mainly perpendicular to the current direction.

Fig. 11. Measured Id/Vg characteristic for  $4x3 \mu m^2$  n-transistor under nitrogen flows (0, 1, 2 and 3 l/min).

Fig. 12. Measured Id/Vg characteristic for  $72x2 \mu m^2$  centroid p-transistor under nitrogen flows (0, 1, 2, 3 and 3.5 l/min).

| n-MOS transistor         |                         | p-MOS transistor         |                         |  |

|--------------------------|-------------------------|--------------------------|-------------------------|--|

| R <sub>//</sub> (%/kBar) | R <sub>⊥</sub> (%/kBar) | R <sub>//</sub> (%/kBar) | R <sub>⊥</sub> (%/kBar) |  |

| -3.35                    | -1.9                    | +6                       | -5                      |  |

Tab. 2. Typical values of piezoresistive coefficients in MOSFET transistors <110> directions, (100) plane.

## **CONCLUSIONS**

It has been presented that and how the thin film SOI CMOS specificities can be interestingly combined to address the realization of intelligent SOI CMOS integrated sensors for special environments in a wide range of applications such as automotive, aerospace, gas detection, biomedical, quality control.

## **REFERENCES**

- [1] Bernstein, K., and Rohrer, N., SOI circuit design concepts, Kluwer Academic Publishers, 2000.

- [2] Flandre, D., Raskin, J.-P., and Vanhoenacker, D., "SOI CMOS Transistors for RF and Microwave Applications," *CMOS RF modeling, characterization and applications*, published in the series "Selected Topics in Electronics and Systems" by World Scientific Publishing Co, Ed. M.J. Dean and T.A. Fjeldly, 2002 (ISBN 981-02-4905-5) pp. 273-362.

- [3] Flandre, D., "Silicon-on-insulator technology for high temperature metal oxide semiconductor devices and circuits," *High temperature electronics*, IEEE Press, Ed. R. Kirschman, 1998, pp. 303-308.

- [4] Davis, G.E., et al., *IEEE Trans. on Nuclear Science*, Vol. 32, 1985, p. 4432.

- [5] Laconte, J., Dupont, C., Flandre, D., and Raskin, J.-P., "SOI CMOS compatible low-power microheater optimization for the fabrication of Smart Gas Sensors", *IEEE Sensors Journal*, Vol. 4, No. 5, October 2004, pp. 670-680.

- [6] B. Diem, P. Rey, S. Renard, S. V. Bosson, H. Bono, F. Michel, M. Delaye, and G. Delapierre, "SOI SIMOX; from bulk to surface micromachining, a new age for silicon sensors and actuators," *Sensors and Actuators A*, vol. 46-47, pp. 8-16, 1995.

- [7] W. Mokwa, "Advanced sensors and microsystems on SOI," *Int. Journal of High Speed Electronics and Systems*, vol. 10, no. 1, pp. 147-153, 2000.

- [8] M. Horrillo, I. Sayago, L. Arés, J. Rodriguo, J. Gutiérrez, A. Götz, I. Gràcia, L. Fonseca, C. Cané, and E. Lora-Tamayo, "Detection of low NO2 concentrations with low power micromachined tin oxide gas sensors," *Sensors and Actuators B*, vol. 58, pp. 325-329, 1999.

- [9] D. Flandre *et al.*, "Intelligent SOI CMOS integrated circuits and sensors for heterogeneous environments and applications," in *Proc. 1st IEEE Int. Conf. Sensors*, vol. II, Orlando, FL, 2002, pp. 1407–1412.

- [10] C. Rossi *et al.*, "Realization and performance of thin SiO /SiN membrane for microheater applications," *Sensors and Actuators A*, vol. 64, pp. 241–245, 1998.

- [11] Barrettino, D., Graf, M., Zimmermann, M., Hagleitner, C., Hierlemann, A., and Baltes, H., "A smart single-chip microhotplate-based gas sensor system in CMOS-technology", *Analog Integrated Circuits and Signal Processing*, Vol. 39, 2004, pp. 275-287.

- [12] Laconte, J., Rue, B., Flandre, D., and Raskin, J.-P., "Fully CMOS-SOI Compatible Low-Power Directional Flow Sensor", *IEEE Sensors 2004 Conference*, Vienna, Austria, October 24-27 2004.

- [13] Ivanov, P., Laconte, J., Raskin, J.-P., Stankova, M., Sotter, E., Llobet, E., Vilanova, X. Flandre, D., and Correig, X., "SOICMOS Compatible Low-Power Gas Sensor Using Sputtered and Drop-coated Metal-Oxide Active Layers", *Proceedings of IEEE Design, Test, Integration and Packaging of MEMS/MOEMS DTIP*, Montreux, Switzerland, 2004, pp. 137-142.