#### **Alcatel Space - Toulouse - France**

C. Schaffauser - C. Drevon

Flip chip Vs wire bonding Which flip chip in microwave modules ? Main results and characteristics thermo mechanical daisy chains underfill microwave (HFSS simulations and measurements) flip chip module parasitic mode Non Destructive Test

#### Flip chip Vs wire bondin

#### Wire bonding towards flip chip

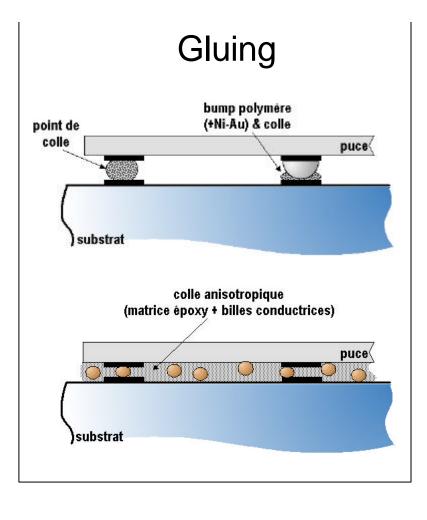

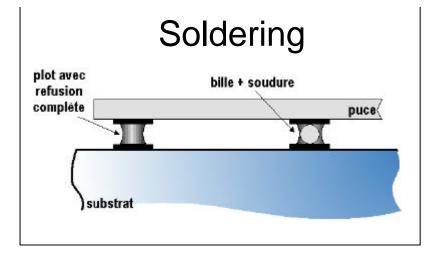

mechanical interface : glue electrical interface : glue and wires Only one mechanical and electrical interface : bumps

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

All rights reserved © 2005, Alcatel Space

#### Flip chip Vs wire bondin

# Flip Chip or Gluing&Wire bonding ?

- Cons Flip Chip

- Hectrical

- the back of the die must be well connected to ground

- Fabrication

- "new" process (gluing and wire bonding still present)

- Control is more difficult and visual inspection is impossible after assembly

- Pros Flip Chip

- Electrical

- better RF performances

- perfect for reaching higher frequencies

- better performances

- wider frequency bandwidth (less selective)

- more repetitive results

#### Flip chip Vs wire bondin

# **Alcatel Flip Chip Needs**

- When wire bonding assembly is limited

- - when heat dissipation through GaAs is not enough,

- thermal bumps near transistor hot parts

- when bonding 2 or 3 wires in parallel is not sufficient for good S11,

- when parasitic effect of wires can not be cancelled any more,

- need for thin and high bumps

- Quality Insurance

- Thermal Expansion Coefficient difference between die and substrate can quickly create failure

- Need for underfill ? Which underfill ?

- Verification with thermal cycles

- Non destructive Control ?

####

#### Which flip chip in microwave modules ?

- Main results and characteristics

- thermo mechanical

- daisy chains

- underfill

- microwave (HFSS simulations and measurements)

- flip chip module

- parasitic mode

Non Destructive Test

Which flip chip

## **RF** application particularities

- GaAs components (usually 100 µm thick)

- rightarrow pad dimensions and pitch : 50 to 100  $\mu$ m Au top metallization

# in a flip chip configuration

- package influence on RF performances

- material electrical characteristics (dielectric constant, losses...)

- ground plane position, connection, quality and proximity,

- gap height between die and substrate...

Impose of the time : microstrip access on substrate and ground plane just beneath

#### Which flip chip

# Which Flip Chip for microwave applications ?

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

## Which flip chip

- Alcatel Space hyper frequency dice are GaAs dice with gold pads

- - no SnPb solder directly on die

- AuSn would be more appropriate

- quite high temperature process

- ➡ Is one solution when low temperature process is needed (ex : organic parts)

- still need small pitches and thin and high bumps

- gold bumps too

- not compatible with usual gluing techniques

- Compatible with Silicon and GaAs pads

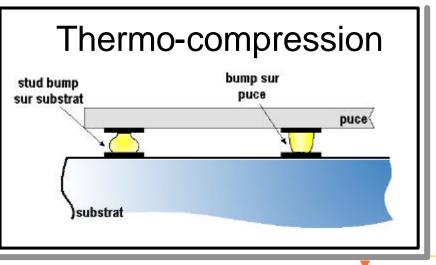

- Thermocompression ?

- Alcatel Space main experience

- compatible with gold pads and their small dimensions and pitches

- but high temperature process

- gold bumps

#### Which flip chip

STATISTICS IN COLUMN

FC 150

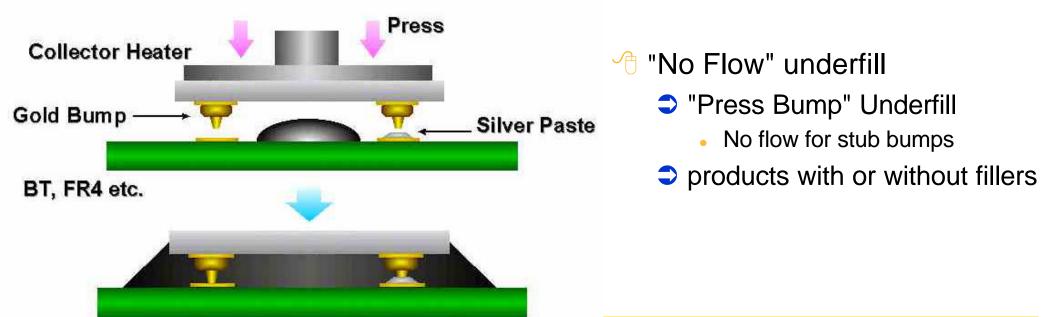

# Suss Microtec Flip chip machine

- Thermocompression or refusion

- depends on used arm

- - maximum temperature : 450°C

- Maximum Load : 50 Kgf

- Parallelism correction :

- with optical autocollimation system (if die and substrates have highly reflective metallization)

.....

- with Laser system (if metallization is not reflective enough)

- most of the time the case with GaAs dice

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

All rights reserved © 2005, Alcatel Space

Flip Chip under study at Alcatel Space

# Power Flip Chip

- ➡ Gold thermal bumps made on wafer (by the foundry)

- ➡ High Thermal dissipation substrate (AIN, Diamond...) with thin film and via

#### Low Power Flip Chip

- ➡ Gold stud bumps (3 possible heights) made by HCM La Rochelle

- Al<sub>2</sub>O<sub>3</sub> substrate with thin film and via

- **Possible "dice"** : MMIC, transistors, MEMS

- Mostly used technique : thermocompression

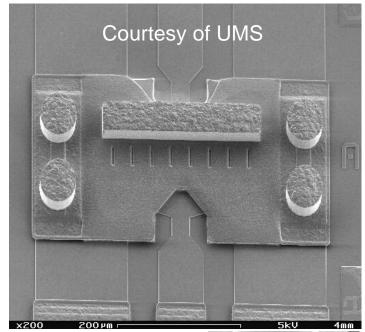

# "Power Applications"

#### **Electrolytic Bumps**

- - perfect for mass production

- gold electrolytic growth

- Height  $\leq$  Diameter

- Excellent for thermal dissipation

- Thermal bumps on the hottest points of the transistors

- Critical Points

- How to perform electrical tests ?

- No proper evaluation due to bump fabrication default

- Some foundries can make those bumps on GaAs, GaN, SiC wafers

Courtesy of UMS

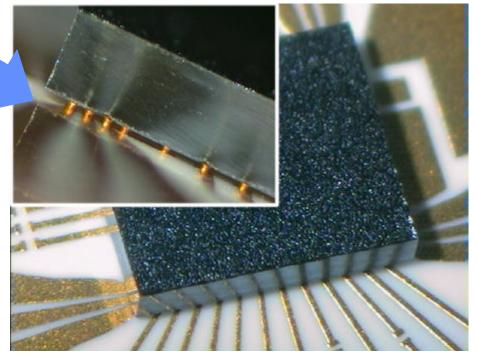

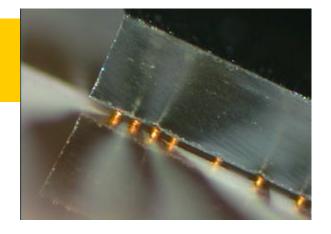

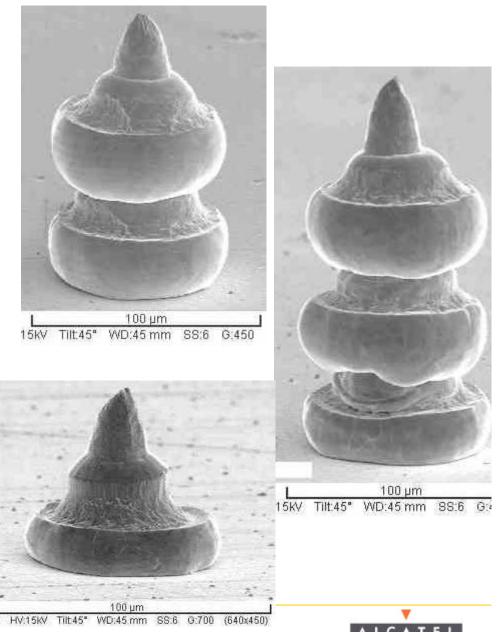

# "Standard Applications" Stud Bumps

can use MMICs of the shelves

Adapted to both RF and LF part dimensions

60µm diameter

Several possible heights

**2**0 to 90µm

Very good adhesion on AIN and Alumina substrates

around 20gf per bump

Evaluation performed on HCM bumps

ESTEC Study (2004)

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

# Which flip chip

# Which flip chip

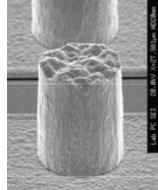

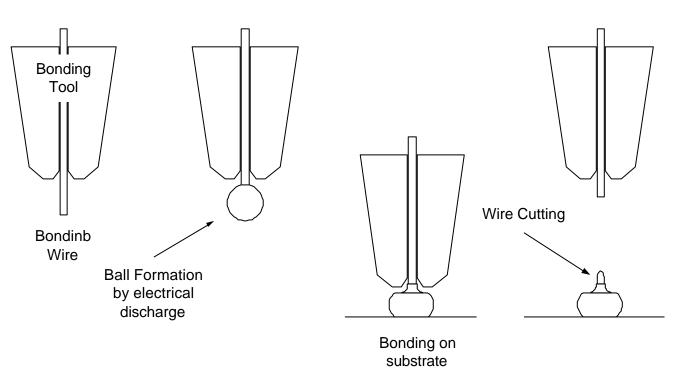

# **Stud Bump Theory**

- Two ways of performing stud bumps

- 1 PANASONIC patent

- gold wire used for wire bonding (same gold)

- wire cutting by a quick movement of bonding tool wire torsion

- stitch against the ball

- 1 2 HCM bumps

- wire pulling until break

- dedicated gold wire (1 or 2% palladium for wire breaking)

- usually 20 μm

diameter wires, could

be 17.5 μm

# Which flip chip

# **HCM Stud Bumps possibilities**

- HCM La Rochelle France Micro electronic Packaging

- Design rules

- **+/- 3,5 μm** accuracy with K&S8028 machine

- Minimum pitch between bumps : 55 μm

- Minimum pad dimension : 50 μm

- Gold wire

- AW6 type gold wire with Pd 20 µm diameter

- 18 µm diameter

- Machine and tools

- K&S 8028PPS new machine

- <sup>(1)</sup>Many tools can be used but difficult to test them all.

<sup>⊕</sup>Flip chip Vs wire bonding Which flip chip in microwave modules ? <sup>A</sup>Main results and characteristics thermo mechanical daisy chains underfill microwave (HFSS simulations and measurements) • flip chip module • parasitic mode Non Destructive Test

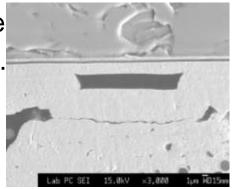

# Process quality and reliability

- Hen optimising a process, one must check its quality and strength

- just after assembly : see if all bumps are correctly connecte

- after ageing tests : see if bumps stay correctly connected..

- Possible defaults

- Too much strain between die and substrate (due to Coefficient of Thermal Expansion mismatch and big dice)

- délamination between bump and pad

- Pollution

- no bump adhesion on pad

- ⇒ Air trapped inside underfill (if there is some)

- if those bubbles are against bumps, it might concentrate stress on those bumps

- Checking techniques

- Cut / SEM / EDAX -> long and expensive

- Daisy Chain and 4-point resistance measurement

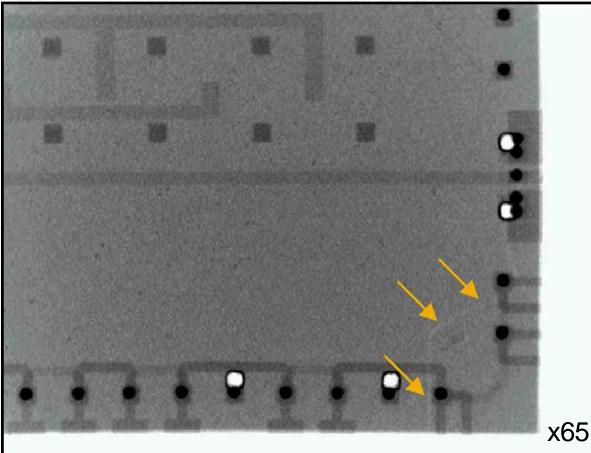

Fabrication default o bumps made on the wafer by UMS

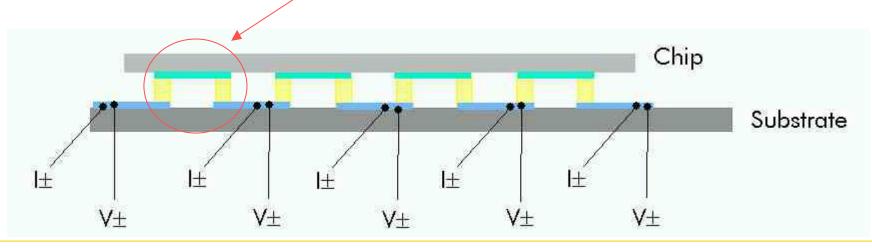

#### **Daisy Chain Resistance Measurement**

- The best way to control assembly quality and reliability

- Oprecise and complete information on contacts at initial time & during ageing

- Oto see the impact of chosen materials, dimensions...on assembly sturdiness

- to find the weakest parts of assemblies

- ASP has a dedicated test bench 4 point resistance measurement

deasy adaptation to different dice, assemblies...

- -65% precision on a  $1m\Omega$  resistance

- very precise measurement of bump evolution

- 4 automatic measurement of entire daisy chain and small parts of it

- some defaults appear and progress very slowly

- one bump default could stay a long time unnoticed as bump resistance

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of

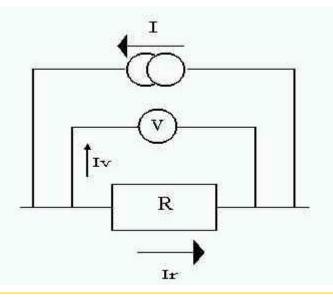

# 4 point resistance measurement Theory

# lr » I

#### lv<<lr

- So measured resistance is nearly exact R

- Wires and lines that bring current or that measure voltage are not taken into account

- $\bigcirc$  and moreover, any  $\Delta R$  will be more easily noticed

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

Thermo mechanica

#### Thermo mechanica

#### Bump pairs - ordinary daisy chains

bumps are connected with lines alternately on die and substrate

- the total length of the daisy chain can be measured

- immediate indication of failure

- but not always information on default apparition

- or we can measure groups of "Two bumps and a line on die"

- Measured resistance is smaller so one bump evolution should be visible

- location of the default

- very simple principle and measurement

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

#### Thermo mechanica

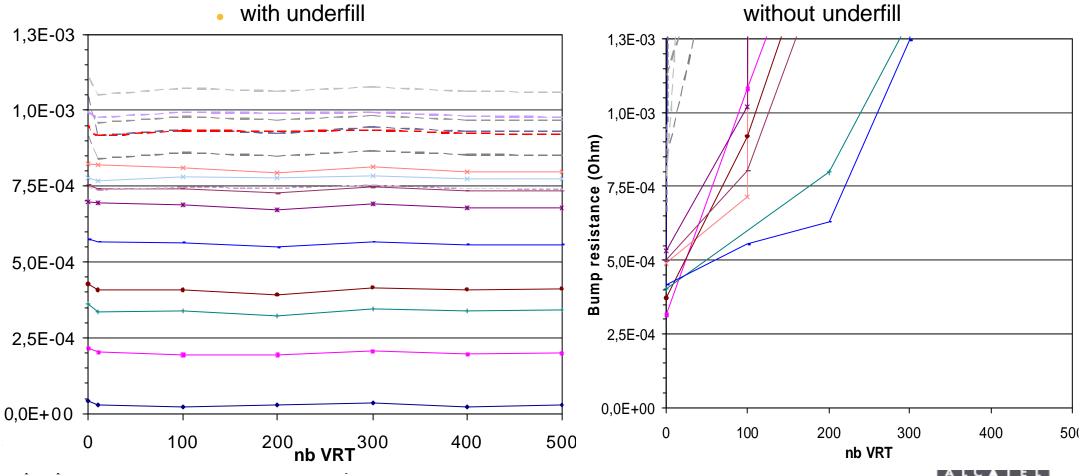

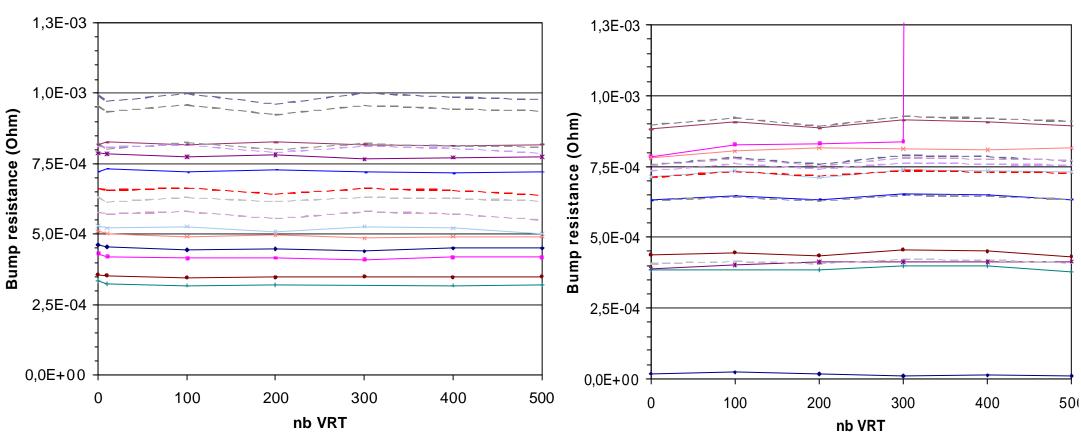

Some results with GaAs on alumina and AIN

- <sup>(1)</sup>Thermocompression process

- Thermal cycling

- On AIN

On Alumina

with underfill

without underfill

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

All rights reserved © 2005, Alcatel Space

# Why Underfill ?

Coefficient of Thermal Expansion Mismatch between die and substrate

High stress concentrated at the bump level

| Chip | CTE @ 25°C<br>(ppm/°C) | Substrate | CTE @ 25°C<br>(ppm/°C) |

|------|------------------------|-----------|------------------------|

| GaAs | 5.8                    | Alumina   | 5.25                   |

| Si   | 2.6                    | AIN       | 2.3                    |

# Solution : Underfill

Inserting a curable liquid resin between the die and the substrate

- Spread the thermally induced stress over the entire package

- - Small bump height : 20 to 50 microns

- ⇒ Few bumps, mainly at the die periphery (i.e. high DNP)

- Die size : from 1x1 to 5x5 mm<sup>2</sup>

# **Underfill Solutions**

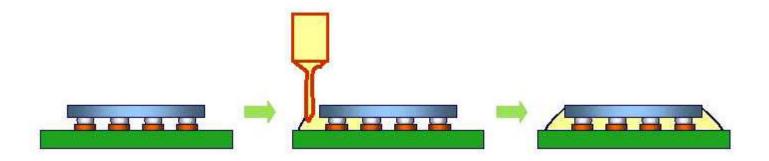

# Capillary underfill

Underfill dispensed near the edge of the chip

- flow under the die by capillary action

- <sup>d</sup> cured when flow completed

Image: Market Common State of Commercial Underfill

- Iimit for high volume : time consumming (flow time + curing time)

- new solutions under development

"No Flow" underfill

Underfill dispensed on substrate at the die location

- Chip is placed & pressed on the bump

- Ip chip assembly & underfill polymerisation at the same time

- most of the time dedicated to solder bump

- unfilled resin, so high CTE : source of fatigue

- critical dispensing proccess ("floating chip")

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

# Underfill ?

#### Pros : Fabrication et reliability

Proven effectiveness for die dimensions up to 5x5mm et 5.5x4mm on AIN circuit:

- Thermal cycles [-55;+125°C] : 500-1000 OK

- Storage at 125°C : 2000h OK

- Better and stabilise good but imperfect assemblies (// pb for ex).

- Assembly secured

- Less severe control

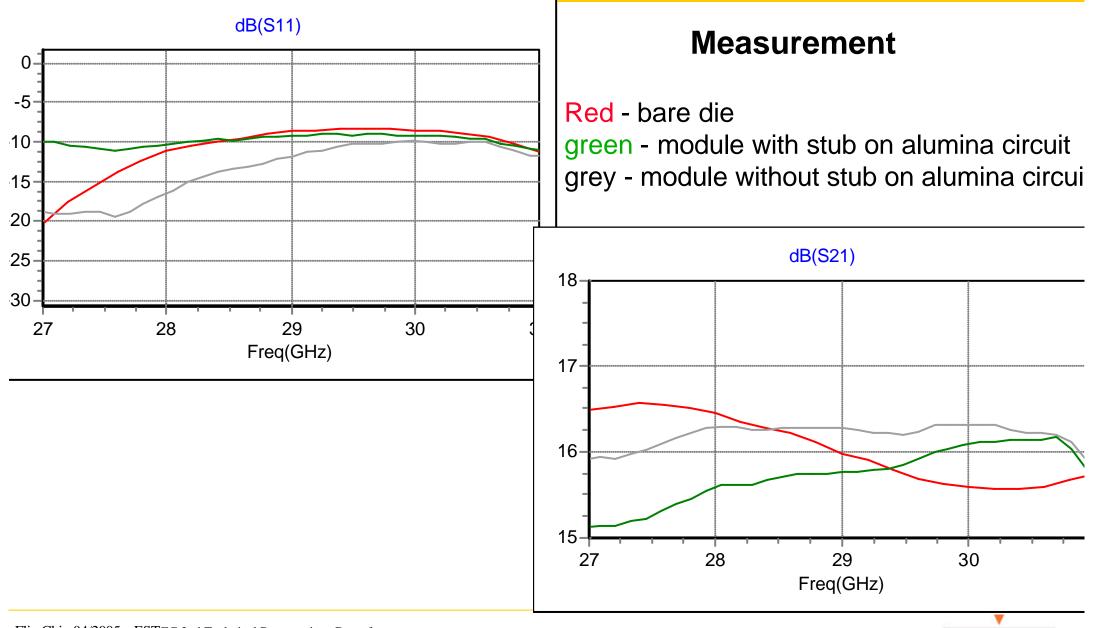

#### Cons : Fabrication and electrical

- New organic material (need evaluation and qualification)

- More fabrication steps

- More RF losses

- RF mismatch (frequency bandwidth gets lower)

- MMIC design taken underfill into account (new library)

- Or module design taken this frequency shift into account

<sup>⊕</sup>Flip chip Vs wire bonding Which flip chip in microwave modules ? <sup>A</sup>Main results and characteristics thermo mechanical daisy chains underfill microwave (HFSS simulations and measurements) flip chip module parasitic mode Non Destructive Test

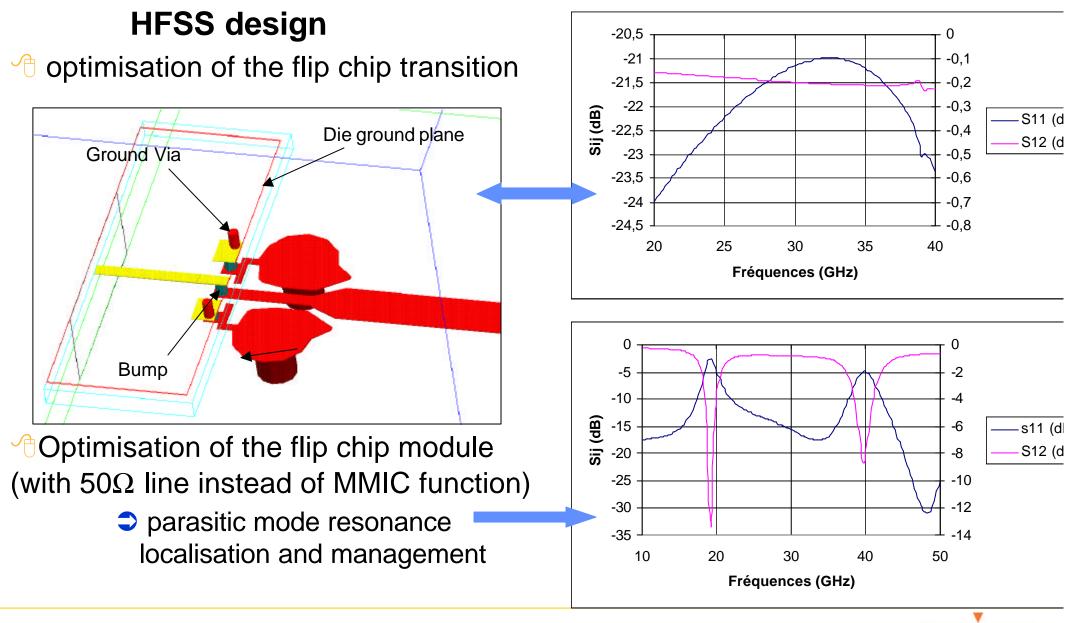

#### Microwave

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

# Parasitic mode : type of "Parallel Plate Mode"

- Coupling between MMIC and circuit ground planes

- happens in main application with the chosen flip chip topology

- $\bigcirc$  Resonance frequency  $\succ$  if :

- 🗢 die size 🛛 🌱

- bump height >

- $\bigcirc$  ground bump position and number  $\succ$

- $\bigcirc$  underfill between die and substrate (global  $\varepsilon$ r below the die  $\checkmark$ )

- circuit thickness >

- Solutions

- HFSS simulations before circuit design -> possible to move this resonance frequency above active bandwidth

- Take it into account in MMIC design

- or other flip chip configuration

- ("Hot Via" or "Embedded transmission-lines (ETL)" topologies)

Microwave

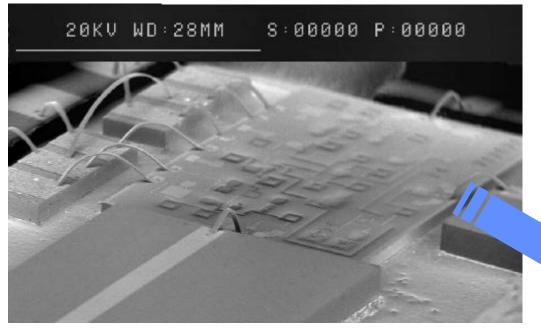

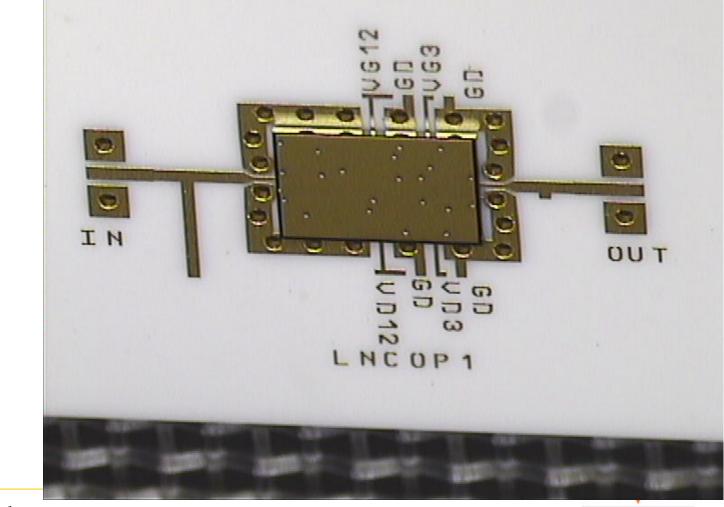

# Flip Chip assembly of a 30GHz LNA

#### LNAUM24A flip chip mounted on alumina circuit with HCM triple bumps

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

All rights reserved © 2005, Alcatel Space

Microwave

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

All rights reserved © 2005, Alcatel Space

<sup>⊕</sup>Flip chip Vs wire bonding Which flip chip in microwave modules ? <sup>A</sup>Main results and characteristics thermo mechanical daisy chains underfill microwave (HFSS simulations and measurements) • flip chip module parasitic mode Non Destructive Test

Control ?

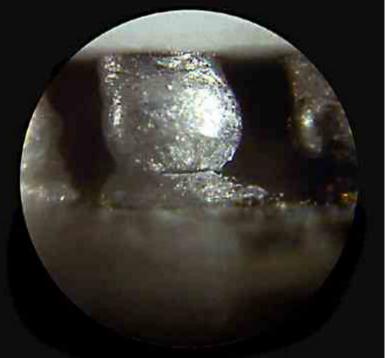

#### **Non Destructive Control**

- What makes it to difficult...

- $\bigcirc$  Bump dimensions -> ~60µm  $\phi$  and height

- Horizon ->at die periphery

- Default dimension and nature -> lack of adhesion of delaminations betwee two gold layers

- 1 Possible complexity of assembly (many metallic or different material layers

- Possible presence of underfill if CTE mismatch is too big

- Techniques under test

- Infra Red Microscopy BARNES / QUANTUM FOCUS

- Stress analysis with ESPI system HIRONDELLE & ETTEMEYER

- Visual Inspection Ersascope

- <sup>4</sup>√ Very simple and direct technique

- dapted to BGAs

- Obut not enough accurate for bump and associated default dimensions

- This technique must be watched (possible evolution)

Control?

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

All rights reserved © 2005, Alcatel Space

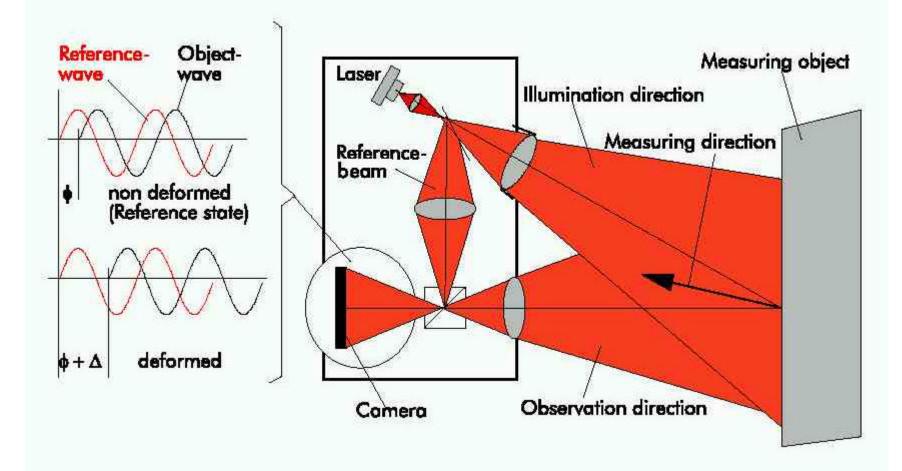

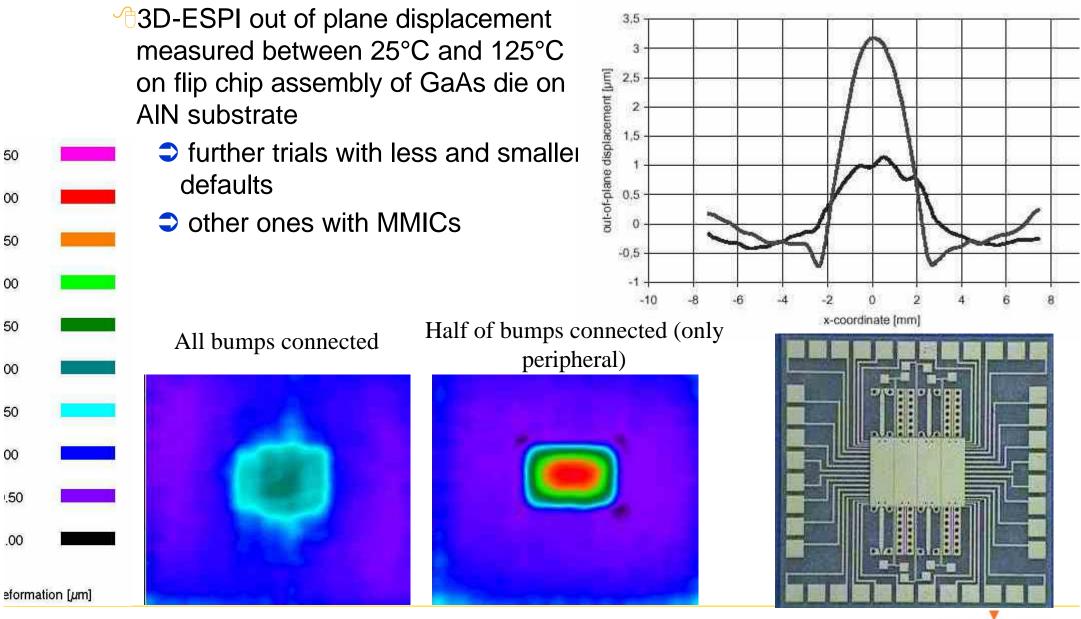

- ESPI technology of ETTEMEYER

- European study HIRONDELLE (not finished)

- 4 stress and deformation analysis through interferometry

Control

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

# Control ?

Flip Chip 04/2005 - ESTEC 2nd Technical Presentations Day of the activities of the CTB Working Group on Hybrids, MCM,

All rights reserved © 2005, Alcatel Space

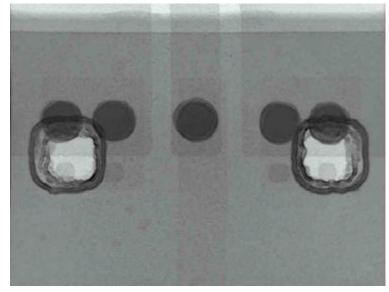

#### X- ray microscopy (PHOENIX)

- $\bigcirc$  nanofocus tube -> 0.3µm lateral resolution

- $\bigcirc$  but defaults <1µm detection mainly depends on used detector contrast

- could not see any default on bumps

x360

**Control**?

the activities of the CTB Working Group on Hybrids, MCM,

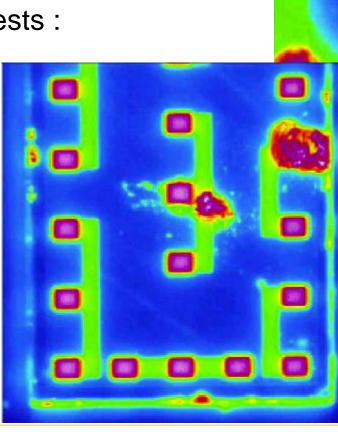

- Infra Red Microscopy (QUANTUM FOCUS)

- good resolution

- but bumps hidden by metallisations

- some further possible tests :

- Temperature pulse

- Faster acquisition

**Control**?

# **Proposed Solution - Sampling**

- Widely used elsewhere but could it be applied to Space equipment fabrication ?

- Application domains :

- when control is destructive

- when control takes too long

- when control is too expensive

- ⁴Goal

- decide whether or not the lot is acceptable

- not for quality estimation

- ⊕ between 100% and 0% control

- but with a good knowledge of error probability

- several kinds of Acceptance Sampling Plans

# Control ?

# Conditions

- Process must already be qualified

- - different kind of samples (part to part variation),

- operator (reproducibility)

- and error inherent in measurement tool (repeatability)

- Which acceptance or rejection criteria ?

- Can some defaults be accepted ? (depending on default nature or position)

- Iook for norms depending on chosen control test.

- Which control for flip chip inspection ?

- Cuts and SEM inspection (most precise)

- Pull tests (maybe better results than shear tests but much more difficult to implement)