Europäisches Patentamt (19)European Patent Office Office européen des brevets (11)EP 1 041 610 A1 (43) Date of publication: (51) Int. Cl. H01L 21/20, H01L 21/205, 04.10.2000 Bulletin \*\*\*\*/\*\* H01L 21/203. H01L 21/208. (21) Application number: 98950452 H01L 33/00, H01S 3/18, (22) Date of filing: 29.10.1998 C01B 21/06 (87) International publication number: WO 99/23693 (04.10.2000 Gazette \*\*\*\*/\*\*) (84) Designated Contracting States: Electric DE FR GB (30) Priority: 30.10.1997 JP 29830097 OKAHISA, Takuji Itami Works of Sumitomo 20.01.1998 JP 900898 Electric 14.04.1998 JP 10254698 (71) Applicant: Sumitomo Electric Industries, Ltd. MATSUMOTO, Naoki Itami Works of Sumitomo Electric (72) Inventors: MOTOKI, Kensaku Itami Works of Sumitomo

#### (54) GaN SINGLE CRYSTALLINE SUBSTRATE AND METHOD OF PRODUCING THE SAME

Patent published on CD-ROM : ESPACE 00/051

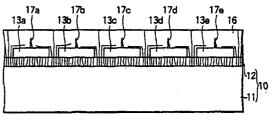

(57) The method of making a GaN single crystal substrate comprises a mask layer forming step of forming on a GaAs substrate 2 a mask layer 8 having a

plurality of opening windows 10 disposed separate from each other; and an epitaxial layer growing step of growing on the mask layer 8 an epitaxial layer 12 made of GaN.

| (19) | Europ                                                                                                                                         | päisches Patentamt<br>pean Patent Office<br>e européen des brevets |   | (11)     | _                                 |                        | EP | 10 | 34 : | 325 | A1 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---|----------|-----------------------------------|------------------------|----|----|------|-----|----|

| . ,  | Date of publication:<br>13.09.2000 Bulletin ****/*<br>Application number: 98950<br>Date of filing: 15.10.1998                                 | *<br>0142                                                          |   | Internat | C3(<br>tional pub                 | )B 29/4<br>plication n |    |    | 0,   |     |    |

| . ,  | Designated Contracting Si<br>AT BE CH CY DE DK ES<br>MC NL PT SE<br>Priority: 20.10.1997 FF<br>Applicant: CENTRE NATH<br>RECHERCHE SCIENTIFIC | FI FR GB GR IE IT LI LU<br>R 9713096<br>IONAL DE LA                | • | GUILL    | T, Pierre<br>AUME, Jo<br>DUZ, Sou | ean-Clau               | de |    |      |     |    |

| (72) | Inventors:<br>BEAUMONT, Bernard                                                                                                               |                                                                    | • |          | , Gilles<br>E, Michel             |                        |    |    |      |     |    |

- (54) METHOD FOR PRODUCING A GALLIUM NITRIDE EPITAXIAL LAYER

- (87) This international application for which the EPO is a designated office has not been republished by the EPO according to article 158(1) EPC.

Cette demande internationale pour laquelle l'OEB est office désigné n'a pas été republiée par l'OEB en vertu de l'article 158(1) CBE.

Diese internationale Anmeldung, für die das EPA Bestimmungsamt ist, würde, gemäß Artikel 158(1) EPÜ, vom EPA nicht wieder veröffentlicht.

Patent published on CD-ROM : ESPACE 00/046, FIRST 00/005, FIRST 99/002, WORLD 99/065

(57) The invention concerns a method for producing a gallium nitride (GaN) epitaxial layer characterised in that it consists in depositing on a substrate a dielectric layer acting as a mask and depositing on the masked gallium nitride, by epitaxial deposit, so as to induce the deposit of gallium nitride patterns and the anisotropic lateral growth of said patterns, the lateral growth being pursued until the different patterns coalesce. The deposit of the gallium nitride patterns can be carried out ex-situ by dielectric etching or in-situ by treating the substrate for coating it with a dielectric film whereof the thickness is of the order of one angstrom. The invention also concerns the gallium nitride layers obtained by said method.

(57) La présente invention concerne un procédé de réalisation d'une couche épitaxiale de nitrure de

gallium (GaN) caractérisé en ce qu'il comprend le dépôt sur un substrat d'une couche de diélectrique fonctionnant comme un masque et la reprise du substrat masqué par du nitrure de gallium, dans des conditions de dépôt par épitaxie, de façon à induire le dépôt de motifs de nitrure de gallium et la croissance anisotrope et latérale desdits motifs, la croissance latérale étant poursuivie jusqu'à la coalescence des différents motifs. Le procédé de dépôt de motifs de nitrure de gallium peut être effectué ex situ par gravure de délectrique ou in situ par traitement du substrat consistant à recouvrir celui-ci par un film diélectrique dont l'épaisseur est de l'ordre de l'angström. L'invention concerne également les couches de nitrure de gallium susceptibles d'être obtenues par le procédé.

*)*

(19)

(43) Date of publication: 14.06.2000 Bulletin \*\*\*\*/\*\*

(21) Application number: 98935545

(22) Date of filing: 02.07.1998

(11)

## EP 1 007 771 A1

(51) Int. CI. C30B 2 3/04, C30B 25/04, C30B 25/18, C30B 29/40

(87) International publication number: WO 99/01594 (14.06.2000 Gazette \*\*\*\*/\*\*)

| (84) | -                     | d Contracting States:<br>CY DE DK ES FI FR GB GR IE IT LI LU | (71) | Applicant: CBL Technologies  |

|------|-----------------------|--------------------------------------------------------------|------|------------------------------|

| (30) | MC NL PT<br>Priority: |                                                              | (72) | Inventor: SOLOMON, Glenn, S. |

| (30) | r noncy.              | 03.07.1997 US 51816 P                                        |      |                              |

- (54) THERMAL MISMATCH COMPENSATION TO PRODUCE FREE STANDING SUBSTRATES BY EPITAXIAL DEPOSITION

- (87) This international application for which the EPO is a designated office has not been republished by the EPO according to article 158(1) EPC.

Cette demande internationale pour laquelle l'OEB est office désigné n'a pas été republiée par l'OEB en vertu de l'article 158(1) CBE.

Diese internationale Anmeldung, für die das EPA Bestimmungsamt ist, würde, gemäß Artikel 158(1) EPÜ, vom EPA nicht wieder veröffentlicht.

Patent published on CD-ROM : ESPACE 00/028, FIRST 00/003, FIRST 99/001, WORLD 99/005

producing thick, high (57) A method for quality GaN substrates uses an epitaxially deposited film and is used as a substrate material for further device or epitaxial processing. The film (11) is deposited using an epitaxial technique on a thin substrate called the disposable substrate (10). The deposited film is thick enough so that upon cooling the thermal mismatched strain is relieved through cracking of the lower disposable substrate and not the newly deposited epitaxy. The epitaxial film now becomes a platform for either further epitaxial deposition or device processing.

(57) La présente invention concerne un procédé de

production de substrats GaN épais de grande qualité comportant une couche déposée par épitaxie utilisée comme matériau de substrat pour un nouveau dispositif ou traitement épitaxique. La couche (11) est déposée sur un substrat mince appelé substrat jetable (10), en utilisant une technique épitaxique. La couche déposée est assez épaisse, de sorte que lors du refroidissement, la contrainte du déséquilibre thermique est réduite par la fissuration du substrat inférieur jetable et non par celle de l'épitaxie fraîchement déposée. La couche épitaxique devient ainsi une plate-forme, soit pour un nouveau dépôt épitaxique, soit pour un nouveau traitement de dispositif.

| (19)                         | <u>))</u>                                                                                   | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |      | (11)     |                                                       | EP 1 001 468 A1 |

|------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|----------|-------------------------------------------------------|-----------------|

| (43)<br>(21)<br>(22)         | Date of publication:<br>17.05.2000 Bulletin<br>Application number:<br>Date of filing: 02.11 | 99308690                                                                        | (51) | Int. Cl. | H01L 29/5 <sup>,</sup>                                | 1               |

| (84)<br>(30)<br>(71)<br>(72) | MC NL PT SE<br>Priority: 12.11.19                                                           | ek es fi fr GB GR ie it li lu                                                   | •    | Kwo, .   | n, Ahmet Refik<br>Jueinai Raynien<br>aerts, Joseph Pe | trus            |

#### (54) Rare earth oxide layer on a GaAs- or GaN-based semiconductor body

Patent published on CD-ROM : ESPACE 00/023, FIRST 00/003

(57) We have found that a single crystal, single domain oxide layer of thickness less than 5 nm can be grown on a (100) oriented GaAs-based semiconductor substrate. Similar epitaxial oxide can be grown on GaN and GaN-based semiconductors. The oxide typically is a rare earth oxide of the Mn2O3 structure (e.g., Gd2O3). The oxide/semiconductor interface can be of high quality, with low interface state density, and the oxide layer can have low leakage current and high breakdown voltage. The low thickness and high dielectric constant of the oxide layer result in a MOS structure of high capacitance per unit area. Such a structure advantageously forms a GaAs-based MOS-FET.

| (19)                 | <u>))</u>                                             | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets    |      | (11)                                          | EP 0 987 741 A1 |

|----------------------|-------------------------------------------------------|------------------------------------------------------------------------------------|------|-----------------------------------------------|-----------------|

| (43)<br>(21)<br>(22) | 22.03.2000 Bulletin                                   | 1 ****/**<br>: 99113574                                                            | (51) | Int. Cl. H01L 2 1/20                          |                 |

| (84)<br>(30)<br>(71) | AT BE CH CY DE D<br>MC NL PT SE<br>Priority: 14.09.19 | tting States:<br>IK ES FI FR GB GR IE IT LI LU<br>198 US 152848<br>Packard Company | (72) | ) Inventors:<br>Wang, Shih-Yuan<br>Chen, Yong |                 |

#### (54) Method for relieving stress in GaN devices

Patent published on CD-ROM : ESPACE 00/013, FIRST 00/002

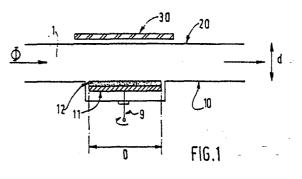

(57) An improved method for growing a first layer[10, 30] on a second layer[12, 32] in which the first and second layers have different thermal indices of expansion and/or a mismatch of the lattice constants and the deposition being carried out at a temperature above ambient. The first layer[10, 30] includes a material that decomposes upon heating above a decomposition temperature. One of the first and second layers absorbs light in a first frequency range and the other of the first and second layers is transparent to the light in the first frequency range. In the method of the present invention, the one of the first and

second layers that absorbs light in the first frequency range is exposed to light[14] in the first frequency range by passing the light through the other of the first and second layers. This exposure heats the first layer[10, 30] to a temperature above the decomposition temperature at the interface of the first and second layers after the first layer[10, 30] has been deposited on the second layer[12,32]. The decomposition can also mean to physically remove the material by means such as chemical etching. The present invention is well suited to the deposition of III-V semiconducting materials on substrates such as sapphire.

| (19)                 | <i>)</i> )                                                                                  | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |              | (11)            | EP 0 972 097 A1                                                                  |

|----------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------|-----------------|----------------------------------------------------------------------------------|

| (43)<br>(21)<br>(22) | Date of publication:<br>19.01.2000 Bulletin<br>Application number:<br>Date of filing: 13.03 | 98907295                                                                        | (51)<br>(87) | International p | <b>3 3/00</b> , C30B 29/40<br>ublication number:<br>(19.01.2000 Gazette ****/**) |

| (84)                 | AT BE CH DE DK E<br>NL PT SE                                                                | S FI FR GB GR IE IT LI LU MC                                                    | •            | NOWAK, Grze     | egorz                                                                            |

| (30)<br>(71)         | •                                                                                           | 997  PL 31932997<br>n badan Wysokocisnieniowych                                 | •            | POROWSKI, :     | Sylwester                                                                        |

| (72)                 | Inventors:<br>GRZEGORY, Izabe                                                               | ella                                                                            | •            | WEYHER, Jai     | 1                                                                                |

(54) MECHANO-CHEMICAL POLISHING OF CRYSTALS AND EPITAXIAL LAYERS OF GaN AND Ga 1-x-yAi xin yN

(87) This international application for which the EPO is a designated office has not been republished by the EPO according to article 158(1) EPC.

Cette demande internationale pour laquelle l'OEB est office désigné n'a pas été republiée par l'OEB en vertu de l'article 158(1) CBE.

Diese internationale Anmeldung, für die das EPA Bestimmungsamt ist, würde, gemäß Artikel 158(1) EPÜ, vom EPA nicht wieder veröffentlicht.

Patent published on CD-ROM : ESPACE 00/003, FIRST 00/001, FIRST 98/004, WORLD 98/124

(57) This method of removal of irregularities and highly defected regions of the surface of crystals and epitaxial layers of GaN and Ga1-x-yAlxInyN characterized by mechano-chemical polishing on the soft polishing pad under pressure in presence of chemical etching agent of water solution of bases of the total concentration above 0.01N in time longer than 10 seconds after which the agent is replaced by the pure water without interruption of the polishing and polishing by at least 1 minute and subsequent diminution of the load and the machine and then the stopping of polished GaN crystal or GaA1InN epitaxial layer is removed of the polishing machine and dried in the stream of dry nitrogen.

(57) L'invention concerne un procédé d'enlèvement

d'irrégularités et de zones très défectueuses de la surface de cristaux et de couches épitaxiales de GaN et de Ga1-x-yAlxInyN, lequel procédé est caractérisé par un polissage mécanochimique consistant à utiliser un tampon de polissage doux, sous pression, en présence d'un agent d'attaque chimique placé dans une solution aqueuse de bases dont la concentration totale est supérieure à 0,01N, et ce pendant une période supérieure à 10 secondes, puis à remplacer l'agent d'attaque par de l'eau pure, sans interrompre le polissage, à polir pendant au moins 1 minute, à diminuer ensuite la charge, à stopper la machine, à enlever alors de la machine de polissage le cristal de GaN ou la couche épitaxiale de GaA11nN, polis, et enfin à les sécher dans un courant d'azote sec.

| (19) | <u>))</u>                                   | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |      | (11)     |          | EP 0 967 664 A1             |

|------|---------------------------------------------|---------------------------------------------------------------------------------|------|----------|----------|-----------------------------|

| (43) | Date of publication:<br>29.12.1999 Bulletin |                                                                                 | (51) | Int. CI. | H01L     | <b>3 3/00</b> , H01L 21/205 |

| (21) | Application number                          | 99110229                                                                        |      |          |          |                             |

| (22) | Date of filing: 26.0                        | 5.1999                                                                          |      |          |          |                             |

| (84) | Designated Contrac                          | cting States:                                                                   |      |          |          |                             |

|      | AT BE CH CY DE D<br>MC NL PT SE             | OK ES FI FR GB GR IE IT LI LU                                                   | •    | Okahi    | sa, Taku | Ji                          |

| (30) | Priority: 28.05.19                          | 998 JP 14771698                                                                 | •    | Matsu    | moto, N  | aoki                        |

| (71) | Applicant: Sumitor                          | no Electric Industries, Ltd.                                                    |      |          |          |                             |

| ·    |                                             |                                                                                 | •    | Matsu    | shima, N | lasato                      |

| (72) | Inventors:                                  |                                                                                 |      |          |          |                             |

| •    | Motoki, Kensaku                             |                                                                                 |      |          |          |                             |

#### (54) Gallium nitride single crystal substrate and method of producing the same

Patent published on CD-ROM : ESPACE 99/097

(57) An n-type GaN substrate having a safe n-type dopant instead of Si which is introduced by perilous silane gas. The safe n-dopant is oxygen. An oxygen doped n-type GaN free-standing crystal is made by forming a mask on a GaAs substrate, making apertures on the mask for revealing the undercoat GaAs, growing GaN films through the apertures of the

mask epitaxially on the GaAs substrate from a material gas including oxygen, further growing the GaN film also upon the mask for covering the mask, eliminating the GaAs substrate and the mask, and isolating a freestanding GaN single crystal. The GaN is an n-type crystal having carriers in proportion to the oxygen concentration.

| (19)         | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets                                                                            | (11)                                                                       | EP 0 966 047 A2            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------|

| . ,          | Date of publication:<br>22.12.1999 Bulletin ****/**<br>Application number: 99111739<br>Date of filing: 17.06.1999                                          | (51) Int. Cl. <b>H01L 3 3/00</b><br>C30B 29/4                              |                            |

| . ,          | Designated Contracting States:<br>AT BE CH CY DE DK ES FI FR GB GR IE IT LI L<br>MC NL PT SE<br>Priority: 18.06.1998 JP 17127698<br>30.06.1998 JP 18344698 | <ul> <li>Okahisa, Takuji, Sumito</li> </ul>                                | mo Electric Ind., Ltd.     |

| (71)<br>(72) |                                                                                                                                                            | <ul> <li>Matsumoto, Naoki, Sum</li> <li>Nishimoto, Tatsuya, Sui</li> </ul> | nitomo Electric Ind., Ltd. |

#### (54) GaN single crystal substrate and method of producing same

#### Patent published on CD-ROM : ESPACE 99/095

(57) A freestanding GaN single crystal substrate is made by the steps of preparing a (111) GaAs single crystal substrate, forming a mask having periodically arranged windows on the (111) GaAs substrate, making thin GaN buffer layers on the GaAs substrate in the windows of the mask, growing a GaN epitaxial layer on the buffer layers and the mask by an HVPE or an MOC, eliminating the GaAs substrate and the mask away and obtaining a freestanding GaN single crystal substrate. The GaN single crystal has a diameter larger than 20mm and a thickness more than 0.07mm, being freestanding and substantially distortion-free.

| (19) | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets                                                                                                                                                                                                              | (11) EP 0 942 459 A1                                                                                                                                                                                                                                                                                                                                                                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (12) |                                                                                                                                                                                                                                                                                              | ENT APPLICATION<br>ce with Art. 158(3) EPC                                                                                                                                                                                                                                                                                                                                                         |

| (43) | Date of publication:<br>15.09.1999 Bulletin 1999/37                                                                                                                                                                                                                                          | (51) Int. Cl. <sup>6</sup> : <b>H01L 21/205</b> , H01L 33/00,<br>C23C 16/34                                                                                                                                                                                                                                                                                                                        |

| • •  | Application number: 98912742.8<br>Date of filing: 09.04.1998                                                                                                                                                                                                                                 | (86) International application number:<br>PCT/JP98/01640                                                                                                                                                                                                                                                                                                                                           |

| ()   |                                                                                                                                                                                                                                                                                              | (87) International publication number:<br>WO 98/47170 (22.10.1998 Gazette 1998/42)                                                                                                                                                                                                                                                                                                                 |

| (30) | Designated Contracting States:<br>AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU<br>MC NL PT SE<br>Priority: 11.04.1997 JP 9331597<br>30.06.1997 JP 17449497<br>07.07.1997 JP 18107197<br>28.07.1997 JP 20147797<br>09.10.1997 JP 20147797<br>22.10.1997 JP 29009897<br>26.11.1997 JP 32499797 | <ul> <li>NAKAMURA, Shuji-Nichia Chemical Industries,<br/>Ltd.<br/>Tokushima-ken 774-0044 (JP)</li> <li>KOZAKI, Tokuya-Nichia Chemical Industries,<br/>Ltd.<br/>Tokushima-ken 774-0044 (JP)</li> <li>IWASA, Naruhito-Nichia Chemical Industries,<br/>Ltd.<br/>Tokushima-ken 774-0044 (JP)</li> <li>CHOCHO, Kazuyuki-Nichia Chemical Industries,<br/>Ltd.<br/>Tokushima-ken 774-0044 (JP)</li> </ul> |

| (72) | Applicant:<br>NICHIA CHEMICAL INDUSTRIES, LTD.<br>Anan-shi, Tokushima 774-8601 (JP)<br>Inventors:<br>KIYOKU, Hiroyuki-Nichia Chemical Industries,<br>Ltd.<br>Tokushima-ken 774-0044 (JP)                                                                                                     | (74) Representative:<br>Hertz, Oliver, Dr.<br>v. Bezold & Partner,<br>Patentanwälte<br>Akademiestrasse 7<br>80799 München (DE)                                                                                                                                                                                                                                                                     |

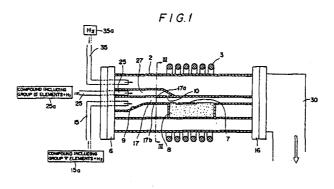

#### (54) METHOD OF GROWING NITRIDE SEMICONDUCTORS, NITRIDE SEMICONDUCTOR SUBSTRATE AND NITRIDE SEMICONDUCTOR DEVICE

(57) A method of growing a nitride semiconductor crystal which has very few crystal defects and can be used as a substrate is disclosed. This invention includes the step of forming a first selective growth mask on a support member including a dissimilar substrate having a major surface and made of a material different from a nitride semiconductor, the first selective growth mask having a plurality of first windows for selectively exposing the upper surface of the support member, and the step of growing nitride semiconductor portions from the upper surface, of the support member, which is exposed from the windows, by using a gaseous Group 3 element source and a gaseous nitrogen source, until the nitride semiconductor portions grown in the adjacent windows combine with each other on the upper surface of the selective growth mask.

FIG.1C

Printed by Xerox (UK) Business Services 2.16.7/3.6

| (19)                 | <u>))</u>                                                                                  | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |      | (11)     |                        | EP 0 937 790 A2            |

|----------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|----------|------------------------|----------------------------|

| <b>、</b>             | Date of publication:<br>25.08.1999 Bulletin<br>Application number<br>Date of filing: 21.01 | : ****/**<br>: 99101114                                                         | (51) | Int. CI. | C30B                   | <b>2 3/00</b> , C30B 29/40 |

| (84)<br>(30)<br>(71) | AT BE CH CY DE D<br>MC NL PT SE                                                            | cting States:<br>DK ES FI FR GB GR IE IT LI LU<br>298 JP 1264598                | (72  | Shion    | ni, Hirom              |                            |

| •                    | Sumitomo Electric                                                                          |                                                                                 |      |          | ni, Masai<br>Io, Shige |                            |

#### (54) Method of making GaN single crystal and apparatus for making GaN single crystal

Patent published on CD-ROM : ESPACE 99/061, FIRST 99/004

(57) An apparatus comprises a Ga-disposing section in which Ga is disposed; a seed-crystal-disposing section in which a seed crystal of GaN is disposed; a synthesis vessel adapted to accommodate the Ga-disposing section, the seed-crystal-disposing section, and a gas containing nitrogen; heating means adapted to heat the Ga-disposing section and the seed-crystal-disposing section; and a control section for transmitting to the heating means a command for heating the Ga to an evaporation temperature of Ga or higher and heating the seed crystal to a temperature higher than that of the Ga, wherein the Ga evaporated by the heating means is adapted to react with the nitrogen of a nitrogen component in the gas so as to yield a GaN-forming gas, the GaN-forming gas being adapted to reach the seed-crystal-disposing section.

| (19)                 | Office européen des brevets                                                                                                                                                                                                                                                                        | (11) EP 0 887 436 A1<br>ENT APPLICATION                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (43)<br>(21)         | Date of publication:<br>30.12.1998 Bulletin 1998/53<br>Application number: 98111626.2<br>Date of filing: 24.06.1998                                                                                                                                                                                | (51) Int. Cl. <sup>6</sup> : <b>C23C 16/30</b> , C23C 16/34                                                                                                                                                                                                                                                                                                                                                                                     |

| (30)<br>(71)<br>(72) | Designated Contracting States:<br>AT BE CH CY DE DK ES FI FR GB GR IE IT LI LU<br>MC NL PT SE<br>Designated Extension States:<br>AL LT LV MK RO SI<br>Priority: 25.06.1997 JP 168553/97<br>Applicant: SONY CORPORATION<br>Tokyo (JP)<br>Inventors:<br>Asatsuma, Tsunenori<br>Shinagawa, Tokyo (JP) | <ul> <li>Hashimoto, Shigeki<br/>Shinagawa, Tokyo (JP)</li> <li>Nakamura, Fumihiko<br/>Shinagawa, Tokyo (JP)</li> <li>Yanashima, Katsunori<br/>Shinagawa, Tokyo (JP)</li> <li>Ikeda, Masao<br/>Shinagawa, Tokyo (JP)</li> <li>Ikeda, Masao<br/>Shinagawa, Tokyo (JP)</li> <li>(74) Representative:<br/>Müller, Frithjof E., DiplIng.<br/>Patentanwälte<br/>MÜLLER &amp; HOFFMANN,<br/>Innere Wiener Strasse 17<br/>81667 München (DE)</li> </ul> |

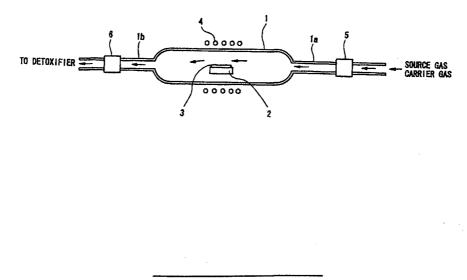

#### (54) Method and apparatus for growth of a nitride III-V compound semiconductor

(57) It is intended to provide a method and apparatus for growing a high-quality nitride III-V compound semiconductor efficiently. A nitride III-V compound semiconductor, such as GaN or InGaN, is grown in a reaction tube of a MOCVD apparatus by setting the inner pressure of the reaction tube to a value not lower than 1.1 atmospheres, particularly, not lower than 1.1 atmospheres and not higher than two atmospheres, and more preferably not lower than 1.2 atmospheres and not higher than 1.8 atmospheres. The reaction tube is made of quartz glass or another material which is sufficiently resistive against a difference between inner and outer pressures.

Fig. 1

Printed by Xerox (UK) Business Services 2.16.6/3.4

| (19)                 | <u>))</u>                                 | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |        | (11)     |                                                         | EP 0 884 767 A2 |

|----------------------|-------------------------------------------|---------------------------------------------------------------------------------|--------|----------|---------------------------------------------------------|-----------------|

| (43)<br>(21)<br>(22) | 16.12.1998 Bulletin<br>Application number | ו ****/**<br>: 98110817                                                         | (51)   | Int. CI. | H01L 21/20                                              |                 |

| (84)<br>(30)<br>(71) | MC NL PT SE                               | DK ES FI FR GB GR IE IT LI LU<br>997 DE 19725900                                | . (72) | Krost,   | erg, Dieter, Prof. Dr<br>Alois<br>tor: Strittmatter, Ar |                 |

#### (54) Method of epitaxy of gallium nitride on silicon substrates

Patent published on CD-ROM : ESPACE 98/089, FIRST 98/005

(57) Gallium nitride epitaxy on silicon In a process for gallium nitride epitaxy on a silicon substrate, an aluminium arsenide layer is applied between the substrate and the gallium nitride layer. A GaAs layer is preferably deposited on the aluminium arsenide layer and converted

to gallium nitride before gallium nitride deposition is completed and the aluminium arsenide layer is preferably partially or completely converted into an aluminium nitride layer in a nitrogen-rich atmosphere. The silicon substrate may be oriented with its surface normals in the crystallographic [100] direction (or equivalent directions) and its surface may be structured with V-shaped trenches having side faces oriented in the [111] direction (or equivalent directions). Alternatively, the silicon substrate may be oriented with its surface normals at 2-6 degrees to the crystallographic [100] direction (or equivalent directions).

| (19)                 | <u>))</u>                                                                                 | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |      | (11)     |                                  |                           | EP 0 881             | 666 A3 |

|----------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|----------|----------------------------------|---------------------------|----------------------|--------|

| (21)                 | Date of publication<br>02.12.1998 Bulletin<br>Application number<br>Date of filing: 22.09 | : ****/**<br>: 98109371                                                         | (51) | Int. CI. |                                  | <b>3 3/00</b><br>1L 29/20 | , H01L 29/205,<br>07 |        |

| (84)<br>(30)<br>(71) | MC NL PT SE<br>Priority: 26.05.19                                                         | 0K ES FI FR GB GR IE IT LI LU<br>997 JP 13540697                                | •    | Yanas    | uma, Tsi<br>hima, Ka<br>na, Taka | itsunori                  |                      |        |

| (72)                 | Inventors:                                                                                |                                                                                 |      |          |                                  |                           |                      |        |

#### (54) P-type nitrogen compound semiconductor and method of manufacturing same

Patent published on CD-ROM : ESPACE 98/085, FIRST 98/005, ESPACE 99/061

(57) A plurality of first layers made of AlGaN mixed crystal each having a thickness of the order of 1 to 100 nm and a plurality of second layers of p-type GaN with Mg each having a thickness of the order of 1 to 100 nm are alternately stacked. Since each of the first and second layers is thin, the stacked layers as a whole have properties of p-type AlGaN mixed crystal although the first layers do not include Mg and the second layers do not include Al. An Al source and a Mg source are temporally separated to be introduced in a stacking process. A reaction between the Al source and Mg source which may interfere desirable crystal growth is thereby prevented. Crystals of good quality are thus grown and electrical conductivity is thereby improved.

| (19)                 | ))                                                                                        | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets     |      | (11)     |                                    |              | EP 0 8 | 871 20 | 08 A3 |

|----------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|----------|------------------------------------|--------------|--------|--------|-------|

| (43)<br>(21)<br>(22) | Date of publication<br>14.10.1998 Bulletin<br>Application number<br>Date of filing: 14.11 | *****/**<br>: 97120023                                                              | (51) | Int. CI. | H01L                               | 2 1/20       |        |        |       |

| (84)<br>(30)<br>(71) | NL PT SE<br>Priority: 09.04.19                                                            | cting States:<br>ES FI FR GB GR IE IT LI LU MC<br>997 US 833813<br>-Packard Company | •    | Schne    | , Yong<br>Mder, Rich<br>, Shih-Yui | hard P., Jr. |        |        |       |

| (72)                 | Inventors:                                                                                |                                                                                     |      |          |                                    |              |        |        |       |

#### (54) Reduction threading dislocations by amorphization and recrystalization

Patent published on CD-ROM : ESPACE 98/072, FIRST 98/004, ESPACE 98/088

(57) A method for providing an epitaxial layer[14] of a first material over a substrate[11] comprising a second material having a lattice constant different from that of the first material. In the method of the present invention, a first layer of the first material is grown on the substrate[11]. A portion of the first layer is treated to render that portion amorphous. The amorphous portion is then annealed at a temperature

above the recrystallization point of the amorphous portion, but below the melting point of the crystallized portion of the first layer thereby recrystallizing the amorphous portion of the first layer. The first layer may rendered amorphous by ion implantation. The method may be used to generate GaN layers on sapphire having fewer dislocations than GaN layers generated by conventional deposition techniques. <**IMAGE>**

| (19)                 | Euro                                                                                                      | opäisches Patentamt<br>opean Patent Office<br>ce européen des brevets |      | (11)           | _                                         | EP 0 865 088 A2 |

|----------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|----------------|-------------------------------------------|-----------------|

| (43)<br>(21)<br>(22) | Date of publication:<br>16.09.1998 Bulletin ****/<br>Application number: 983<br>Date of filing: 16.03.199 | /**<br>01948                                                          | (51) | Int. CI.       | H01L 33/00                                |                 |

| 、,                   | NL PT SE<br>Priority: 14.03.1997 .<br>11.03.1998 J                                                        | FR GB GR IE IT LI LU MC<br>JP 8231997                                 | •    | Shima<br>Taken | Katsushi<br>Izu, Mitsuru<br>Noto, Kikurou |                 |

| (72)<br>•            | Inventors:<br>Motoki, Kensaku                                                                             |                                                                       | •    |                | Hisashi<br>tu, Akinori                    |                 |

| •                    | Matsushima, Masato                                                                                        |                                                                       |      |                |                                           |                 |

#### (54) Epitaxial wafer having a gallium nitride epitaxial layer deposited on semiconductor substrate and method for preparing the same

Patent published on CD-ROM : ESPACE 98/064, FIRST 98/004

comprising a (111) substrate of a semiconductor having second GaN layer having a thickness of cubic crystal structure, a first GaN layer having a more and a method for preparing it. </br>

(57) The present invention provides an epitaxial wafer thickness of 60 nanometers or more, a second GaN layer having a thickness of 0.1µm or

| (19)                 | <i>)</i> )                                                                                | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |      | (11)     | EP 0 864 672 A3                                                     |

|----------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|----------|---------------------------------------------------------------------|

| (43)<br>(21)<br>(22) | Date of publication<br>16.09.1998 Bulletin<br>Application number<br>Date of filing: 12.03 | n ****/**<br>:: 98301842                                                        | (51) | Int. Cl. | C30B 2 3/02 , C30B 29/40,<br>C23C 16/34, C23C 16/44,<br>H01L 21/205 |

| (84)<br>(30)<br>(71) | NL PT SE                                                                                  | ES FI FR GB GR IE IT LI LU MC<br>997 GB 9705233                                 | •    | Kean,    | er, Stewart<br>Alistair<br>In, Geoffrey                             |

| (72)                 | Inventors:                                                                                |                                                                                 |      |          |                                                                     |

#### (54) Molecular beam epitaxy method

Patent published on CD-ROM : ESPACE 98/063, FIRST 98/004, ESPACE 99/032

(57) An epitaxial deposit of GaN is formed on a substrate S by molecular beam epitaxy. The substrate S is located in a vacuum chamber 10 containing a heated support 12 for the substrate S. The chamber 10 is fitted with an exhaust conduit 16 and connected with an ultra high vacuum pump 14. An ammonia supply conduit 20 is adjustably mounted in the chamber 10. The inner end of the exhaust conduit 16 defines an exhaust outlet 18 of the chamber 10, whilst the first supply conduit

20 has an ammonia outlet 22 opening into the chamber 10. The outlet 22 and the vacuum outlet 18 are disposed adjacent the substrate S. The ammonia outlet 22 of the first supply conduit 20 is disposed nearer to the substrate S than those of conventionally positioned effusion cells 24 and 26 defining second and further supply conduits respectively for gallium and another elements to be supplied in elemental form to the vacuum chamber 10.

| (19) | <i>)</i> )                                                                                 | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |      | (11)     | _                               | EP 0 846 79                | 91 A1 |

|------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|----------|---------------------------------|----------------------------|-------|

| . ,  | Date of publication:<br>10.06.1998 Bulletin<br>Application number<br>Date of filing: 05.12 | 1 ****/**<br>: 97121460                                                         | (51) | Int. CI. | C30B                            | <b>2 5/02</b> , C30B 29/40 |       |

| . ,  | NL PT SE                                                                                   | ES FI FR GB GR IE IT LI LU MC<br>996 JP 32526096                                | •    | lkeda,   | shima, Ka<br>Masao<br>ka, Satos |                            | -     |

| (72) | Inventors:                                                                                 |                                                                                 |      |          |                                 |                            |       |

# (54) Method for growing nitride III-V compound semiconductor layers and method for fabricating a nitride III-V compound semiconductor substrate

Patent published on CD-ROM : ESPACE 98/039, FIRST 98/003

(57) A method for growing nitride III-V compound semiconductor layers, comprises the steps of: growing a first BwAlxGayInzN layer (where  $0 \le w \le 1$ ,  $0 \le x \le 1$ ,  $0 \le y \le 1$ ,  $0 \le y \le 1$ , and w+x+y+z=1) on a substrate by first vapor deposition at a growth rate not higher than  $4\mu$ m/h; and growing a second BwAlxGayInzN layer (where  $0 \le w \le 1$ ,  $0 \le x \le 1$ ,  $0 \le y \le 1$ ,  $0 \le z \le 1$  and w+x+y+z=1) on the first BwAlxGayInzN layer by second vapor deposition at a growth rate higher than  $4\mu$ m/h and not higher than 200 $\mu$ m/h. A method for fabricating a nitride III-V

compound semiconductor substrate, comprises the steps of: growing a first BwAlxGayInzN layer (where  $0 \le w \le 1$ ,  $0 \le x \le 1$ ,  $0 \le y \le 1$ ,  $0 \le z \le 1$  and w + x + y + z = 1) on a substrate by first vapor deposition at a growth rate not higher than  $4\mu m/h$ ; growing a second BwAlxGayInzN layer (where  $0 \le w \le 1$ ,  $0 \le x \le 1$ ,  $0 \le y \le 1$ ,  $0 \le y \le 1$  and w + x + y + z = 1) on the first BwAlxGayInzN layer by second vapor deposition at a growth rate higher than  $4\mu m/h$  and not higher than  $200\mu m/h$ ; and removing the substrate. *<IMAGE>*

| (19) | Europäisches Patentamt<br>European Patent Office                                          |                                                                                                                                                                                    |

|------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Office européen des brevets                                                               | (11) EP 0 811 708 A3                                                                                                                                                               |

| (12) | EUROPEAN PA                                                                               | TENT APPLICATION                                                                                                                                                                   |

| (88) | Date of publication A3:<br>11.11.1998 Bulletin 1998/46                                    | (51) Int Cl. <sup>6</sup> : C30B 23/02, C30B 29/38                                                                                                                                 |

| (43) | Date of publication A2:<br>10.12.1997 Bulletin 1997/50                                    |                                                                                                                                                                                    |

| (21) | Application number: 97303785.6                                                            | •                                                                                                                                                                                  |

| (22) | Date of filing: 03.06.1997                                                                |                                                                                                                                                                                    |

| (84) | Designated Contracting States:<br>AT BE CH DE DK ES FI FR GB GR IE IT LI LU M<br>NL PT SE | <ul> <li>(72) Inventors:</li> <li>Tanaka, Motoyuki</li> <li>1-1. Koyakita 1-chome, Itami-shi, Hyogo (JP)</li> <li>Sogabe, Kouichi</li> </ul>                                       |

| (30) | Priority: 04.06.1996 JP 141236/96<br>11.04.1997 JP 94078/97                               | 1-1. Koyakita 1-chome, Itami-shi, Hyogo (JP)                                                                                                                                       |

| (71) | Applicant: SUMITOMO ELECTRIC INDUSTRIES<br>LTD.<br>Osaka-shi, Osaka 541 (JP)              | <ul> <li>(74) Representative: Rackham, Stephen Neil</li> <li>GILL JENNINGS &amp; EVERY,</li> <li>Broadgate House,</li> <li>7 Eldon Street</li> <li>London EC2M 7LH (GB)</li> </ul> |

#### (54) Single crystal of nitride and process for preparing it

(57) A single crystal of a nitride having a length of not less than 10 mm, a width of not less than 10 mm and a thickness of not less than 300  $\mu$ m, or having a length of not less than 20 mm and a diameter of not less than 10  $\mu$ m. In the production of the single crystal, either a mixed powder composed of a nitride powder and an oxide powder or an amorphous nitride powder is provided as a source material powder, the source material powder is heated in a nitrogen atmosphere or in a nitrogen

atmosphere containing hydrogen and/or carbon at a temperature below the sublimation temperature or melting temperature of the nitride to decompose and vaporize the nitride powder, and the decomposed and vaporized component is subjected to crystal growth from the vapor phase on a substrate. The nitride single crystal is useful as a bulk material for heat sinks, electric and electronic components, such as semiconductors, optical components, and components of electric equipment and office automation equipment.

Printed by Jouve, 75001 PARIS (FR)

Europäisches Patentamt (19)European Patent Office Office européen des brevets (11)(43) Date of publication: (51) Int. Cl. C30B 23/02, C30B 29/40 03.12.1997 Bulletin \*\*\*\*/\*\* (21) Application number: 97303690 (22) Date of filing: 02.06.1997 (84) Designated Contracting States: Bestwick, Timothy David AT BE CH DE DK ES FI FR GB GR IE IT LI LU MC NL PT SE Hooper, Stewart Edward 01.06.1996 GB 9611471 (30) Priority: (71) Applicants: Duggan, Geoffrey SHARP KABUSHIKI KAISHA Cheng, Tin Sun THE UNIVERSITY OF NOTTINGHAM Foxon, Charles Thomas Bayley (72) Inventors:

#### (54) Method of forming a compound semiconductor film

Patent published on CD-ROM : ESPACE 97/073, FIRST 97/009

smooth, of forming (57) A method а continuous GaN film in which Ga is caused to arrive at a sapphire substrate in accordance with a first arrival rate profile over a growth period during which said film is formed, and nitrogen is caused to arrive at said substrate in accordance with a second arrival rate profile over said growth period. The first and second arrival rate profiles are such that the Ga and N are caused to arrive simultaneously at the substrate over said growth period and so that (i) during an initial part of said growth period, growth of the film takes place under a stoichiometric excess of Ga and subsequent during а part of (ii) the growth period, growth of the film takes place under a stoichiometric excess of N. <IMAGE>

# EP 0 810 307 A2

| (19)                         | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets                                                                                                                                                                                                         | (11) EP 0 801 156 A2                                                                              |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| (43)<br>(21)<br>(22)         | Date of publication:<br><b>15.10.1997 Bulletin</b> ****/**<br>Application number: <b>97302033</b><br>Date of filing: <b>25.03.1997</b>                                                                                                                                                  | (51) Int. Cl. <b>C30B 25/02</b> , C30B 29/40,<br>H01L 21/205                                      |

| (84)<br>(30)<br>(71)<br>(72) | Designated Contracting States:<br>DE FR GB<br>Priority: 25.03.1996 JP 6776296<br>21.03.1997 JP 8757097<br>Applicant: SUMITOMO ELECTRIC INDUSTRIES,<br>LIMITED<br>Inventors:<br>Okahisa, Takuji, c/oSumitomo Electric Ind. Ltd.<br>Shimazu, Mitsuru, Sumitomo Electric Industries<br>Ltd | <ul> <li>Motoki, Kensaku, Sumitomo Electric Industries<br/>Ltd.</li> <li>Seki, Hisashi</li> </ul> |

### (54) Process for vapor phase epitaxy of compound semiconductor

Patent published on CD-ROM : ESPACE 97/063, FIRST 97/008

(57) The present invention provides a process for nitride forming a high quality epitaxial compound semiconductor gallius layer of indium gallium nitride<x<1) on a substrate (1). GaN

nitrideepitaxially galliumepitaxial GaN

| (19)                 | <u>))</u>                                                                                 | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets |      | (11)           | EP 0 720 240 A2                           |

|----------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|----------------|-------------------------------------------|

| (43)<br>(21)<br>(22) | Date of publication:<br>03.07.1996 Bulletin<br>Application number<br>Date of filing: 21.1 | n ****/**<br>∵ 95120238                                                         | (51) | Int. Cl.       | H01L 3 3/00 , H01L 21/205                 |

| (84)                 | Designated Contra<br>DE FR GB NL                                                          | cting States:                                                                   | •    | Matsusł        | nima, Masato, c/o Sumitomo Elec. Ind.,    |

| (30)                 | ,                                                                                         | 994 JP 33779794<br>195 JP 6804895                                               |      | Ltd            | r .                                       |

| (71)                 | Applicant: SUMITO                                                                         | DMO ELECTRIC INDUSTRIES,                                                        | •    | Matsuba        | ara, Hideki, c/o Sumitomo Elec. Ind., Ltd |

| (72)                 | Inventors:<br><b>Miura, Yoshiki, c</b> /                                                  | o Sumitomo Electric Ind., Ltd.                                                  | •    | Takagis<br>Ltd | hi, Shigenori, c/o Sumitomo Elec. Ind.,   |

| •                    |                                                                                           | /o Sumitomo Electric Ind., Ltd                                                  | •    | Seki, Hi       |                                           |

| •                    | Takemoto, Kikuro<br>Ltd                                                                   | u, c/o Sumitomo Electric Ind.,                                                  |      | NOUKITU        | , Akinori                                 |

#### (54) Epitaxial wafer and method of preparing the same

Patent published on CD-ROM : ESPACE 96/036, FIRST 96/005

(57) Provided are an epitaxial wafer of high performance which is applicable to a light emitting device, for example, and a method which can industrially prepare the same. The epitaxial wafer comprises a substrate (1) of a compound semiconductor selected from a group consisting of GaAs, GaP, InAs and InP, a buffer layer (2), consisting if GaN, of 10 nm to 80 nm in thickness which is formed on the substrate (1),

and an epitaxial layer (3), containing GaN, which is formed on the buffer layer (2). The buffer layer (2) is formed at a first temperature by organic metal chloride vapor phase epitaxy, while the epitaxial layer (3) is formed at a second temperature, which is higher than the first temperature, by the organic metal chloride vapor phase epitaxy.

<IMAGE>

EP 0720240 12/22/00 13:51:38 page -1-

Europäisches Patentamt (19)European Patent Office Office européen des brevets (11)EP 0 713 542 A1 (43) Date of publication: (51) Int. Cl. C30B 11/00, C30B 11/12, 29.05.1996 Bulletin \*\*\*\*/\*\* C30B 29/40 (21) Application number: 94913850 (87) International publication number: (22) Date of filing: 27.04.1994 WO 95/04845 (29.05.1996 Gazette \*\*\*\*/\*\*) (84) Designated Contracting States: JUN, Jan AT BE CH DE DK ES FR GB GR IE IT LI LU MC NL PT SE GRZEGORY, Izabella (30) Priority: 10.08.1993 PL 30001993 (71) Applicant: Centrum badan Wysokocisnieniowych KRUKOWSKI, Stanislaw (72) Inventors: WROBLEWSKI, Miroslaw POROWSKI, Sylwester

(54) CRYSTALLINE MULTILAYER STRUCTURE AND MANUFACTURING METHOD THEREOF

(87) This international application for which the EPO is a designated office has not been republished by the EPO according to article 158(1) EPC.

Cette demande internationale pour laquelle l'OEB est office désigné n'a pas été republiée par l'OEB en vertu de l'article 158(1) CBE.

Diese internationale Anmeldung, für die das EPA Bestimmungsamt ist, würde, gemäß Artikel 158(1) EPÜ, vom EPA nicht wieder veröffentlicht.

Patent published on CD-ROM : ESPACE 96/028, FIRST 96/004, FIRST 95/001, WORLD 95/013

(57) A process for fabricating а multilayer crystalline structure of nitrides of metals from group III of periodic table including GaN, AIN and InN is provided. The process includes the steps of heating a group III metal (26) to a temperature T1 under an equilibrium nitrogen pressure while maintaining group III metal nitride stability to form a first crystal layer of the group III metal nitride. Thereafter the method includes the step of forming a second crystal layer (28) of the group III metal nitride by decreasing the nitrogen pressure such that the second crystal laver grows on the first laver with a growth rate slower than the growth rate of the first laver at a temperature T2 not greater than temperature T1. The second laver (28) grows on at least a portion of the first layer at a predetermined thickness under the new nitrogen pressure.

(57) Procédé de fabrication d'une structure

multicouche cristalline de nitrures de métaux du groupe III du tableau périodique, notamment le GaN, l'AiN et l'InN. Le procédé consiste à porter un métal du groupe III (26) à une température (T1) sous une pression d'équilibre d'azote, et simultanément à préserver la stabilité du nitrure du métal du groupe III, de manière à former une première couche cristalline du nitrure du métal du groupe III; puis à former une seconde couche cristalline (28) du nitrure du métal du groupe III par réduction de la pression de l'azote de manière à provoquer la croissance de la seconde couche cristalline sur la première couche à une vitesse inférieure à la vitesse de croissance de la première couche, et à une température (T2) égale ou inférieure à la température (T1). La croissance de la seconde couche (28) se produit sur au moins une partie de la première couche et selon une épaisseur prédéterminée sous la nouvelle pression d'azote.

(19)

(43) Date of publication:

15.05.1996 Bulletin \*\*\*\*/\*\*

(21) Application number: 95914510

(22) Date of filing: 05.04.1995

(11)

# EP 0 711 853 A1

(51) Int. CI. C30B 23/00, H01L 21/203

(87) International publication number:

WO 95/27815 (15.05.1996 Gazette \*\*\*\*/\*\*)

| (84)  | Designated Contracting States:      |   | Inventors:                                 |

|-------|-------------------------------------|---|--------------------------------------------|

|       | DE FR GB                            | • | TOGAWA, Seiji, Japan Energy Corporation    |

| (30)  | Priority: 08.04.1994 JP 9396394     |   |                                            |

|       | 16.09.1994 JP 24680394              | • | OKAZAKI, Hitoshi, Japan Energy Corporation |

| (71)  | Applicant: JAPAN ENERGY CORPORATION |   |                                            |

| · · / |                                     |   |                                            |

|       |                                     |   |                                            |

#### (54) METHOD FOR GROWING GALLIUM NITRIDE COMPOUND SEMICONDUCTOR CRYSTAL, AND GALLIUM NITRIDE COMPOUND SEMICONDUCTOR DEVICE

Patent published on CD-ROM : ESPACE 96/025, FIRST 96/004, FIRST 95/006, WORLD 95/071

(57) In a method for growing a gallium nitride semiconductor crystal on a single-crystal substrate, the (011) or (101) face of perovskite containing group 13 (3B) rare-earth elements is used as the single-crystal substrate, so that a gallium nitride semiconductor crystal having an excellent crystallinity is formed on the surface of the substrate by epitaxial growth. (57) Procédé de tirage d'un cristal semi-conducteur à base de nitrure de gallium sur un substrat monocristallin, selon lequel la face (011) ou (101) d'éléments de terres rares 13 (3B) du groupe contenant de la pérovskite est utilisé comme substrat monocristallin, de sorte que l'on obtient par croissance épitaxiale un cristal semi-conducteur de nitrure de gallium présentant un excellente cristallinité sur la surface du substrat.

EP 0711853 12/22/00 13:52:43 page -1-

| (19) | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets       | (11) EP 0 647 730 A3                                                                                                                           |  |  |  |  |  |

|------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| (12) | EUROPEAN PATI                                                                         | ENT APPLICATION                                                                                                                                |  |  |  |  |  |

| (88) | Date of publication A3:<br>28.01.1998 Bulletin 1998/05                                | (51) Int. Cl. <sup>6</sup> : <b>C30B 29/38</b> , H01L 21/00                                                                                    |  |  |  |  |  |

| (43) | (43) Date of publication A2:<br>12.04.1995 Bulletin 1995/15                           |                                                                                                                                                |  |  |  |  |  |

| (21) | Application number: 94115739.8                                                        | •                                                                                                                                              |  |  |  |  |  |

| (22) | Date of filing: 06.10.1994                                                            |                                                                                                                                                |  |  |  |  |  |

| (84) | Designated Contracting States:<br>DE FR GB                                            | <ul> <li>Watabe, Shinichi,</li> <li>c/o Itaml Works of</li> <li>Itami-shi, Hyogo 664 (JP)</li> </ul>                                           |  |  |  |  |  |

|      | Priority: 08.10.1993 JP 253098/93<br>31.03.1994 JP 62813/94<br>31.03.1994 JP 62815/94 | <ul> <li>Okagawa, Hiroaki,</li> <li>c/o Itami Works of</li> <li>Itami-shi, Hyogo 664 (JP)</li> <li>Hiramatsu, Kazumasa</li> </ul>              |  |  |  |  |  |

| (71) | Applicant:<br>Mitsubishi Cable Industries, Ltd.<br>Hyogo-ken 660 (JP)                 | Yokkaichi-shi, Mie 510 (JP)<br>(74) Representative:                                                                                            |  |  |  |  |  |

|      | Inventors:<br>Tadatomo, Kazuyuki,<br>c/o Itami Works of<br>Itami-shi, Hyogo 664 (JP)  | von Kreisler, Alek, DiplChem. et al<br>Patentanwälte,<br>von Kreisler-Selting-Werner,<br>Bahnhofsvorplatz 1 (Deichmannhaus)<br>50667 Köln (DE) |  |  |  |  |  |

#### (54) GaN single crystal

(57) A GaN single crystal having a full width at halfmaximum of the double-crystal X-ray rocking curve of 5-250 sec and a thickness of not less than 80  $\mu$ m, a method for producing the GaN single crystal having superior quality and sufficient thickness permitting its use as a substrate and a semiconductor light emitting element having high luminance and high reliability, comprising, as a substrate, the GaN single crystal having superior quality and/or sufficient thickness permitting its use as a substrate.

Printed by Xerox (UK) Business Services 2.15.8/3.4

(12)

Europäisches Patentamt European Patent Office Office européen des brevets

1 Publication number:

0 622 858 A2

### EUROPEAN PATENT APPLICATION

- 2) Application number: 94106587.2

- ⑤ Int. CI.⁵: H01L 33/00, H01L 31/0224, H01L 21/28

- 2 Date of filing: 27.04.94

- (3) Priority: 28.04.93 JP 124890/93 (1) Applicant: NICHIA CHEMICAL INDUSTRIES, LTD. 31.05.93 JP 129313/93 491-100, Oka, 28.07.93 JP 207274/93 21.09.93 JP 234684/93 Kaminaka-cho 21.09.93 JP 234685/93 Anan-shi, Tokushima-ken (JP) 08.10.93 JP 253171/93 28.01.94 JP 8726/94 Inventor: Nakamura, Shuji, c/o Nichia Chem. 28.01.94 JP 8727/94 Ind., Ltd. 491-100, Oka, Kaminaka-cho Anan-shi, Tokushima-ken (JP) 43 Date of publication of application: 02.11.94 Bulletin 94/44 inventor: Yamada, Takao, c/o Nichia Chem. Ind., Ltd. 491-100, Oka, Kaminaka-cho Designated Contracting States: DE FR GB IT NL Anan-shi, Tokushima-ken (JP) Inventor: Senoh, Masayuki, c/o Nichia Chem. Ind., Ltd. 491-100, Oka, Kaminaka-cho Anan-shi, Tokushima-ken (JP) Inventor: Bando, Kanji, c/o Nichia Chem. Ind., Ltd. 491-100, Oka, Kaminaka-cho Anan-shi, Tokushima-ken (JP) Inventor: Yamada, Motokazu, c/o Nichia Chem. Ind., Ltd. 491-100, Oka, Kaminaka-cho Anan-shi, Tokushima-ken (JP) 7 Representative: von Bezold, Dieter, Dr. Dr. Dieter von Bezold Dipl.-Ing. Peter Schütz **Dipl.-Ing. Wolfgang Heusler Brienner Strasse 52** D-80333 München (DE)

Gallium nitride-based III-V group compound semiconductor device and method of producing the same.

(T) A gallium nitride-based III-V Group compound semiconductor device (10) has a gallium nitride-based III-V Group compound semiconductor layer (13) provided over a substrate (11), and an ohmic electrode (15) provided in contact with the semiconductor layer (13). The ohmic electrode (15) is formed of a metallic material, and has been annealed.

(11)

## EP 0 609 799 A3

(43) Date of publication A2: 10.08.1994 Bulletin \*\*\*\*/\*\*

(19)

- (21) Application number: 94101374

- (22) Date of filing: 31.01.1994

### (51) Int. Cl. **H01L 2 1/20**, H01L 21/36, C30B 25/18

(84) Designated Contracting States:

INCORPORATED

DE FR GB IT NL

(30) Priority:

02.02.1993 US 12556

(71) Applicant: TEXAS INSTRUMENTS

(72) Inventor: Summerfeit, Scott R.

#### (54) Improvements in heteroepitaxy by large surface steps

Patent published on CD-ROM : ESPACE 94/056, FIRST 94/005, ESPACE 97/024

(57) A method for heteroepitaxial growth and the device wherein a single crystal ceramic substrate 20, preferably Y stabilized zirconia, MgAl2O4, Al2O3, 3C-SiC, 6H-SiC or MgO is cut and polished at from about 1.0 to about 10 degrees off axis to produce a substantially flat surface. The atoms on the surface are redistributed on the surface to produce surface

steps 22 of at least three lattice spacings. An optional epitaxially grown ceramic buffer layer, preferably AIN or GaN, is then formed on the substrate. Then a layer of semiconductor 24, preferably SiC, AIN when the buffer layer is used and is not AIN or GaN is grown over the substrate and buffer layer, if used. *<IMAGE>*

(19)

(43) Date of publication:

05.01.1994 Bulletin \*\*\*\*/\*\*

(21) Application number: 92908776

(22) Date of filing: 18.03.1992

(11)

## EP 0 576 566 A1

(51) Int. Cl. H01L 2 1/20 3, H01L 21/205

(87) International publication number:

WO 92/16966 (05.01.1994 Gazette \*\*\*\*/\*\*)

| (84) | Designated | d Contracting | States:   | (71) | Applicant: TRUSTEES OF BOSTON UNIVERSITY |

|------|------------|---------------|-----------|------|------------------------------------------|

| (30) | Priority:  | 18.03.1991    | US 670692 | (72) | Inventor: MOUSTAKAS, Theodore, D.        |

# (54) A METHOD FOR THE PREPARATION AND DOPING OF HIGHLY INSULATING MONOCRYSTALLINE GALLIUM NITRIDE THIN FILMS

(87) This international application for which the EPO is a designated office has not been republished by the EPO according to article 158(1) EPC.

Cette demande internationale pour laquelle l'OEB est office désigné n'a pas été republiée par l'OEB en vertu de l'article 158(1) CBE.

Diese internationale Anmeldung, für die das EPA Bestimmungsamt ist, würde, gemäß Artikel 158(1) EPÜ, vom EPA nicht wieder veröffentlicht.

Patent published on CD-ROM : ESPACE 94/001, FIRST 94/001, FIRST 92/006, WORLD 92/040

(57) This invention relates to a method of preparing highly insulating GaN single crystal films in a molecular beam epitaxial growth chamber. A single crystal substrate is provided with the appropriate lattice match for the desired crystal structure of GaN. A molecular beam source of Ga and source of activated atomic and ionic nitrogen are provided within the growth chamber. The desired film is deposited by exposing the substrate to Ga and nitrogen sources in a two step growth process using a low temperature nucleation step and a high temperature growth step. The low temperature process is carried out at 100-400 °C and the high temperature process is carried out at 600-900 °C. The preferred source of activated nitrogen is an electron cyclotron resonance microwave plasma. (57) Procédé de préparation de couches

monocristallines de GaN très isolant dans une chambre de croissance épitaxiale à faisceau moléculaire. On confère à un substrat monocristallin la structure en treillis appropriée pour obtenir la structure cristalline de GaN désirée. Une source de faisceaux moléculaires de Ga et une source d'azote atomique et ionique activé sont présentes dans la chambre de croissance. On dépose la couche désirée en exposant le substrat aux sources de Ga et d'azote dans un processus de croissance en deux étapes comprenant une étape de nucléation à basse température et une étape de croissance à haute température. Le processus à basse température est exécuté à 100-400 °C et le processus à haute température est exécuté à 600-900 °C. La source préférée d'azote activé est un plasma à micro-ondes de résonance produit par un cyclotron à électrons.

| (19) | <u>)</u> |

|------|----------|

|      |          |

(1) Publication number:

0 559 326 A1

(12)

EUROPEAN PATENT APPLICATION

(1) Application number: 93300724.7

2 Date of filing: 01.02.93

③ Priority: 06.03.92 JP 49711/92

Date of publication of application:

08.09.93 Bulletin 93/36

Designated Contracting States:

DE FR GB

Applicant: PIONEER ELECTRONIC CORPORATION

No. 4-1, Meguro 1-chome

Meguro-ku Tokyo-to(JP)

Applicant: Amano, Hiroshi

Nijigaoka-higashidanchi Room No. 19-103,

No. 21, Kamioka-machi 2-chome, Meitou-ku

Nagoya-shi, Aichi-ken(JP)

Applicant: Akasaki, Isamu

No. 1-38-805, Jyoshin 1-chome, Nishi-ku

Nagoya-shi, Aichi-ken(JP)

2 Inventor: Watanabe, Atsushi, c/o Pioneer

Electronic Corp. Sougou Kenkyusho, No. 6-1-1 Fujimi Tsurugashima-shi, Saitama-ken(JP) Inventor: Amano, Hiroshi, Nijigaoka-higashidanchi Room No. 19-103, No. 21, Kamioka-machie 2-chome Meitou-ku, Nagoya-shi, Aichi-ken(JP) Inventor: Hiramatsu, Kazumasa No. 4-22, Shibata 1-chome Yokkaichi-shi, Mie-ken(JP) Inventor: Akasaki, Isamu No. 1-38-805, Jyoshin 1-chome, Nishi-ku Nagoya-shi, Aichi-ken(JP)

(i) Int. Cl.5: C30B 25/14, C23C 16/44

Representative: Brunner, Michael John

GILL JENNINGS & EVERY, Broadgate House,

7 Eldon Street

London EC2M 7LH (GB)

(a) Compound semiconductor vapor phase epitaxial device.

A compound semiconductor vapor phase epitaxial device comprises a cylindrical reactor vessel (2), a plurality of flow channels (17, 27) disposed in the reactor vessel, a crystal substrate (7) disposed in one of the flow channels, a plurality of gas supply pipes for respectively supplying gas containing element of compound to be grown on the crystal substrate and at least one slit (10) or linearly arranged fine holes (P) communicating adjacent two flow channels so as to extend in a direction normal to a direction of the gas flow to form a laminate layer flow consisting of two or more than two gases at an upstream portion of location of the crystal substrate.

Rank Xerox (UK) Business Services (3, 10/3.6/3.3.1)

| (19)                     | <u>)</u>                              | Europäisches Patentamt<br>European Patent Office<br>Office européen des brevets | (1)          | Publication number: 0 497 350 A1                                                                                                                                                                                              |

|--------------------------|---------------------------------------|---------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12                       |                                       | EUROPEAN PAT                                                                    | ENT          | APPLICATION                                                                                                                                                                                                                   |

| (21)<br>(22)             | Application r                         | number: 92101560.8<br>: 30.01.92                                                | <b>(51</b> ) | Int. Cl. <sup>5</sup> : C30B 25/02, H01L 21/20                                                                                                                                                                                |

| (3)<br>(3)<br>(3)<br>(3) | 27.0<br>Date of publi<br>05.08.92 Bul | Contracting States:                                                             |              | Applicant: Nichla Kagaku Kogyo K.K.<br>No. 491-100, Oka Kaminaka-cho<br>Anan-shi Tokushima-ken(JP)<br>Inventor: Nakamura, Shuji, c/o Nichia Kagaku<br>Kogyo K.K.<br>491-100, Oka, Kaminaka-cho<br>Anan-shi, Tokushima-ken(JP) |