# european space agency agence spatiale européenne

Pages 1 to 41

# INTEGRATED CIRCUITS, SILICON MONOLITHIC, CMOS, 16 CHANNEL MULTIPLEXER, RADIATION HARDENED, BASED ON TYPE HS-1840RH

ESA/SCC Detail Specification No. 9408/019

# space components coordination group

|            |               | Appro         | Approved by                        |  |  |  |  |

|------------|---------------|---------------|------------------------------------|--|--|--|--|

| Issue/Rev. | Date          | SCCG Chairman | ESA Director General or his Deputy |  |  |  |  |

| Issue 2    | February 1999 | Sannott       | Hom                                |  |  |  |  |

|            |               |               |                                    |  |  |  |  |

|            |               |               |                                    |  |  |  |  |

|            |               |               |                                    |  |  |  |  |

PAGE 2

ISSUE 2

# **DOCUMENTATION CHANGE NOTICE**

|                |              | DOCUMENTATION CHANGE NOTICE |                  |

|----------------|--------------|-----------------------------|------------------|

| Rev.<br>Letter | Rev.<br>Date | CHANGE<br>Reference Item    | Approved DCR No. |

|                |              |                             | DCR No.          |

|                |              |                             |                  |

PAGE 3

ISSUE 2

# **TABLE OF CONTENTS**

| 1.    | GENERAL                                                               | <u>Page</u><br><b>5</b> |

|-------|-----------------------------------------------------------------------|-------------------------|

| 1.1   | Scope                                                                 | 5                       |

| 1.2   | Component Type Variants                                               | 5                       |

| 1.3   | Maximum Ratings                                                       | 5                       |

| 1.4   | Parameter Derating Information                                        | 5                       |

| 1.5   | Physical Dimensions                                                   | 5                       |

| 1.6   | Pin Assignment                                                        | 5                       |

| 1.7   | Truth Table                                                           | 5                       |

| 1.8   | Circuit Schematic                                                     | 5                       |

| 1.9   | Functional Diagram                                                    | 5                       |

| 1.10  | Handling Precautions                                                  | 5                       |

| 1.11  | Input Protection Networks                                             | 6                       |

| 2.    | APPLICABLE DOCUMENTS                                                  | 6                       |

| 3.    | TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS                  | 6                       |

| 4.    | REQUIREMENTS                                                          | 14                      |

| 4.1   | General                                                               | 14                      |

| 4.2   | Deviations from Generic Specification                                 | 14                      |

| 4.2.1 | Deviations from Special In-Process Controls                           | 14                      |

| 4.2.2 | Deviations from Final Production Tests                                | 14                      |

| 4.2.3 | Deviations from Burn-in and Electrical Measurements                   | 14                      |

| 4.2.4 | Deviations from Qualification Tests                                   | 14                      |

| 4.2.5 | Deviations from Lot Acceptance Tests                                  | 14                      |

| 4.2.6 | Radiation Screening Procedure                                         | 14                      |

| 4.3   | Mechanical Requirements                                               | 15                      |

| 4.3.1 | Dimension Check                                                       | 15                      |

| 4.3.2 | Weight                                                                | 15                      |

| 4.4   | Materials and Finishes                                                | 15                      |

| 4.4.1 | Case                                                                  | 15                      |

| 4.4.2 | Lead Material and Finish                                              | 15                      |

| 4.5   | Marking                                                               | 15                      |

| 4.5.1 | General                                                               | 15                      |

| 4.5.2 | Lead Identification                                                   | 15                      |

| 4.5.3 | The SCC Component Number                                              | 15                      |

| 4.5.4 | Traceability Information                                              | 16                      |

| 4.6   | Electrical Measurements                                               | . 16                    |

| 4.6.1 | Electrical Measurements at Room Temperature                           | 16                      |

| 4.6.2 | Electrical Measurements at High and Low Temperatures                  | 16                      |

| 4.6.3 | Circuits for Electrical Measurements                                  | 16                      |

| 4.7   | Burn-in Tests                                                         | 16                      |

| 4.7.1 | Parameter Drift Values                                                | 16                      |

| 4.7.2 | Conditions for H.T.R.B. and Burn-in                                   | 16                      |

| 4.7.3 | Electrical Circuits for H.T.R.B. and Burn-in                          | 16                      |

| 4.8   | Environmental and Endurance Tests                                     | 38                      |

| 4.8.1 | Electrical Measurements on Completion of Environmental Tests          | 38                      |

| 4.8.2 | Electrical Measurements at Intermediate Points during Endurance Tests | 38                      |

| 4.8.3 | Electrical Measurements on Completion of Endurance Tests              | 38                      |

| 4.8.4 | Conditions for Operating Life Tests                                   | 38                      |

| 4.8.5 | Electrical Circuits for Operating Life Tests                          | 38                      |

| 4.8.6 | Conditions for High Temperature Storage Test                          | 38                      |

PAGE 4

| TABLES | <u>3</u>                                                                                                                     | <u>Page</u> |

|--------|------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1(a)   | Type Variants                                                                                                                | 7           |

| 1(b)   | Maximum Ratings                                                                                                              | 7           |

| 2      | Electrical Measurements at Room Temperature - d.c. Parameters                                                                | 17          |

| 0(-)   | Electrical Measurements at Room Temperature - a.c. Parameters                                                                | 20<br>21    |

| 3(a)   | Electrical Measurements at High Temperature - d.c. Parameters  Electrical Measurements at High Temperature - a.c. Parameters | 24          |

| 3(b)   | Electrical Measurements at high remperature - a.c. Parameters                                                                | 25          |

| 3(0)   | Electrical Measurements at Low Temperature - a.c. Parameters                                                                 | 28          |

| 4      | Parameter Drift Values                                                                                                       | 34          |

| 5(a)   | Conditions for High Temperature Reverse Bias Burn-in                                                                         | 35          |

| 5(b)   | Conditions for Burn-in, Dynamic and Operating Life Tests                                                                     | 35          |

| 6      | Electrical Measurements on Completion of Environmental Tests and at Intermediate Points                                      | 39          |

|        | and on Completion of Endurance Testing                                                                                       |             |

| FIGURE | <u>≣S</u>                                                                                                                    |             |

| 1      | Parameter Derating Information                                                                                               | 8           |

| 2      | Physical Dimensions                                                                                                          | 9           |

| 3(a)   | Pin Assignment                                                                                                               | 10          |

| 3(b)   | Truth Table                                                                                                                  | 11          |

| 3(c)   | Circuit Schematic                                                                                                            | 12          |

| 3(d)   | Functional Diagram                                                                                                           | 13          |

| 3(e)   | Input Protection Network                                                                                                     | 13          |

| 4      | Circuits for Electrical Measurements                                                                                         | 29          |

| 5(a)   | Electrical Circuit for High Temperature Reverse Bias Burn-in and Accelerated Life                                            | 36          |

| 5(b)   | Electrical Circuit for Burn-in, Dynamic and Operating Life Tests                                                             | 37          |

| APPEN  | DICES (Applicable to specific Manufacturers only)                                                                            |             |

| 'A'    | Agreed Deviations for Harris (US)                                                                                            | 40          |

PAGE

ISSUE 2

5

### 1. **GENERAL**

#### 1.1 SCOPE

This specification details the ratings, physical and electrical characteristics, test and inspection data for a silicon, monolithic, radiation hardened, 16 channel multiplexer, constructed with the Linear Dielectric CMOS technology, based on Type HS-1840RH. It shall be read in conjunction with ESA/SCC Generic Specification No. 9000, the requirements of which are supplemented herein.

### 1.2 COMPONENT TYPE VARIANTS

Variants of the basic type integrated circuits specified herein, which are also covered by this specification, are given in Table 1(a).

### 1.3 MAXIMUM RATINGS

The maximum ratings, which shall not be exceeded at any time during use or storage, applicable to the integrated circuits specified herein, are as scheduled in Table 1(b).

### 1.4 PARAMETER DERATING INFORMATION

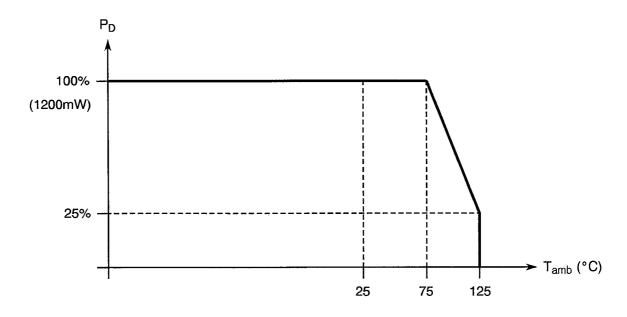

As per Figure 1.

### 1.5 PHYSICAL DIMENSIONS

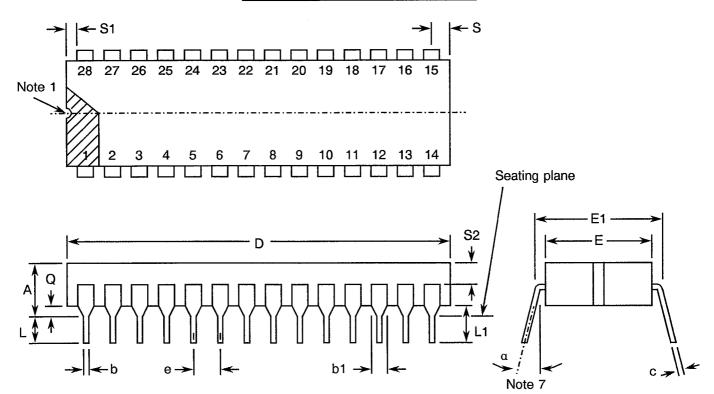

As per Figure 2.

#### 1.6 PIN ASSIGNMENT

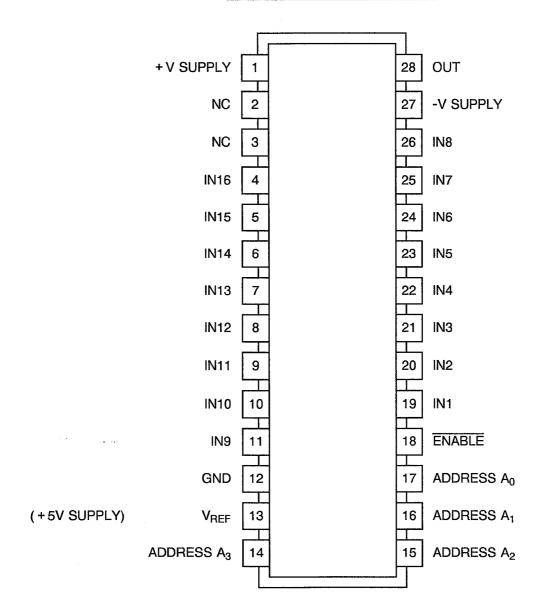

As per Figure 3(a).

### 1.7 TRUTH TABLE

As per Figure 3(b).

### 1.8 CIRCUIT SCHEMATIC

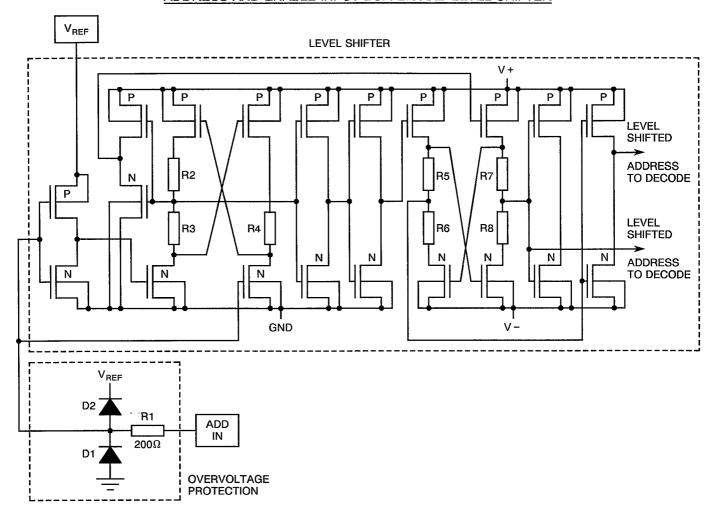

As per Figure 3(c).

### 1.9 FUNCTIONAL DIAGRAM

As per Figure 3(d).

#### 1.10 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, test, packaging, shipping and any handling. Devices may be damaged if the following conditions are exceeded:-

C = 100pF

$R = 1500\Omega$

$V = \pm 400V.$

The following handling practices are recommended:-

- (a) Devices should be handled on benches with conductive and grounded surfaces.

- (b) Ground test equipment and tools.

- (c) Do not handle devices by the terminations.

- (d) Store devices in conductive foam or carriers.

- (e) Avoid use of plastic, rubber or silk in the fabrication and assembly areas.

- (f) Maintain relative humidity above 50%, if practical.

- (g) Ground all handling personnel with a conductive bracelet through a 1.0MΩ resistor to ground.

- (h) Ionised air blowers reduce charge build-up areas where grounding is not possible or desirable.

PAGE

ISSUE 2

6

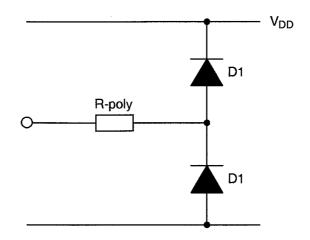

### 1.11 <u>INPUT PROTECTION NETWORKS</u>

Double diode protection shall be incorporated into each input as shown in Figure 3(e).

### 2. APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:-

- (a) ESA/SCC Generic Specification No. 9000 for Integrated Circuits.

- (b) MIL-STD-883, Test Methods and Procedures for Micro-electronics.

- (c) MIL-M-38510, Microcircuits, General Specification for.

### 3. TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESA/SCC Basic Specification No. 21300 shall apply. In addition, the following abbreviations are used:-

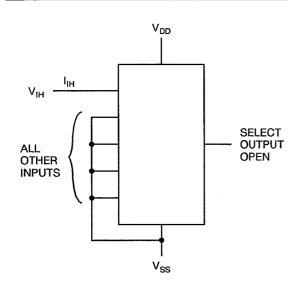

$I_{IH}$  = Input current, high level  $I_{IL}$  = Input current, low level

I<sub>D(OVP)</sub> = Overvoltage protection, leakage current into the drain terminal of an "OFF" switch.

I<sub>S(OVP)</sub> = Overvoltage protection, leakage current into the source terminal of an "OFF" switch.

$I_{+(PSC)}$  = Positive supply current.  $I_{-(PSC)}$  = Negative supply current.

I + (STDBY) = Positive supply standby current. I - (STDBY) = Negative supply standby current.

R<sub>ON</sub> = Switch "ON" resistance.

C<sub>A</sub> = Address capacitance.

C<sub>OS</sub> = Output switch capacitance.

C<sub>IS</sub> = Input switch capacitance.

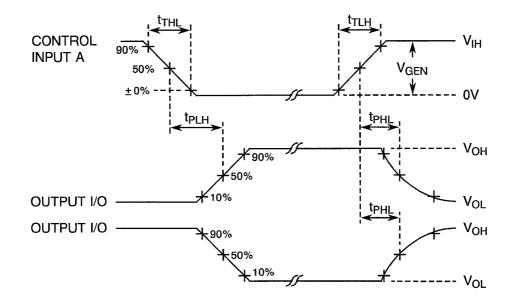

t<sub>PLH1</sub> = Rise Time, Address inputs to I/O channels. t<sub>PHL1</sub> = Fall Time, Address inputs to I/O channels.

t<sub>PLH2</sub> = Rise Time, Enable to I/O channels. t<sub>PHL2</sub> = Fall Time, Enable to I/O channels.

PAGE 7

ISSUE 2

### TABLE 1(a) - TYPE VARIANTS

| VARIANT | CASE  | FIGURE | LEAD MATERIAL AND<br>FINISH |

|---------|-------|--------|-----------------------------|

| 01      | D.I.L | 2      | D2 or G2                    |

| 02      | D.I.L | 2      | D3 or G3                    |

### **TABLE 1(b) - MAXIMUM RATINGS**

| No. | CHARACTERISTICS           | SYMBOL                           | MAXIMUM RATINGS                     | UNITS | REMARKS                  |

|-----|---------------------------|----------------------------------|-------------------------------------|-------|--------------------------|

| 1   | Supply Voltage            | Vcc                              | + 40                                | V     | Between Pins 1<br>and 27 |

| 2   | Reference                 | $V_{REF}$                        | +20                                 | ٧     | to Gnd                   |

| 3   | Digital Input Overvoltage | V <sub>EN</sub> , V <sub>A</sub> | V <sub>REF</sub> + 4.0<br>Gnd - 4.0 | V     |                          |

| 4   | Analog Input Overvoltage  | V <sub>S</sub>                   | +V supply +20<br>-V supply -20      | V     |                          |

| 5   | Device Dissipation        | P <sub>D</sub>                   | 1200                                | mWdc  | Per package.<br>Note 1   |

| 6   | Output Dissipation        | P <sub>DSO</sub>                 | 100                                 | mWdc  | Note 2                   |

| 7   | Operating Temperature     | T <sub>opr</sub>                 | -55 to +125                         | °C    |                          |

| 8   | Storage Temperature       | T <sub>stg</sub>                 | -65 to +150                         | °C    |                          |

| 9   | Soldering Temperature     | T <sub>sol</sub>                 | + 300                               | °C    | Note 3                   |

| 10  | Junction Temperature      | TJ                               | + 175                               | °C    |                          |

#### NOTES

- 1. Derate 8mW/°C above  $T_{amb} = +25$ °C.

- 2. The maximum power dissipation.

- 3. Duration 10 seconds maximum at a distance of not less than 1.5mm from the device body and the same lead shall not be resoldered until 3 minutes have elapsed.

PAGE

ISSUE 2

8

### FIGURE 1 - PARAMETER DERATING INFORMATION

Device Dissipation versus Temperature

PAGE

ISSUE 2

9

### FIGURE 2 - PHYSICAL DIMENSIONS

| SYMBOL   | MILLIM     | ETRES | NOTES |

|----------|------------|-------|-------|

| STIVIBOL | MIN.       | MAX.  | NOTES |

| Α        | -          | 5.08  |       |

| b        | 0.36       | 0.58  | 8     |

| b1       | 1.02       | 1.78  | 2, 8  |

| С        | 0.20       | 0.36  | 8     |

| D        | 36.6       | 37.6  | 4     |

| E        | 13.21      | 13.97 | 4     |

| E1       | 14.99      | 15.75 | 7     |

| E2       | N/A        | N/A   |       |

| E3       | N/A        | N/A   |       |

| е        | 2.54       | BSC   | 5, 9  |

| L        | 3.18       | 4.57  |       |

| L1       | 3.81       | 5.08  |       |

| Q        | 0.51       | 1.27  | 3     |

| Q1       | N/A        | N/A   |       |

| S        | · <b>-</b> | 2.49  | 6     |

| S1       | 0.13       | -     | 6     |

| S2       | N/A        | N/A   |       |

| α        | 0°         | 15°   |       |

### **NOTES**

- Index area; a notch or a pin 1 identification mark shall be located adjacent to pin 1 and shall be located within the shaded area shown. The Manufacturer's identification shall not be used as a pin 1 identification mark.

- 2. The minimum limit for dimension b1 may be 0.58mm for leads number 1, 14, 15 and 28 only.

- 3. Dimension Q shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-centre lid, meniscus and glass overrun.

- The basic pin spacing is 2.54mm between centrelines. Each pin centreline shall be located within ±0.25mm of its exact longitudinal position relative to pins 1 and 28.

- Applies to all 4 corners (leads number 1, 14, 15 and 28), and 40.5 appendix C of MIL-M-38510 shall apply.

- 7. Lead centre when  $\alpha = 0^{\circ}$ . E1 shall be measured at the centreline of the leads (see 40.4 appendix C of MIL-M-38510).

- 8. All leads Increase maximum limit by 0.08mm measured at the centre of the flat, when lead finish A is applied.

- 9. 26 spaces.

PAGE 10

ISSUE 2

### FIGURE 3(a) - PIN ASSIGNMENT

TOP VIEW

PAGE 11

ISSUE 2

# FIGURE 3(b) - TRUTH TABLE

| A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | ĒŃ | "ON" CHANNEL |

|----------------|----------------|----------------|----------------|----|--------------|

| Х              | Х              | Х              | Х              | Н  | NONE         |

| L              | L              | L              | L              | L  | 1            |

| L              | L              | L              | Н              | L  | 2            |

| L              | L              | Н              | · L            | L  | 3            |

| L              | L              | Н              | Н              | L  | 4            |

| L              | Н              | L              | L              | L  | 5            |

| L              | Н              | L              | Н              | L  | 6            |

| L              | Н              | Н              | L              | L  | 7            |

| L              | Н              | Н              | Н              | L  | 8            |

| Н              | Ļ              | L              | L              | L  | 9            |

| Н              | L              | L              | Н              | L  | 10           |

| Н              | L              | Н              | L              | L. | 11           |

| Н              | L              | Н              | Н              | L  | 12           |

| H              | Н              | L              | L              | L  | 13           |

| Н              | Н              | L              | Н              | L  | 14           |

| Н              | Н              | Н              | L.             | L  | 15           |

| Н              | Н              | Н              | Н              | L  | 16           |

PAGE 12

ISSUE 2

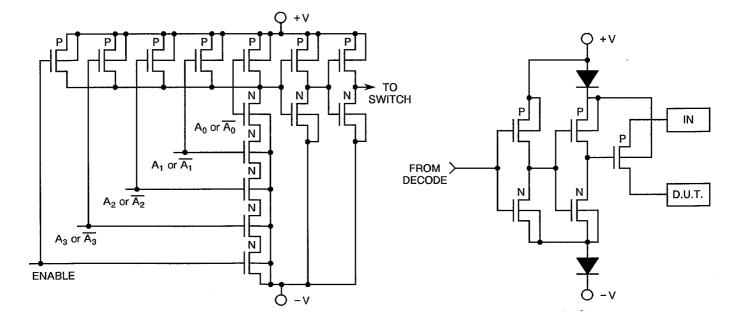

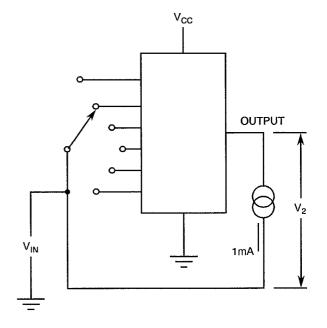

### FIGURE 3(c) - CIRCUIT SCHEMATIC

### ADDRESS AND ENABLE INPUT BUFFER AND LEVEL SHIFTER

### ADDRESS DECODER

### MULTIPLEXER SWITCH

PAGE 13

ISSUE 2

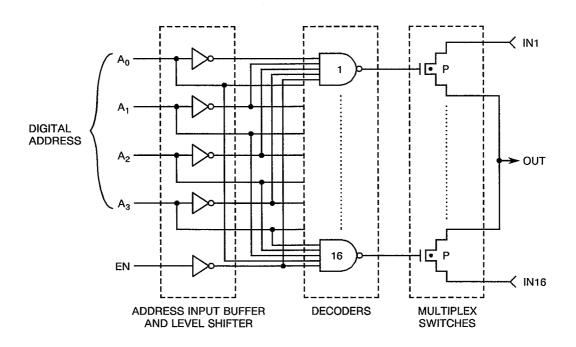

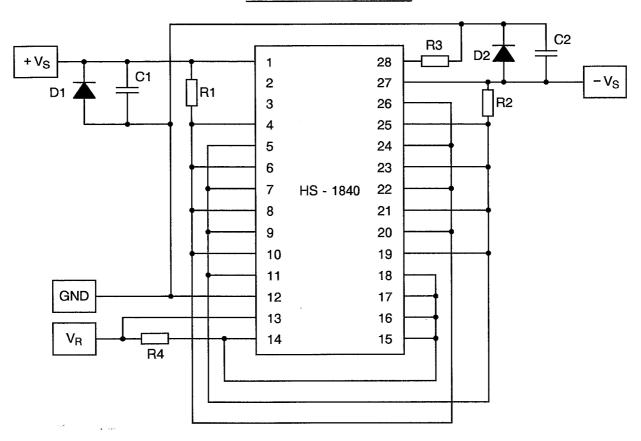

### FIGURE 3(d) - FUNCTIONAL DIAGRAM

### FIGURE 3(e) - INPUT PROTECTION NETWORK

PAGE 14

ISSUE 2

### 4. REQUIREMENTS

### 4.1 GENERAL

The complete requirements for procurement of the integrated circuits specified herein are stated in this specification and ESA/SCC Generic Specification No. 9000 for Integrated Circuits. Deviations from the Generic Specification applicable to this specification only, are listed in Para, 4.2.

Deviations from the applicable Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESA/SCC requirements and do not affect the components' reliability, are listed in the appendices attached to this specification.

### 4.2 DEVIATIONS FROM GENERIC SPECIFICATION

### 4.2.1 <u>Deviations from Special In-process Controls</u>

None.

### 4.2.2 Deviations from Final Production Tests (Chart II)

None.

### 4.2.3 Deviations from Burn-in and Electrical Measurements (Chart III)

(a) Para. 9, "High Temperature Reverse Bias" (H.T.R.B.): Not applicable.

### 4.2.4 Deviations from Qualification Tests (Chart IV)

None.

### 4.2.5 <u>Deviations from Lot Acceptance Tests (Chart V)</u>

None.

### 4.2.6 Radiation Screening Procedure

All devices supplied in accordance with this specification shall be from lots whose samples passed the radiation screening procedure as follows:-

| STEP | RADIATION SCREENING PROCEDURE                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Two (2) probed good samples per wafer will be selected from 20% of the wafers in a run. (All wafers in a "run" will have been processed together through all high temperature processing steps and through metallisation). |

| 2    | The sample die shall be assembled and tested for functionality.                                                                                                                                                            |

| 3    | The sample devices shall be subjected to a Total Dose Radiation level of $2 \times 10^4$ Rad Si ( $\pm 10\%$ ) from a Gamma Cell 220 rads/sec.                                                                             |

| 4    | The samples will be tested to the data sheet limits within 1 hour (±15 minutes) after irradiation. The Lot will be accepted only if all units, exclusive of non-radiation failures, meet the Table 2 parameter limits.     |

| 5    | The sample devices shall pass functional test(s) consisting of Logic 1's, Logic 0's and a checkerboard pattern.                                                                                                            |

PAGE 15

ISSUE 2

### 4.3 MECHANICAL REQUIREMENTS

#### 4.3.1 Dimension Check

The dimensions of the integrated circuits specified herein shall be checked. They shall conform to those shown in Figure 2.

#### 4.3.2 Weight

The maximum weight of the integrated circuits specified herein shall be 2.5 grammes for the dual-in-line package.

### 4.4 MATERIALS AND FINISHES

The materials and finishes shall be as specified herein. Where a definite material is not specified, a material which will enable the integrated circuits specified herein to meet the performance requirements of this specification shall be used. Acceptance or approval of any constituent material does not guarantee acceptance of the finished product.

### 4.4.1 <u>Case</u>

The case shall be hermetically sealed and have a metal body with hard glass seals or a ceramic body and the lids shall be welded, brazed or preform-soldered.

### 4.4.2 Lead Material and Finish

The material shall be either Type 'D' or Type 'G' with either Type '2' or Type '3' finish in accordance with the requirements of ESA/SCC Basic Specification No. 23500. (See Table 1(a) for Type Variants).

### 4.5 MARKING

#### 4.5.1 General

The marking of components delivered to this specification shall be in accordance with ESA/SCC Basic Specification No. 21700. Each component shall be marked in respect of:-

- (a) Lead Identification.

- (b) The SCC Component Number.

- (c) Traceability Information.

### 4.5.2 Lead Identification

An index shall be located at the top of the package in the position defined in Note 1 to Figure 2 or, alternatively, a tab will be used to identify Pin No. 1. The pin numbering shall be read with the index or tab on the left-hand side.

#### 4.5.3 The SCC Component Number

Each component shall bear the SCC Component Number which shall be constituted and marked as follows:

|                                         | <u>940801901B</u> |

|-----------------------------------------|-------------------|

| Detail Specification Number             |                   |

| Type Variant (see Table 1(a))           |                   |

| Testing Level (B or C, as applicable) - |                   |

PAGE 16

ISSUE 2

### 4.5.4 Traceability Information

Each component shall be marked in respect of traceability information in accordance with ESA/SCC Basic Specification No. 21700.

### 4.6 ELECTRICAL MEASUREMENTS

#### 4.6.1 Electrical Measurements at Room Temperature

The parameters to be measured in respect of electrical characteristics are scheduled in Table 2. Unless otherwise specified, the measurements shall be performed at  $T_{amb}$  = +25 ±5 °C.

### 4.6.2 Electrical Measurements at High and Low Temperatures

The parameters to be measured at high and low temperatures are scheduled in Tables 3. The measurements shall be performed at  $T_{amb} = +125(+0-5)$  °C and -55(+5-0) °C respectively.

### 4.6.3 <u>Circuits for Electrical Measurements</u>

Circuits and functional test sequence for use in performing the electrical measurements listed in Tables 2 and 3 of this specification are shown in Figure 4.

### 4.7 BURN-IN TESTS

### 4.7.1 Parameter Drift Values

The parameter drift values applicable to burn-in are specified in Table 4 of this specification. Unless otherwise stated, measurements shall be performed at  $T_{amb}$  = +25 ±5 °C. The parameter drift values ( $\Delta$ ) applicable to the parameters scheduled, shall not be exceeded. In addition to these drift value requirements, the appropriate limit value specified for a given parameter in Table 2 shall not be exceeded.

### 4.7.2 Conditions for H.T.R.B. and Burn-in

The requirements for H.T.R.B. and burn-in are specified in Section 7 of ESA/SCC Generic Specification No. 9000. The conditions for H.T.R.B. and burn-in shall be as specified in Tables 5(a) and 5(b) of this specification.

### 4.7.3 Electrical Circuits for H.T.R.B. and Burn-in

Circuits for use in performing the H.T.R.B. and burn-in tests are shown in Figures 5(a) and 5(b) of this specification.

PAGE 17

ISSUE 2

### TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS

|                  | Ob                                                                | O wala al        | MIL-STD-<br>883 | Test | Test Conditions                                                                                                                                                                                                    | Lim   | nits | Unit |

|------------------|-------------------------------------------------------------------|------------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|

| No.              | Characteristics                                                   | Symbol           | Test<br>Method  | Fig. | (Pins Under Test)<br>(Notes 1, 2 and 4)                                                                                                                                                                            | Min   | Max  | Unit |

| 1                | Functional Test                                                   | ı                |                 | 4(a) | Verify Truth Table.                                                                                                                                                                                                | -     | 1    | -    |

| 2<br>to<br>22    | Input Current High<br>Level 1, All Inputs                         | l <sub>IH1</sub> | 3010            | 4(b) | $V_{IN}$ (under test) = 15V<br>$\underline{V_{IN}}$ (other Inputs) = 0V<br>$\overline{EN}$ = GND<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = 4.0V<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26-28)  | -1.0  | 1.0  | μА   |

| 23<br>to<br>44   | Input Current High<br>Level 2, All Inputs                         | l <sub>IH2</sub> | 3010            | 4(b) | $V_{IN}$ (under test) = 4.0V<br>$\underline{V_{IN}}$ (other Inputs) = GND<br>$\overline{EN}$ = 15V<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = GND<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26-28) | -1.0  | 1.0  | µА   |

| 45<br>to<br>66   | Input Current Low<br>Level 1, All Inputs                          | l <sub>IL1</sub> | 3009            | 4(c) | $V_{IN}$ (under test) = 0V<br>$V_{IN}$ (other Inputs) = 15V<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = 4.0V<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26)                                          | - 1.0 | 1.0  | μА   |

| 67<br>to<br>89   | Input Current Low<br>Level 2, All Inputs                          | l <sub>IL2</sub> | 3009            | 4(c) | $V_{IN}$ (under test) = 4.0V<br>$V_{IN}$ (other Inputs) = GND<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = GND<br>(Pins 4-5-6-7-8-9-10-11-14-15-16-17-18-19-20-21-22-23-24-25-26-28)                                         | -1.0  | 1.0  | μA   |

| 90<br>to<br>106  | Leakage Current into<br>the Source Terminal<br>of an "Off" Switch | ls+(OFF)         | -               | 4(d) | V <sub>IN</sub> = -10V, OUT = 10V<br>All unused inputs = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                                                                              | - 100 | 100  | nA   |

| 107<br>to<br>123 |                                                                   | IS-(OFF)         |                 |      | V <sub>IN</sub> = 10V, OUT = 10V<br>All unused inputs = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                                                                               | - 100 | 100  | nA   |

| 124<br>to<br>140 | the Source Terminal                                               | ls±(OFF)         | -               | 4(e) | +V <sub>S</sub> , -V <sub>S</sub> , V <sub>REF</sub> , A <sub>0</sub> , A <sub>1</sub> , A <sub>2</sub> ,<br>A <sub>3</sub> , EN = Open<br>Inputs = +10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)   | - 100 | 100  | nA   |

PAGE 18

ISSUE 2

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS (CONT'D)

|                  | Obs. and besides                                                                         | 0                      | MIL-STD-<br>883 | Test         | Test Conditions                                                                                                                        | Lim              | nits | l lait |

|------------------|------------------------------------------------------------------------------------------|------------------------|-----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------|------|--------|

| No.              | Characteristics                                                                          | Symbol                 | Test<br>Method  | Fig.         | (Pins Under Test)<br>(Notes 1, 2 and 4)                                                                                                | Min              | Max  | Unit   |

| 141<br>to<br>156 | Leakage Current into<br>the Drain Terminal of<br>an "Off" Switch                         | I <sub>D + (OFF)</sub> | -               | 4(f)         | Connect All Inputs to -10V<br>Output = 10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                     | -1.0             | 1.0  | μA     |

| 157<br>to<br>172 |                                                                                          | I <sub>D – (OFF)</sub> |                 |              | Connect All Inputs to +10V<br>Output = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                    | -1.0             | 1.0  | μA     |

| 173<br>to<br>188 | Leakage Current from<br>an "Off" Driver into<br>the Switch (Drain)                       | I <sub>D+(ON)</sub>    | -               | <b>4</b> (g) | Connect All Unused Inputs to $+10V$ , $V_{IN} = -10V$<br>Output = $-10V$<br>(Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)           | 1.0              | 1.0  | μA     |

| 189<br>to<br>204 | Leakage Current from<br>an "Off" Driver into<br>the Switch (Drain)                       | I <sub>D - (ON)</sub>  | -               | 4(g)         | Connect All Unused Inputs to<br>- 10V, V <sub>IN</sub> = -10V<br>Output = +10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26) | <del>-</del> 1.0 | 1.0  | μА     |

| 205<br>to<br>217 | Overvoltage. Protection, Leakage Current into the Drain Terminal of an "Off" Switch      | I <sub>D + (OVP)</sub> | 3008            | 4(h)         | Measure Inputs Sequentially<br>VIN = 35V, OUT = 0V<br>EN = 4.0V<br>(Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)                    | 1                | 2.0  | μA     |

| 218<br>to<br>233 |                                                                                          | I <sub>D</sub> – (OVP) |                 |              | Measure Inputs Sequentially $V_{IN} = -25V$ , OUT = 0V $\overline{EN} = 4.0V$ (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)         | -1.0             | 1.0  | μΑ     |

| 234<br>to<br>249 | Overvoltage<br>Protection, Leakage<br>Current into the<br>Source Terminal of an<br>"Off" | IS+(OVP)               | 3008            | 4(i)         | Measure Inputs Sequentially $V_{OUT}$ = +35V, $V_{IN}$ = 0V $\overline{EN}$ = 4.0V (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)    | -2.0             | 2.0  | μА     |

| 250<br>to<br>265 |                                                                                          | I <sub>S</sub> – (OVP) |                 |              | Measure Inputs Sequentially $V_{OUT} = -20V$ , $V_{IN} = 0V$ $EN = 4.0V$ (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)              | -1.0             | 2.0  | μΑ     |

PAGE 19

ISSUE 2

# TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - d.c. PARAMETERS (CONT'D)

| No.              | Characteristics                    | Symbol                | MIL-STD-<br>883 | Test | Test Conditions<br>(Pins Under Test)                                                                                                               | Lin | nits  | Unit |

|------------------|------------------------------------|-----------------------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|

| NO.              | Characteristics                    | Syllibol              | Test<br>Method  | Fig. | (Notes 1, 2 and 4)                                                                                                                                 | Min | Max   | Unit |

| 266              | Positive Supply<br>Current         | I <sub>+(PSC)</sub>   | 3005            | 4(j) | $\frac{V_{IN}}{EN} = 0V$ $EN = 0.8V$ (Pin 1)                                                                                                       | -   | 500   | μA   |

| 267              | Negative Supply<br>Current         | I <sub>- (PSC)</sub>  | 3005            | 4(j) | V <sub>IN</sub> = 0V<br>EN = 0.8V<br>(Pin 27)                                                                                                      | -   | -500  | μA   |

| 268              | Positive Supply<br>Standby Current | + (STDBY)             | 3005            | 4(j) | <u>V<sub>IN</sub></u> = 0V<br>EN = 4.0V<br>(Pin 1)                                                                                                 | -   | 100   | μA   |

| 269              | Negative Supply<br>Standby Current | I <sub>-(STDBY)</sub> | 3005            | 4(j) | V <sub>IN</sub> = 0V<br>EN = 4.0V<br>(Pin 27)                                                                                                      | -   | - 100 | μА   |

| 270<br>to<br>285 | Switch "On"<br>Resistance          | R <sub>1ON+</sub>     | -               | 4(k) | $V_{IN}$ = + 15V<br>EN = 0.8V<br>$I_{OUT}$ = + 1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to 28)<br>(Pins 19-20-21-22-23-24-25-26 to 29)                     | _   | 1.0   | kΩ   |

| 286<br>to<br>301 |                                    | R <sub>20N+</sub>     |                 |      | V <sub>IN</sub> = +5.0V<br>EN = 0.8V<br>I <sub>OUT</sub> = +1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to<br>28)<br>(Pins 19-20-21-22-23-24-25-<br>26 to 28) | -   | 3.0   | kΩ   |

| 302<br>to<br>317 | Switch "On"<br>Resistance          | R <sub>10N</sub> -    | -               | 4(k) | $V_{IN}$ = 5.0V<br>$\overline{EN}$ = 0.8V<br>$I_{OUT}$ = + 1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to 28)<br>(Pins 19-20-21-22-23-24-25-26 to 28)         | -   | 5.0   | kΩ   |

PAGE 20

ISSUE 2

### TABLE 2 - ELECTRICAL MEASUREMENTS AT ROOM TEMPERATURE - a.c. PARAMETERS

| No.              | Characteristics             | Symbol                                     | MIL-STD-<br>883 | Test | Test Conditions<br>(Pins Under Test)                                                                                     | Lin | nits | Unit  |

|------------------|-----------------------------|--------------------------------------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------|-----|------|-------|

| NO.              | Citalacteristics            | Symbol                                     | Test<br>Method  | Fig. | (Notes 1, 2 and 4)                                                                                                       | Min | Max  | Offic |

| 318<br>to        | Propagation Delay<br>Times: | t <sub>PLH1</sub>                          | -               | -    | $R_L$ = 10mΩ, $C_L$ = 14pF<br>EN = 15V                                                                                   | 50  | 1000 | ns    |

| 319              | Address Inputs              | t <sub>PHL1</sub>                          |                 |      | See Figure 4(a)                                                                                                          | 50  | 1000 |       |

| 320<br>to<br>322 | Enable to I/O               | t <sub>PLH2</sub><br>(t <sub>ON</sub> EN)  | -               | -    | $R_L = 1.0k\Omega$ , $C_L = 12.5pF$<br>EN = Input<br>$V_{AL} = GND$                                                      | 50  | 1000 | ns    |

| 322              |                             | t <sub>PHL2</sub><br>(t <sub>OFF</sub> EN) |                 |      | See Figure 4(a)                                                                                                          | 50  | 1000 |       |

| 323<br>to<br>326 | Address Capacitance         | C <sub>A</sub>                             | -               | -    | V <sub>IN</sub> = V <sub>CC</sub> or GND<br>f = 1.0MHz<br>Note 3<br>(Pins 14-15-16-17)                                   | ı   | 5.0  | pF    |

| 327              | Output Capacitance          | C <sub>OS</sub>                            | •               | 1    | V <sub>IN</sub> = V <sub>EE</sub> or GND<br>f = 1.0MHz<br>Note 3<br>(Pin 28)                                             | •   | 50   | pF    |

| 328<br>to<br>343 | Input Capacitance           | C <sub>IS</sub>                            | -               | -    | V <sub>IN</sub> = V <sub>CC</sub> or GND<br>f = 1.0MHz<br>Note 3<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26) | -   | 5.0  | pF    |

### **NOTES**

- 1. Current flowing in either direction between any associated input and output terminals of switch shall be 30mA

- 2.  $V_{IN}$  is the voltage applied to the channel inputs.

- 3. Guaranteed but not tested.

- 4. Unless otherwise specified:  $+V_S = 15V$ ,  $-V_S = -15V$ ,  $V_{REF} = +15V$ ,  $V_{N1} = 4.0V$  and  $V_{AL} = 0.8V$ .

PAGE 21

ISSUE 2

# TABLE 3(a) - ELECTRICAL MEASUREMENTS AT HIGH TEMPERATURE, + 125(+0-5) °C d.c. PARAMETERS

| No               | Charactariatica                                                   | Symbol           | MIL-STD-<br>883 | Test | Test Conditions                                                                                                                                                                            | Lim   | nits | Lloit |

|------------------|-------------------------------------------------------------------|------------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|

| No.              | Characteristics                                                   | Symbol           | Test<br>Method  | Fig. | (Pins Under Test)<br>(Notes 1, 2 and 4)                                                                                                                                                    | Min   | Max  | Unit  |

| 1                | Functional Test                                                   | -                |                 | 4(a) | Verify Truth Table.                                                                                                                                                                        | -     | •    |       |

| 2<br>to<br>22    | Input Current High<br>Level 1, All Inputs                         | l <sub>IH1</sub> | 3010            | 4(b) | $V_{IN}$ (under test) = 15V<br>$V_{IN}$ (other Inputs) = 0V<br>EN = GND<br>$A_0$ , $A_1$ , $A_2$ , $A_3 = 4.0Vdc$<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26-28) | - 1.0 | 1.0  | μA    |

| 23<br>to<br>44   | Input Current High<br>Level 2, All Inputs                         | l <sub>IH2</sub> | 3010            | 4(b) | $V_{IN}$ (under test) = 4.0V<br>$V_{IN}$ (other Inputs) = GND<br>EN = 15V<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = GND<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26-28)  | -1.0  | 1.0  | μA    |

| 45<br>to<br>66   | Input Current Low<br>Level 1, All Inputs                          | կլ 1             | 3009            | 4(c) | $V_{IN}$ (under test) = 0V<br>$V_{IN}$ (other Inputs) = 15V<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = 4.0V<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26)                  | -1.0  | 1.0  | μА    |

| 67<br>to<br>89   | Input Current Low<br>Level 2, All Inputs                          | l <sub>IL2</sub> | 3009            | 4(c) | $V_{IN}$ (under test) = 4.0V<br>$V_{IN}$ (other Inputs) = GND<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = GND<br>(Pins 4-5-6-7-8-9-10-11-14-<br>15-16-17-18-19-20-21-22-23-<br>24-25-26-28)         | -1.0  | 1.0  | μА    |

| 90<br>to<br>106  | Leakage Current into<br>the Source Terminal<br>of an "Off" Switch | ls+(OFF)         | -               | 4(d) | V <sub>IN</sub> = -10V, OUT = 10V<br>All unused inputs = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                                                      | - 100 | 100  | nA    |

| 107<br>to<br>123 |                                                                   | ls – (OFF)       |                 |      | V <sub>IN</sub> = 10V, OUT = 10V<br>All unused inputs = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                                                       | 100   | 100  | nA    |

| 124<br>to<br>140 | Leakage Current into the Source Terminal with Power "Off"         | ls±(OFF)         | -               | 4(e) | $+V_{S.}$ $-V_S$ , $V_{REF}$ , $A_0$ , $A_1$ , $A_2$ , $A_3$ , $EN = Open$ Inputs = $+10V$ (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)                                                | -100  | 100  | nA    |

PAGE 22

ISSUE 2

# TABLE 3(a) - ELECTRICAL MEASUREMENTS AT HIGH TEMPERATURE, + 125(+0-5) °C d.c. PARAMETERS (CONT'D)

|                  |                                                                                                | 0                      | MIL-STD-<br>883 | Test | Test Conditions                                                                                                                       | Lim  | its | Unit |

|------------------|------------------------------------------------------------------------------------------------|------------------------|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

| No.              | Characteristics                                                                                | Symbol                 | Test<br>Method  | Fig. | (Pins Under Test)<br>(Notes 1, 2 and 4)                                                                                               | Min  | Max | Unit |

| 141<br>to<br>156 | Leakage Current into<br>the Drain Terminal of<br>an "Off" Switch                               | I <sub>D+(OFF)</sub>   | -               | 4(f) | Connect All Inputs to -10V<br>Output = 10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                    | -1.0 | 1.0 | μА   |

| 157<br>to<br>172 |                                                                                                | l <sub>D</sub> – (OFF) |                 |      | Connect All Inputs to +10V<br>Output = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                   | -1.0 | 1.0 | μА   |

| 173<br>to<br>188 | Leakage Current from<br>an "Off" Driver into<br>the Switch (Drain)                             | l <sub>D</sub> + (ON)  | -               | 4(g) | Connect All Unused Inputs to $+ 10V$ , $V_{IN} = - 10V$<br>Output = $- 10V$<br>(Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)       | -1.0 | 1.0 | μА   |

| 189<br>to<br>204 | Leakage Current from<br>an "Off" Driver into<br>the Switch (Drain)                             | I <sub>D</sub> (ON)    | -               | 4(g) | Connect All Unused Inputs to - 10V, V <sub>IN</sub> = - 10V<br>Output = + 10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26) | -1.0 | 1.0 | μА   |

| 205<br>to<br>217 | Overvoltage<br>Protection, Leakage<br>Current into the Drain<br>Terminal of an "Off"<br>Switch | I <sub>D+(OVP)</sub>   | 3008            | 4(h) | Measure Inputs Sequentially $\underline{V_{IN}}$ = 35V, OUT = 0V EN = 4.0V (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)           | -    | 2.0 | µА   |

| 218<br>to<br>233 |                                                                                                | I <sub>D – (OVP)</sub> |                 |      | Measure Inputs Sequentially $V_{IN} = -25V$ , OUT = 0V $\overline{EN} = 4.0V$ (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)        | -1.0 | 1.0 | μА   |

| 234<br>to<br>249 | Overvoltage<br>Protection, Leakage<br>Current into the<br>Source Terminal of an<br>"Off"       | I <sub>S+(OVP)</sub>   | 3008            | 4(i) | Measure Inputs Sequentially $V_{OUT}$ = +35V, $V_{IN}$ = 0V $\overline{EN}$ = 4.0V (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)   | -2.0 | 2.0 | μА   |

| 250<br>to<br>265 |                                                                                                | I <sub>S</sub> – (OVP) |                 |      | Measure Inputs Sequentially $V_{OUT} = -20V$ , $V_{IN} = 0V$ $EN = 4.0V$ (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)             | -1.0 | 2.0 | μА   |

PAGE 23

ISSUE 2

# TABLE 3(a) - ELECTRICAL MEASUREMENTS AT HIGH TEMPERATURE, + 125(+0-5) °C d.c. PARAMETERS (CONT'D)

| N.               | Observatoristics                   | Cumbal                 | MIL-STD-<br>883 | Test | Test Conditions                                                                                                                                    | Lim | nits  | Unit |

|------------------|------------------------------------|------------------------|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|

| No.              | Characteristics                    | Symbol                 | Test<br>Method  | Fig. | (Pins Under Test)<br>(Notes 1, 2 and 4)                                                                                                            | Min | Max   | Unit |

| 266              | Positive Supply<br>Current         | I + (PSC)              | 3005            | 4(j) | <u>V<sub>IN</sub></u> = 0V<br>EN = 0.8V<br>(Pin 1)                                                                                                 | -   | 500   | μA   |

| 267              | Negative Supply<br>Current         | I - (PSC)              | 3005            | 4(j) | V <sub>IN</sub> = 0V<br>EN = 0.8V<br>(Pin 27)                                                                                                      | -   | - 500 | μА   |

| 268              | Positive Supply<br>Standby Current | I <sub>+ (STDBY)</sub> | 3005            | 4(j) | V <sub>IN</sub> = 0V<br>EN = 4.0V<br>(Pin 1)                                                                                                       | -   | 100   | μА   |

| 269              | Negative Supply<br>Standby Current | I <sub>- (STDBY)</sub> | 3005            | 4(j) | V <sub>IN</sub> = 0V<br>EN = 4.0V<br>(Pin 27)                                                                                                      | -   | - 100 | μА   |

| 270<br>to<br>285 | Switch "On"<br>Resistance          | R <sub>10N+</sub>      | -               | 4(k) | $V_{IN}$ = + 15V<br>$\overline{EN}$ = 0.8V<br>$I_{OUT}$ = + 1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to 28)<br>(Pins 19-20-21-22-23-24-25-26 to 29)        | -   | 1.0   | kΩ   |

| 286<br>to<br>301 |                                    | R <sub>2ON+</sub>      |                 |      | $V_{IN}$ = +5.0V<br>EN = 0.8V<br>$I_{OUT}$ = +1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to 28)<br>(Pins 19-20-21-22-23-24-25-26 to 28)                      | -   | 3.0   | kΩ   |

| 302<br>to<br>317 | Switch "On"<br>Resistance          | R <sub>10N</sub> –     | -               | 4(k) | V <sub>IN</sub> = 5.0V<br>EN = 0.8V<br>I <sub>OUT</sub> = + 1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to<br>28)<br>(Pins 19-20-21-22-23-24-25-<br>26 to 28) | -   | 5.0   | kΩ   |

PAGE 24

ISSUE 2

# TABLE 3(a) - ELECTRICAL MEASUREMENTS AT HIGH TEMPERATURE, +125(+0-5) °C a.c. PARAMETERS

| No.       | Characteristics                | Symbol                                     | Test Conditions<br>(Pins Under Test)                                                  | Lim | nits | Unit |

|-----------|--------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------|-----|------|------|

|           |                                |                                            | (Notes 1, 2 and 4)                                                                    | Min | Max  |      |

| 318<br>to | Propagation Delay<br>Times:    | t <sub>PLH1</sub>                          | $R_L = 10$ mΩ, $C_L = 14$ pF<br>EN = 15V                                              | 75  | 1000 | ns   |

| 319       | Address Inputs to I/O Channels | <sup>†</sup> PHL1                          | See Figure 4(a)                                                                       | 75  | 1000 | ļ    |

| 320<br>to | Enable to I/O                  | t <sub>PLH2</sub><br>(t <sub>ON</sub> EN)  | $R_L = 1.0 \text{k}\Omega$ , $C_L = 12.5 \text{pF}$<br>$\overline{EN} = \text{Input}$ | 75  | 1000 | ns   |

| 322       |                                | t <sub>PHL2</sub><br>(t <sub>OFF</sub> EN) | V <sub>AL</sub> = GND, V <sub>AH</sub> = 15V<br>See Figure 4(a)                       | 75  | 1000 |      |

PAGE 25

ISSUE 2

# TABLE 3(b) - ELECTRICAL MEASUREMENTS AT LOW TEMPERATURE, -55(+5-0) °C d.c. PARAMETERS

|                  |                                                                   | O male al        | MIL-STD-<br>883 | Test | Test Conditions                                                                                                                                                                                                   | Lim   | nits | l la la |

|------------------|-------------------------------------------------------------------|------------------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------|

| No.              | Characteristics                                                   | Symbol           | Test<br>Method  | Fig. | (Pins Under Test)<br>(Notes 1, 2 and 4)                                                                                                                                                                           | Min   | Max  | Unit    |

| 1                | Functional Test                                                   | •                |                 | 4(a) | Verify Truth Table.                                                                                                                                                                                               | -     | -    | -       |

| 2<br>to<br>22    | Input Current High<br>Level 1, All Inputs                         | l <sub>IH1</sub> | 3010            | 4(b) | $V_{IN}$ (under test) = 15V<br>$\underline{V}_{IN}$ (other Inputs) = 0V<br>$\overline{EN}$ = GND<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = 4.0V<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26-28) | - 1.0 | 1.0  | μA      |

| 23<br>to<br>44   | Input Current High<br>Level 2, All Inputs                         | l <sub>IH2</sub> | 3010            | 4(b) | $V_{IN}$ (under test) = 4.0V<br>$V_{IN}$ (other Inputs) = GND<br>EN = 15V<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = GND<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26-28)                         | - 1.0 | 1.0  | μА      |

| 45<br>to<br>66   | Input Current Low<br>Level 1, All Inputs                          | l <sub>IL1</sub> | 3009            | 4(c) | $V_{IN}$ (under test) = 0V<br>$V_{IN}$ (other Inputs) = 15V<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = 4.0V<br>(Pins 4-5-6-7-8-9-10-11-12-14-15-16-17-18-19-20-21-22-23-24-25-26)                                         | -1.0  | 1.0  | μA      |

| 67<br>to<br>89   | Input Current Low<br>Level 2, All Inputs                          | l <sub>IL2</sub> | 3009            | 4(c) | $V_{IN}$ (under test) = 4.0V<br>$V_{IN}$ (other Inputs) = GND<br>$A_0$ , $A_1$ , $A_2$ , $A_3$ = GND<br>(Pins 4-5-6-7-8-9-10-11-14-<br>15-16-17-18-19-20-21-22-23-<br>24-25-26-28)                                | - 1.0 | 1.0  | μA      |

| 90<br>to<br>106  | Leakage Current into<br>the Source Terminal<br>of an "Off" Switch | Is+(OFF)         | -               | 4(d) | V <sub>IN</sub> = -10V, OUT = 10V<br>All unused inputs = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                                                                             | - 100 | 100  | nA      |

| 107<br>to<br>123 |                                                                   | ls-(off)         |                 |      | V <sub>IN</sub> = 10V, OUT = 10V<br>All unused inputs = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                                                                              | - 100 | 100  | nA      |

| 124<br>to<br>140 | Leakage Current into the Source Terminal with Power "Off"         | ls±(OFF)         | -               | 4(e) | $+V_{S}$ , $-V_{S}$ , $V_{REF}$ , $A_{0}$ , $A_{1}$ , $A_{2}$ , $A_{3}$ , $EN = Open$<br>Inputs = +10V<br>(Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)                                                        | - 100 | 100  | nA      |

PAGE 26

ISSUE 2

# TABLE 3(b) - ELECTRICAL MEASUREMENTS AT LOW TEMPERATURE, -55(+5-0) °C d.c. PARAMETERS (CONT'D)

| No               | Characteristics                                                                                | Symbol                 | Test<br>Method  | Test | Test Conditions                                                                                                                      | Lim  | nits | 1 1  |

|------------------|------------------------------------------------------------------------------------------------|------------------------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| No.              | Characteristics                                                                                | Symbol                 | MIL-STD-<br>883 | Fig. | (Pins Under Test)<br>(Notes 1, 2 and 4)                                                                                              | Min  | Max  | Unit |

| 141<br>to<br>156 | Leakage Current into<br>the Drain Terminal of<br>an "Off" Switch                               | I <sub>D+(OFF)</sub>   | •               | 4(f) | Connect All Inputs to -10V<br>Output = 10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                   | -1.0 | 1.0  | μА   |

| 157<br>to<br>172 |                                                                                                | I <sub>D</sub> – (OFF) |                 |      | Connect All Inputs to +10V<br>Output = -10V<br>(Pins 4-5-6-7-8-9-10-11-19-<br>20-21-22-23-24-25-26)                                  | -1.0 | 1.0  | μА   |

| 173<br>to<br>188 | Leakage Current from<br>an "Off" Driver into<br>the Switch (Drain)                             | I <sub>D+(ON)</sub>    | -               | 4(g) | Connect All Unused Inputs to $+10V$ , $V_{IN} = -10V$<br>Output = $-10V$<br>(Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)         | -1.0 | 1.0  | μА   |

| 189<br>to<br>204 | Leakage Current from<br>an "Off" Driver into<br>the Switch (Drain)                             | I <sub>D</sub> – (ON)  | -               | 4(g) | Connect All Unused Inputs to $-10V$ , $V_{\text{IN}} = -10V$<br>Output = $+10V$<br>(Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)  | 1.0  | 1.0  | Αц   |

| 205<br>to<br>217 | Overvoltage<br>Protection, Leakage<br>Current into the Drain<br>Terminal of an "Off"<br>Switch | I <sub>D + (OVP)</sub> | 3008            | 4(h) | Measure Inputs Sequentially $V_{IN}$ = 35V, OUT = 0V $\overline{EN}$ = 4.0V (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)         | -    | 2.0  | µА   |

| 218<br>to<br>233 |                                                                                                | I <sub>D - (OVP)</sub> |                 |      | Measure Inputs Sequentially $V_{IN} = -25V$ , OUT = 0V $\overline{EN} = 4.0V$ (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)       | -1.0 | 1.0  | μA   |

| 234<br>to<br>249 | Overvoltage<br>Protection, Leakage<br>Current into the<br>Source Terminal of an<br>"Off"       | Is+(OVP)               | 3008            | 4(i) | Measure Inputs Sequentially $V_{OUT} = +35V$ , $V_{IN} = 0V$ $EN = 4.0V$ (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26)            | -2.0 | 2.0  | µА   |

| 250<br>to<br>265 |                                                                                                | I <sub>S - (OVP)</sub> |                 |      | Measure Inputs Sequentially $V_{OUT} = -20V$ , $V_{IN} = 0V$ $\overline{EN} = 4.0V$ (Pins 4-5-6-7-8-9-10-11-19-20-21-22-23-24-25-26) | -1.0 | 2.0  | μА   |

PAGE 27

ISSUE 2

# TABLE 3(b) - ELECTRICAL MEASUREMENTS AT LOW TEMPERATURE, -55(+5-0) °C d.c. PARAMETERS (CONT'D)

|                  | Observats delication               | O wash all         | Test<br>Method  | Test | Test Conditions                                                                                                                           | Lim | nits  | 11   |

|------------------|------------------------------------|--------------------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------|

| No.              | Characteristics                    | Symbol             | MIL-STD-<br>883 | Fig. | (Pins Under Test)<br>(Notes 1, 2 and 4)                                                                                                   | Min | Max   | Unit |

| 266              | Positive Supply<br>Current         | I + (PSC)          | 3005            | 4(j) | <u>V<sub>IN</sub></u> = 0V<br>EN = 0.8V<br>(Pin 1)                                                                                        | -   | 500   | μA   |

| 267              | Negative Supply<br>Current         | I - (PSC)          | 3005            | 4(j) | V <sub>IN</sub> = 0V<br>EN = 0.8V<br>(Pin 27)                                                                                             | 1   | - 500 | μA   |

| 268              | Positive Supply<br>Standby Current | I +(STDBY)         | 3005            | 4(j) | <u>V<sub>IN</sub></u> = 0V<br>EN = 4.0V<br>(Pin 1)                                                                                        | -   | 100   | μA   |

| 269              | Negative Supply<br>Standby Current | I - (STDBY)        | 3005            | 4(j) | V <sub>IN</sub> = 0V<br>EN = 4.0V<br>(Pin 27)                                                                                             | -   | - 100 | μA   |

| 270<br>to<br>285 | Switch "On"<br>Resistance          | R <sub>1ON+</sub>  | -               | 4(k) | $V_{IN}$ = +15V<br>EN = 0.8V<br>$I_{OUT}$ = +1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to 28)<br>(Pins 19-20-21-22-23-24-25-26 to 29)              | -   | 1.0   | kΩ   |

| 286<br>to<br>301 |                                    | R <sub>2ON+</sub>  |                 |      | $V_{IN}$ = +5.0V<br>EN = 0.8V<br>$I_{OUT}$ = +1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to 28)<br>(Pins 19-20-21-22-23-24-25-26 to 28)             | -   | 3.0   | kΩ   |

| 302<br>to<br>317 | Switch "On"<br>Resistance          | R <sub>10N</sub> – | -               | 4(k) | $V_{IN}$ = 5.0V<br>$\overline{EN}$ = 0.8V<br>$I_{OUT}$ = +1.0mA<br>(Pins 4-5-6-7-8-9-10-11 to 28)<br>(Pins 19-20-21-22-23-24-25-26 to 28) | -   | 5.0   | kΩ   |

PAGE 28

ISSUE 2

# TABLE 3(b) - ELECTRICAL MEASUREMENTS AT LOW TEMPERATURE, -55(+5-0) °C a.c. PARAMETERS

| No.       | No. Characteristics            |                                            | Test Conditions<br>(Pins Under Test)                            | Lim | nits | Unit |

|-----------|--------------------------------|--------------------------------------------|-----------------------------------------------------------------|-----|------|------|

|           |                                |                                            | (Notes 1, 2 and 4)                                              |     | Max  |      |

| 318<br>to | Propagation Delay Times:       | t <sub>PLH1</sub>                          | $R_L = 10 \text{m}\Omega$ , $C_L = 14 \text{pF}$<br>EN = 15V    | 75  | 1000 | ns   |

| 319       | Address Inputs to I/O Channels | t <sub>PHL1</sub>                          | See Figure 4(a)                                                 | 75  | 1000 |      |

| 320<br>to | Enable to I/O                  | t <sub>PLH2</sub><br>(t <sub>ON</sub> EN)  |                                                                 | 75  | 1000 | ns   |

| 322       |                                | t <sub>PHL2</sub><br>(t <sub>OFF</sub> EN) | V <sub>AL</sub> = GND, V <sub>AH</sub> = 15V<br>See Figure 4(a) | 75  | 1000 |      |

PAGE 29

ISSUE 2

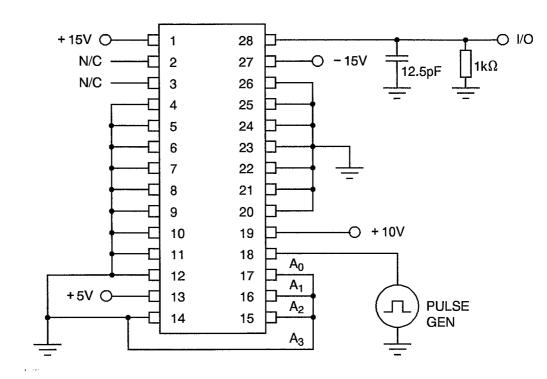

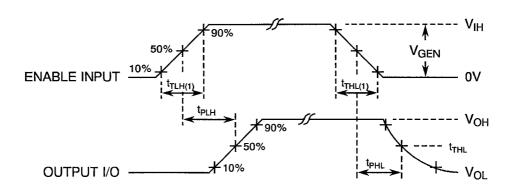

### FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS

### FIGURE 4(a) - SWITCHING TIMES TEST CIRCUIT AND WAVEFORMS

### ADDRESS INPUTS TO I/O

### **DYNAMIC TEST WAVEFORMS**

### **NOTES**

1. Input pulse requirements:  $V_{GEN} = 4.0V$ ,  $t_{THL(1)} = t_{TLH(1)} \le 20$ ns.

PAGE 30

ISSUE 2

### FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS (CONT'D)

### FIGURE 4(a) - SWITCHING TIMES TEST CIRCUIT AND WAVEFORMS (CONTINUED)

### **ENABLE TO I/O**

### **DYNAMIC TEST WAVEFORMS**

### **NOTES**

1. Input pulse requirements:  $V_{GEN} = 4.0V$ ,  $t_{THL(1)} = t_{TLH(1)} \le 20$ ns.

PAGE 31

ISSUE 2

### FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS (CONTINUED)

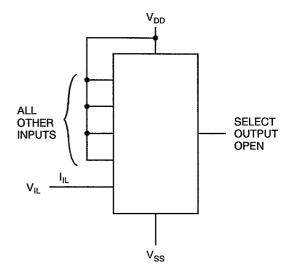

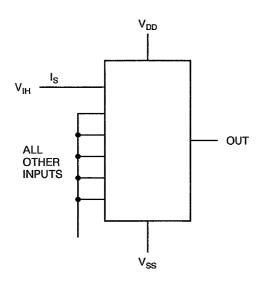

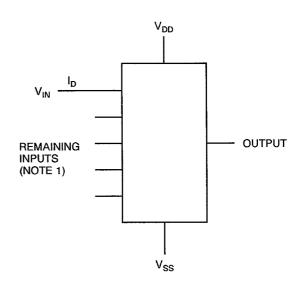

### FIGURE 4(b) - INPUT CURRENT HIGH LEVEL

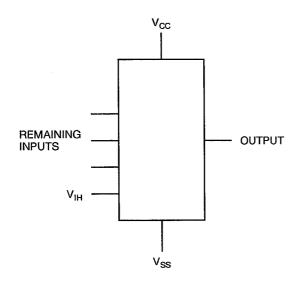

# FIGURE 4(c) - INPUT CURRENT LOW LEVEL

### **NOTES**

1. Each input to be tested separately.

### **NOTES**

1. Each input to be tested separately.

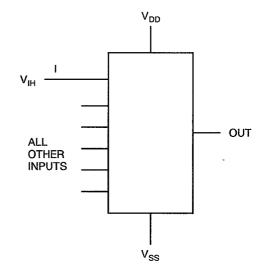

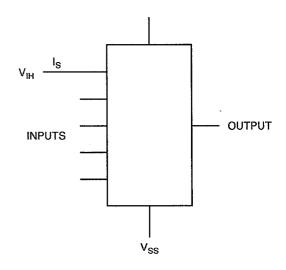

# FIGURE 4(d) - LEAKAGE CURRENT INTO THE SOURCE TERMINAL OF AN "OFF" SWITCH

# FIGURE 4(e) - LEAKAGE CURRENT INTO THE SOURCE TERMINAL WITH POWER "OFF"

### **NOTES**

1. All unused inputs to -10V.

### **NOTES**

1. All unused inputs open.

PAGE 32

ISSUE 2

### FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS (CONTINUED)

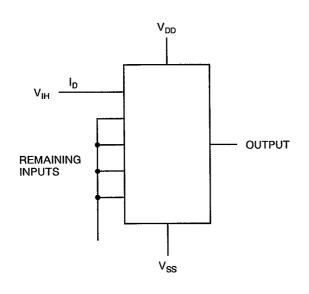

# FIGURE 4(f) - LEAKAGE CURRENT INTO THE DRAIN TERMINAL OF AN "OFF" SWITCH

FIGURE 4(g) - LEAKAGE CURRENT FROM AN "OFF" DRIVER INTO THE SWITCH (DRAIN)

#### **NOTES**

1. Each input to be tested separately.

#### **NOTES**

1. Connect all unused inputs to -10V.

### FIGURE 4(h) - OVERVOLTAGE PROTECTION, LEAKAGE CURRENT INTO THE DRAIN TERMINAL OF AN "OFF" SWITCH

### FIGURE 4(i) - OVERVOLTAGE PROTECTION, LEAKAGE CURRENT INTO THE SOURCE TERMINAL OF AN "OFF" SWITCH

### **NOTES**

1. Measure inputs sequentially.

PAGE 33

ISSUE 2

# FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS (CONTINUED)

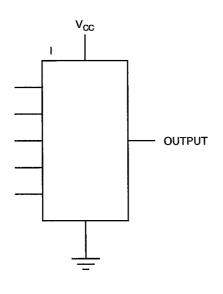

### FIGURE 4(j) - SUPPLY CURRENT

### FIGURE 4(k) - SWITCH "ON" RESISTANCE

$$\frac{\text{NOTES}}{1. \quad R_{ON} = \quad V_2}$$

$$\frac{1 \text{mA}}{1}$$

PAGE 34

ISSUE 2

### **TABLE 4 - PARAMETER DRIFT VALUES**

| No.              | CHARACTERISTICS                              | SYMBOL            | SPEC. AND/OR<br>TEST METHOD | TEST<br>CONDITIONS | CHANGE<br>LIMITS<br>(Δ) | UNIT     |

|------------------|----------------------------------------------|-------------------|-----------------------------|--------------------|-------------------------|----------|

| 2<br>to<br>22    | Input Current<br>High Level 1,<br>All Inputs | l <sub>IH1</sub>  | As per Table 2              | As per Table 2     | ± 100<br>or (1)<br>±20  | nA<br>%  |

| 23<br>to<br>44   | Input Current<br>High Level 2,<br>All Inputs | l <sub>IH2</sub>  | As per Table 2              | As per Table 2     | ± 100<br>or (1)<br>±20  | nA<br>%  |

| 45<br>to<br>66   | Input Current<br>Low Level 1,<br>All Inputs  | l <sub>IL1</sub>  | As per Table 2              | As per Table 2     | ± 100<br>or (1)<br>± 15 | nA<br>%  |

| 67<br>to<br>89   | Input Current<br>Low Level 2,<br>All Inputs  | l <sub>IL2</sub>  | As per Table 2              | As per Table 2     | ± 100<br>or (1)<br>± 15 | nA<br>%  |

| 266              | Positive Supply Current                      | 1 + (PSC)         | As per Table 2              | As per Table 2     | Note 2                  | <u>.</u> |

| 267              | Negative Supply Current                      | I - (PSC)         | As per Table 2              | As per Table 2     | Note 2                  | -        |

| 270<br>to<br>285 | Switch "On" Resistance 1                     | R <sub>1ON+</sub> | As per Table 2              | As per Table 2     | ± 10                    | %        |

| 286<br>to<br>301 | Switch "On" Resistance 2                     | R <sub>2ON+</sub> | As per Table 2              | As per Table 2     | ± 10                    | %        |

### **NOTES**

- Whichever is greater, referred to the initial value.

The absolute value of Table 2, only, shall be applied.

PAGE 35

ISSUE 2

### TABLE 5(a) - CONDITIONS FOR HIGH TEMPERATURE REVERSE BIAS BURN-IN

| No. | CHARACTERISTICS         | SYMBOL           | CONDITION  | UNIT |

|-----|-------------------------|------------------|------------|------|

| 1   | Ambient Temperature     | T <sub>amb</sub> | + 135 min. | °C   |

| 2   | Input Signals           |                  | None       |      |

| 3   | Positive Supply Voltage | +V <sub>S</sub>  | + 15 ± 10% | V    |

| 4   | Negative Supply Voltage | -V <sub>S</sub>  | - 15 ± 10% | V    |

| 5   | Reference Voltage       | $V_{R}$          | +5±10%     | ٧    |

| 6   | Duration                | t                | ≥48        | Hrs  |

### **NOTES**

### TABLE 5(b) - CONDITIONS FOR BURN-IN, DYNAMIC AND OPERATING LIFE TESTS

| No. | CHARACTERISTICS                                                | SYMBOL                                 | CONDITION                 | UNIT     |

|-----|----------------------------------------------------------------|----------------------------------------|---------------------------|----------|

| 1   | Ambient Temperature                                            | T <sub>amb</sub>                       | + 125 min.                | °C       |

| 2   | Outputs                                                        | V <sub>OUT</sub>                       | V <sub>DD/2</sub>         | V        |

| 3   | Input                                                          | V <sub>IN</sub>                        | $V_{\sf GEN}$             | Vac      |

| 4   | Input                                                          | V <sub>IN</sub>                        | V <sub>GEN2</sub>         | Vac      |

| 5   | Pulse Voltage                                                  | V <sub>GEN1</sub><br>V <sub>GEN2</sub> | 0V to +15 peak<br>minimum | Vac      |

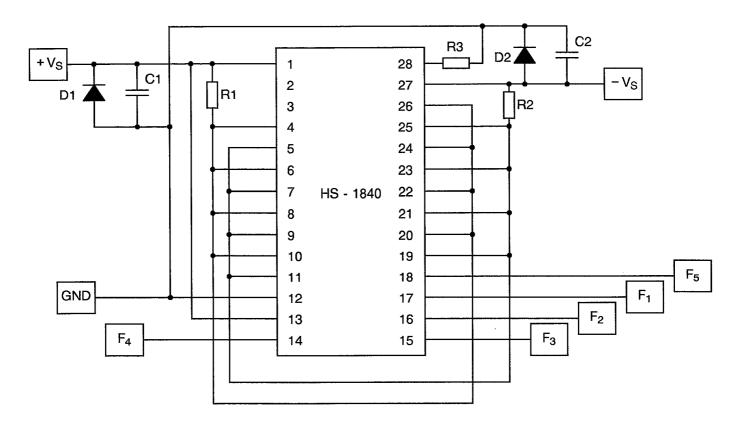

| 6   | Pulse Frequency - (Pin 17)<br>Square Wave (V <sub>GEN1</sub> ) | F <sub>1</sub>                         | 100                       | kHz      |

| 7   | Pulse Frequency - (Pin 16)<br>Square Wave (V <sub>GEN2</sub> ) | F <sub>2</sub>                         | 50                        | kHz      |

| 8   | Pulse Frequency - (Pin 15)<br>Square Wave (V <sub>GEN3</sub> ) | F <sub>3</sub>                         | 25                        | kHz<br>· |

| 9   | Pulse Frequency - (Pin 14)<br>Square Wave (V <sub>GEN4</sub> ) | F <sub>4</sub>                         | 12.5                      | kHz      |

| 10  | Pulse Frequency - (Pin 18)<br>Square Wave (V <sub>GEN5</sub> ) | F <sub>5</sub>                         | 6.25                      | kHz      |

| 11  | Positive Supply - (Pin 1)<br>Voltage                           | +V <sub>S</sub>                        | + 15 ± 10%                | ٧        |

| 12  | Negative Supply - (Pin 27)<br>Voltage                          | -V <sub>S</sub>                        | - 15 ± 10%                | V        |

<sup>1.</sup> Cool device down to ≤ +35°C, under bias, measure within 24 hours, after removal from bias.

PAGE 36

ISSUE 2

# FIGURE 5(a) - ELECTRICAL CIRCUIT FOR HIGH TEMPERATURE REVERSE BIAS BURN-IN AND ACCELERATED LIFE

Ambient temp. = +135°C min.

Package = 28 pin CerDIP, 1M

Input signals = none.

$R1 - R4 = 1k\Omega \pm 5\%$

C1 - C2 =  $0.01\mu$ F, one each per socket

D1 - D2 = 1N4002 or equivalent, one each per board

$-V_S = -15V \pm 10\%, +V_S = +15V \pm 10\%$

$V_R$  = +15V ± 10%  $I_{(+V_S)}$   $\leq$  100 $\mu$ A per device  $I_{(-V_S)}$   $\leq$  100 $\mu$ A per device

PAGE 37

ISSUE 2

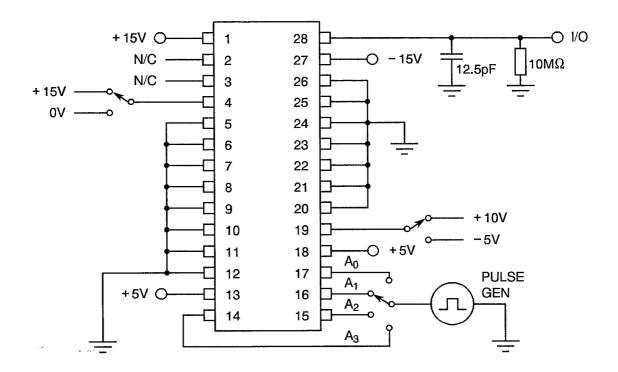

### FIGURE 5(b) - ELECTRICAL CIRCUIT FOR BURN-IN, DYNAMIC AND OPERATING LIFE TESTS

Ambient temp. = +125°C min.

= 28 pin CerDIP, 1M Package

Input signals:

(a) Square wave, 50% duty cycle, 0 to +15V peak, minimum

(b)  $F_1 = 100kHz$

$F_2 = 50kHz$

$F_3 = 25kHz$

$F_4 = 12.5 \text{kHz}$

$F_5 = 6.25 \text{kHz}$

(c)  $t_{TLH}$  and  $t_{THL} < 1\mu s$

R1 - R3 =  $1k\Omega \pm 5\%$ ,  $\frac{1}{4}$  watt min.

C1 - C2 =  $0.01\mu$ F, one each per socket

D1 - D2 = 1N4002 or equivalent, one each per board

$+V_S = +15V \pm 10\%$  $-V_S = -15V \pm 10\%$

PAGE 38

ISSUE 2

# 4.8 <u>ENVIRONMENTAL AND ENDURANCE TESTS (CHARTS IV AND V OF ESA/SCC GENERIC SPECIFICATION NO. 9000)</u>

### 4.8.1 Electrical Measurements on Completion of Environmental Tests

The parameters to be measured on completion of environmental tests are scheduled in Table 6. Unless otherwise stated, the measurements shall be performed at  $T_{amb}$  = +25 ±5 °C.

### 4.8.2 Electrical Measurements at Intermediate Points during Endurance Tests

The parameters to be measured at intermediate points during endurance tests are as scheduled in Table 6 of this specification. Unless otherwise stated, the measurements shall be performed at  $T_{amb}$  = +25 ±5 °C.

### 4.8.3 Electrical Measurements on Completion of Endurance Tests

The parameters to be measured on completion of endurance testing are as scheduled in Table 6 of this specification. Unless otherwise stated, the measurements shall be performed at  $T_{amb}$  = +25 ±5 °C.

### 4.8.4 Conditions for Operating Life Tests

The requirements for operating life testing are specified in Section 9 of ESA/SCC Generic Specification No. 9000. The conditions for operating life testing shall be as specified in Table 5(b) of this specification.

### 4.8.5 Electrical Circuits for Operating Life Tests

Circuits for use in performing the operating life tests are shown in Figure 5(b) of this specification.

### 4.8.6 Conditions for High Temperature Storage Test

The requirements for the high temperature storage test are specified in ESA/SCC Generic Specification No. 9000. The conditions for high temperature storage shall be  $T_{amb} = +150(+0-5)$  °C.

PAGE 39

ISSUE 2

# TABLE 6 - ELECTRICAL MEASUREMENTS ON COMPLETION OF ENVIRONMENTAL TESTS AND AT INTERMEDIATE POINTS AND ON COMPLETION OF ENDURANCE TESTING

| No.              | CHARACTERISTICS                                                                             | SYMBOL                 | SPEC. AND/OR<br>TEST METHOD | TEST<br>CONDITIONS | LIMITS |       | UNIT |

|------------------|---------------------------------------------------------------------------------------------|------------------------|-----------------------------|--------------------|--------|-------|------|

|                  |                                                                                             |                        |                             |                    | MIN    | MAX   | 0111 |