**e**2v

ICs packaging: Road Map and Trends for Space applications Thierry Gouvernel, Head of Strategic Business Development e2v Grenoble

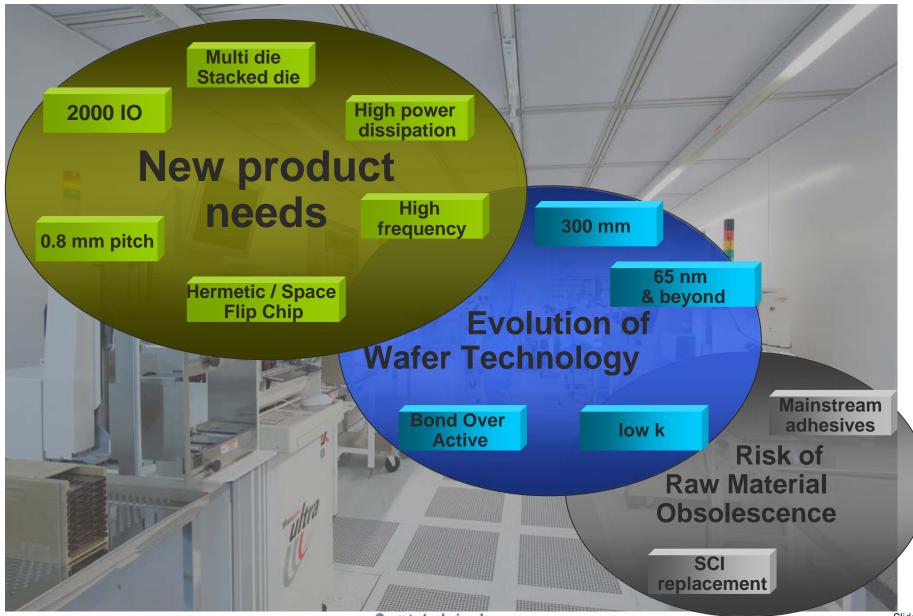

### **Needs**

# **e**2V

© e2v technologies plc

### Packaging products & process Where are we today?

| Wire bonding               |              | Flip Chip                |                         |

|----------------------------|--------------|--------------------------|-------------------------|

| Hermetic                   | Non hermetic | AI2O3                    | HiTCE                   |

| Ceramic DIL, PGA, QFP, BGA | EBGA         | High lead bumps          | High lead bumps         |

| → 352 leads (800 wires)    |              | → 1 cm <sup>2</sup> die  | → 1 cm <sup>2</sup> die |

| 32 µm aluminium wedge      | → 380 I/O    | → 25 x 25 mm LGA         | → 33 x 33 mm LGA        |

|                            | Ball bonding | Solder column interposer | High lead balls         |

|                            | SAC balls    |                          |                         |

|                            |              |                          |                         |

600 m<sup>2</sup>, class ISO5 (100) 500 m<sup>2</sup>, class ISO6 (1000) nb : preseal in class ISO 4 (10)

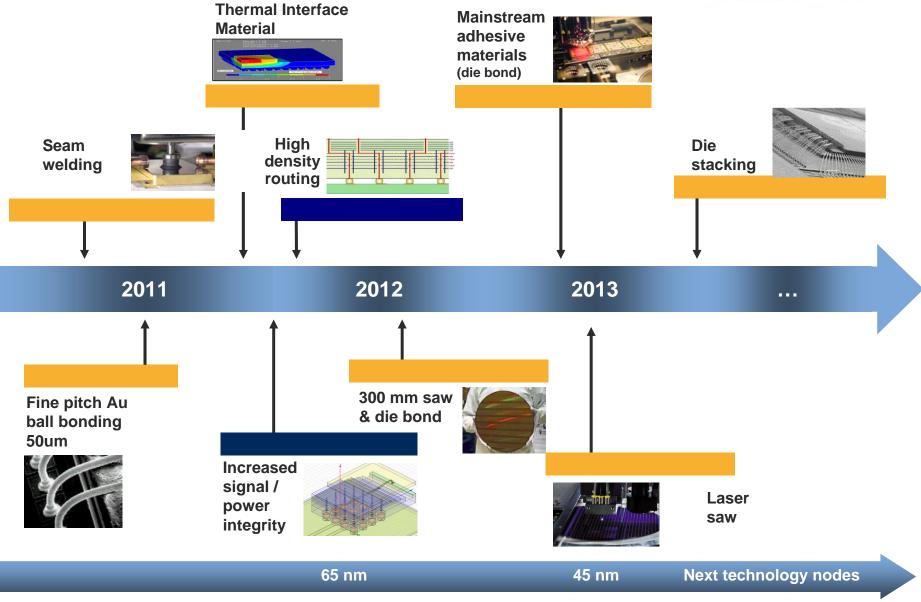

### Road Map Package Design & Assembly Process Capabilities

**e**2V

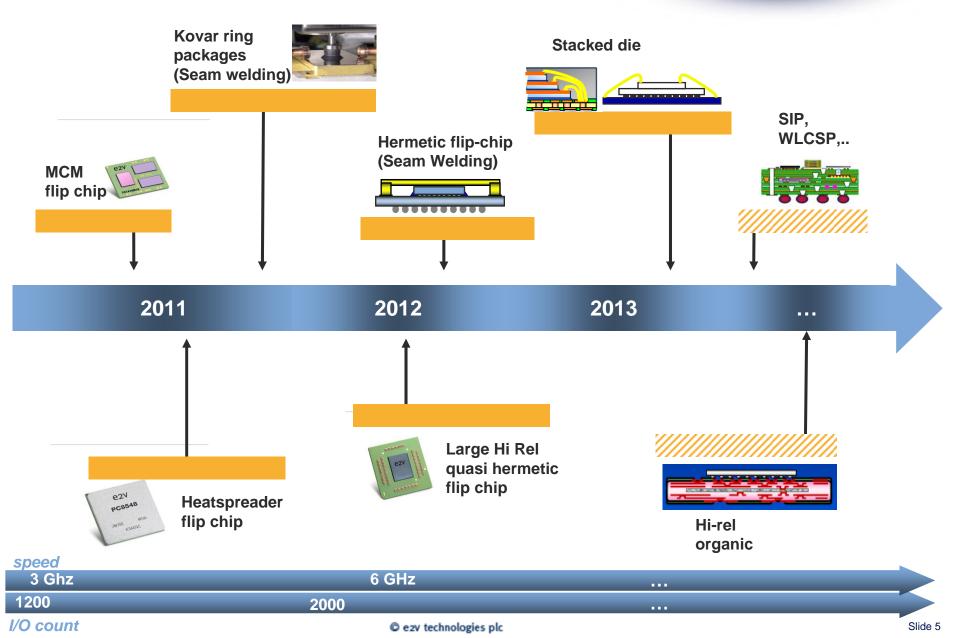

# Package Road Map

**e**2V

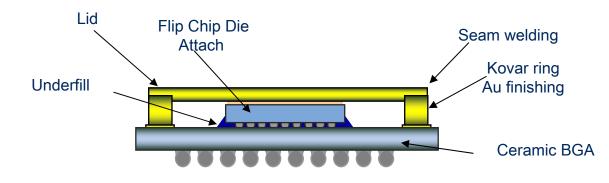

## **Technical Solutions Focus on : seam welding**

Current seal technology for hermetic packages (AuSn reflow) is performed at more than 300°C.

This temperature is now an important drawback, and seam welding becomes mandatory for :

- → gold wire bonding (condition for very fine pitch)

- → hermetic flip chip / underfill

→ use of mainstream die attach adhesives (epoxies,..) instead of high temperature specific materials, such as silver glass

- ➔ and, more generally, use of organic materials in the cavity for specific applications (getters, stacked die, Thermal Interface..)

- → compatibility with some wafer technologies which cannot withstand high temperature

For future products, this will lead to the addition of a kovar ring on package.

# Technical Solutions Focus on : Extended flip chip – Hermetic flip chip

Flip chip assembly has been performed at e2v for more than 10 years for military grade, up to 1 cm<sup>2</sup>, 1200 bumps.

In the next years, this capability shall extend to :

Larger dice (up to 2 cm<sup>2</sup>), high pin count

Smaller bump pitch

Low k wafers

Hermetic flip chip or Quasi hermetic (HiTCE ceramics)

### **Global trends - Discussion**

#### **Mainstream use**

On one side : Hi Rel / space market is becoming a specific requirement

On the other side : materials and equipements suppliers implement company / factory merges, which often leads to low runners EOL

→ In order to guarantee long term availability, we must use, as much as possible, mainstream materials / process / equipments

#### Hermeticity

It is still the baseline for ICs & should remain for several years. Nethertheless, attention should be paid to technologic evolutions in order to assess organic substrates, quasi hermetic solutions, etc...

#### Need for community support, in order to

develop or adapt materials / process / equipments for space applications

- assess reliability in Space environment

- develop ESCC specifications for flip chip, stacked die, etc...