# A3PE3000L - ACTEL FLASH FPGA -IRRADIATION TEST RESULTS

ESA contract No 22327/09/NL/SFE – ProASIC3L Family Flash Based FPGA M. Grandjean, F.X. Guerre, Hirex Engineering

## **Reference Documents**

#### 2/47

###

S. Rezgui & al., "New Reprogrammable and Non-Volatile Radiation Tolerant FPGA: RTA3P," presented at RADECS 2007, Deauville, France, September 2007

### $\square RD2$

S. Rezgui & al., "New Methodologies for SET Characterization and Mitigation in Flash-Based FPGAs," IEEE Trans. Nuc. Sci., vol, 54, n°6, pp. 2512-2524, Dec. 2007

###

ECSS Q 60-02, "Space Product Assurance, ASIC and FPGA development," July 2007

## Summary

- Background and Objectives

- □ Device overview

- Statement Of Work (SOW) requirements

- □ Test Vehicle designs

- □ Test conditions

- Radiation test results

## Steps

4/47

- Background and Objectives

- □ Device overview

- Statement Of Work (SOW) requirements

- □ Test Vehicle designs

- □ Test conditions

- Radiation test results

- □ Conclusion

## **Background and Objectives**

- □ ProASIC3 Flash Based FPGA (ACTEL)

- Reprogrammable and Non-Volatile

- $\square > 1$  Millions gates

- □ Previous ACTEL test results (RD1 and RD2)

=> Very attractive for space applications

## Steps

6/47

- Background and Objectives

- Device overview

- Statement Of Work (SOW) requirements

- □ Test Vehicle designs

- □ Test conditions

- Radiation test results

- □ Conclusion

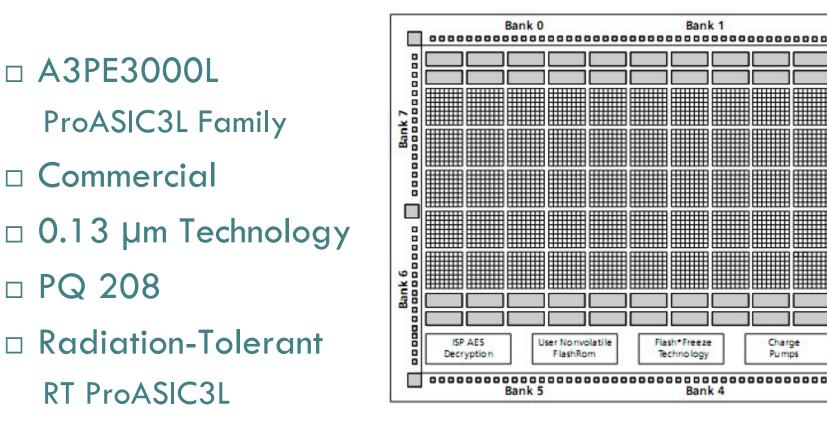

## Device overview

0000

00000

000000000000

Bank 3

□ RT3PE3000L / A3PE3000L same silicon

ESA - Microelectronics Presentation Days

## Steps

8/47

- Background and Objectives

- □ Device overview

- Statement Of Work (SOW) requirements

- □ Test Vehicle designs

- □ Test conditions

- □ Radiation test results

# SOW - Requirements (1/2)

- □ A3PE3000L radiation test (HIs, protons, TID)

- □ SEL, SEFI, SEU, SET and SEGR sensitivities

- □ Temperature: room up to 125 °C

- □ Frequencies: 2, 50, 100 and 200 MHz

- □ 2 Test Vehicle (TV) Designs:

- TV1 Characterization of the FPGA

- TV2 Characterization of SEE mitigation methods

Reference Documents: RD1, RD2, RD3

SOW - Requirements (2/2)

### □ TV1

- $_{\circ}$  14 SRs (1024 R-cells) with different I/O standards

- SRAM, UFROM

- CCC/PLL

- □ TV2

- SRs (1024 R-cells) with SEU & SET mitigation methods

## Steps

- Background and Objectives

- □ Device overview

- Statement Of Work (SOW) requirements

- Test Vehicle designs

- □ Test conditions

- Radiation test results

# TV1 - Shift Registers

- □ 14 SRs

- □ Different clock sources and I/O Types

- □ Frequency up to 200 MHz

| Shift Register | Clock source | I/O Type         | Singularity                |  |

|----------------|--------------|------------------|----------------------------|--|

| 1              | External     | 3.3 V LVCMOS     | Reference                  |  |

| 2              | External     | 3.3 V LVCMOS     | Enable C-cells             |  |

| 3              | External     | 3.3 V LVCMOS     | Clear C-cells              |  |

| 4              | External     | 3.3 V LVCMOS     | C-cells in-between R-cells |  |

| 5 to 8         | External     | 3.3 V LVCMOS DDR | DDR registers              |  |

| 9 to 10        | External     | 2.5 V LVDS       | LVDS buffers               |  |

| 11 to 14       | Internal PLL | 3.3 V LVCMOS     | PLL Clock                  |  |

ESA - Microelectronics Presentation Days

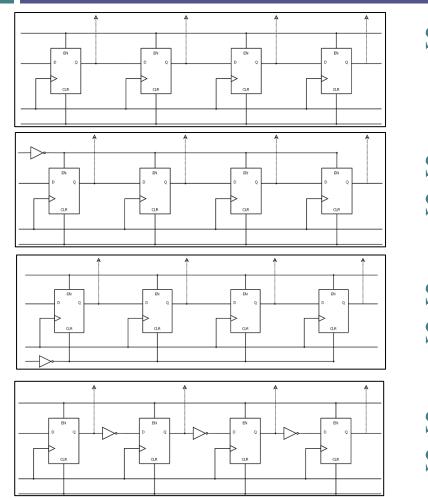

## TV1 - SR 1 to 4

#### 13/47

ESA - Microelectronics Presentation Days

SEU on registers

SEU on registers SET on enable signal

SEU on registers SET on clear signal

SEU on registers SET on C-cells

# TV1 - SR 5 to 14

- □ Cores are identical to the SR 1

- □ 4 Channels with DDR I/O registers

- $_{\rm O}\,$  SEU on registers and on DDR I/O registers

- □ 2 Channels with LVDS I/O buffers

- SEU on registers

- $_{\rm O}\,$  SET on LVDS I/O buffers

- □ 4 Channels clocked by the PLL output

- SEU on registers

- $_{\rm O}\,$  SEU and SET on the CCC / PLL

# TV2 - Shift Registers

15/47

6 SRs including SEE mitigation methods

Frequency up to 75 MHz

| Shift Register | Sequential<br>Cell<br>Triplication | I/O Block<br>Triplication | SET<br>Filtering | Combinational<br>Cell<br>Duplication | Combinational<br>Cell<br>Triplication |

|----------------|------------------------------------|---------------------------|------------------|--------------------------------------|---------------------------------------|

| 1              | ×                                  |                           |                  |                                      |                                       |

| 2              | ×                                  | ×                         |                  |                                      |                                       |

| 3              |                                    |                           | ×                |                                      |                                       |

| 4              | ×                                  | ×                         | ×                |                                      |                                       |

| 5              | ×                                  | ×                         |                  | ×                                    |                                       |

| 6              | ×                                  | ×                         |                  |                                      | ×                                     |

## SRAM & UFROM

16/47

□ Only on the TV1 112 Blocks of 512 Words of 9 Bits • Frequency up to 20 MHz 8 Banks of 16 Words of 8 Bits • Frequency up to 10 MHz

## **Miscellaneous Parts**

### $\square$ CCC / PLL:

- Only on the TV1

- Static mode (single frequency) set on 200 MHz

- Output clock used to clock 4 SRs (TV1)

- Lock signal supervised

- Configuration Flash, Charge pump and ISP

- Verification of the functionality

- Verification of the re-configurability

## TVs - Design Results

### □ TV1

- 14 SRs, 100 % of the Memories, 1 CCC with PLL, several I/O standards

- => 32 % of the logic core, 93 % of I/O

$\Box$  TV2

6 SRs, no memory, no PLL, LVCMOS 3.3V => 97 % of the logic core, 52 % of I/O

## Steps

- Background and Objectives

- □ Device overview

- Statement Of Work (SOW) requirements

- □ Test Vehicle designs

- Test conditions

- Radiation test results

## **Power Supplies**

- □ 13 power supplies

- VCC: 1 x Core supply 1.5 V nom

- Vbanks: 8 x Banks supplies 2.5 or 3.3 V nom

- VPLLs: 2 x CCC / PLL supplies 1.5 V nom

- VJTAG: 1 x JTAG supply 3.3 V nom

- VPUMP: 1 x PUMP supply 3.3 V nom

### $\square$ V nom + 10 % for SEL tests

## Test set-up

- □ Heavy ions: RADEF 2 campaigns

- □ Protons: PIF 1 campaign

- □ TID: design process is running

- □ Test sequence: fill / expose / check

- Dynamic, static and flash-freeze tests

- Selectable frequencies (up to > 200 MHz)

- □ Standard patterns (checkerboard and static)

- □ Specific algorithms

## **Configuration Flash Set-up**

- Configuration sequence under beam: erase / program / check - using ACTEL tool

- Status declared by:

- Success of operation (program passed / failed)

- Design functionality

- Verification of the re-configurability

## Steps

- Background and Objectives

- □ Device overview

- Statement Of Work (SOW) requirements

- □ Test Vehicle designs

- □ Test conditions

- Radiation test results

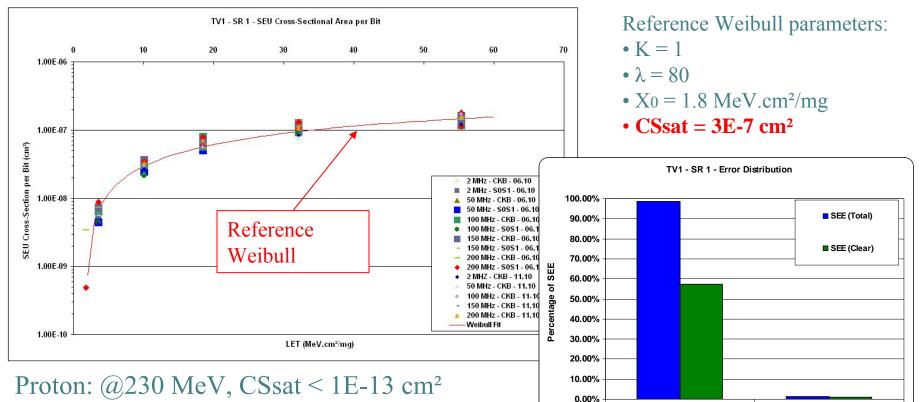

# (1/14) - TV1 - SR 1

24/47

### Reference channel - standard shift register

Low sensitivity => 1E11 p/cm<sup>2</sup> => Large dose => limits the characterization => 230 MeV

ESA - Microelectronics Presentation Days

March 28th and 29th 2001

LE

SEU

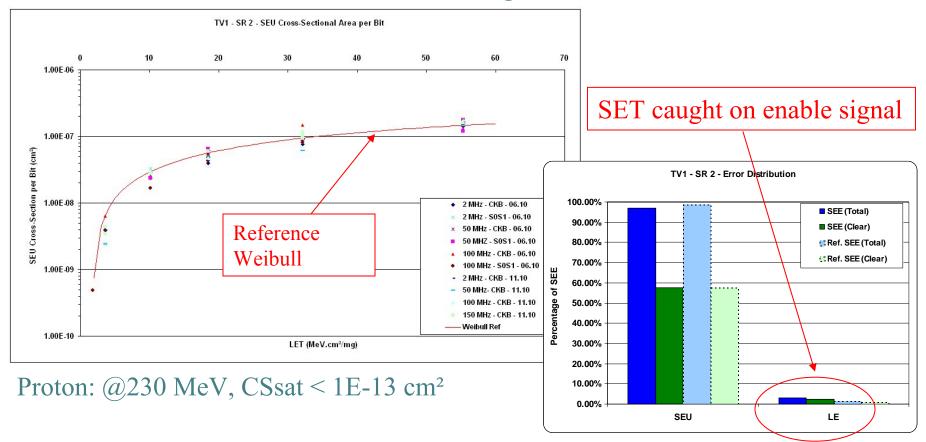

# (2/14) - TV1 - SR 2

25/47

### Channel with C-cells in the enable signal

ESA - Microelectronics Presentation Days

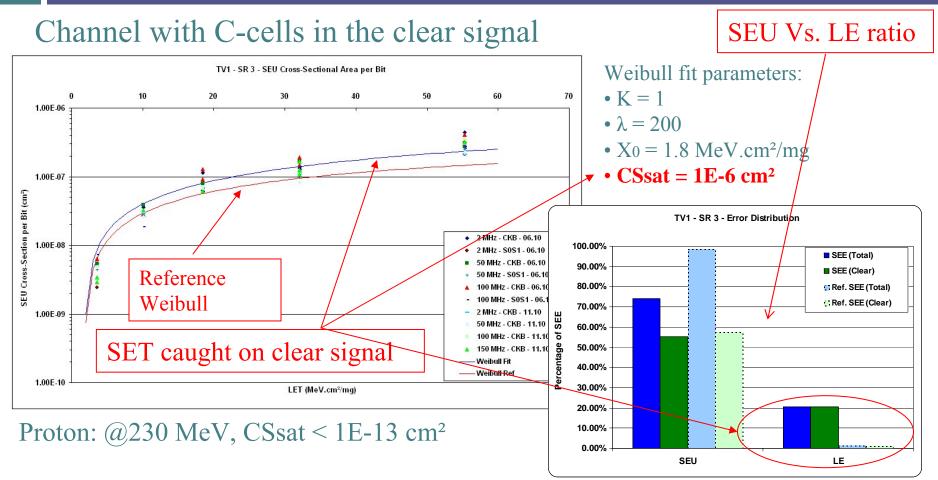

# (3/14) - TV1 - SR 3

26/47

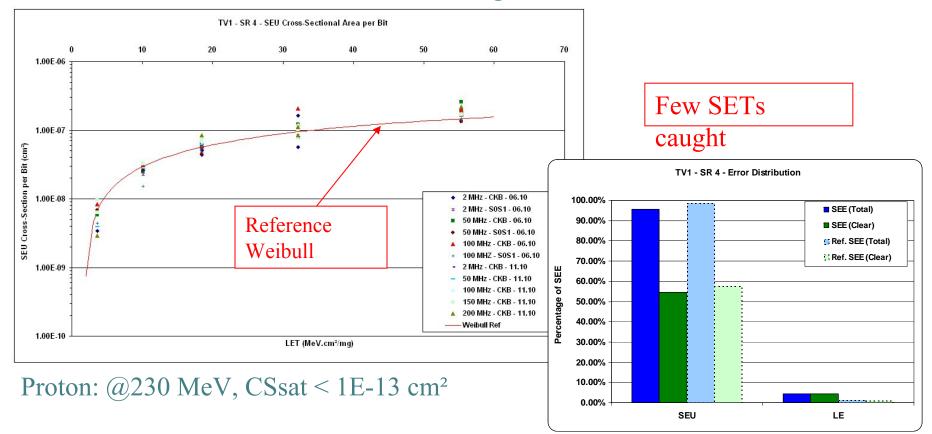

# (4/14) - TV1 - SR 4

27/47

### Channel with C-cells in-between registers

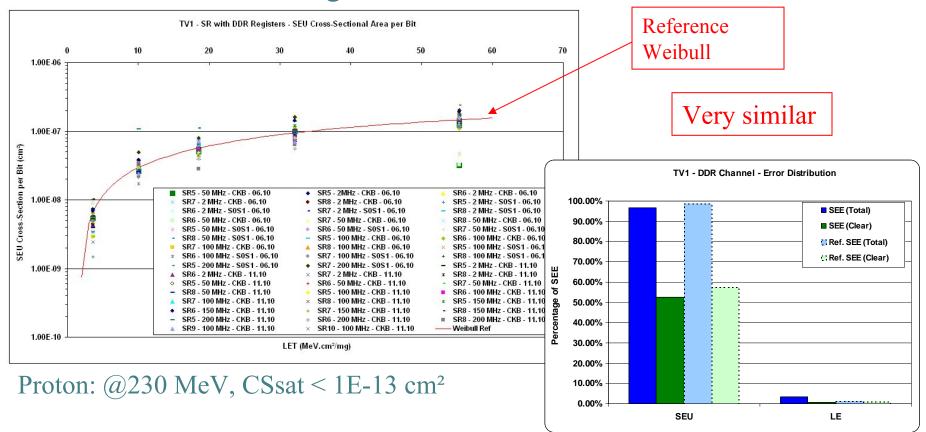

# (5/14) - TV1 - SR DDR

28/47

### Channels with DDR registers

ESA - Microelectronics Presentation Days

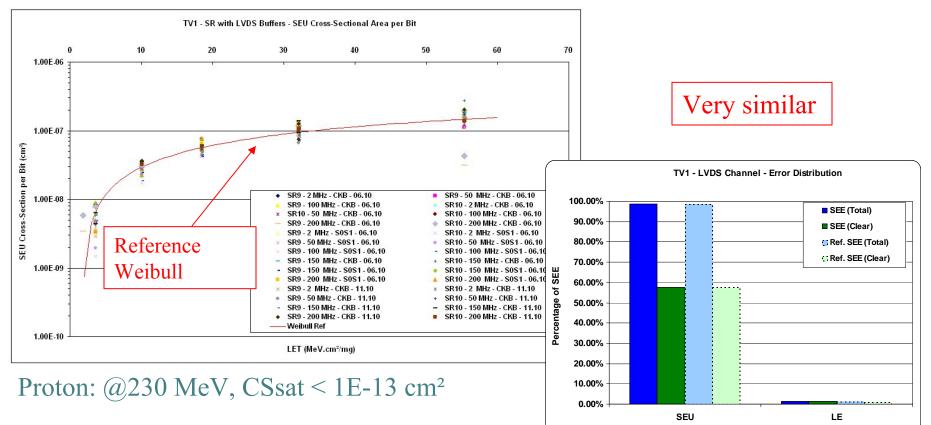

# (6/14) - TV1 - SR LVDS

29/47

### Channels with LVDS buffers

ESA - Microelectronics Presentation Days

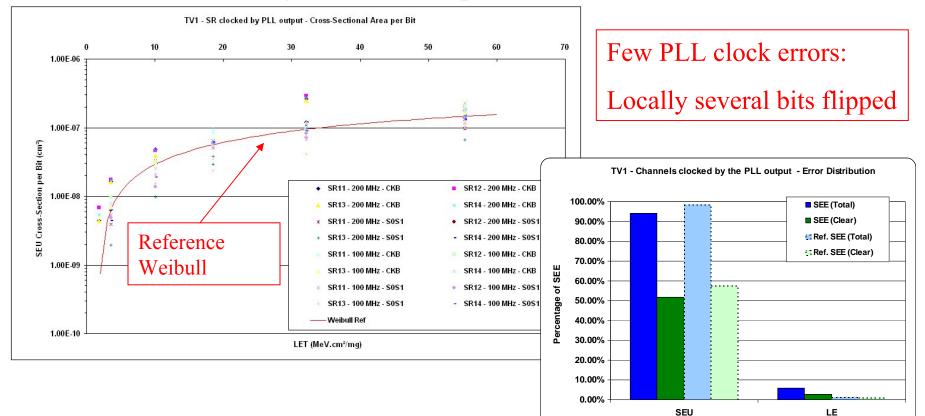

# (7/14) - TV1 - SR PLL

30/47

### Channels clocked by the PLL output

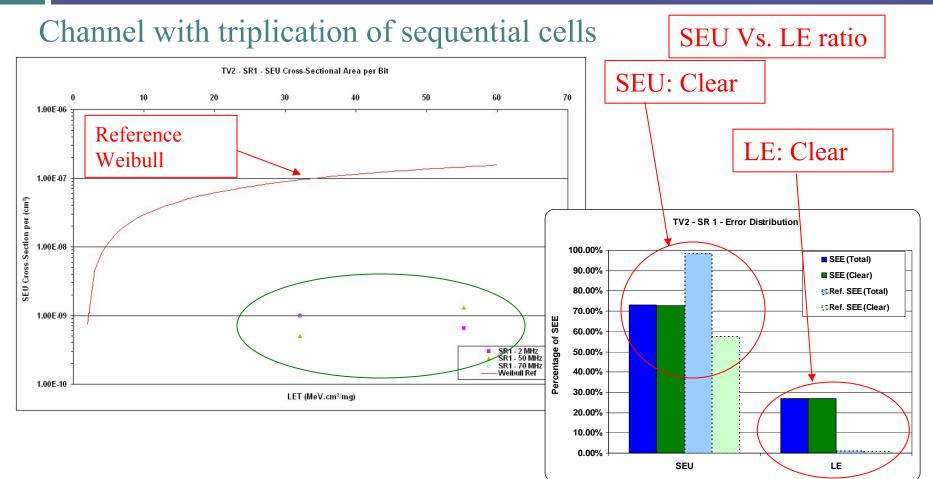

# (8/14) - TV2 - SR 1

#### 31/47

#### ESA - Microelectronics Presentation Days

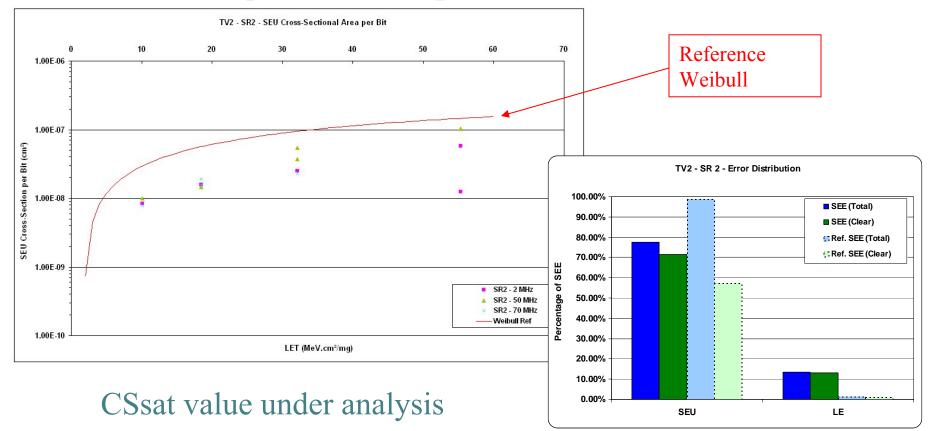

# (9/14) - TV2 - SR 2

#### 32/47

### Channel with triplication of sequential cells and I/O Blocks

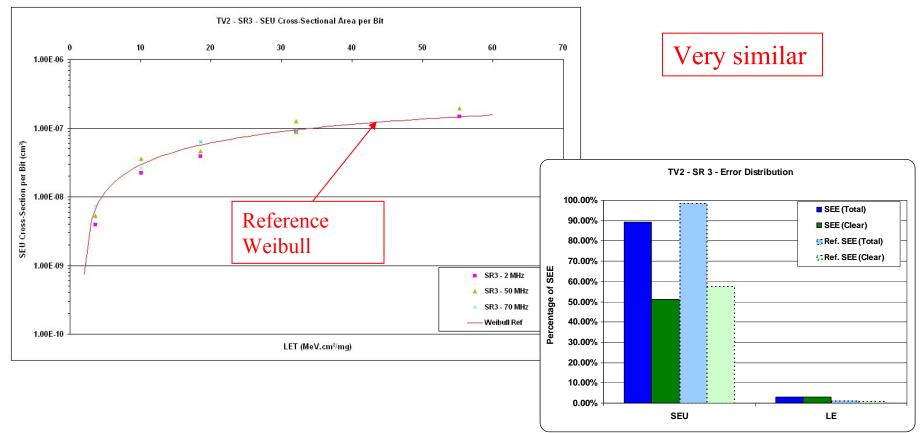

# (10/14) - TV2 - SR 3

33/47

### Channel with SET filtering (2 ns)

ESA - Microelectronics Presentation Days

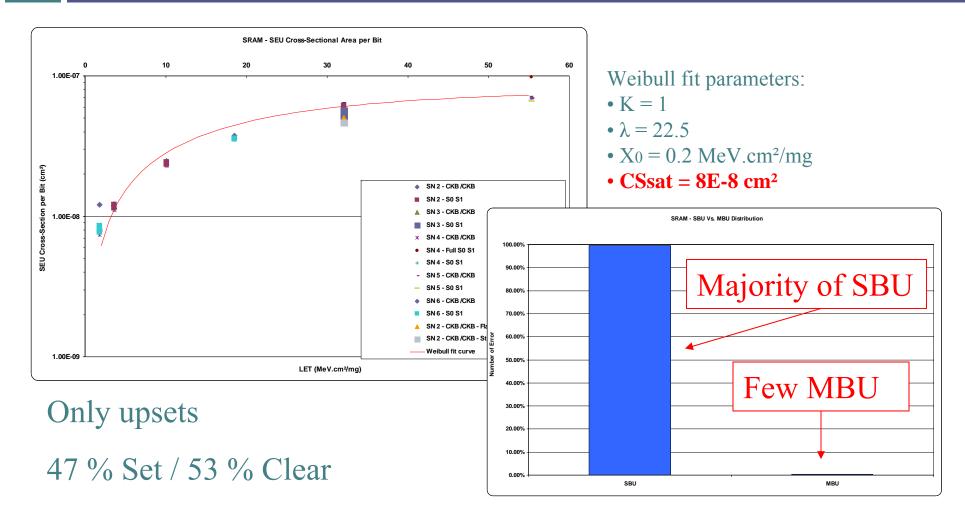

# (11/14) - SRAM - HI

34/47

ESA - Microelectronics Presentation Days

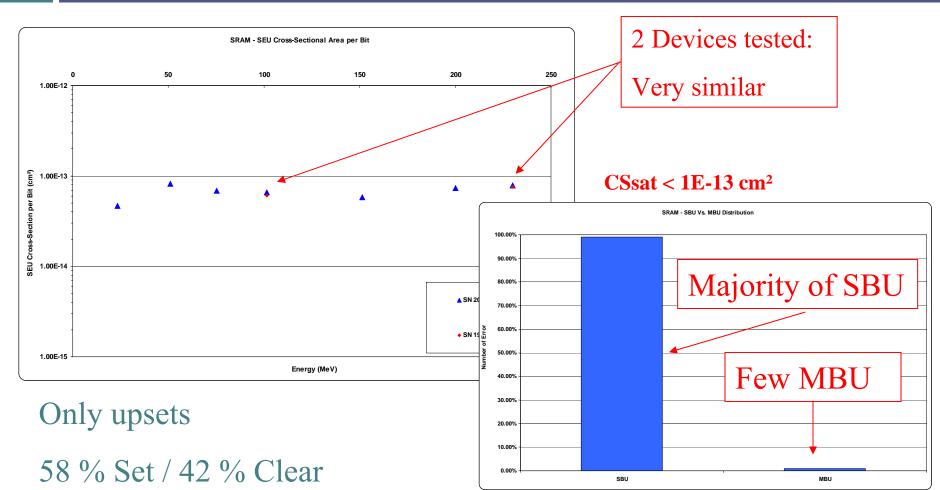

# (12/14) - SRAM - Protons

35/47

ESA - Microelectronics Presentation Days

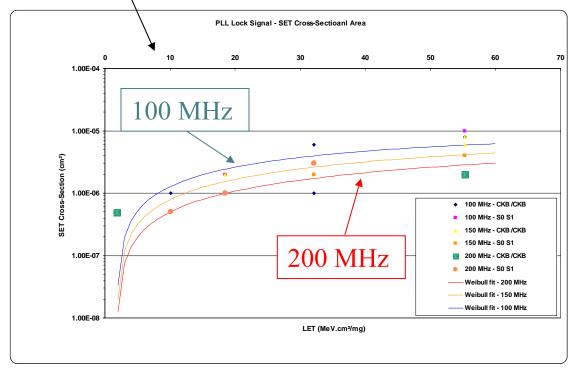

(13/14) - PLL

### Output clock is lightly sensitive to SEE

□ Lock signal is sensitive to SEE (SEFI, SET)

Weibull fit parameters:

- K = 1

- $\lambda = 60$

- $X_0 = 1.8 \text{ MeV.cm}^2/\text{mg}$

- CSsat = 1E-5 cm<sup>2</sup>

The clock output never stopped

ESA - Microelectronics Presentation Days

# (14/14) - SEL & Flash

### □ <u>NO SEL</u>

Vnom +10%, 125 °C, 55.3 MeV.cm<sup>2</sup>/mg, 5E6 p/cm<sup>2</sup>

- □ Flash is NOT sensitive to SEE

- Configuration and User flash remained intact

- □ The Flash **programming part** is sensitive to:

- **SEE**

- SHE

- Cumulated dose deposited by the cumulated fluence

## Steps

- Background and Objectives

- □ Device overview

- Statement Of Work (SOW) requirements

- □ Test Vehicle designs

- □ Test conditions

- Radiation test results

# Conclusion (1/2)

Irradiation characterization made on:

• A3PE3000L

39/47

- SEE mitigation methods (flash based FPGA)

- □ **No SEL** up to 55.3 MeV.cm<sup>2</sup>/mg, Vnom +10%, 125°C, 5E6 p/cm<sup>2</sup>

- □ Flash is not sensitive to SEE up to 55.3 MeV.cm<sup>2</sup>/mg

- □ Registers, SRAM, PLL and Global network

- => sensitive to SEU and SET

- Cross-Sections are established

# Conclusion (2/2)

40/47

| TV | Shift Register | Singularity                             | SEE Summary               |  |

|----|----------------|-----------------------------------------|---------------------------|--|

| 1  | 1              | Reference                               | SEU (DFF)                 |  |

|    | 2              | Enable C-cells                          | SEU (DFF) + SET (enable)  |  |

|    | 3              | Clear C-cells                           | SEU (DFF) + SET (clear)   |  |

|    | 4              | C-cells in-between R-cells              | SEU (DFF) + SET (C Cells) |  |

|    | 5 to 8         | DDR registers                           | SEU (DFF)                 |  |

|    | 9 to 10        | LVDS buffers                            | SEU (DFF)                 |  |

|    | 11 to 14       | PLL Clock                               | SEU (DFF) + Few SEE (PLL) |  |

| 2  | 1              | R Cells TMR                             | Few SEU (DFF)             |  |

|    | 2              | R Cells + I/O TMR                       | Under analysis            |  |

|    | 3              | SET Filtering                           | SEU (DFF)                 |  |

|    | 4              | R Cells + I/O TMR + SET Filtering       | Φ                         |  |

|    | 5              | R Cells + I/O TMR + C Cells duplication | Φ                         |  |

|    | 6              | Full TMR                                | Φ                         |  |

### Final report estimated for June 2011

ESA - Microelectronics Presentation Days

## THANK YOU!

### Any question?