## SECTION 4. ARTIFICIAL RADIATION ENVIRONMENTS IN ORBIT

## 4.1. GENERAL

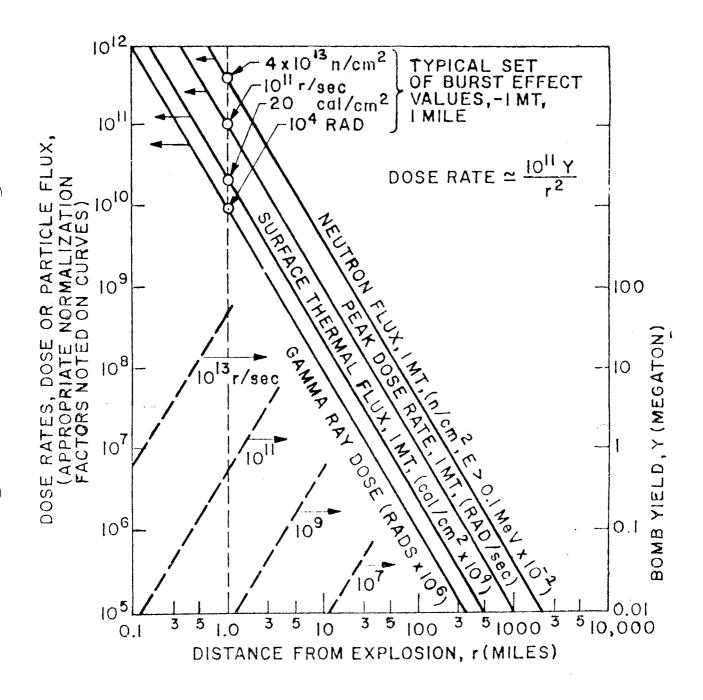

In the natural space environment, intense, transient pulses of ionising radiation do not occur except in the form of single-particle events. However, it is possible that even civil satellites may be exposed to the effects of distant nuclear weapons exploded in space, as happened in the 1962 "Starfish" nuclear test. In the future, exposure to pulsed beams of ionising radiation from spaceborne particle accelerators, X-ray generators or nuclear reactors is also possible. We will therefore give a brief account of "Transient Radiation Effects in Electronics" (TREE) and give references to the very extensive sources of information which have been generated mainly by defence agencies. An unclassified version of the yields from a nuclear event is given in Figure 4.1

## 4.2. WEAPON EFFECTS

A nuclear explosion generates a very short (20 ns) pulse of gamma rays from nuclear reactions, and X-ray, neutron and electromagnetic pulses which may last for milliseconds. Particle accelerators and X-ray machines can generate continuous beams, but are often operated in a series of pulses of microsecond duration. The exposure of a device to one of these sources will produce:

- (a) dose-rate or "transient" effects (e.g. photocurrents),

- (b) "total dose" or long-lived effects (e.g. charging or bulk damage).

There is likely to be "rapid annealing" of the material response during the first few seconds, then more gradual relaxations over many hours. In logic circuits, the transient photocurrents generate spurious signals and may produce "logic upset" or, at higher intensities, induce thermal destruction. In some semiconductor devices containing 4-layer junction structures, a low impedance condition, known as latchup may be triggered. Latchup leads to thermal destruction caused by the energy from the power supply.

"Logic upset" is fundamentally a transient effect, but - in some circuits - may have a permanent result. For example, while a simple NAND gate, set in the logic "1" state, may transiently indicate a "0" state during the burst, it will return to the "1" state within microseconds. A bistable circuit such as a memory cell may return to the original state or, instead, change to the opposite state. These two upset effects are called "temporary" and "permanent" respectively.

Brucker has tabulated some general values for the levels of pulsed radiation environment at which the above effects take place in certain CMOS and bipolar integrated circuits. These levels are given in Table 4(1). Only orders of magnitude are stated here, but the data still supply useful guidance for system engineers and circuit designers. Brucker notes that bulk CMOS logic gates can be used in a transient radiation environment (20 nanosecond pulse) if they are not required to operate during the radiation burst. Limiting resistors or SCR crow bars can be used on CMOS voltage supplies as protection against latchup. Bulk CMOS shift registers or memories are vulnerable if they are required to store data through a radiation burst without loss. These devices are subject to permanent upset or scrambling of stored data. SOS CMOS shift registers, memories or logic gates can be used in a transient environment without risk of latchup. Logic gates are still subject to temporary and permanent upsets, but the limiting dose rates of the SOS devices exceed those of the bulk devices by at least an order of magnitude.

Brucker comments further that upset and latchup rates are strongly dependent on the circuit design and that the reduction of operating voltage from 10 to 5 volts increases by at least a factor of two the dose rate threshold for latchup. In some circuits, latchup dose rates may be very high. For example, the CD4061 is very resistant to latchup. In a transient environment, the higher noise immunity of CMOS devices makes them preferable to TTL.

FIGURE 4.1 - NOMINAL RADIATION LEVELS FROM NUCLEAR EXPLOSIVES IN SPACE

TABLE 4.(1) - SOME UPSET LEVELS FOR CMOS CIRCUITS

|                                           | Effect                                                           | General range                                                                                                                                          |

|-------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMOS/BULK LOGIC GATES                     |                                                                  | 108 - 10 <sup>9</sup> rad/s                                                                                                                            |

| - Transient (20 ns pulse)<br>- Long-lived | Temporary upset Latchup Survival Total dose Neutrons             | 10 <sup>6</sup> - 5x10 <sup>9</sup> rad/s<br>10 <sup>12</sup> - 10 <sup>13</sup> rad/s<br>10 - 1000 Krad<br>10 <sup>15</sup> n/cm <sup>2</sup>         |

| CMOS/BULK SHIFT REGISTERS                 | Temporary upset                                                  | 10 <sup>8</sup> - 10 <sup>9</sup> rad/s                                                                                                                |

| - Transient<br>- Long-lived               | Permanent upset<br>Latchup<br>Survival<br>Total dose             | 5x10 <sup>8</sup> - 5x10 <sup>9</sup> rad/s<br>10 <sup>8</sup> - 5x10 <sup>9</sup> rad/s<br>10 <sup>12</sup> - 12 <sup>13</sup> rad/s<br>10 - 1000 rad |

| CMOS/BULK MEMORIES - Transient            | Temporary upset<br>Permanent upset<br>Latchup                    | 10 <sup>7</sup> - 10 <sup>8</sup> rad/s<br>8 x 10 <sup>7</sup> rad/s<br>8 x 11 rad/s                                                                   |

| - Long-lived                              | Survival<br>Total dose<br>Neutrons                               | 10 <sup>11</sup> rad/s<br>10 - 1000 Krad<br>10 <sup>15</sup> n/cm <sup>2</sup>                                                                         |

| CMOS/SOS MEMORIES                         | Temporary upset                                                  | 7 x 10 <sup>9</sup> rad/s                                                                                                                              |

| - Transient                               | Permanent upset<br>Latchup                                       | 10 <sup>11</sup> rad/s<br>Not possible                                                                                                                 |

| - Long-lived                              | Survival<br>Total dose<br>Neutrons                               | 10 <sup>11</sup> rad/s<br>6 Mrad<br>10 <sup>15</sup> n/cm <sup>2</sup>                                                                                 |

| CMOS/BULK MICROPROCESSORS                 | Permanent upset<br>Latchup<br>Survival<br>Total dose<br>Neutrons | 10 <sup>8</sup> rad/s<br>10 <sup>8</sup> rad/s<br>10 <sup>11</sup> - 10 <sup>12</sup> rad/s<br>10 Krad<br>10 <sup>15</sup> n/cm <sup>2</sup>           |

TABLE 4(1) - SOME UPSET LEVELS FOR CMOS CIRCUITS (Continued)

|                                                        | Effect                                                           | General range                                                                                                                                                   |

|--------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TTL LOGIC, JUNCTION ISOLATED  - Transient - Long-lived | Temporary upset<br>Latchup<br>Survival<br>Total dose<br>Neutrons | 10 <sup>8</sup> - 10 <sup>9</sup> rad/s<br>Very limited evidence<br>of existence<br>10 <sup>12</sup> rad/s<br>10 Mrad<br>5 x 10 <sup>13</sup> n/cm <sup>2</sup> |

| TTL DIELECTRIC-ISOLATED LOGIC                          | Temporary upset<br>Latchup<br>Survival<br>Total dose<br>Neutrons | 10 <sup>9</sup> - 10 <sup>10</sup> rad/s<br>Not possible<br>10 <sup>12</sup> rad/s<br>10 Mrad<br>3 x 10 <sup>14</sup> n/cm <sup>2</sup>                         |

| I <sup>2</sup> L LOGIC                                 | Temporary upset<br>Latchup<br>Survival<br>Total dose<br>Neutrons | 2 x 10 <sup>9</sup> rad/s<br>Not possible<br>10 <sup>12</sup> rad/s<br>1 Mrad<br>10 <sup>13</sup> n/cm <sup>2</sup>                                             |