# NASA - Led G12 Class Y Initiative (Infusion of New Technology into QML)

European Space Components Conference

(ESCCON)

Noordwijk, The Netherlands

March 12 – 14, 2013

S. Agarwal<sup>1</sup>, R. Carlson<sup>1</sup>, D. Sunderland<sup>2</sup>, M. Akbar<sup>3</sup>, L. Harzstark<sup>4</sup>

<sup>1</sup> Jet Propulsion Laboratory, California Institute of Technology; <sup>2</sup> Boeing Corporation,

<sup>3</sup> DLA Land & Maritime, <sup>4</sup> The Aerospace Corporation

Curiosity in Operation (Artist's Concept)

## G12 Task Group No. 2010-01 Class Y: A New QML Class for Non-Hermetic Space Products

Task Group Meeting No. 9

San Antonio, Texas January 15, 2013

S. Agarwal<sup>1</sup>, R. Carlson<sup>1</sup>, D. Sunderland<sup>2</sup>, M. Akbar<sup>3</sup>, L. Harzstark<sup>4</sup>

<sup>1</sup> Jet Propulsion Laboratory, California Institute of Technology; <sup>2</sup> Boeing Corporation,

<sup>3</sup> DLA Land & Maritime, <sup>4</sup> The Aerospace Corporation

www.nasa.gov Copyright 2012. All rights reserved.

## **Agenda**

- Introduction

- Why "Class Y"

- The Initiative at a Glance

- Progress Status

- Issues

- 38535 QML Space Status

- Including:

- > Section Y: Task Group 10-01 Summary (pp. 14-20)

#### Introduction

**Purpose:** This talk is about an **EXPERIMENT** in adopting a new technology for military and space.

**Fact:** Advancements in packaging technology, increasing functional density, and increasing operating frequency have resulted in single-die system-on-a-chip (SoC) with non-hermetic flip-chip construction, in high-pin-count ceramic column grid array packages.

**Question:** Do we want to stay current with developments in technology? If so, how to bring such devices into the military/space standardization system?

**Approach:** Perform reliability and radiation evaluations. If acceptable, work on making it a QML product.

## Why "Class Y"?

- This effort is an attempt to bring advancements in packaging technology into the QML system.

- Advancements in packaging technology, increasing functional density, and increasing operating frequency have resulted in single-die SoCs with non-hermetic flip-chip construction, in high-pin-count ceramic column grid array packages

- "Poster Child" example: Virtex-4 (V-4) FPGAs from Xilinx

- Such products were evaluated for radiation and reliability and have drawn the attention of the space user community

- Question: How do we bring V-4 and similar microcircuits into the QML system as space products?

- It can't be Class V because those are hermetic devices

- Our intent is to put V-4 like products for space users in a new category: "Class Y".

- In Jan. 2010, G-12 opened a Task Group to develop Class Y

- What if we dropped the Class Y effort?

- It would be a major loss for the space community and the QML program at large because the industry would be limited to ordering via Source Control Drawings (SCDs), which is counterproductive to Mission Assurance, prevents standardization, and is expensive.

#### **Background**

Back in 2009, there was a big push to bring the Xilinx Virtex-4 (a non-hermetic part) into the Qualified Manufacturing List (QML) system as Class V device. NASA and others were not in favor as this would have created massive confusion. Mike Sampson conceived the idea of a new Class Y for non-hermetic space parts to provide QML coverage for the Xilinx Virtex-4 and similar devices.

A new G-12 Task Group, TG 2010-01, was formed in early 2010 to address non-hermetic devices for space. Shri Agarwal was asked to lead the effort.

This task was challenging because it:

- Was far more involved than typical G12 tasks,

- Required development of a brand new concept,

- Used system-on-a-chip (SoC) one of the most complicated devices,

- Needed to be simple and easily understood,

- Possessed sketchy testing and board assembly boundaries, and

- Was needed to procure a standard QML product as quickly as possible.

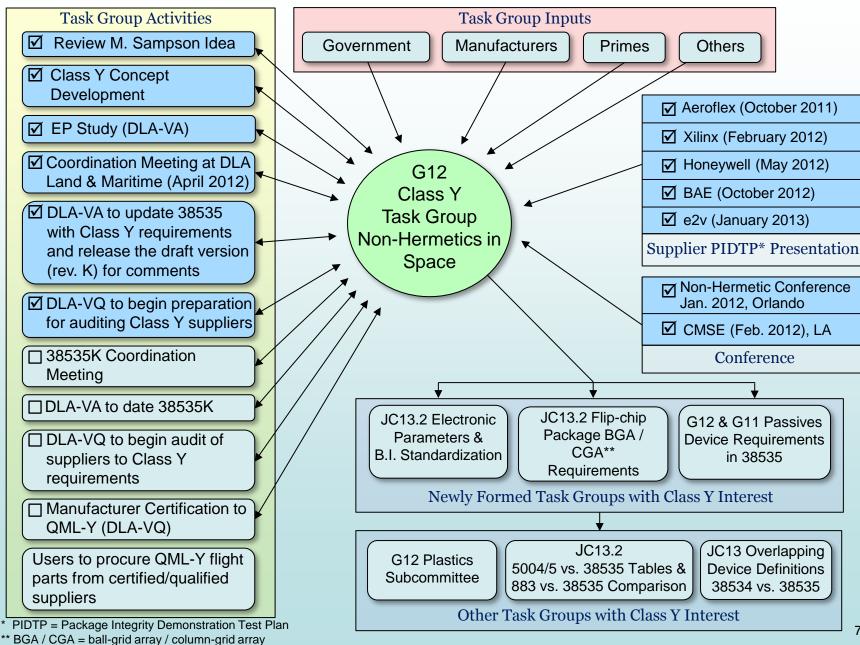

#### Infusion of New Technology into the QML System **G12 Class Y Effort at a Glance**

#### **Progress Status**

- DLA-VA completed their Engineering Practice (EP) Study on class Y.

The amended EP study report available on DLA website.

- At the October 2012 TG meeting in Columbus, the group voted to go with option 1 recommendation which was:

DLA-VA to update 38535 with Class Y requirements and release it (keeping the requirements for common issues the same as they exist today for QMLV). DLA-VQ to begin preparation for auditing Class Y suppliers based on initial draft of 38535, rev. K.

Keep working the common issues as quickly as possible. Continue to update the MIL documents as conclusions are reached on these issues.

DLA-VA released draft of 38535, Rev. K with added Class Y requirements along with other updates. The community should give a thorough review to the draft and submit their comments to DLA by February 21, 2013.

#### **Issues Discussed in G12 Class Y Meetings**

- Solder-terminated parts (could be hermetic or non-hermetic) need attention. Proposed a paragraph to add to MIL-PRF-38535, Appendix B. The JC-13.2 Task Group on solder terminations has been formed. The broad issues are: solderability, storage and shelf life, electrical testing, reworks, pull test, termination definition (tin– lead solder based?), etc. Some specific questions are:

- ➤ What is the shelf life of the CGA? Specifically, how long will these parts be 100% solderable? Is this guaranteed?

- As the columns would tend to oxidize when exposed to atmosphere, how do you store them: keep in sealed dry bags? Store in dry nitrogen?

- ➤ Do all internal and external portions of the flip-chip package pass MIL-STD-883, Method 5011 (evaluation of polymeric materials)?

- ➤ Once assembled, can the finished CGA (Like all other microcircuits, transistors, and hybrids) be functionally tested at -55°C, 25°C, and +125°C? (If the solder melting point is estimated at about 180°C, then it would be risky to electrically test the parts at 125°C case temperature. Any cold brittle concerns at -55°C?)

- What board/assy level tests have been run for temp cycling/vibration, etc.?

- What is the max number of allowable column reworks for space products?

- Specify column pull test

- Inspection of CGAs (area arrays, in general)

- ➤ Need application notes on CGAs after column attach so that the users know what they are getting, any temperature limitations, adequacy of visual inspection, cleanliness, fluxes to avoid, etc.

- Coordinate with IPC what boundaries separate JEDEC work from IPC work?

#### **Issues Discussed in G12 Class Y Meetings (Contd.)**

- Clarification needed on burn-in, electricals, and delta requirements. This is a major issue for all microcircuits and would apply to Class Y products as well. For instance, statements such as, "The XXX FPGA has undergone 4000 hours of life test with parts biased in a static condition," make one wonder why an FPGA (which is basically a digital part) was not subjected to a dynamic condition? There are other questions related to the activation energy, low temperature burn-in, etc. At the request of L. Harzstark and S. Agarwal, a JC13 Task Group was formed to clarify/update requirements in MIL-STD-883, Method 5004.

- The screening/qual requirements for signal conditioning capacitors should be clearly stated (ref. MIL-PRF-38535, Paragraphs 3.15 and 3.15.1). What is the attaching method of the BME capacitors used in many designs? During the G12, a couple companies said they use epoxy or silver–glass die attachment material to adhere the capacitor to the internal portion of the IC package. There are others who only use solder attachment. A JC13 Task Group has been formed to address these issues.

- What is a space flight part?

- Land Grid Array, LGA, configuration (yes)

- Column Grid Array, CGA, configuration (debatable)

- Will the set of 38535 classes, with Class Y added, cover microcircuits for the next several years? (yes, per the poll taken of major manufacturers)

#### 38535 QML Space – Current Status

|            |                           | Class V<br>(Existing) | Class Y<br>(In Development) | Comment               |

|------------|---------------------------|-----------------------|-----------------------------|-----------------------|

| QML        | Need class specific PIDTP | No                    | Yes                         |                       |

| CGA**      | Offered as QML            | Yes                   | Yes                         |                       |

| CGA*       | CGA specific PIDTP        | Yes                   | Yes                         | same for both classes |

| Flip-chip* | Flip-chip specific PIDTP  | Yes                   | Yes                         | same for both classes |

| Passives*  | 38535 Para 3.15           | applies               | applies                     | same for both classes |

| Passives*  | Any updates for BME       | would apply           | would apply                 | same for both classes |

#### Observations

- \* represents an issue which is common to both classes (V and Y)

- \*\* highlights the fact that CGA devices are currently offered as QMLV.

- Despite limited resources in working this task, a meaningful QML Y product must be delivered to the flight projects in a timely manner. While the common issues are being worked, we should be able to update MIL-PRF-38535 to include Class Y requirements. This would enable the manufacturers and DLA-VQ to gear up for Class Y audits, an activity that can start now and continue in parallel with resolution of common issues, thus saving time.

#### Recommendations

- DLA-VA to update 38535 with Class Y requirements and release it (keeping the requirements for common issues the same as they exist today for QMLV). DLA-VQ to begin preparation for auditing Class Y suppliers.

- Keep working the common issues as quickly as possible. Continue to update the MIL documents as conclusions are reached on these issues.

PIDTP = Package Integrity Demonstration Test Plan

CGA = column-grid array BME = base metal electrode

## Closure of QML-Y (and related) Activities

Time T (October 2012) DLA-VA Effort: Completed EP Study. Working on initial draft of 38535 (Rev. K) to add Class Y, etc. DLA **DLA-VQ Effort** JC13.2 Electronic Parameters & B.I. (Request priority for FPGAs, ASICs) JC13.2 Flip-chip Package BGA / CGA Requirements (CGA items) G12 & G11 Passives Device Requirements in 38535 (BMEs) Task Groups G12 Plastics Subcommittee (CSAM) JC13.2 5004/5 vs. 38535 Tables & 883 vs. 38535 Comparison J13 Overlapping Device Definitions 38534 vs. 38535 Aeroflex (Completed October 2011) Manufactures' Xilinx (Completed February 2012) **PIDTP** Honeywell (Completed May 2012) Class Y Data Presentations BAE (Completed October 2012) e2v (Scheduled for January 2013) Non-Hermetic Packaging Technology Conference held Jan. 2012 Conferences Components for Military & Space Fronics (CMSE) held Feb. 2012

# NEPAG

#### The Team

#### The **Team members** are:

- Muhammad Akbar, DLA-VA

- Larry Harzstark, Aerospace

- David Sunderland, Boeing

- Shri Agarwal, NASA/JPL

- Roger Carlson, NASA/JPL

#### **Team resources** include:

- Mike Sampson, NASA/GSFC

- Mark Porter, G12

- Brent Rhoton, JC13

- Anduin Touw, G12

- Mike Adams, DLA-VQ

- Rob Heber, DLA-VA

- Tom Hess, DLA-VA

- Charles Saffle, DLA-VA

#### **Section Y**

## G12 Task Group 10-01 (Class Y)

**Summary**

#### **G12 Class Y Task Group Summary**

- G12 Task Group formed in Jan. 2010 to develop screening/qualification requirements for non-hermetics for Space (TG2010-01).

- The TG's work so far may be summarized as follows:

- Each of the meetings was well attended

- As soon as the TG was formed, users were enthusiastic and eager to know when they could procure QML-Y flight parts. See slide 8 on roadmap to procurement.

- A questionnaire was sent to a targeted group of users, manufacturers, and others

(There are about 150 names on the Class Y distribution list). The major inputs were:

- ➤ Class Y should cover those items that are ceramic flip-chip non-hermetic construction that passed the requirements of MIL-PRF-38535, Appendix B. The broader issue of organic-based substrates would be addressed in the next phase.

- ➤ Some respondents asked why the space community should even allow use of non-hermetic parts. (Although the feasibility of a hermetic ceramic package with under-fill flip-chip die has been demonstrated, there are concerns with cost, sealing process, board level, etc. There are no current development programs as there is no user interest.)

- ➤ Added the word "hermetic" to the definitions of QML-Q and QML-V classes in MIL-PRF-38535. (Done)

#### **G12 Class Y Task Group Summary (Contd.)**

- TG meetings summary (cont'd):

- Boeing proposed "simplified approach" was adopted:

- ➤ Add paragraph to existing 38535 Appendix B stating differences for class Y (most remains same as Class V). One key element is for the manufacturers to submit a Package Integrity Demonstration Test Plan (PIDTP) to Qualifying Activity (QA) for approval. This plan must address issues unique to non-hermetic construction and materials, such as potential materials degradation, interconnect reliability, thermal management, resistance to processing stresses, thermo-mechanical stresses, & shelf life. The PIDTP plan shall be approved by QA after consultation with the space community.

- > Separate issues related to non-hermeticity from those related to solder terminations (see below).

- Provide markups to other affected documents.

- 10 manufacturers so far have expressed interest in offering Class Y products (Xilinx, Actel, Intersil, Aeroflex, BAE, Honeywell, TI, e2v, 3D Plus, & Cypress).

- Government customers and contractors have provided statements of support.

- DLA Land and Maritime VA (M. Akbar) was added to the team.

- Comment from G12 management: The group may be surprised at how quickly this is moving. Usually, documents take longer than a year to get a full draft. You are far ahead of schedule. People just may not realize that Class Y is out of the conceptual stage and into the writing stage.

## **G12 Class Y Task Group Summary (Contd)**

- The Team requested G12 approval for DLA VA to conduct an Engineering Practice (EP) study using the detailed requirement input the Task Group has developed. This request was approved by G12.

- The Team's request for clear approval of the Task Group charter was also approved by G12. The charter statement reads:

- "This task group will develop requirements, including qualification and screening standards, for non-hermetic, ceramic-based microcircuits suitable for space applications. Initial effort will be focused on support for devices using flip-chip ceramic column grid array packaging, with resulting requirements to be submitted as a proposal for consideration to DLA Land and Maritime."

- At the October 2012 TG meeting held in Columbus, Ohio, the group voted to go with option 1 recommendation which was:

- DLA-VA to update 38535 with Class Y requirements and release it (keeping the requirements for common issues the same as they exist today for QMLV). DLA-VQ to prepare auditing Class Y suppliers.

- Keep working the common issues as quickly as possible. Continue to update the MIL documents as conclusions are reached on these issues.

# Class Y—Infusion of New Technology into QML System Picked Option 1 at Oct. 1, 2012 meeting

Class Y Current status:

DLA-VA EP study—done

(G12 deliverable)

DLA-VA coordination

meeting—done

(Add'l deliverable to G12)

#### **Common Issues**

Base Metal Electrodes Column Grid Array Flip-Chip Burn-in

DLA-VA to issue

38535 K draft with

Class Y requirements

using common tables

for screening / QCI

(Deliverable to G12)

DLA-VQ and manufacturers to use K draft to prepare for Class Y audits (Deliverable to G12)

**Option 1:** Begin two parallel activities to save time.

**Option 2:** Stop any further activity until common issues are resolved.

# Infusion of New Technology into the QML system Roadmap to QML-Y Flight Parts Procurement

- Major Milestones:

- ☑ G12 approval of TG charter

- ☑ G-12 Class Y Task Group to develop requirements

- ☑ G12 approval for DLA-VA to commence EP study

- ☑ DLA-VA to conduct EP study

- ☑ DLA-VA to release "final" report

- ☑ Coordination meeting at DLA Land and Maritime (April 2012)

- ☑ DLA-VA to update 38535 with Class Y requirements and release the draft version (rev. K) for comments

- ☑ DLA-VQ to begin preparation for auditing Class Y suppliers

- ☐ 38535, rev. K Coordination meeting

- □ DLA-VA to date 38535, rev. K

- □ DLA-VQ to commence audit of suppliers to Class Y requirements

- After milestones completed,

Users to procure QML-Y flight parts from certified/qualified suppliers

## CLASS Y - Package Integrity Demonstration Test Plan (Class Y - PIDTP) Data Sharing with the Space Community

- Presentations by Major Suppliers:

- ☑ Aeroflex (Presented at the Class Y TG meeting in October 2011)

- ☑ Xilinx (Presented at the TG meeting in February 2012)

- ☑ Honeywell (Presented at the TG meeting in May 2012)

- ☑ BAE (Presented at the TG meeting in October 2012)

- ☑ e2v (Presented at the TG meeting in January 2013)

- □ TBD

#### **Recent Picture from NASA's Curiosity on Mars**

#### **Layered Martian Outcrop "Shaler" in "Glenelg Area"**

The NASA Mars rover Curiosity used its Mast Camera (Mastcam) during the mission's 120th Martian day, or sol (Dec. 7, 2012), to record this view of a rock outcrop informally named "Shaler."