# Current state and future trends of PCBs in AVIO

May 20, 2014

Nippon Avionics Co., Ltd.

5th electronic materials, processes and packaging

for space workshop (EMPPS)

20 - 22 may 2014, esa-estec, the netherlands

European Space Agency

1. Printed Circuit Boards qualified by JAXA 2.PCBs Road Map 3.PCBs for area array packages 3.1 High density via pitch 3.2 Fine pattern layout 3.3 Qualification Test 3.4 Specification 4. PCBs for high speed digital signal 5.Summary

- Nippon Avionics Co.,Ltd. (AVIO) was established in 1960 between NEC and Hughes aircraft company.

- PCB division was licensed in multilayer board technology by Hughes.

- AVIO's PCBs were certified by JAXA in 1972, and we have been supplying PCBs for Japanese space programs more than 40 years.

JAXA : Japan Aerospace Exploration Agency

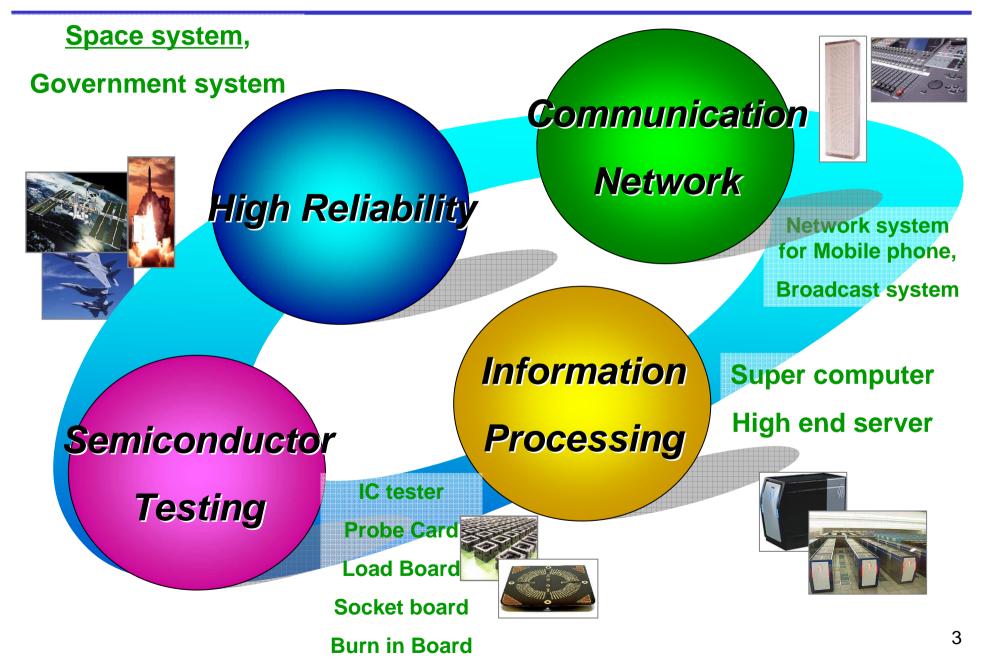

### **AVIOs PCB products**

## 1. Printed Circuit Boards qualified by JAXA

## AVIO have JAXA-qualified PCBs according to JAXA-QTS-2140 (generic specification)

| JAXA-QTS-2140 |                                                                                                                     | Printed Wiring Boards, General Specification For                                                                                                                                             |  |

|---------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|               | ſ                                                                                                                   |                                                                                                                                                                                              |  |

| Appendix A    | PRINTED WIRING BOARDS, GLASS BASE WOVEN POLYIMIDE RESIN OR<br>GLASS BASE WOVEN EPOXY RESIN BASE MATERIAL            |                                                                                                                                                                                              |  |

| Appendix B    | FINE PITCH PRINTED WIRING BOARDS, GLASS BASE WOVEN POLYIMIDE<br>RESIN OR GLASS BASE WOVEN EPOXY RESIN BASE MATERIAL |                                                                                                                                                                                              |  |

| Appendix D    | PRINTED WIRING BOARDS, FLEXIBLE, POLYIMIDE FILM BASE MATERIAL                                                       |                                                                                                                                                                                              |  |

| Appendix E    | RIGID-FLEX PRINTED WIRING BOARDS                                                                                    |                                                                                                                                                                                              |  |

| Appendix F    | PRINTED WIRING BOARDS, CIC*1 CONTROLLED THERMAL EXPANSION,<br>GLASS BASE WOVEN POLYIMIDE RESIN BASE MATERIAL        |                                                                                                                                                                                              |  |

| Appendix G    |                                                                                                                     | PRINTED WIRING BOARDS, <b>AREA ARRAY PACKAGING</b><br>CAPABLE (Qualified January 2014)                                                                                                       |  |

| (Appendix H)  |                                                                                                                     | PRINTED WIRING BOARDS, HIGH SPEED DIGITAL SIGNAL<br>Under Qualification Test)                                                                                                                |  |

|               | Appendix A<br>Appendix B<br>Appendix D<br>Appendix E<br>Appendix F<br>Appendix G                                    | Appendix APRINTE<br>GLASSAppendix BFINE PI<br>RESIN CAppendix DPRINTEAppendix ERIGID-FAppendix FPRINTE<br>GLASSAppendix FPRINTE<br>GLASSAppendix GPRINTE<br>CAPAE(Appendix H)PRINTE<br>CAPAE |  |

\*1 CIC : Copper-Inver-Copper

JAXA-QTS-2140 can be soon available from : https://eeepitnl.tksc.jaxa.jp/en/qts\_list

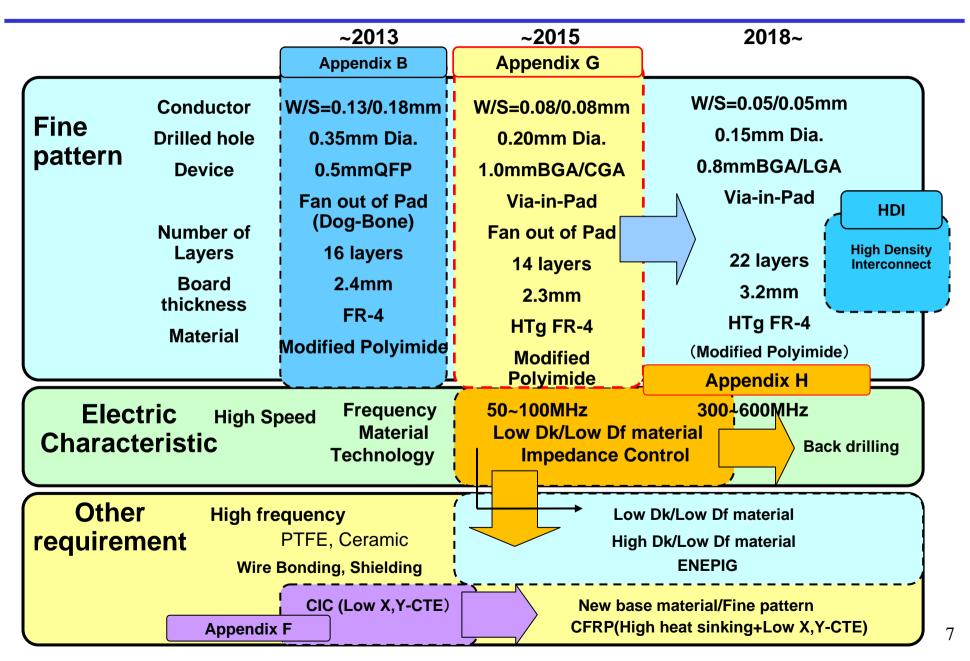

## 2. PCBs Road Map

#### 2. PCBs Road Map

## **3.PCBs for AREA ARRAY PACKAGING**

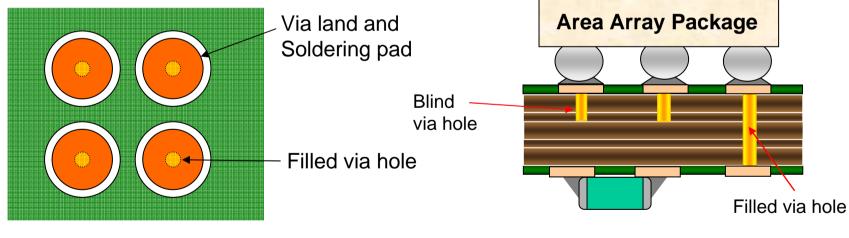

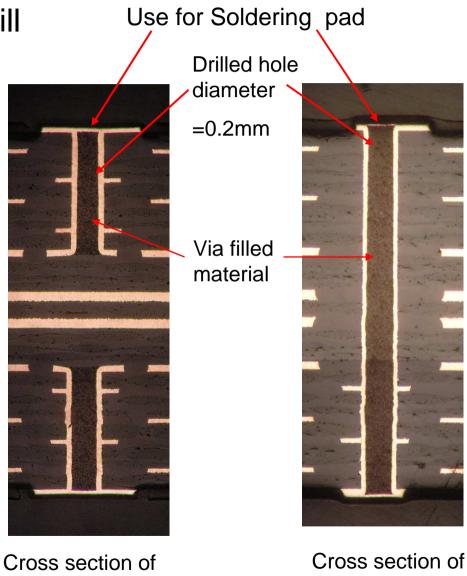

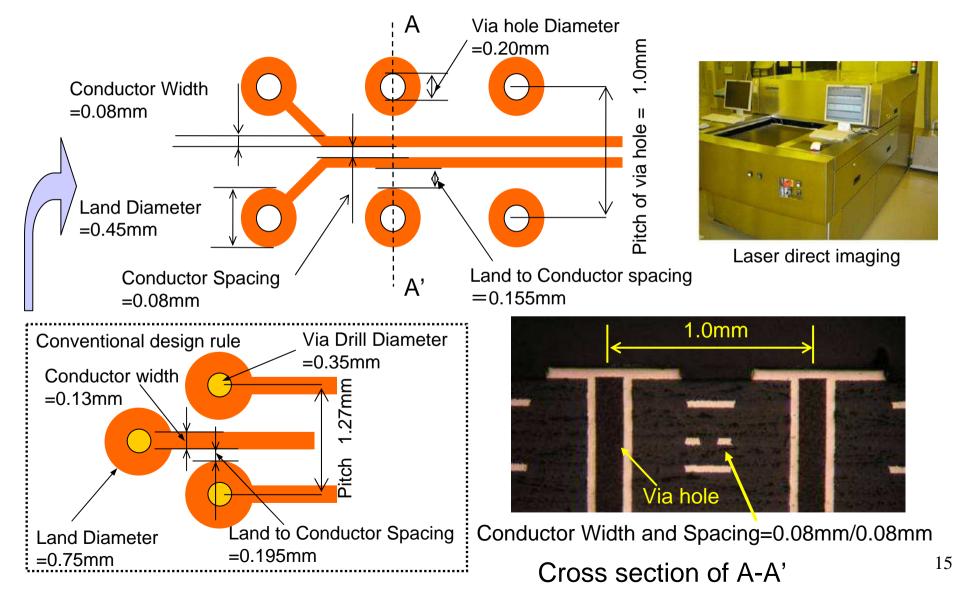

#### Target of Area Array Package to be mounted on PCB Ceramic BGA/CGA for space use •1.0mm pitch Approximately 2000 pins **Key Technologies of PCBs** ✓ High density via pitch Cross section image of Area Array Via-in-Pad (VIP) structure and Via fill Package and Printed Wiring Board ✓ Fine pattern **Conductor Width and Spacing** 0.08mm/0.08mm

Via-in-Pad structure and Via fill

- Via-in-Pad structure gives more flexibility to soldering pads design than Fan out pads structure.

- Via-in-Pad structure perform fine pitch area array pads with conventional high reliable PTH.

Top view of Via-in-Pad structure

Cross section of Via-in-Pad structure

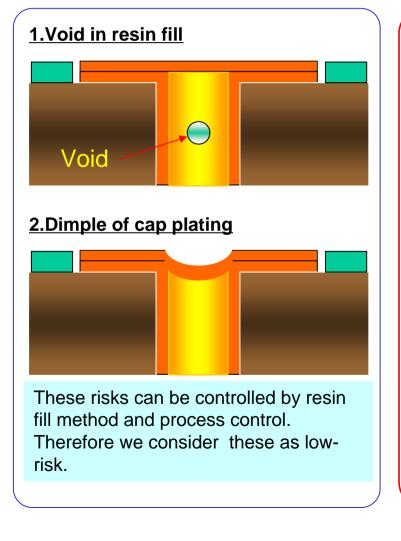

#### Issues of VIP

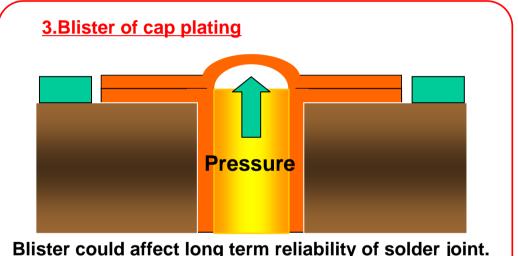

In general, Via in Pad structure has three issues as follows. We consider that blister of cap plating is the rested issue of all. Therefore we evaluated the blister.

Mechanism of blister occurrence

1.In soldering, cap plating receives the pressure from filled resin expanded in plated through hole.

2.Cap plating deforms beyond plastic deformation limit.

3. Then by cooling, filled resin returns to the original form, but cap plating can not return.

Blister rely on cap plating thickness and via hole (drill) diameter. We should be consideration for the optimum conditions for space use.

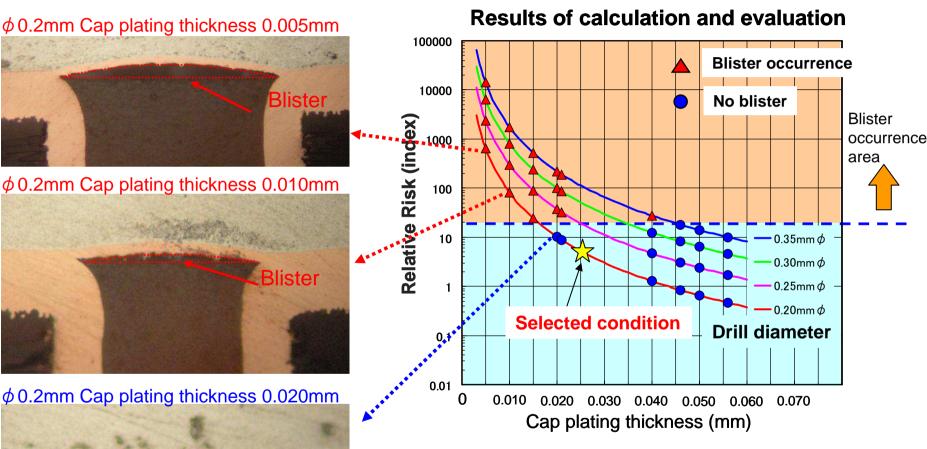

#### Evaluation

We considered the cap plating section as picture below. Then we calculated the risk of blister occurrence as deflection volume for drill diameter and cap plating thickness shown in the table. Next we made sample board and evaluated the actual blister of cap plating by thermal stress test. We compared calculation and evaluation.

Uniformly distributed load: P

#### Young's modulus : E Poisson's ratio : 1/m

#### Condition of blister evaluation

| Drill diameter        | φ 0.20, 0.25, 0.30, 0.35mm                               |  |  |

|-----------------------|----------------------------------------------------------|--|--|

| Cap plating thickness | 0.005, 0.010, 0.015, 0.020, 0.040, 0.045, 0.050, 0.055mm |  |  |

| Board thickness       | 2.4mm                                                    |  |  |

| Test condition        | Thermal stress test (Solder float)                       |  |  |

|                       | Temperature=288°C, Time=10seconds, Operation=3times      |  |  |

| Evaluation method     | Observation of cross section by microscope               |  |  |

| Requirement           | No blister                                               |  |  |

#### Sesa 5th EMPPS workshop 3.1 High density via pitch-4

#### Result of Evaluation

We obtained risk curve and blister occurrence for each drill diameter and cap plating thickness.

We find that blister occurrence risk decreases by using small drill diameter and thick cap plating from above chart. We selected condition of Via in pad structure with margin. Dill diameter= $\phi$  0.20mm,

Cap plating thickness=0.025mm(nominal)

#### Via-in-Pad structure and Via fill

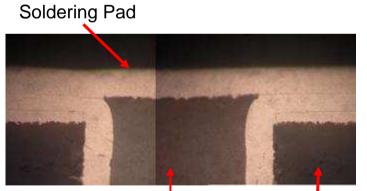

Soldering Pads need flatness of surface without void in solder or other soldering problem. We solved this issue by vacuum via filled technology.

Via filled material

Base material

**Blind Via Holes**

Magnifying of Via-in-Pad

#### Design for 1.0mm pitch via hole and two signal lines.

We passed the Qualification Test under JAXA-QTS-2140 Appendix G.

The main items of QT are as follows;

| Item                                                        | Requirements                                                                             | Result |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------|--------|

| Thermal cycling                                             | -30 to +125 deg.C, 1,000 cycles<br>(Preconditioning : 240 deg.C, max. reflow<br>3 times) | pass   |

| Solder bath float                                           | 288 deg.C, 10 seconds                                                                    | pass   |

| Hot oil dip Resistance                                      | 260deg.C, 10seconds, 10 cycles                                                           | pass   |

| Humidity and<br>Insulation Resistance                       | 25 to 65deg.C, 90~98%RH, less than<br>500M ohm                                           | pass   |

| Dielectric Withstanding<br>Voltage                          | 500Vdc, 30 seconds                                                                       | pass   |

| Radiation Hardness 1X10 <sup>4</sup> Gy, less than 500M ohm |                                                                                          | pass   |

#### Table: Specification JAXA-QTS-2140 Appendix G.

| Item                    |                       | Specification      |            |

|-------------------------|-----------------------|--------------------|------------|

| Pad                     | Pitch                 | 1.0mm              |            |

|                         | Structure             | Fan out of Pad     | Via-in-Pad |

| Drilled hole diameter   |                       | 0.20mmDia.         |            |

| Conductor<br>(External) | Width                 | 0.10mm             |            |

|                         | Spacing               | 0.15mm             |            |

| Conductor               | Width                 | 0.08mm             |            |

| (Internal)              | Spacing               | 0.08mm             |            |

| Number of Layers        | Total                 | 14                 |            |

|                         | Blind via             | 6                  |            |

| Board thickness         | Modified<br>Polyimide | 2.1mm              |            |

|                         | HTgFR-4               | 2.3mm              |            |

| Surface finish          |                       | HASL*(SnPb solder) |            |

|                         |                       |                    |            |

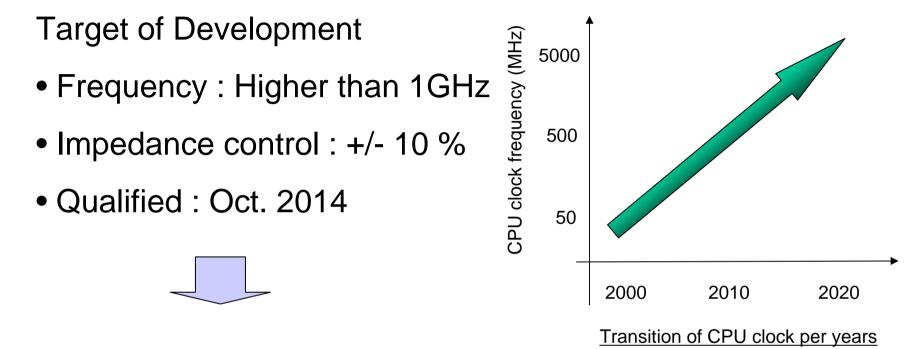

## 4.PCBs for High Speed digital signal

**Elemental Technologies**

- ✓ Processing technology for low dielectric constant material

- ✓ High accuracy conductor width control

by thin conductor thickness and large number of layers

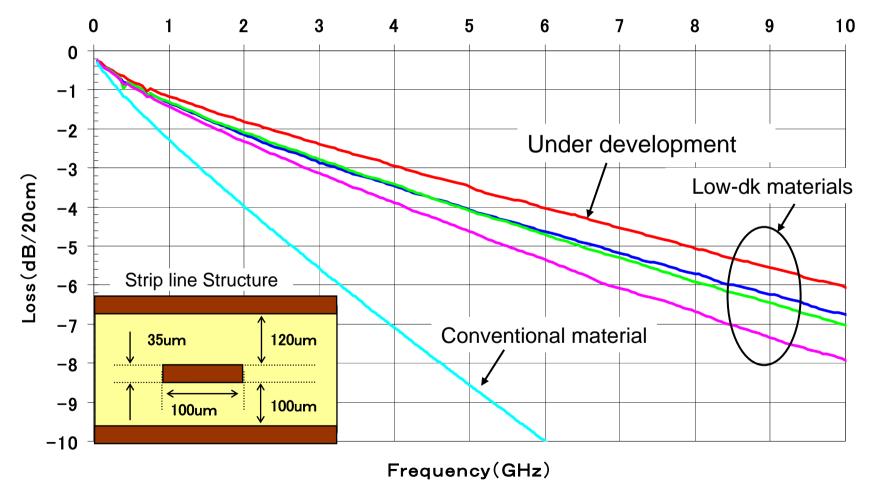

We evaluated signal loss of 4 types Low dielectric constant (Low-dk) materials and conventional material. We selected the material with best result.

Measuring instrument : Network analyzer E8363B Agilent technologies inc

High accuracy conductor width control for characteristic impedance control by thin conductor thickness, low profile copper foil, and large number of layers.

#### Cesa 5th EMPPS workshop 4. PCBs for high speed digital signal

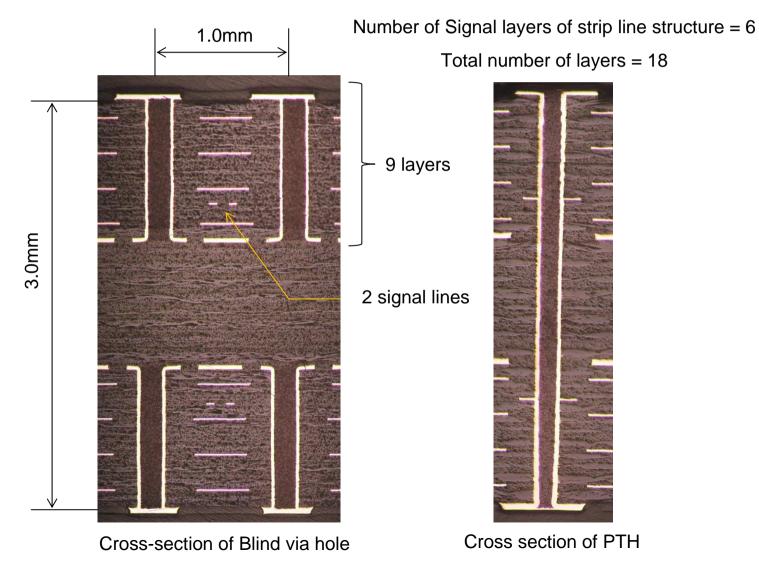

| Specification         |                      |                   |            |  |  |

|-----------------------|----------------------|-------------------|------------|--|--|

| Item                  |                      | Specification     |            |  |  |

| Base<br>Material      | Dk (εr) (1GHz)       | 3.65              |            |  |  |

|                       | Df (tan δ)<br>(1GHz) | 0.002             |            |  |  |

| Pad                   | Pitch                | 1.0mm             |            |  |  |

|                       | Structure            | Fan out of Pad    | Via-in-Pad |  |  |

| Drilled hole diameter |                      | 0.20mmDia.        |            |  |  |

| Conductor             | Width                | 0.12mm            |            |  |  |

| (External)            | Spacing              | 0.14mm            |            |  |  |

| Conductor             | Width                | 0.07mm            |            |  |  |

| (Internal)            | Spacing              | 0.08mm            |            |  |  |

|                       | Thickness            | 0.018mm           |            |  |  |

| Number of Layers      | Total                | 18                |            |  |  |

|                       | Blind via            | 9                 |            |  |  |

| Board thickness       |                      | 3.0mm             |            |  |  |

| Surface finish        |                      | HASL(SnPb solder) |            |  |  |

## 5. Summary

•Needs to Printed Circuit Boards for space use are to respond to the high performance and down sizing of electronic components.

-We were qualified capable PCBs that be 1.0mm pitch and 14 layers for high pin counts BGA/CGAs.

-We are developing PCBs for high speed digital signal with Low-Dk. (We will finish in September 2014)

## Thank you for your attention.

#### **Point of Contact**

ENGINEER : Shunji Sano Engineering department E-mail: sano-syunji@avio.co.jp Tel : 81-55-284-2495 Fax : 81-55-284-1703

SALES : Shin-ichi Uenomachi Fuchu Branch Multi-Layered Boards Division E-mail: uenomachi-shi@avio.co.jp Tel : 81-42-334-1700 Fax : 81-42-334-1703

Mt. Fuji was registered as a world cultural heritage in 2013.

http://www.avio.co.jp/products/mlb/index.htm