**ESCCON 2016**

### FIRST TELECOM APPLICATION OF DIGITAL **COMPONENT DEVELOPMENTS:** 65NM ASIC AND DATA CONVERTERS

F. MALOU, C. AMIOT-BAZILE (CNES), P. VOISIN (TAS)

1st March, 2015

1

Cones

- FAST project overview : TAS Digital Transparent Processor (DTP)

- ${\mbox{\sc DTP}}$  Key technologies :

- ATMEL-ST-E2V 65nm ASIC

- E2V High speed Data Converters

- $\sim$  Conclusion

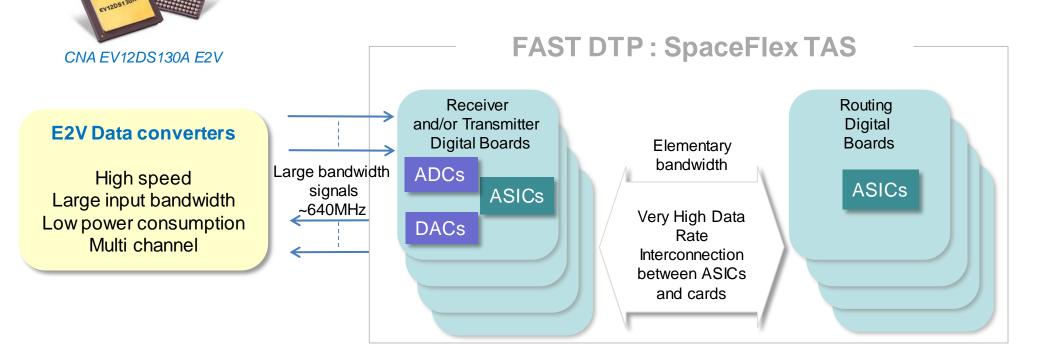

### **FAST DTP : TAS SPACEFLEX**

SpaceFlex Processor is a complete product offer from ground interface to space segment and fully scalable from SpaceFlex 2 [2 GHz] up to SpaceFlex 74 [74 GHz]

### **COMSAT NG**

#### COMSAT NG Program

Cnes

- New generation of defense telecommunications satellites

- Renewal of in-orbit Syracuse 3 capabilities

- Two satellites, first satellite in orbit in 2020

- C Dual pre-developments

- Under CNES responsibility

- Programs :

- FAST : KO in 2012

- C TELEMAK : KO in 2015

## A new generation Digital Transparent Processor is necessary for COMSAT NG program

**Dual Developments in progress at Thales Alenia Space**

### **DTP : Key technologies**

ATMEL-ST 65nm space ASIC ATMEL-E2V Hermetic Flip-chip assembly High integration Low power consumption/Mbps HSSL IP

VT65 ASIC ATMEL-ST-TAS-CNES

Other disruptive technologies

Connectors PCB DCDC,...

### Commercial Telecom Market Evolution

#### Evolution of telecoms services

- Very High Definition TV

- Very High Throughput Internet

- Mobility

- Machine to Machine

- TV/Web and fixe/mobile convergence

**Demand for data rates increase**

**Demand for Quality of Service enhancement**

- Availability

- Latency

### Impact on commercial payloads

#### C Fractioned coverage and multispot

Example of single beam coverage - W6

Example of multi-beam coverage - Kasat

- Increased needs for on-board connectivity

- Increased needs for flexibility

Digital Transparent Processor (DTP) is a key technology in the core of telecommunications commercial payload roadmap

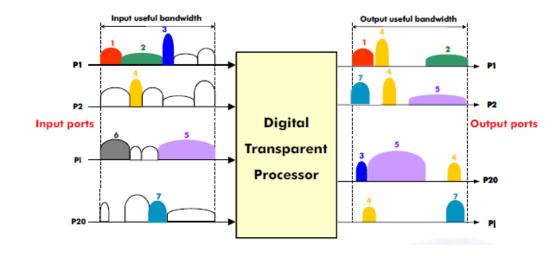

# DTP in the core of telecommunications payloads

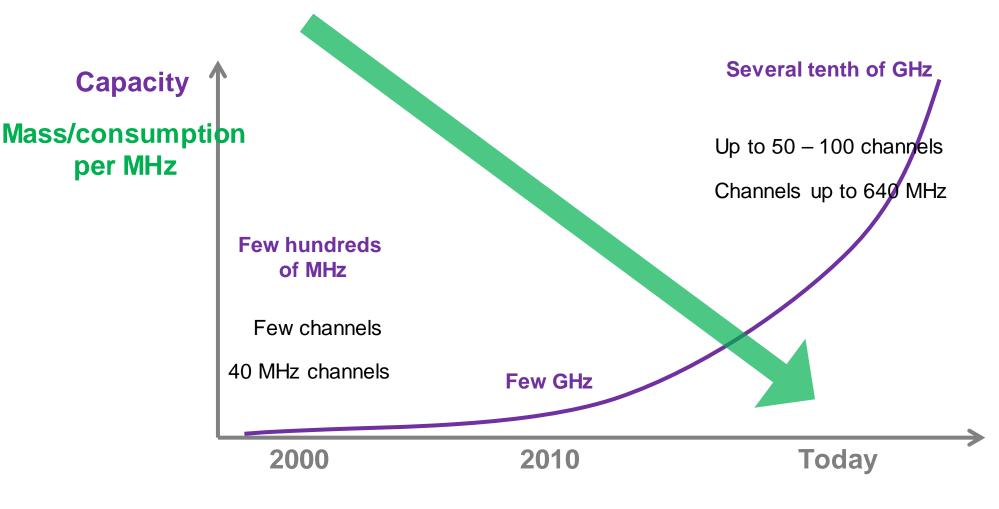

- C Technological trends and needs

- Ability to sample and digitally on-board process data flows with increasing data rates

- With costs decreases in mass/consumption per GHz

- C With functionalities of

- Full connectivity between

↑ and ↓ beams

- Flexible channelization

- Flexible frequency positioning between (sub-) channels

- Gain control

- Beam forming capability

Cnes

**DTP Evolution**

~20 gain factor in mass per MHz ~10 gain factor in consumption per MHz

### 65NM ASIC

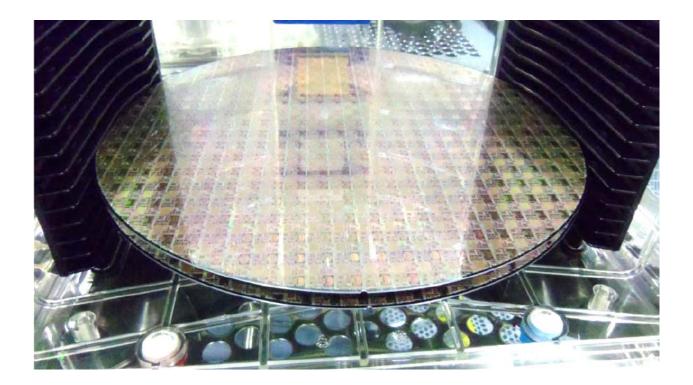

65nm wafer from ST

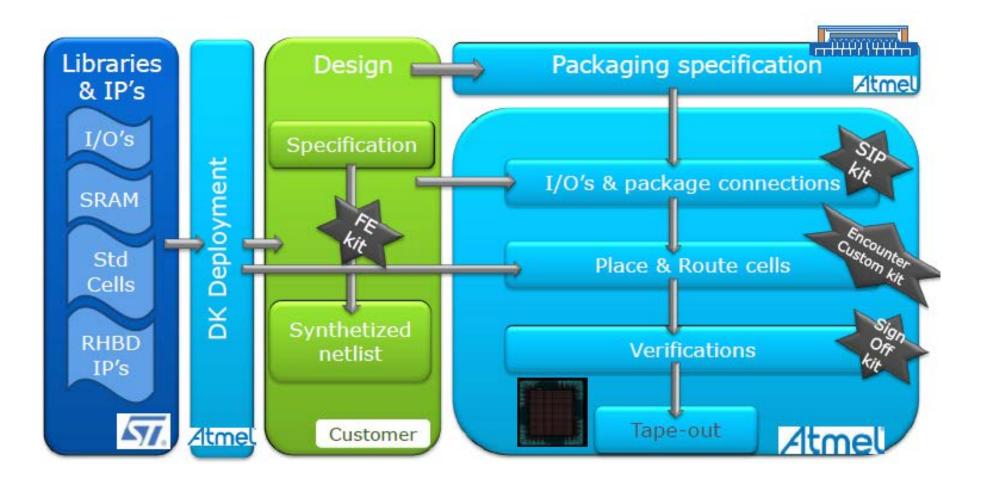

### **ATMEL AT65RHA ASIC offer**

- In the frame of ESA and CNES supported activities, ST has developed the C65SPACE, a radiation hardened standard cell library for space, based on the 65 nm bulk process, produced in their fab in Crolles (F).

- 65nm supply chain proposed in 2010 by ST has been selected in 2012 by FAST project

- The C65SPACE platform is supplied by ATMEL with space qualification support, HSSL and Flip-Chip under the AT65RHA name.

For FAST DTP ATMEL is the supplier of 65nm ASICs which are based on ST process and e2V packaging

### **AT65RHA** features

- $\sim$  65 nm technology

- >100 usable Mgates equivalent nand2

- Hardening-by-Design

- C Designed In Reliability

#### Key Features

Process 7 copper metallization with 5 thin and 2 thick Compatible with flip-chip and wire bonding <u>Radiation</u> No SEL - up to LET=60Mev/mg/cm2 @ 125C & Vdd=1.3V <u>Reliability</u> Mission profile: 20 years at 110C @ Vdd = 1.3V

- $\subset$  Supply voltages: 1.2V for core, 1.8V, 2.5V & 3.3V for periphery

- Very low operating consumption < 0.5 nW/gate.MHz at 20% activity (target)</p>

- Maximum toggle frequency : 30 GHz

- Compiled ROM, SRAM & DPRAM memory

- LVDS (655 Mps)

- $\subset$  PLL 6 phases 100MHz input / 1.2GHz output

- **HSSL up to 6.25Gbps**

C Typical signal I/O's > 1000 – Hermetic Flip-Chip technology

Disruptive technology Key performances for DTP cnes

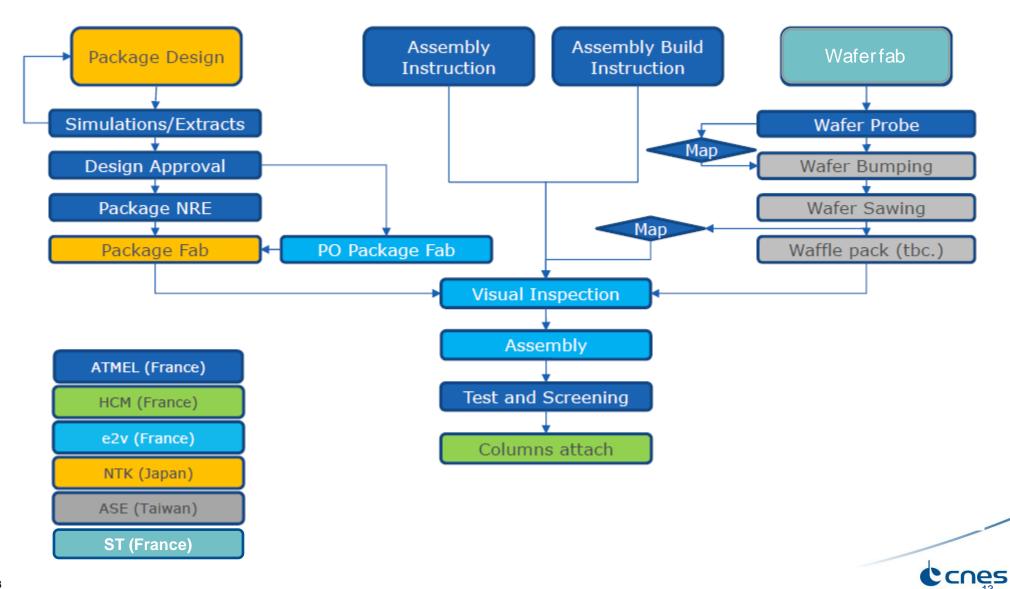

### **AT65RHA Supply Chain**

#### **AT65RHA Design flow**

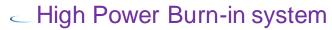

### **ATMEL test capabilities for 65nm ASICs**

- < 300mm wafer Prober

- High performance tester for

Digital and Analog: Xcerra

Sapphire

400 MHz, up to 800 Mbits/sec, 768 digital pins, High accuracy

- Dynamic Burn-In

- Testing capabilities for high-power devices.

- Individual Temperature Control

- Up to 8 different pattern zones with one burn-in board per zone.

Cones cones

15

¢cnes

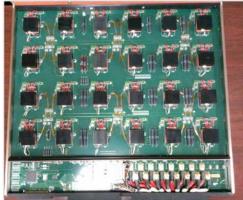

### 1<sup>st</sup> 65nm ASIC : TAS-ATMEL-ST VT65

- ${}_{\frown}$  VT65 ASIC characteristics :

- Working Frequency > 600 MHz

- Technology : AT65RHA

- Core Power supply : 1.2V

- Periphery Power supply : 3.3V and 2.5V

- Package > 1600 IO

- Usefull pins > 500

#### Core Cells summary:

- > 40 Mgates eq.

- > 600 mémoires

- HSSL IP (6.25Gbps)

- PLLs (100MHz input / 1.2GHz output)

- 1 THSENS

- Cold Sparing buffers

- LVDS (655Mps)

- Total transistors > 200 Million

VT65 ASIC die > 200mm<sup>2</sup>

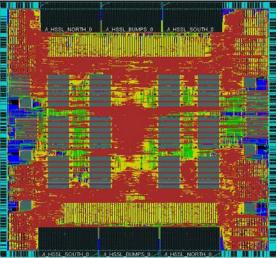

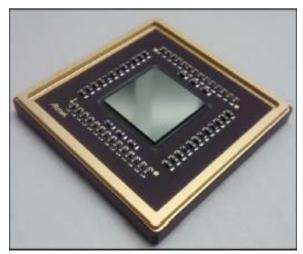

VT65 ASIC in CCGA1752 package

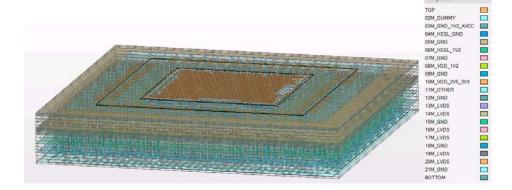

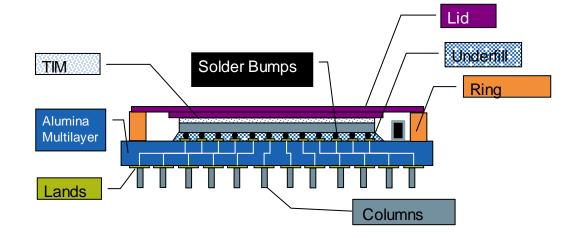

### VT65 ASIC : CCGA1752 Flip-chip package

Laver

Flip-chip package is mandatory :

- Complexity and I/O number

- HSSL link performances

- Hermetic Package

- CCGA1752 (alumina 18 layers)

- Body size: 45x45mm 4.2mm thick

- Design by Atmel, Assembly done by E2V

#### < Die

- Die Size 15.4x15.4mm

- Bumps count: 3814

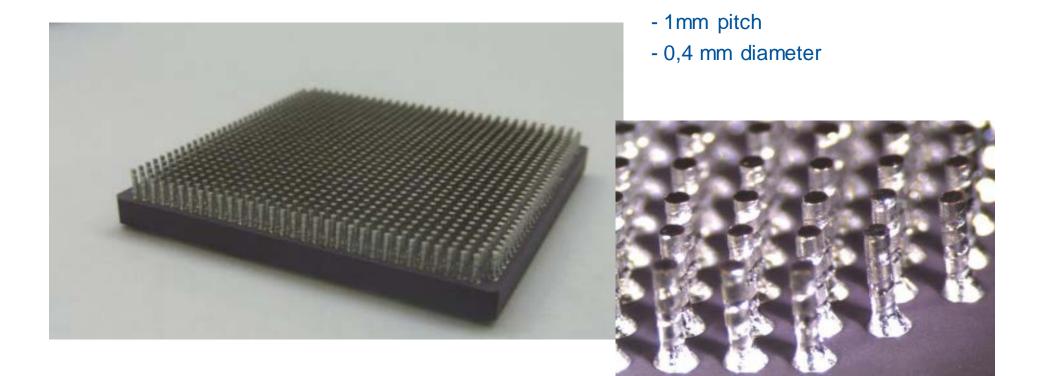

### VT65 CCGA 1752 columns

#### Ceramic Column Grid Array : 85Pb 15Sn columns

#### Mounting of columns array in Europe:

- HCM (F) : ESA ECI3 contract with Atmel/HCM

- Airbus DS (F) : CNES contract

### **DATA CONVERTERS**

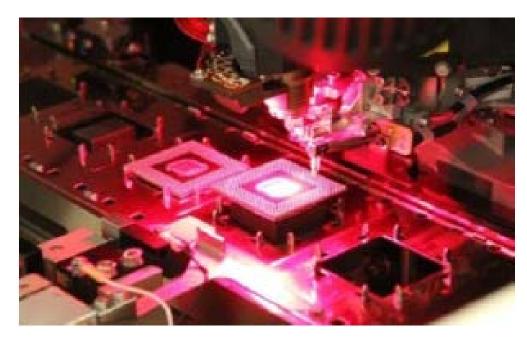

E2V assembly line

#### Cnes

### E2V EV12AD550 ADC

#### C Developement and ESCC evaluation in the frame of CNES and DGA programs

#### ADC Main Features :

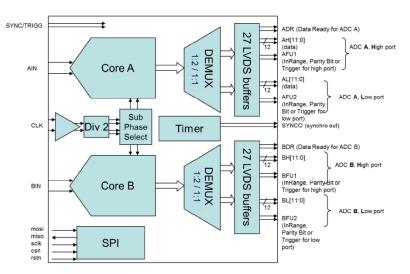

- Dual channel ADC

- 12-bit resolution

- 1.5 Gsps conversion rate

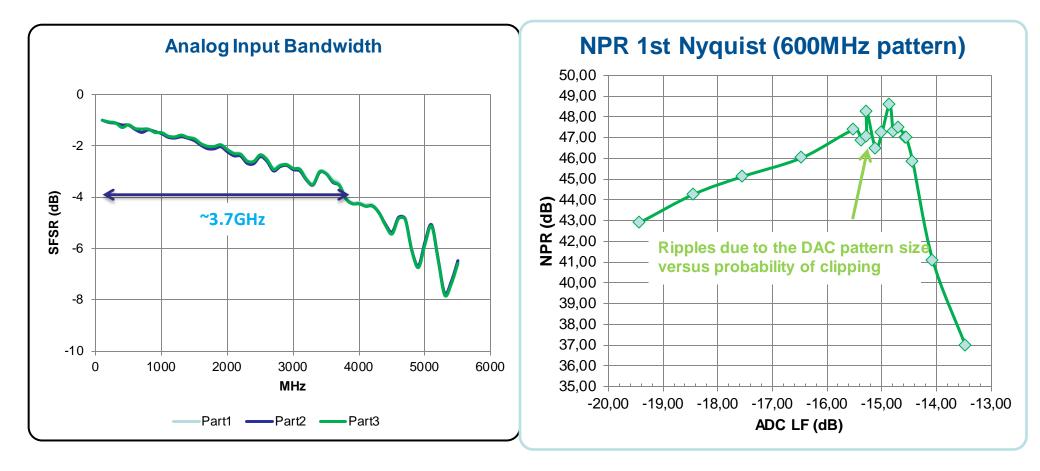

- Large input bandwidth up to ~3,7GHz

- LVDS parallel outputs 1:2-1:1 DEMUX.

- 2.1 W typ in 1:1 DEMUX ratio per core

#### EV12AD550 block diagram

- Flip-chip Hermectic package CCGA323 (AlN 21x21mm, Pitch 1.0mm)

- 130nm BiCMOS from ST (F)

#### **EV12AD550 is under Evaluation**

- Electrical characterization completed

- ESCC evaluation and Radiation test in progress

Large input bandwidth up to ~3,7GHz

NPR ~ 48 dB in 1st Nyq. at -15dB loading factor

Cnes

**EV12AD550 Output Spectrums**

#### Cnes

### E2V EV12DS130A DAC

#### C Development and ESCC evaluation in the frame of CNES program

#### ⊂ DAC Main Features :

- c 12-bit resolution

- GSps Conversion rate

- 6 GHz analog output bandwidth

- 4:1 or 2:1 built in MUX (selectable)

- 1.3 W Power Dissipation

- NRZ, Narrow RTZ, 50% RTZ, RF modes

- UCM mode (Patent e2v/CNES)

- SEL& SEFI free, 110 krads

- Ci-CGA255 Package (21x21mm, pitch 1,27mm)

- B7HF200 SiGeC techno. from Infineon (G)

- \_ 1st Nyquist (NRTZ): NPR = 51.3dB at Fs = 3Gsps

- Ist Nyquist (NRTZ): NPR = 55.7dB at Fs = 1.5Gsps

- $_{\odot}\,$  2nd Nyquist (NRTZ or RTZ): NPR = 44.6 dB at Fs = 3 Gsps

- 3rd Nyquist (RF): NPR = 42.5 dB at Fs = 3 Gsps

#### EV12DS130A is used on Telecom projects

- ESCC evaluation completed since 2012 : very good performances, reliability and radiation results

- QMLV qualified in 2015

- C DTP Key performances :

- 640 MHz digitalized bandwidth

- Many tens of GHz of full capacity

- Cost decreases in Mass/consumption/volume per GHz

#### $\subset$ ASIC Key performances :

- High speed link: 6,25Gbps rad-hard HSSL IP

- High integration with 65nm

ASIC die size up to 400 mm<sup>2</sup>

- > 600 MHz working frequency

- Flip-chip Packaging

- Data converters Key performances:

- High speed >1,5Gsps

- L-band & S-band

- Integration with multi channel

- Low power consumption  $\sim 2W$

- Flip-chip Packaging

#### DTP is a high tech product with high innovation For drastically enhanced performances

Constructive collaboration between all the FAST partners, Telecoms, Technologists, Components engineers and Manufacturers

### **Acknowledgements**

ATMEL : AT65RHA team

ST : C65Space team

E2V : CALLISTO team

TAS : FAST team

**CNES : FAST team**

ESA : L.Hili, L.Murphy

DGA : G.Jestin

### Thank you !

**Contacts:**

Florence.Malou@cnes.fr

Caroline.Amiot-Bazile@cnes.fr

Philippe.Voisin@thalesaleniaspace.com