# ESCCON 2016 Lifetime predictions of Deep Sub-Micron commercial EEE parts for space applications

Dr. Florian MOLIERE florian.moliere@airbus.com

Airbus Group Innovations

+33 1 46 97 30 22

# Lifetime predictions of Deep Sub-Micron commercial EEE parts for a specific application Lifetime assessment by the OEM

## Summary

- 1. Introduction

- 2. Airbus Group Methodology

- 3. Conclusions

#### A. Context

#### 1) Introduction

Airbus Group Methodology

3) Conclusion

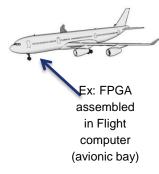

Assets for Airbus Group to use COTS semiconductor technologies into design aeronautic/space designs:

To implement performing functions in electronic equipment

- To remain competitive vs competitors with the integration of low cost components

- To have access to mature process due to the high volume in production

#### Issues with existing and future COTS semiconductor technologies:

Driven by mass market needs (cost, performance, density, power consumption)

Airbus Group does/will not have the definition of COTS semiconductors (long term reliability, various and harsh environments, obsolescence)

#### How to face with:

Aerospace OEMs have to adapt its constraints & requirements

OEMs have to redefine criteria of selection for COTS semiconductor components

#### A. Context

#### Criteria of selection for COTS semiconductor components:

1) Introduction

Airbus Group Methodology

3) Conclusion

- Performance

- Frequency, number of macrocells (FPGA)

- Density (Memories)

- Board requirements:

- Bias voltage

- Number of I/O

- Power Management:

- Power consumption/dissipation (W)

- · Device packaging:

- o Dimensions/type

- Number of pins/balls/pads

- o Flip-chip die?

- o Others...

- RoHS compliance

- Thermal Grade (commercial, industrial, automotive, military, space etc...)

- Availability

- Obsolescence, production life cycle

- o Sourcing, delay....

- Radiation sensitivity

- Latchup

- SEU/MBU/SEFI...

- o TID

- Reliability

- Failure rate in operation

- Cifetime in mission (wearout)

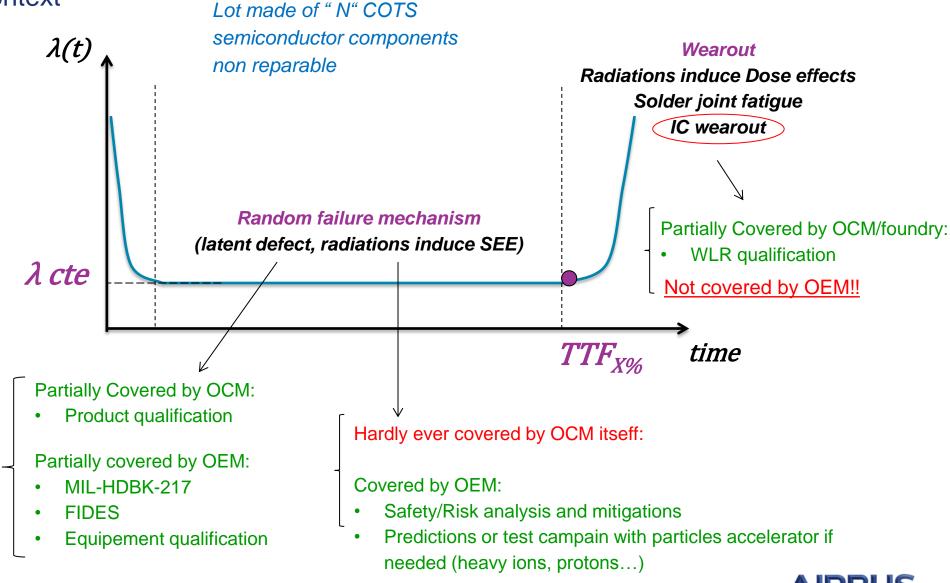

#### A. Context

1) Introduction

Airbus Group Methodology

3) Conclusion

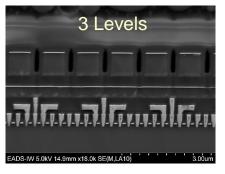

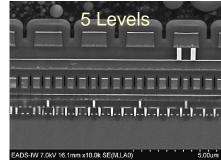

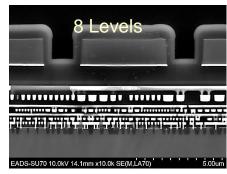

## B. Problematic with COTS semiconductors components

Increase of fonction density:

1) Introduction

2) Airbus Group

Methodology

3) Conclusion

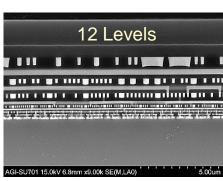

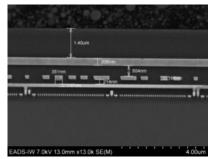

Metallizations 90 nm

Metallizations 65 nm

Metallizations 45 nm

Metallizations 22 nm

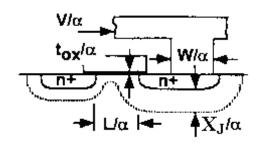

#### Non Homothetic FEOL shrink:

#### 1990 2001. 2004 Year 1992 1995 1999 2007 2009 2011 2012 2014 2016 32 Technologie (nm) 1000 500 350 250 180 130 65 45 28 20 16/14

**Deep Sub Micron**

Increase of electrical field and current leakage vs integration

AIRBUS GROUP

## B. Problematic with COTS semiconductors components

#### Introduction of new material/architecture for Performance/consumption purposes:

1) Introduction

2) Airbus Group Methodology

3) Conclusion

Operating frequency improvement (reduction of RC delay)

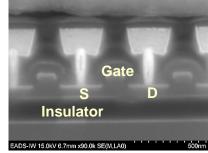

BEOL Copper wires + Low K oxides

Idsat increase (gate capacitance improvement)

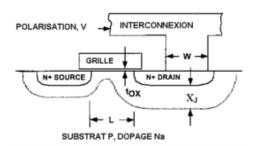

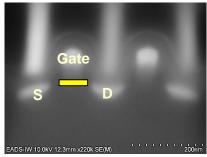

45 nm CMOS SiON transistors

Current consumption improvement (gate leakage), Idsat increase (gate capacitance improvement)

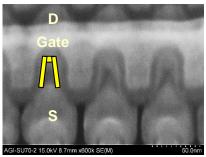

22 nm FinFETs HKMG transistors

#### Frequency switch improvement Drain current leakage reduction

Silicon On Insulator (SOI)

# Frequency switch improvement (carrier mobility improvement)

28nm CMOS Si-Ge transistor

What reliability Impact on HiRel applications ??

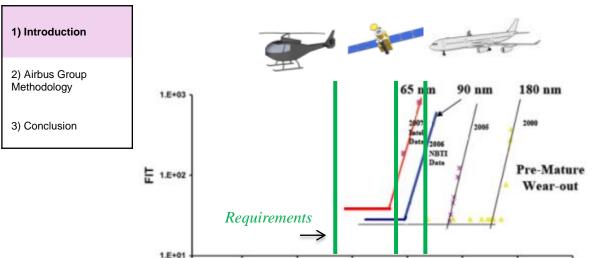

## B. Problematic with COTS semiconductors components

Technical issue: early wearout effects of IC

Time(equivalent hours)

# With COTS semiconductor technologies < 180 nm:

- Increase of failure rate

- Decrease of intrinsic lifetime

#### **Inputs necessary for relevant lifetime assessment:**

- Impact of mission profile (aircraft, equipment)

- Impact of technology (BEOL, FEOL)

- Definition of failure mechanisms (PoF)

#### **Industrial issues:**

[BERNSTEIN 07]

1.E+02

Not easy collaboration with OCM for COTS (proprietary WLR data, fabless strategy, low purchase volume) Wearout effects on COTS semiconductors are not concerned by classical methodologies (MiL HDBK, FIDES...)

Aerospace OEMs must define specific guidance devoted to COTS semiconductors

1.E+07

1.E+06

Airbus Group Methodology AVSI AFE83

#### A. Scope of the methodology

## Lifetime predictions of Deep Sub-Micron commercial EEE parts for a specific application Lifetime assessment by the OEM

|             | Criteria           | Items concerned                                                                                                                                                                      |  |  |  |  |  |  |  |

|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|             | Type of component  | COTS components (ASICs are excluded)                                                                                                                                                 |  |  |  |  |  |  |  |

| Technology  | Component family   | Focus on CMOS digital devices such as µProcessor, FPGA & SRAM and NVM memories, DRAM, Flash)                                                                                         |  |  |  |  |  |  |  |

|             | Node               | Focus on CMOS Deep Sub Micron < 130 nm                                                                                                                                               |  |  |  |  |  |  |  |

|             | Localization       | Integrated circuit (areas BEOL et FEOL)                                                                                                                                              |  |  |  |  |  |  |  |

|             | Nature of failure  | Integrated circuit Wearout failures (Radiation & overstress aspects are excluded)                                                                                                    |  |  |  |  |  |  |  |

| Degradation | Failure mechanisms | Failure mechanisms:  Time Dependent Dielectric Breakdown (FEOL)  Time Dependent Dielectric Breakdown (BEOL)  Bias Temperature Instabilities  Hot Carrier Injection  Electromigration |  |  |  |  |  |  |  |

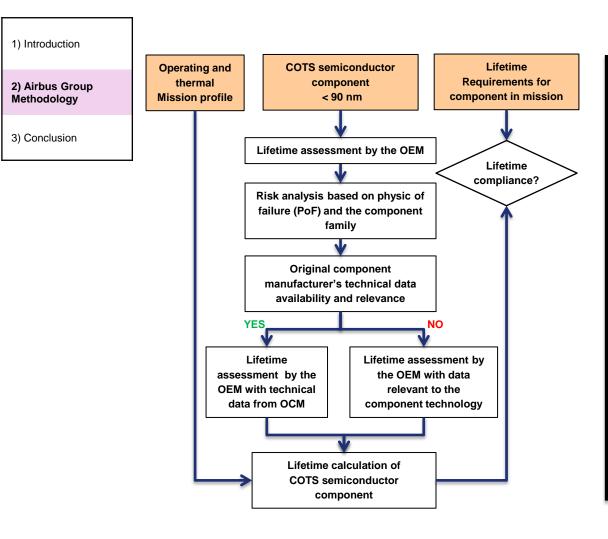

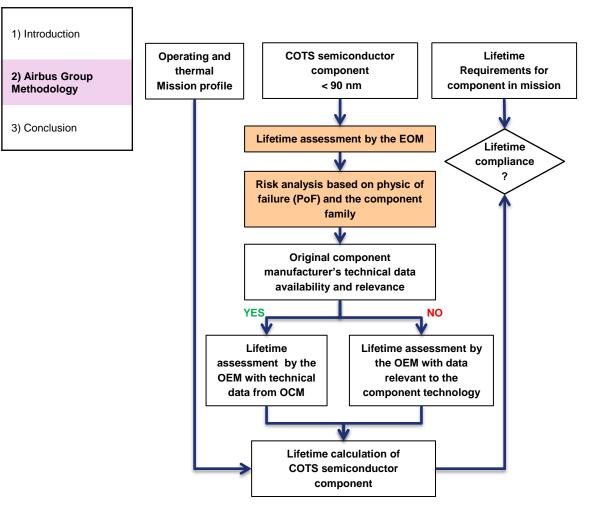

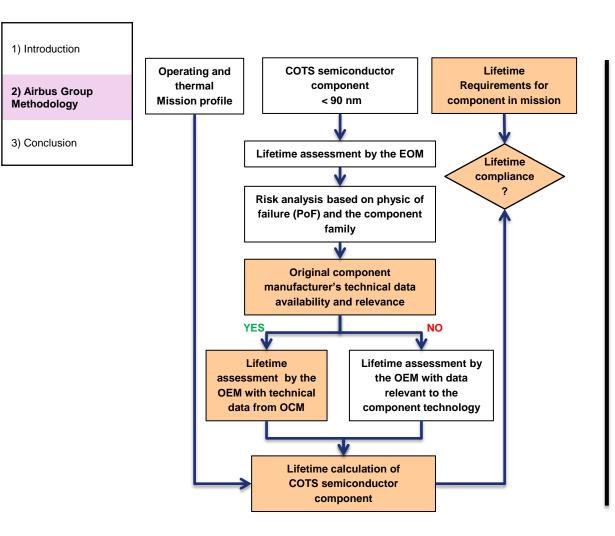

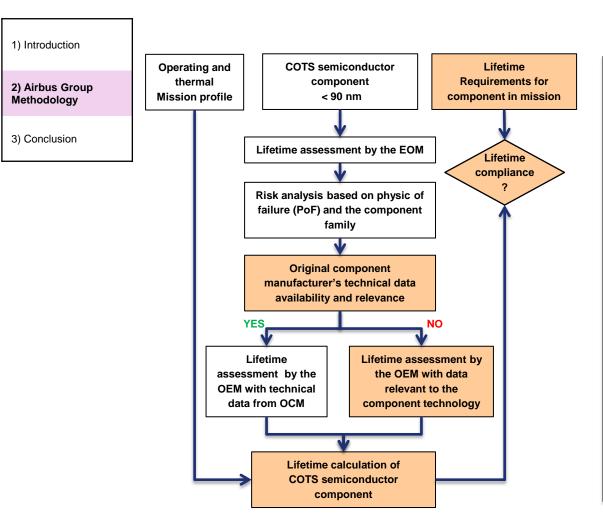

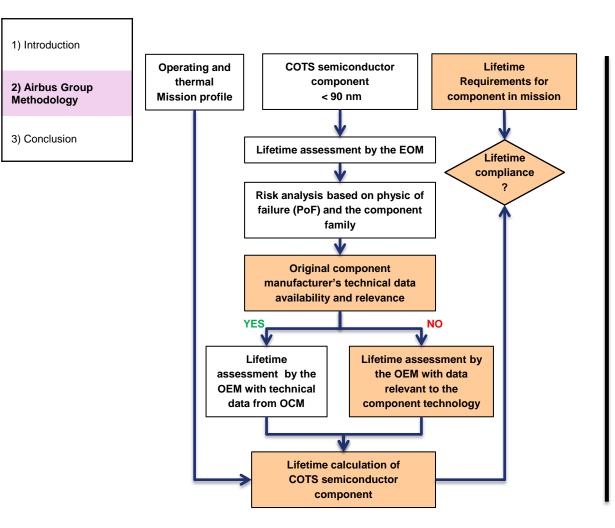

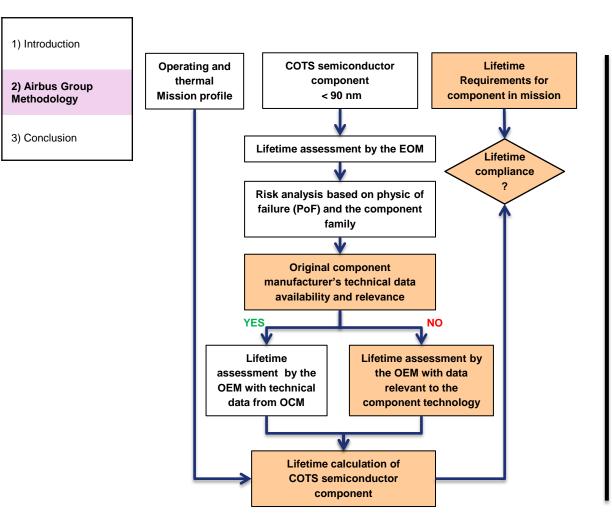

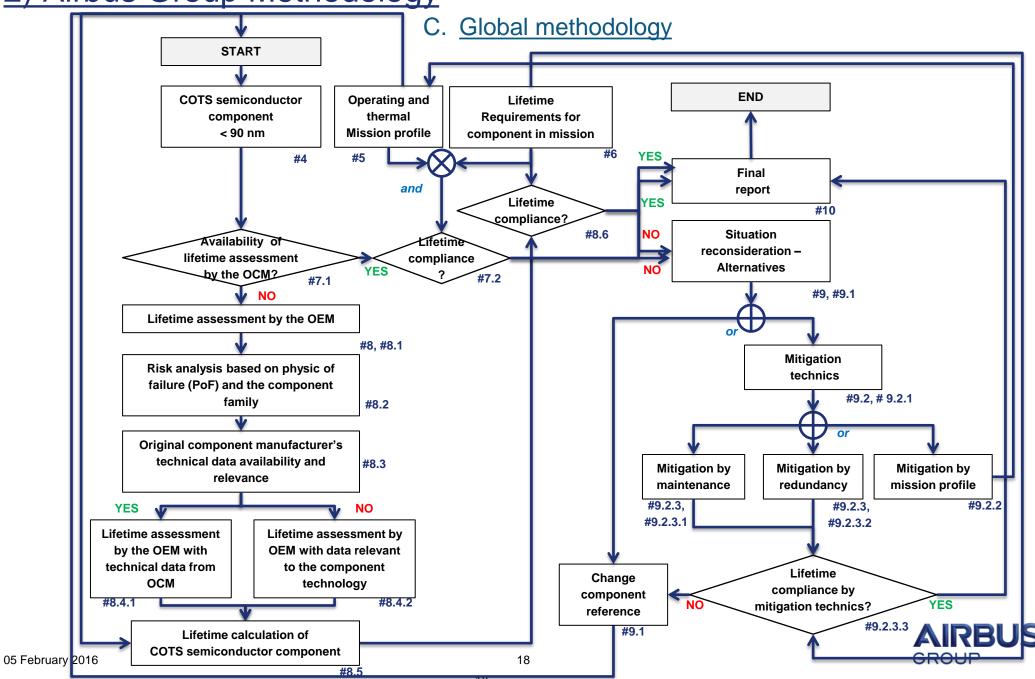

#### B. Methodology process flow

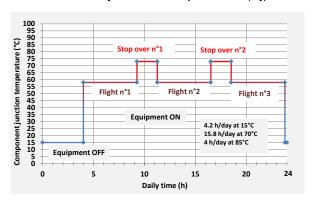

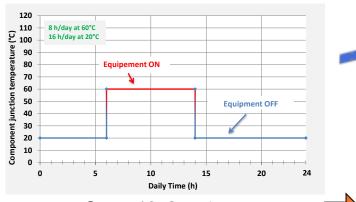

#### Operating and thermal Mission profile

- Operating (Equipment/component ON state)

- Thermal junction temperature (Tj)

- 166 000 h @Tj=73°C, V<sub>DD</sub> nominal, f nominal

- 42 000 h @Tj=58°C, V<sub>DD</sub> nominal, f nominal

• 87 600h @Tj=20°C, OFF, f nominal

43 800 h @Tj=60°C, V<sub>DD</sub> nominal, f nominal

~ 5 years

AIRBUS GROUP

#### B. Methodology process flow

Matrix of Failure mechanism to investigate by the OEM vs product family

| Failure   |           |              | Electronic component (<90 nm process) |                        |           |                |                        |  |  |  |  |  |  |

|-----------|-----------|--------------|---------------------------------------|------------------------|-----------|----------------|------------------------|--|--|--|--|--|--|

| mechanism | Componer  | nt structure | FPGA                                  | μΡ                     | DRAM      | Flash          | SRAM                   |  |  |  |  |  |  |

|           |           | Global       | <b>V</b>                              | <b>V</b>               | <b>V</b>  | √              | <b>V</b>               |  |  |  |  |  |  |

| EM        | Levels    | Intermediate | <b>V</b>                              | $\checkmark$           | NA        | NA             | NA                     |  |  |  |  |  |  |

|           |           | Local        | <b>√</b>                              | <b>√</b>               | $\sqrt{}$ | $\checkmark$   | $\checkmark$           |  |  |  |  |  |  |

|           |           | Global       | <b>V</b>                              | $\checkmark$           | $\sqrt{}$ | $\checkmark$   | $\checkmark$           |  |  |  |  |  |  |

| TDDB      | Levels    | Intermediate | <b>√</b>                              | $\checkmark$           | NA        | NA             | NA                     |  |  |  |  |  |  |

| BEOL      | Leveis    | Local        | <b>√</b>                              | <b>V</b>               | <b>V</b>  | (if LK oxides) | NA                     |  |  |  |  |  |  |

|           | I/O       | NMOS         | <b>V</b>                              | <b>V</b>               | <b>V</b>  | $\checkmark$   | <b>√</b>               |  |  |  |  |  |  |

| TDDB      | 2         | PMOS         | <b>V</b>                              | <b>V</b>               | <b>√</b>  | $\checkmark$   | <b>√</b>               |  |  |  |  |  |  |

| FEOL      | Core      | NMOS         | <b>V</b>                              | <b>V</b>               | NA        | NA             | <b>V</b>               |  |  |  |  |  |  |

| FEOL      |           | PMOS         | <b>V</b>                              | $\checkmark$           | NA        | NA             | $\checkmark$           |  |  |  |  |  |  |

|           | Capacitor | Oxide        | NA                                    | NA                     | $\sqrt{}$ | NA             | NA                     |  |  |  |  |  |  |

|           | I/O       | NMOS         | <b>V</b>                              | $\checkmark$           | $\sqrt{}$ | $\checkmark$   | $\checkmark$           |  |  |  |  |  |  |

| HCI       | 2)        | PMOS         | <b>V</b>                              | <b>√</b>               | <b>√</b>  | $\checkmark$   | $\checkmark$           |  |  |  |  |  |  |

|           | Core      | NMOS         | $\checkmark$                          | $\checkmark$           | $\sqrt{}$ | √ (if NOR)     | $\checkmark$           |  |  |  |  |  |  |

|           | Cole      | PMOS         | <b>√</b>                              | $\checkmark$           | NA        | NA             | $\checkmark$           |  |  |  |  |  |  |

|           | I/O       | NMOS         | √                                     | √                      | √         | $\checkmark$   | √                      |  |  |  |  |  |  |

| ВТІ       | 1/0       | PMOS         | $\checkmark$                          | $\checkmark$           | $\sqrt{}$ | $\checkmark$   | $\checkmark$           |  |  |  |  |  |  |

|           | Core      | NMOS         | √<br>(if HK<br>oxides)                | √<br>(if HK<br>oxides) | NA        | NA             | √<br>(if HK<br>oxides) |  |  |  |  |  |  |

|           |           | PMOS         | <b>V</b>                              | √                      | NA        | NA             | <b>√</b>               |  |  |  |  |  |  |

Selection of relevant failure mechanisms for a given product

#### B. Methodology process flow

#### Data to collect by the OEM from the OCM:

For the failure mechanisms previously identified by the reisk analysis:

- Raw reliability test results

- Failure distribution F(t)

- Distribution parameters

- Compact models + parameters

- Thermal acceleration

- Bias acceletration

#### B. Methodology process flow

#### Data to collect by the OEM form the scientific literature

For the failure mechanisms previously identified by the risk analysis:

- Raw reliability test results

- Acceleration models

#### Example of models:

| Failure mechanism | level                           | Acceleration model                                                                                                                                                                                                      |

|-------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ЕМ                | Global<br>Intermediate<br>Local | $AF_{EM} = \left(\frac{f_{TEST}}{f_{MISSION}}\right)^{n} \cdot \left(\frac{V_{TEST}}{V_{MISSION}}\right)^{-n} \cdot e^{\frac{E_{a}}{k}\left(\frac{1}{T_{MISSION}} - \frac{1}{T_{TEST}}\right)}$                         |

| TDDB BEOL         | Global<br>Intermediate<br>Local | $AF_{TDDB\_BEOL} = \left(\frac{S_{TEST}}{S_{MISSION}}\right)^{n} \cdot e^{G\left(\sqrt{E_{MISSION}} - \sqrt{E_{TEST}}\right)} \cdot e^{\frac{E_{a}}{k}\left(\frac{1}{T_{MISSION}} - \frac{1}{T_{TEST}}\right)}$         |

| TDDB FEOL         | I/O                             | $AF_{TDDB\_FEOL\_I/O} = \left(\frac{S_{TEST}}{S_{MISSION}}\right)^{n} \cdot e^{\gamma (E_{MISSION} - E_{TEST})} \cdot e^{\frac{E_{a}}{k} \left(\frac{1}{T_{MISSION}} - \frac{1}{T_{TEST}}\right)}$                      |

| TOODTEGE          | Core                            | $AF_{TDDB\_FEOL\_CORE} = \left(\frac{S_{TEST}}{S_{MISSION}}\right)^{n} \cdot \left(\frac{V_{TEST}}{V_{MISSION}}\right)^{r} \cdot e^{\frac{E_{a}}{k} \left(\frac{1}{T_{MISSION}} - \frac{1}{T_{TEST}}\right)}$           |

| нсі               | I/O                             | $AF_{HCI\_I/O} = \left(\frac{f_{TEST}}{f_{MISSION}}\right)^n \cdot e^{\gamma \left(\frac{1}{V_{MISSION}} - \frac{1}{V_{TEST}}\right)} \cdot e^{\frac{-E_a}{k} \left(\frac{1}{T_{MISSION}} - \frac{1}{T_{TEST}}\right)}$ |

|                   | Core                            | $AF_{HCI\_CORE} = e^{\gamma \left(\frac{1}{V_{MISSION}} - \frac{1}{V_{TEST}}\right)} \cdot e^{\frac{E_a}{k} \left(\frac{1}{T_{MISSION}} - \frac{1}{T_{TEST}}\right)}$                                                   |

| ВТІ               | I/O                             | $AF_{BTI\_I/O} = e^{\gamma \cdot (V_{MSSION} - V_{TEST})} \cdot e^{\frac{E_a}{k} \left(\frac{1}{T_{MSSION}} - \frac{1}{T_{TEST}}\right)}$                                                                               |

|                   | Core                            | $AF_{BTI\_CORE} = e^{\gamma \cdot (V_{MISSION} - V_{TEST})} \cdot e^{\frac{E_a}{k} \left(\frac{1}{T_{MISSION}} - \frac{1}{T_{TEST}}\right)}$                                                                            |

Models from literature are technology dependant!!

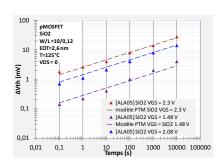

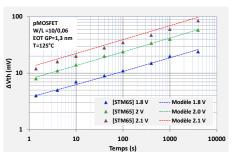

#### B. Methodology process flow

#### **Action for OEM**

Adjust parameters/models on experimental results from literature (with technological relevancy)

$$\Delta V_{th} = K_{v} \cdot \beta^{0.25} \cdot T^{0.25} \cdot \left[ \frac{1 - (1 - \sqrt{\eta(1 - \beta)/n})^{2n}}{1 - (1 - \sqrt{\eta(1 - \beta)/n})^{2}} \right]^{0.5} + \delta_{v}$$

$$K_{v} = A \cdot T_{ox} \cdot \sqrt{C_{ox}(V_{gs} - V_{th})} \cdot \exp\left(\frac{E_{ox}}{E_{0}}\right) \cdot \left[ 1 - \frac{V_{ds}}{\alpha(V_{gs} - V_{th})} \right] \cdot \exp\left(-\frac{E_{a}}{kT}\right)$$

[BTI PTM model, ASU university]

(or) use existing database

Database of AF degradation models relevant with all technologies of COTS semiconductor available on market

#### B. Methodology process flow

#### Data to collect by the OEM

Description of component technology

| Table D<br>FEOL<br>paramet | ers          | Parameter                   | Notation                  | Unit |  |  |

|----------------------------|--------------|-----------------------------|---------------------------|------|--|--|

| BEOL                       | Global wires | Nature of metallization     | NA                        | NA   |  |  |

|                            |              | Nature of insulation oxides | NA                        | NA   |  |  |

|                            |              | Width of metal wires        | $W_{GLOBAL}$              | nm   |  |  |

|                            |              | Thickness of metal wires    | T <sub>GLOBAL</sub>       | nm   |  |  |

|                            |              | Wire to wire pitch          | P <sub>GLOBAL</sub>       | nm   |  |  |

|                            | Intermediate | Nature of metallization     | NA                        | NA   |  |  |

|                            | wires        | Nature of insulation oxides | NA                        | NA   |  |  |

|                            |              | Width of metal wires        | W <sub>INTERMEDIATE</sub> | nm   |  |  |

|                            |              | Thickness of metal wires    | T <sub>INTERMEDIATE</sub> | nm   |  |  |

|                            |              | Wire to wire pitch          | PINTERMEDIATE             | nm   |  |  |

|                            | Local wires  | Nature of metallization     | NA                        | NA   |  |  |

|                            |              | Width of metal wires        | NA                        | NA   |  |  |

|                            |              | Thickness of metal wires    | W <sub>LOCAL</sub>        | nm   |  |  |

|                            |              | Dimension of metal wires    | T <sub>LOCAL</sub>        | nm   |  |  |

|                            |              | Wire to wire pitch          | P <sub>LOCAL</sub>        | nm   |  |  |

| FEOL                       | 1/0          | Nature of Gate oxide        | NA                        | NA   |  |  |

|                            | Transistors  | Equivalent Oxide Thickness  | EOT <sub>I/O</sub>        | nm   |  |  |

|                            |              | Gate oxide surface          | S <sub>G_I/0</sub>        | nm   |  |  |

|                            |              | Nature of gate              | NA                        | NA   |  |  |

|                            |              | Gate lengh                  | $L_{G_{-}I/0}$            | nm   |  |  |

|                            |              | Gate width                  | $W_{G_{-}I/0}$            | nm   |  |  |

|                            | Core         | Nature of Gate oxide        | NA                        | NA   |  |  |

|                            | Transistors  | Equivalent Oxide Thickness  | EOT <sub>CORE</sub>       | nm   |  |  |

|                            |              | Gate oxide surface          | S <sub>G_CORE</sub>       | nm   |  |  |

|                            |              | Nature of gate              | NA                        | NA   |  |  |

|                            |              | Gate lengh                  | L <sub>G_CORE</sub>       | nm   |  |  |

|                            |              | Gate width                  | $W_{G\_CORE}$             | nm   |  |  |

|                            | Substrate    | Nature of substrate         | NA                        | NA   |  |  |

#### From De Processing Analysis (DPA)

#### Database of degradation models

#### Multitude of technology coexist on market

| 1) Introduction                |

|--------------------------------|

| 2) Airbus Group<br>Methodology |

| 3) Conclusion                  |

| Technology CMOS Overview High performance family (nm) |                            |          | USA      |          |          |          |               |          |          |                 |                 | Taiwan        |                |               |                 |   |      |                |   |                | Europe |          |          |          |                   |

|-------------------------------------------------------|----------------------------|----------|----------|----------|----------|----------|---------------|----------|----------|-----------------|-----------------|---------------|----------------|---------------|-----------------|---|------|----------------|---|----------------|--------|----------|----------|----------|-------------------|

|                                                       |                            | Intel    |          |          |          |          | GlobalFoundry |          |          |                 |                 | UMC           |                |               |                 |   | TSMC |                |   |                |        |          | ST Micro |          |                   |

|                                                       |                            | 90<br>nm | 65<br>nm | 45<br>nm | 32<br>nm | 22<br>nm | 90<br>nm      | 65<br>nm | 40<br>nm | 28<br>nm<br>HPP | 22<br>nm<br>UHP | 90<br>nm<br>G | 65<br>nm<br>SP | 40<br>nm<br>G | 28<br>nm<br>HPM |   |      | 40<br>nm<br>GP |   | 20<br>nm<br>HP |        | 90<br>nm | 65<br>nm | 40<br>nm | 28<br>nm<br>FDSOI |

|                                                       | Metal gate                 | N        | N        | Y        | Y        | Y        | N             | N        | N        | Y               | Y               | N             | N              | N             | Y               | N | N    | N              | Y | Y              | Y      | N        | N        | N        | N                 |

| FEOL                                                  | High-k Dielectrics         | N        | N        | Y        | Y        | Y        | N             | N        | N        | Y               | Y               | N             | N              | N             | Y               | N | N    | N              | Y | Y              | Y      | N        | N        | N        | N                 |

|                                                       | Strain silicion            | Y        | Y        | Y        | Y        | Y        | Y             | Y        | Y        | ?               | Y               | N             | Y              | Y             | Y               | N | ?    | Y              | Y | Y              | Y      | N        | N        | Y        | Y                 |

| BEOL                                                  | Copper metalizations       | Y        | Y        | Y        | Y        | Y        | Y             | Y        | Y        | Y               | Y               | Y             | Y              | Y             | Y               | Y | Y    | Y              | Y | Y              | Y      | Y        | Y        | Y        | Y                 |

| BEOL                                                  | Low-k Dielectrics          | Y        | Y        | Y        | Y        | Y        | Y             | Y        | Y        | Y               | Y               | Y             | Y              | Y             | Y               | Y | Y    | Y              | Y | Y              | Y      | Y        | Y        | Y        | Y                 |

| Substrate                                             | Silicon on Insulator (SOI) | N        | N        | N        | N        | N        | Y             | Y        | Y        | Y               | Y               | N             | Y              | 5             | N               | Y | Y    | Y              | Y | Y              | N      | N        | Y*       | N        | Y                 |

| Architecture                                          | FinFETs                    | N        | N        | N        | N        | Y        | N             | N        | N        | N               | Y               | N             | N              | N             | N               | N | N    | N              | N | N              | Y      | N        | N        | N        | N                 |

#### \*On demand

#### At fixe node/OCM: different transistor optimization vs application

|      |                    |                                |                                           | TSMC 28 nm                                            |                                              |                         |

|------|--------------------|--------------------------------|-------------------------------------------|-------------------------------------------------------|----------------------------------------------|-------------------------|

|      |                    | 28 nm<br>High Performance (HP) | 28 nm<br>High Performance Mobile<br>(HPM) | 28 nm High Performance Compact Mobile computing (HPC) | 28 nm<br>High Performance Low power<br>(HPL) | 28 nm<br>Low power (LP) |

|      | Metal gate         | Y                              | Y                                         | Y                                                     | Y                                            | N (PolySi)              |

| FEOL | High-k Dielectrics | Y                              | Y                                         | Y                                                     | Y                                            | N (Nitride Oxide)       |

| FEOL | Lengh gate (nm)    | 31 nm                          | 35 nm                                     | 30 - 40 nm                                            | 35 nm                                        | 38 nm                   |

|      | Vcore              | 0.85 V                         | 0.90 V                                    | 0.90 V                                                | 1,00 V                                       | 1,05 V                  |

[1] [2]

1 technological node ~ 30 differents technologies

~ 30 degradation models

Airbus Group Data base ~ 110 models (2012)

#### <u>Assessment</u>

## Lifetime predictions of Deep Sub-Micron commercial EEE parts for a specific application Lifetime assessment by the OEM

1) Introduction

2) Airbus Group Methodology

3) Conclusion

#### Advantage of the method:

- Based on Physics of failure (PoF), environment and part technology

- Combine two approach:

- Lifetime Assessement with technical data from OCM (by default if possible)

- Lifetime Assessement with technical data relevant to the component technology (in absence of collaboration with OCM)

- Simply enough to be implemented in a tool (Airbus Tool for internal use so far)

- Methodology applied on Airbus Group parts (memories, FPGA, µProcerssors) for aeronautic, aerospace and military applications for 8 years!

#### Weakness/limitations of the method:

- May require to have access to the component technology (De Processing Analysis)

- Do not consider the impact of the design and the manufacturing process

- Method supposed that:

- All failure mechanisms are independant between themselves

- AF degradation models can be extrapolated over a long period of use

## 3) Conclusion and perspectives

#### With COTS semiconductor technologies < 180 nm (and mainly <90 nm):

- Increase of failure rate

- Decrease of intrinsic lifetime

#### How to face with:

- Wearout is a deterministic phenomenon that has to be evaluated/predicted in design phase by OEM

- Some working group develop methodologies

France (Airbus, GIFAS)

US (AFE83)

#### **Discussion and proposition**

Topic "Assessment of COTS semiconductor component in Hi-Rel and long term application"

Has to be addressed at electronic component management level through Technical Standard document proposing an "industrial"

Can be based on Airbus 2015-IW-SI-000036-1 document

Or/and GIFAS document (reference GIFAS/2015/5022), public access [1]

IEC has included concepts from the Airbus Group methodology into their Wearout Life Calculation standard IEC TS 62239-1 (in revision to IEC TS 62239-2)

1) Introduction

2) Airbus Group Methodology

3) Conclusion

## 3) Conclusion and perspectives

#### **Acknowledgement**

1) Introduction

2) Airbus Group Methodology

3) Conclusion

- Airbus Group Innovations Teams

- Divisions of Airbus Group

#### **Thanks for your attention**

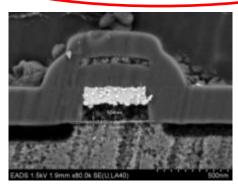

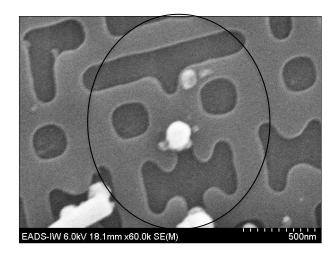

SRAM 90 nm, SEM, x 60k

## 4) Sources

Introduction

Airbus Group Methodology

3) Conclusion

| [1] | "Guide for the selection of Deep Sub-Micron (DSM) for aeronautic equipment -<br>Semiconductors lifetime", edited in 2015<br>https://www.gifas.asso.fr/en/                                                                                                          |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2] | Synopsys website, consulted the 03/01/2016 <a href="https://www.synopsys.com/Company/Publications/DWTB/Pages/dwtb-logic-libraries-tsmc28-hpc-2015q3.aspx">https://www.synopsys.com/Company/Publications/DWTB/Pages/dwtb-logic-libraries-tsmc28-hpc-2015q3.aspx</a> |

| [3] | TSMC webiste, consulted the 03/01/2016 <a href="http://www.tsmc.com/english/dedicatedFoundry/technology/28nm.htm">http://www.tsmc.com/english/dedicatedFoundry/technology/28nm.htm</a>                                                                             |