# Risk analysis on IC in Schneider Electric

Presented by: Claire Garden / EME lab / Schneider Electric

# Summary

#### Summary

- 1. Schneider Electric / EME laboratory

- 2. Mission Profile: Customer expectation

- 3. Risk analysis on IC

- 4. Difficulties / Concerns

#### Schneider Electric,

the global specialist in energy management and automation

~5% of revenues devoted to R&D

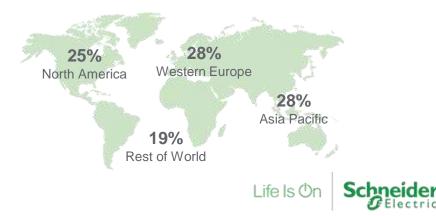

#### Diversified end markets - FY 2014 revenues<sup>1</sup>

#### Balanced geographies – FY 2014 revenues<sup>1</sup>

#### Energy is the base of life.

Life Is On when energy is on.....

We ensure energy is on by making it

- Safe

- Reliable

- Efficient

- Connected

- Sustainable

At Schneider Electric, we combine **Energy Management, Automation** and **Software** serving 4 markets, i.e. 70% of the world energy consumption

#### The maps cannot carriers he displayed.

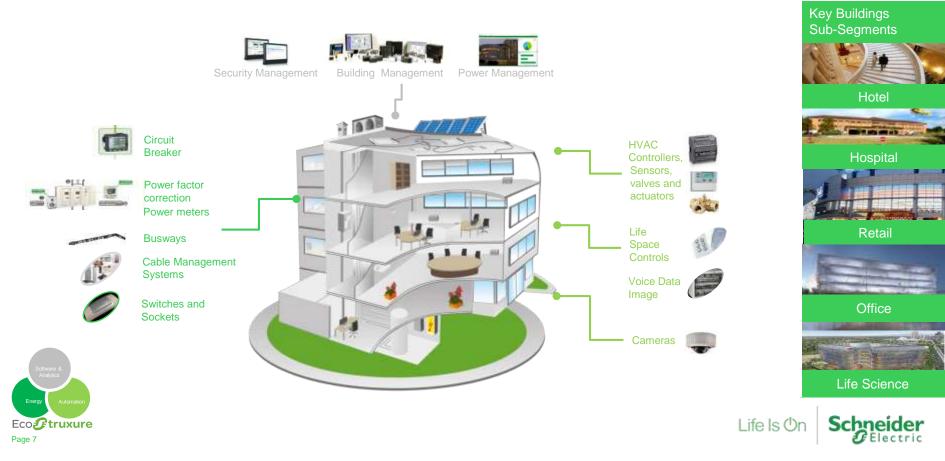

### Life is On with Schneider Electric Building Solutions:

From grid to floor space, we ensure safety, comfort, reliability, efficiency and sustainability

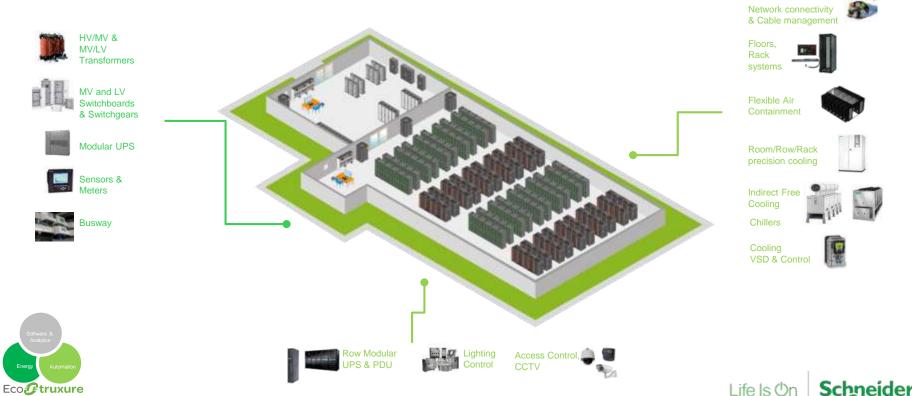

## Life is On with Schneider Datacenter Solutions:

From rack to cyber space, we optimize performance, speed and cost

Page 8

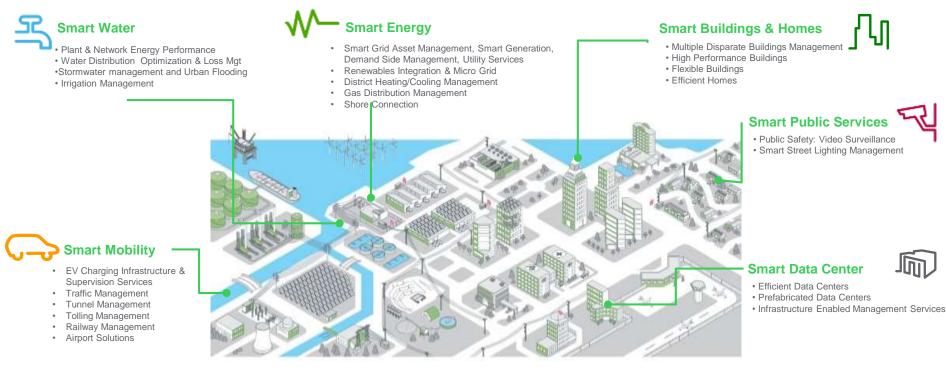

# Life is On with Schneider Electric Smart City Solutions:

From downtown to suburb , we deliver urban efficiency today

- City-wide Platforms

- Energy & Sustainability Resource Management

- Urban Efficiency Platform

- District Energy Management Information System

- Cross-domain Application

Weather

- GIS

Asset Management

- City Strategy Services

Sustainability Services

Smart Cities Advisory Services

- Energy Performance Contracting

Our capabilities allow us to deliver tangible results for customers, wherever they might be.

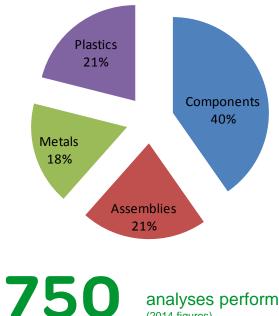

# Electronics and Materials Expertise Lab. (EME)

#### Provide technological expertise support to all Schneider Electric Businesses for product quality mastery

- Qualification

- Failure analysis

- Consulting

#### In the field of

- Electronics

- Materials

- Metals

- Assembly

#### EME lab in few figures

**19** experts 550 m² lab M€ equipment

a wide external laboratory network

analyses performed / year (2014 figures)

expertise reports accessible in our iExpert database

## Mission Profile: Customer Expectation

Electronics to be safe, reliable, connected, green, in our customer environment during the expected lifetime.....

Varieties of environmental constraints in our final customers applications require high reliability & requirements levels where failures cannot be tolerated!

# Our Customers expect the "legendary reliability of Schneider Electric products "!

For each life phase of the product, the mission profile ...

- 1. describes the environmental conditions of the product and its components

- 2. describes the usage conditions

- 3. fixes the expected time duration and cycles numbers

Shipping

#### Manufacturing:

Ś

component storage, assembling, sub-assembly storage Maintenance Operation

Installation /

Storage:

distributor, final customer

distribution center,

Commissioning

### **Product Mission Profile Example**

| Storogo   | Temperature<br>(close to the component) | Humidity<br>(close to the component) | Duration |

|-----------|-----------------------------------------|--------------------------------------|----------|

| Storage   | 30°C                                    | 80%RH                                | 6 months |

|           |                                         |                                      |          |

|           | Temperature<br>(close to the component) | Humidity<br>(close to the component) | Duration |

|           | 90°C                                    | 7%                                   | 61320 h  |

|           | 105°C                                   | 5%                                   | 26280h   |

| Operation |                                         |                                      |          |

|           | Temperature<br>(close to the component) | Humidity<br>(close to the component) | Duration |

|           | 50°C                                    | 15%                                  | 157680h  |

|           | 60°C                                    | 10%                                  | 8760h    |

# Standard components market gets lower level requirements than Schneider industrial products

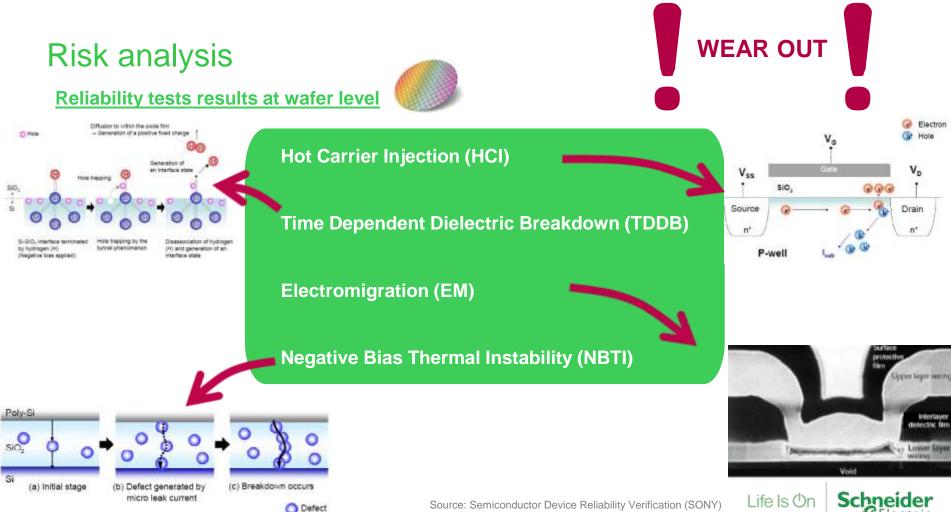

# Risk analysis on IC

Quality and Reliability data from the component manufacturer are compared to the need of the project (mission profile), in order to identify the risks related to the technology and its use in the final product

1<sup>rst</sup> step: Gathering component data by CIR

2<sup>nd</sup> step: Analysis and calculation

3<sup>rd</sup> step: Risk assessment plan

1<sup>rst</sup> step

• Gathering all the data concerning the component: A CIR is sent to the supplier

- Check obsolescence or shrink status of the component,

- Technological node used,

- Wafer plant names and locations,

- Assembly plants/subcontractors names and locations

- All test results (wafer, die and package levels)

2<sup>nd</sup> step

#### Analysis of the CIR form

#### **Reliability tests results at device level**

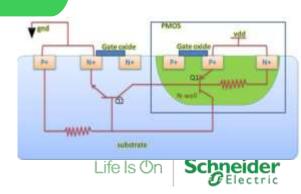

Latch Up (LU) at max. operating temperature

**Electro-Static Discharge (ESD)**

Acc.V WD

15.0 kV 10.2

2 µm

<u>Reliability tests results at die level</u> (applying to non volatile memories and IC's with flash or non volatile memories embedded )

Non-volatile Memory Uncycled High Temperature Data Retention (UCHTDR)

Non-volatile Memory Cycling Endurance (NVCE)

Non-volatile Memory Post Cycling High Temperature Data Retention (PCHTDR)

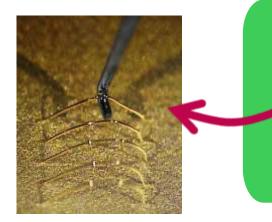

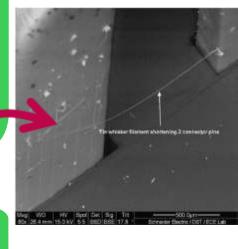

#### Reliability tests results at package level

High Temperature Storage (HTS) Temperature Humidity Bias (THB) or Highly Accelerated Stress test (HAST) Thermal Cycling (TC) Bond Pull Strength (BPS) Bond Shear (BS) Solderability (SD) Tin whisker's tests excepted to BGA package

#### **Qualification tests applying only to BGA packages:**

Convex, Warpage

Concave warpag

Solder Ball Shear (SBS) Thermal warpage characterization test

Source: http://www.tpt-wirebonder.com/en/accessories/add-ons/h53-pull-tester.html JESD22 B112

ife Is (

| 2 <sup>nd</sup> step • Check if JEDEC S                    | all the tests have been parts for the set of all the tests have been parts (or AEC-Q100): JES | erformed in accordance with<br>SD47I / JEP122G / JEP001A                                             |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| JEDEC<br>PUBLICATION                                       | JEDEC<br>STANDARD                                                                             | JEDEC<br>PUBLICATION                                                                                 |

| Failure Mechanisms and Models for<br>Semiconductor Devices | Stress-Test-Driven Qualification of<br>Integrated Circuits                                    | FOUNDRY PROCESS<br>QUALIFICATION GUIDELINES<br>(Wafer Fabrication Manufacturing Sites)               |

| JEP122G<br>(Revision of JEP22E, Neversitive 2008)          | JESD47I<br>(Keritions of JESD47H.01, April 2011)                                              | JEP001A<br>(Bertama of J9001.01, Nov. 2004)                                                          |

| OCTOBER 1913<br>JEDEC SOLID STATE TECHNOLOGY ASSOCIATION   | JULY 2012<br>JEDEC SOLID STATE TECHNOLOGY ASSOCIATION                                         | INDERVISE<br>JEDEC SOLID STATE TECHNOLOGY ASSOCIATION<br>FABLESS SEMICONDUCTOR ASSOCIATION<br>JEDEC. |

2<sup>nd</sup> step

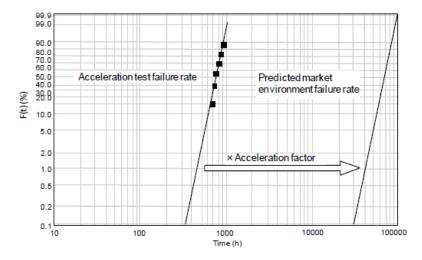

Use acceleration factors and JEDEC models in order to validate the coverage of the mission profile by the reliability tests performed by the supplier

Arrhenius

$$AF = e^{\frac{E_a}{k} \left(\frac{1}{T_{use}} - \frac{1}{T_{rest}}\right)}$$

**Black Model**

$AF = \left(\frac{Juse}{Jtest}\right)^{-n} * e^{\frac{E_a}{k}\left(\frac{1}{T_{use}} - \frac{1}{T_{test}}\right)}$

Life Is C

Hallberg-Peck Model

$$AF = \left(\frac{RH_{Test}}{RH_{use}}\right)^m$$

Source: Semiconductor Device Reliability Verification (SONY)

3<sup>rd</sup> step

| <ul> <li>Identify the risks</li> </ul> |

|----------------------------------------|

|----------------------------------------|

• Propose a risk assessment plan

| Risk n° | Description of risk<br>(describe risks of use in Schneider products that<br>are not covered<br>by Manufacturer's qualification)                                                | Risk Assessment Proposal<br>(describe proposed assessment works necessary for the<br>use of the component<br>in targeted Schneider products) |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Risk of poor quality of assembly of BGA<br>package on electronic boards<br>for <u>ASET assembly site</u> :<br>The supplier did not provide the SBS, SD and<br>warpage tests    | Ask the supplier to provide SBS, SD and warpage test results.                                                                                |

| 2       | Risk of poor quality of assembly of BGA<br>package on electronic boards<br>for <u>CML assembly site</u> :<br>BGA thermal warpage characterization test results<br>are missing. | Ask the supplier to provide BGA thermal warpage characterization results.                                                                    |

Gap coverage following risk analysis

Reliability tests missing: ask the supplier to provide the missing test

Example: missing HTS test

Reliability tests not covering the mission profile: ask the supplier to perform the test with the conditions to cover the mission profile or perform the test in our laboratory

→Example: data retention test

•Technological analyses (verification of the process quality, wafer fab unknown, new technology...)

# Difficulties / Concerns

### **Difficulties / Concerns**

• Difficulties in getting the relevant data from supplier (especially for wear out test results) as companies buy only small quantities of components.

Difficulties in getting the activation energy value for certain test (data retention, HCI...)

→ "Secret" values for component companies (can reveal the maturity of the process...)

• Models used are getting obsolete (combination of failures mechanisms....) and in some points the JEDEC has reached its limit.

• Use multisource to avoid obsolescence: merging of several companies reduce the choice of component supplier (NXP/Freescale, Cypress/Spansion....)

# THANK YOU.

#### Questions?