## **Radiation Testing at System Level**

Christian Poivey 09/03/2021 ESCCON 2021

ESA UNCLASSIFIED - For ESA Official Use Only

→ THE EUROPEAN SPACE AGENCY

\*

Scope TID System/Board Level Testing Advantages and Disadvantages Single Event Effect System/Board Level Testing Advantages and Disadvantages **Conclusion**

→ THE EUROPEAN SPACE AGENCY

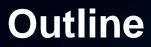

### System Level Testing, What Are We Talking About?

System Level Testing: Board(s) testing (breadboard or EM) or COTS unit

System/Board level testing is not a new technique (common practice in some ISS applications)

esa

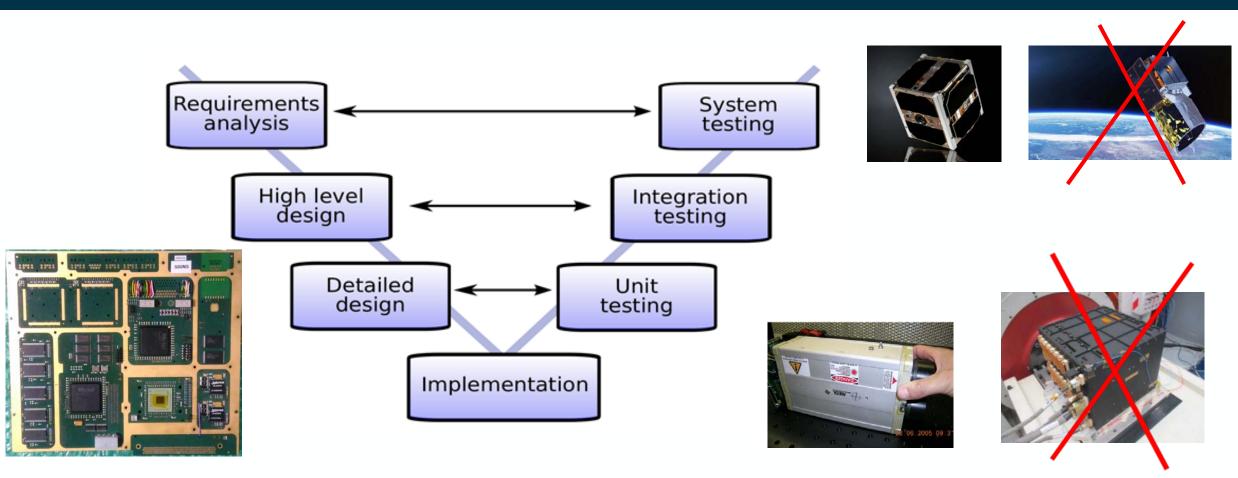

## **Radiation Effects Testing – In a Nutshell**

#### (Adapted from Muschitiello & Costantino, SERESSA 2018)

### **Total Ionizing Dose Testing**

| PART        | PARAM                                                                    | AGING                           | RADIATION          |                          |  |

|-------------|--------------------------------------------------------------------------|---------------------------------|--------------------|--------------------------|--|

|             |                                                                          | Drift                           | Design Dose (Krad) | Drift                    |  |

| RH1014      | Voffset                                                                  | ±0,1mV                          | 100                | ±1,4mV                   |  |

| HS9-139 RH  | V <sub>OFFSET</sub><br>I <sub>b</sub><br>I <sub>OFFSET</sub>             | ±0,1mV<br>+1,8%<br>±9%          | 100                | ±1mV<br>150nA<br>±16nA   |  |

| RH118W      | GBWP<br>V <sub>OFFSET</sub>                                              | -4,4%<br>±0,2mV                 | 100                | -10%<br>±0,75mV          |  |

| OP467F      | V <sub>OFFSET</sub><br>I <sub>b</sub><br>I <sub>OFFSET</sub><br>Min Gain | ±0,2mV<br>+1,8%<br>±9%<br>-1,8% | 15                 | 1mV<br>1μA<br>0,3μA<br>0 |  |

| PE9601      | Κφ                                                                       | ±2%                             | 100                | -                        |  |

| DAC08-498AF | INL<br>Full Range Current                                                | 0%<br>0%                        | 60                 | ±0,25LSB<br>-0,555%      |  |

| SOC 2N2907  | β<br>V <sub>BE</sub>                                                     | -4,4%<br>+1,8%                  | 70                 | -55%<br>-55%             |  |

Radiation data on parts (worst case bias)

#### **Worst-case analysis** Estimation of function degradation

#### **Design Validated**

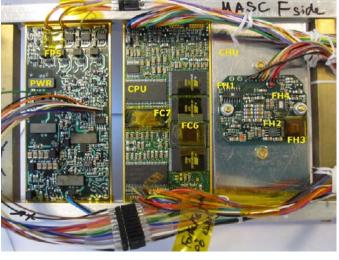

Board Level Testing

Measurement of Function(s) degradation

5

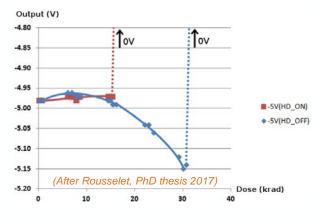

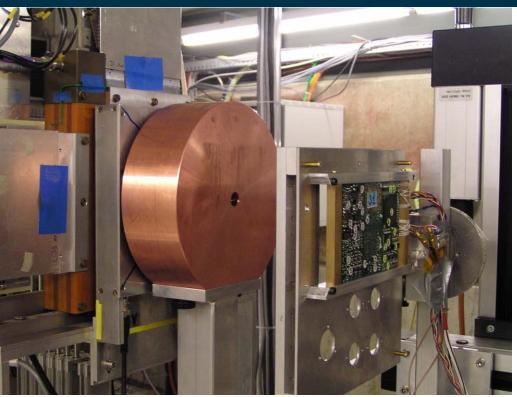

## **TID Board Level Testing**

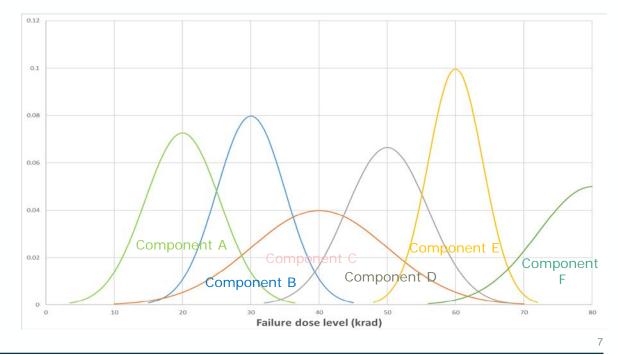

- Board tolerance will the tolerance of the most sensitive part(s) in the board for their particular function(s)

- The approach is commonly used for RHA of hybrid devices and authorized in RHA ECSS standard

DC-DC converters, oscillators,...

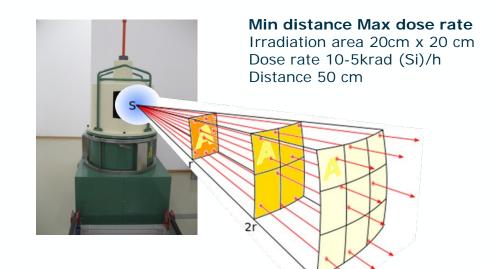

Max distance Min dose rate Irradiation area 3.6 m x 3.6 m Dose rate 40-20 rad (Si)/h Distance 7.5m

### **TID Board Level Testing**

#### Advantage

- Test time is reduced

- Parts are tested in application conditions

- Disadvantage

- Observability is reduced,

- Test up to failure level is recommended

- Complicated test sequences

- Significant loss of RHA quality if sample size is low

(1 board = 1 sample per device type in some cases)

- Maybe compensated with higher margins?

- If a single part is changed, whole board may have to be tested again

- Results cannot always be used for another application

- Component level is done for worst case bias condition

- Results come late in the design phase

#### → THE EUROPEAN SPACE AGENCY

### **Single Event Effect Testing**

#### Component Level Testing

Measurement of SEEs crosssections of each part used SEE criticality analysis (analysis of function response to SEE in parts)

SEE rate calculation

#### **Design Validated**

Observation of effects of SEE in parts to the function

SEE rate calculation

#### Board Level Testing

measurement of SEE cross sections

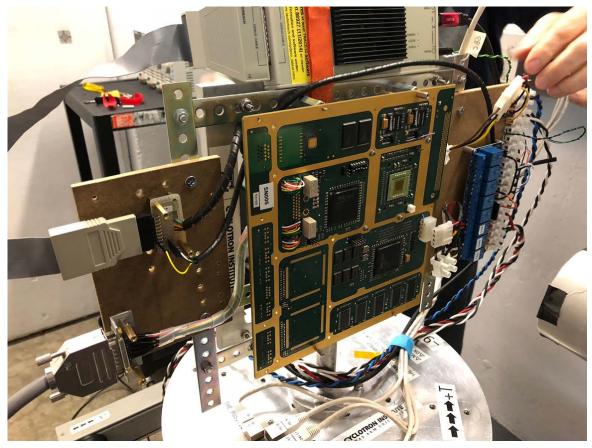

### **SEE Board Level Testing**

In most cases one component is irradiated at a time even when several components on a board shall be tested

- > Max beam area in common facilities is generally limited

- Ions ~ 2\*2 cm

- Protons ~8\*8 cm

- In flight, probability of hitting 2 components on a board at the same time is negligible

- □ GCR flux ~4 ions/s-cm<sup>2</sup>

- Irradiation test conditions vary in function of tested component (flux, fluence, LET,..)

# There is little gain in test and beam time when doing board level SEE testing

#### \_\_\_\_ ▋▋ ▶\_\_ ▋▋ ━━ ┿─ ▋▋ ━━ \_\_\_ ▋▌ ▋▋ \_\_\_ 〓 ╬╦ ▄▄ Ø团 ▋▋ \_\_\_ ▋▌ ▋▌ ▓ → THE EUROPEAN SPACE AGENCY

### **SEE Board Level Testing**

#### Advantages

- Board Testing allows testing in application conditions

- □ Final design (FPGA, ASIC)

- Application software (processors)

- Test of mitigations (SEL, EDAC, TMR. scrubbing, SET filtering..)

- Analog SETs

- Disadvantages

- Complicated test sequence

- Test order, Different test programs per part,..

- Mitigated designs (ie TMR) can only be tested at low flux

- Use of a lot of beam time

- Can be improved with adaptation of setup (scrub frequency,...)

- Long testing (lot of parts) with often unexpected results

- A single test campaign is often not enough to obtain complete and satisfactory results

- > Test results for a part may not always be used for another application (ie. analog SETs)

- Results come late in the design phase

10

### Conclusion

- Board level testing could guarantee a good quality of RHA when it is done right

- Sufficient sample size and margin for TID

- Ion and proton testing for SEE with sufficient statistics

- Board level testing is a risky approach

- A mixed approach between component level and board level could be the optimal approach

- SEE board level testing to test ASICs, FPGAs in their final design, and processors or SoCs with their application software is essential

### **Useful Reading**

" "RADSAGA System-level Testing Guideline for Space Systems," CERN Publication, EDMS 2423146, 2020

- "Board Level Proton Testing Book of Knowledge for NASA Electronic Parts and Packaking Program," S. Guertin & al., JPL Publication 17-7 11/17, <u>http://nepp.nasa.gov</u>

- "Guidelines for SEE Testing of COTS Electronics Using Proton Board Level Testing," S. Guertin & al., NASA WBS: 724297.40.49, <u>http://nepp.nasa.gov</u>

# **Back-up slides**

ESA UNCLASSIFIED – For ESA Official Use Only

####

→ THE EUROPEAN SPACE AGENCY

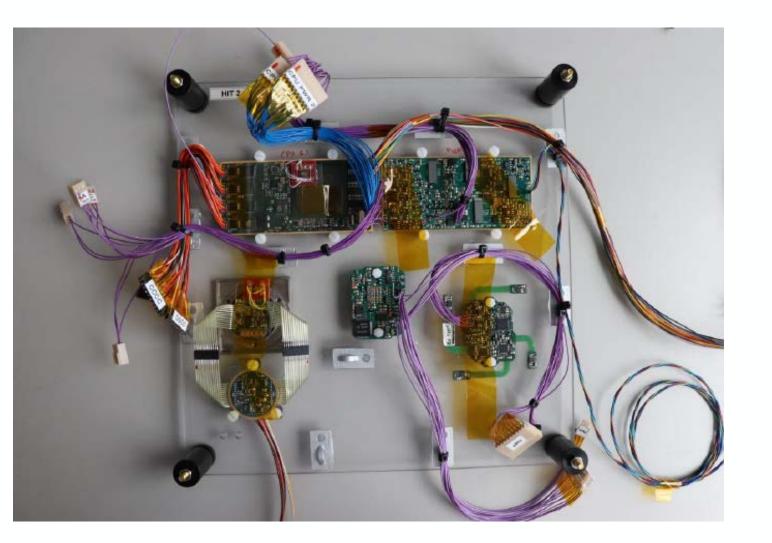

#### **SEE Board Level Testing - Example**

| SN74LVC2G34DRLR (PbF)                                                                                                                                                                                                                                                                                               | 1&2                                                              | μ                                                    | 16                            | SET/SEL                                                                                                | Program 7                                                                            | А                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------|

| NDS355AN                                                                                                                                                                                                                                                                                                            | 1&2                                                              | н                                                    | 23                            | SEB/SEGR                                                                                               | Program 7                                                                            | А                                 |

| NDS355AN<br>Program 1: Star tracking using<br>The instrument is connected to a<br>stimulator update mode.<br>Special probes included in test so<br>• The debug output of ECC<br>of RAM bitflips.<br>• The exception handling is<br>removing the assembler fl<br>• The watchdog timeout is of<br>SEU.<br>S-102T(PbF) | extern<br>CHU<br>oftware<br>_MON<br>set to<br>lag (E)            | nal (<br>with<br>::<br>ITO<br>deb                    | CHU<br>a sta<br>R is e        | with stimulator on<br>r stimulator. The insi<br>enabled in order to g<br>utput (to log informat<br>DT) | Port-B<br>trument operates i<br>et extended inform<br>ion of trapped SE              | n a<br>nation<br>Us) by           |

| 5-1021(PDF)                                                                                                                                                                                                                                                                                                         |                                                                  | <u> </u>                                             |                               | SED/SEGR                                                                                               | Program                                                                              | _                                 |

| S-301T(PbF)                                                                                                                                                                                                                                                                                                         | 1&2                                                              | Р                                                    | 18                            | SEB/SEGR                                                                                               | Program 1                                                                            | В                                 |

| <ul> <li>Special probes included in test so</li> <li>Upon transmission of an a gives the system amble til Typically, 1 or 2 housekee reports).</li> <li>The exception handling is by removing the assemble</li> </ul>                                                                                               | attitude<br>me to p<br>eping p<br>set to                         | e pao<br>powo<br>back<br>deb                         | er up<br>ets w                | and send the two po<br>ill also appear before<br>utput (to log informat                                | ower up reports.<br>e the restart (powe                                              | er up                             |

| SI4963BDY-T1-E3 (PBF)                                                                                                                                                                                                                                                                                               | 1&2                                                              | P                                                    | 20                            | SEB/SEGR                                                                                               | Program 2                                                                            | в                                 |

| Program 4: Verifying telemetry<br>This test verifies primarily the line<br>using memory dump, and the per<br>checksum errors. In order to mair<br>very low. The debug channel is fu<br>(only possible for the Maxim drive<br>startup mode is set to STANDBY<br>Special probes included in the test                  | e driver<br>forman<br>ntain m<br>urthern<br>er circu<br>st softv | r. It in<br>nce i<br>naxir<br>nore<br>uits).<br>ware | resulf<br>num<br>conf<br>Sinc | ts can be assessed f<br>statistics, the teleme<br>igured to MIRROR to<br>e attitude determina          | rom the number o<br>etry packet size is<br>o get maximum sta<br>tion is not required | f<br>set to<br>atistics<br>d, the |

| <ul> <li>The exception handling is<br/>removing the assembler fl</li> <li>The watchdog timeout is a<br/>SEU.</li> <li>The tolemetry packet size</li> </ul>                                                                                                                                                          | lag (E)<br>decrea                                                | (CP<br>sed                                           | _BOO<br>to 2s                 | DT)<br>to enable rapid reco                                                                            | overy after a trapp                                                                  | ed                                |

| The telemetry packet size  FIN1021MX                                                                                                                                                                                                                                                                                |                                                                  |                                                      | 21                            |                                                                                                        |                                                                                      |                                   |

| FIN1031MX                                                                                                                                                                                                                                                                                                           | 1&2                                                              | C                                                    | 21                            | SEL/SEFI                                                                                               | Program 4                                                                            | В                                 |

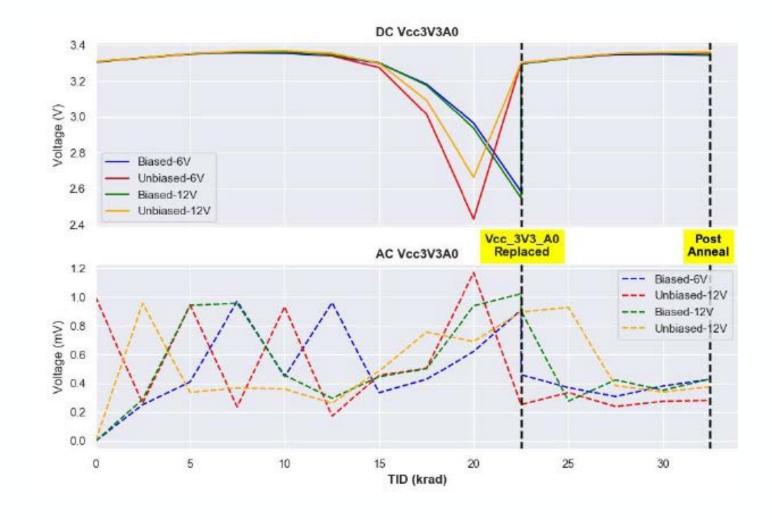

#### **TID Board Level Testing - Example**