An overview of GaN FET Technology, Reliability, Radiation and Market for future Space Application

09 March 2021

DEFENCE AND SPACE

Marco Carbone

# Contents

1/ GaN Background for Power

2/ Market Survey

3/ Failure Mechanism Description and Trapping Effect

4/ Airbus Reliability Approach

5/ Airbus Radiation Approach

6/ Conclusion

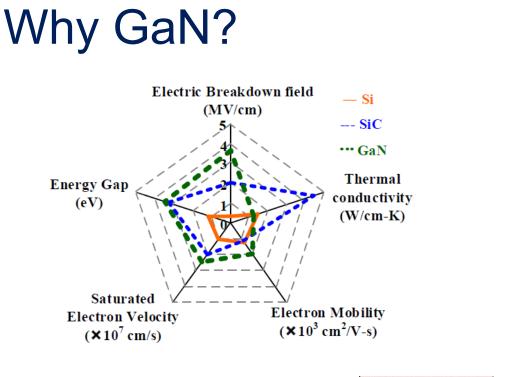

#### Material properties

- High electron saturation velocity ≈2.5 x10<sup>7</sup> cm/s

- High carrier density  $\approx 10^{13}/\text{cm}^2$

- Large bandgap

- High breakdown field

- High temperature operation

- Radiation robustness

- Heterostructure design (GaN)

- High output power density, small size, easy impedance match

- High voltage operation, simplified voltage

- Operation under extreme environmental

conversion

conditions

#### Applications

- Telecommunications

- Radars

- Novel sensors, detectors

- Power switching

- Solar cells, blocking diodes

|                                                                                          | Narrow band gap<br>Eg<<1eV |               | Intermediate band gap<br>Eg≈1eV          |               |               | Wide band gap<br>Eg>3eV |               |

|------------------------------------------------------------------------------------------|----------------------------|---------------|------------------------------------------|---------------|---------------|-------------------------|---------------|

|                                                                                          | InSb                       | InAs          | In <sub>0.53</sub> Ga <sub>0.47</sub> As | Si            | GaAs          | SiC                     | GaN           |

| Electron Mobility<br>x10 <sup>3</sup> (cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ) | 30                         | 16            | 8                                        | 0.6           | 4.5           | 0.8                     | 1.6           |

| Electron Velocity<br>(10 <sup>7</sup> cm/s)                                              | 5.0<br>(peak)              | 4.0<br>(peak) | 2.7<br>(peak)                            | 1.0<br>(sat.) | 2.0<br>(sat.) | 2.0<br>(sat.)           | 2.7<br>(sat.) |

| Band-gap (eV)                                                                            | 0.18                       | 0.36          | 0.72                                     | 1.1           | 1.43          | 3.2                     | 3.4           |

| Breakdown field<br>(MV/cm)                                                               | 0.01                       | 0.1           | 0.4                                      | 0.6           | 0.6           | 3.5                     | 3.5           |

| Thermal conductivity<br>(W/cmK)                                                          | 0.18                       | 0.27          | ≈0.3                                     | 1.5           | 0.46          | 3.55                    | 1.7           |

| Heterojunctions                                                                          | Yes                        | Yes           | Yes                                      | Yes           | Yes           | No                      | Yes           |

|                                                                                          | -                          | -             |                                          |               |               |                         |               |

# Definition Lateral GaN HFET

Most of the GaN devices available today are lateral heterojunction field-effect transistors (HFETs), also known as high electron mobility transistors (HEMTs).

| Source                                                                        | Gate | Passivation<br>(typically SiN) | Drain |  |  |  |  |  |

|-------------------------------------------------------------------------------|------|--------------------------------|-------|--|--|--|--|--|

|                                                                               | AIG  | AlGaN                          |       |  |  |  |  |  |

| 2DEG formed at hetereojunction                                                |      |                                |       |  |  |  |  |  |

| Current path<br>GaN                                                           |      |                                |       |  |  |  |  |  |

| Buffer (may be several layers thick, typically including GaN, AlGan, and AlN) |      |                                |       |  |  |  |  |  |

| <b>Substrate</b><br>(typically Silicon, but can be SiC, sapphire, or diamond) |      |                                |       |  |  |  |  |  |

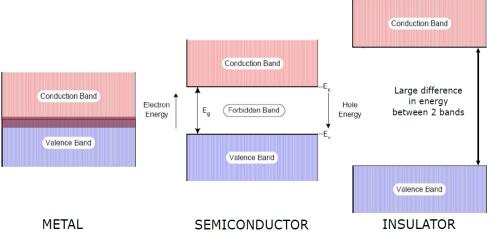

Heterojunction is the interface that occurs between two layers of dissimilar crystalline semiconductor and different unequal bandgap. So when you squeeze GaN on AlGaN electricity results from stress  $\rightarrow$  Piezoelectric Effect. So creation of the 2DEG.

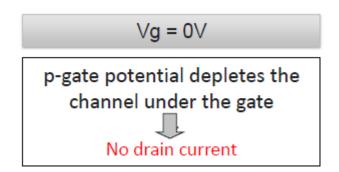

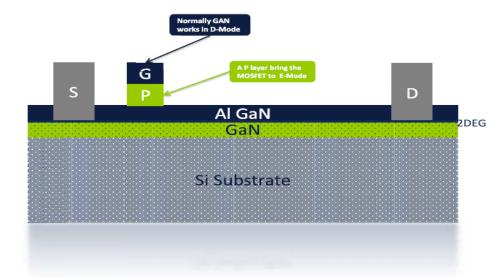

Because of the native 2DEG channel, the HFET is inherently a depletion-mode (normally-on) device. This is not desirable for voltage-source converters, because of the potential for shottky through during startup or loss of control power. Several methods have therefore been used to fabricate normally-off GaN HFETs.

#### DEFENCE AND SPACE

### NORMALLY OFF

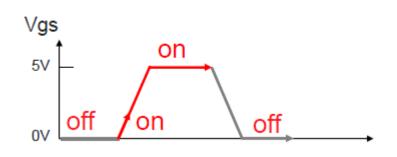

Most common technology of GaN FET transistors is Normally-Off or Enhanced-Mode, where a pdoped layer of GaN beneath the gate creates a diode-like characteristic on the gate that shifts the threshold up by the magnitude of the diode voltage drop. Although the 2DEG makes the lateral HFET natively depletion-mode, the gate can be modified to shift the threshold voltage positively and thereby make an enhancement-mode device. The figure shown the technique which are used to deplete the 2DEG carriers beneath the gate when no voltage is applied. A positive voltage above the threshold is then required to enhance this depleted 2DEG beneath the gate and complete the channel.

## GaN-FET players (power conversion)

#### **North America**

**Renesas** SSDI EPC EPC Space (EPC, Freebird, VPT) GaN Systems (CAN) **Navitas** AOS **Cambridge Electronics Inc.** Nexgen Tagore Vishay International Rectifier **Texas Instruments** Transphorm

**Europe / Israel** Teledyne-e2v (GaN Systems) **ONSemi** imec FBH **CEA-LETI Infineon (Panasonic)** ST MindCET (imec) **Cambridge GaN Devices** Nexperia Exagan Fraunhofer IAF VisIC (ISL) . . .

### Asia / Australia

Fuji / Furukawa Sanken

• •,•

Toyota Rohm (GaN Systems) AIST / ADPERC / GaN-OIL (JPN R&T) Skysilicon (CHN) IMCRC (AUS) Fujitsu / Transphorm Toshiba

#### This list is not exhaustive

Normally-off targeting space, regardless of market readiness or qualification

Normally-off

Normally-on or Cascode

. . .

### **General Market remarks**

- Many GaN-FET players worldwide, but still limited suppliers of GaN-FET normally-off

- Small, niche suppliers have been first on the market

- First market for GaN-FET seems to be telecom, datacenter converter, chargers (consumer)

other applications: PV inverter, motor control, wireless power, audio

- Automotive market for GaN?

- There is a large interest for various Automotive application.

- -GaN System and EPC are strongly targeting in automotive market

- Space market for GaN?

- space qualification cannot be only based on automotive heritage

- however the space market will follow closely the Automotive qualification activities.

- additional effort/cost for space evaluation/qualification necessary, even for new space application!

DEFENCE AND SPACE

## GaN-FET (eGaN) market trends

#### Normally-off devices ("p-GaN-Gate") targeting the Space Market

- 15 to 200 V: EPC (US) COTS (passivated die, non-hermetic). First Company with Automotive qualification.

- 40 to 300 V: EPC Space (US) with proprietary design for rad-hardening, with EPC die (ceramic hermetic package, die adaptor, hermetic and non-hermetic modules)

- 100 V, 200 V: Renesas (US) with EPC die with rad testing (hermetic package, modules). MIL-PRF-19500 tested device.

- 100 V and 650 V Teledyne e2v (F) with GaN Systems (fab-less Canadian company) with die manufactured and tested in Asia and packaged in Europe (die, hermetic package)

- 100 V to 300V SSDI (US)

- OnSEMI (BE) ESA GSTP Activity

- IMEC (BE) GaN-IC foundry

- FBH (GE) R&D no market offer yet

- 400 600 V Infineon Cool GaN Dual-sourcing agreement with Panasonic / i.e. p-GaN-gate structure licensed from Panasonic

#### Still rather limited number of candidate devices for space

• Still expecting other big players (Infineon, STmicroelectronics, Nexperia, TI ...) with a clear space roadmap

DEFENCE AND SPACE

# Open topic to be addressed for FM

Reliability and Radiation are the key issue for Power GN FET HEMT device, indeed several failure mechanisms not observed in Silicon technology can affect the GaN.

#### □ Long-Term Reliability Data

- Missing standards for GaN specific failure mechanisms

- Life test to be performed at operating conditions representative for application (application specific)

- Hard switching test recommended (hot-carrier stress, high dv/dt and thermal effects)

#### □ Radiation

• Even if GaN is inherently a radiation hardened material especially to displacement damage and dose effect, Power GaN is identified to be sensitive to Single Event Effect.

#### □ Space Standards

There is yet a lack of requirements for Space application for GaN Power device

- Part Stress with yet no derating requirements

- WCA

- Thermal Analysis

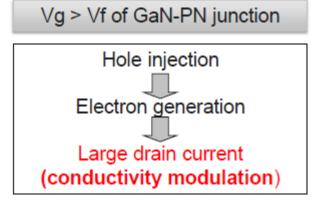

### GaN Issue and Failure Mechanism

- 1. Sub-Threshold Leakage mechanism (STL)

- Punch-Through source-drain (GaN buffer path)

- Surface and passivation layer hoping

- 2. Impact Ionization at Gate or Drain (High Electronic Field). Named Hot Carrier Injection mechanism (HCI)

- 3. Gate Bias Leakage (GBL)

- 4. Drain to Substrate Leakage

- 5. Time dependent Dielectric Breakdown (TDDB) under the gate (lateral failure)

- 6. Time dependent Degradation of the buffer under high vertical field

- 7. Degradation of the gate stack with p-type.

- 8. Ambient arcing at top metal electrodes (source, gate, drain)

(Wuerfl J. et al. Microelectronics reliability 51 (2011) pp 1710-1716)

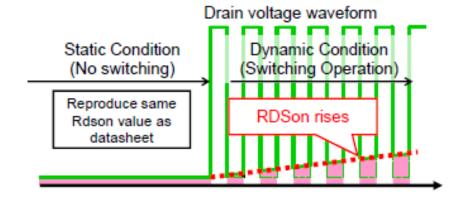

- 9 Trapping

- 1. Dynamic Rds On

- 2. Current Collapse

- 3. Catastrophic rupture

- 4. Vth Shift

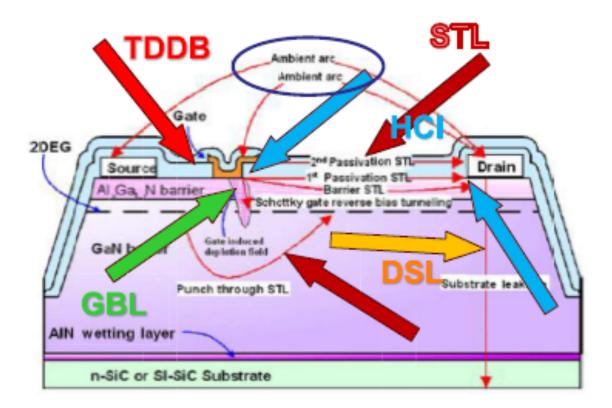

### Mechanism Trapping

The are several trapping phenomena related to the Heterojunctional manufacturing and to high Electrical Field for theGaN FET.

- Surface Traps. Trapping of surface charges near the drain-edge of the gate terminal when the device is in its off-state. This traps capturing "Hot Electron" crossing the AlGaN barrier. During the following switching on-state (or Semi-On-State) these trapped charged act as a "virtual gate," weakening the 2DEG until they are released.

- **Deep Traps**. The second Trapping is called Deep Traps in the Buffer Layer which capturing "hot electrons", particularly in traps caused by carbon doping in the buffer layer. These trapped charges also weaken the 2DEG, and may also cause long-term degradation to the device, indeed the Hot Electron are suspected to trigger a positive destructive feedback loop that will see the electrical field at the drain side increase to the trapped charge until device break.

In other words, when Vds is applied (usually upper than 450V but to be demonstrated device per device) the Rdson increase switching cycle after cycle until it reach a saturated value with the correspondent collapse of the current.

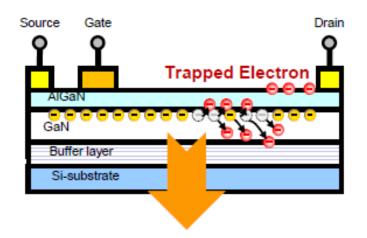

### **EFFECT: Dynamic Rdson and Current Collapse**

AIRB

### **Reliability Consideration**

- The Technology is qualified by running standardized stress test and by validating Life Test requirements.

- In other words, it's the results of detailed work on the understanding of failure mode, their acceleration and modeling, and a statistical framework to assure a minimum level of quality.

- The Silicon stress test are developed by JEDEC released 20 years ago and the qualification procedure has remained the same over the years and this is valid for the Silicon where the manufacturing, quality and reliability milestone have been achieved in the last decades.

- This is not completely applicable to emerging GaN Transistor where failure mode, activation energies and acceleration factor are likely different by than those used for Si.

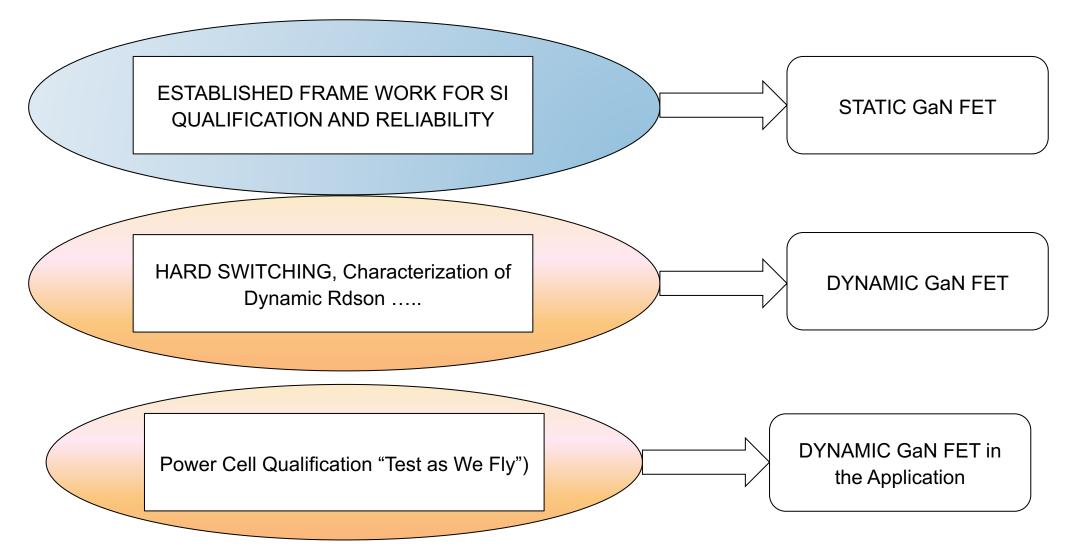

### AIRBUS Qualification Approach for the GaN Power

The AIRBUS idea is the following:

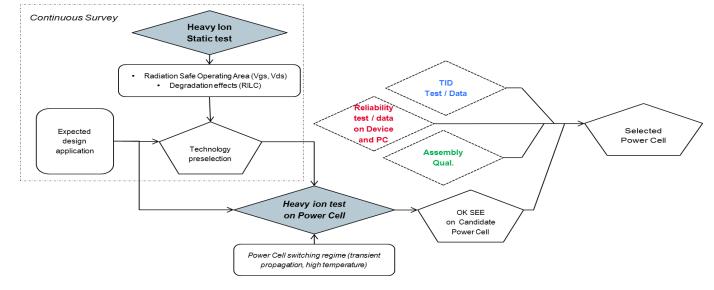

### Accounting Radiation for Power GaN

- GaN material is inherently radiation hardened material, however the Power GaN FET technlogy is identified to be sensitive to Single Event Effect (refer to NASA JPL Survey, JAXA Studies).

- High voltage commercial pGaN FETs presents failure to heavy ion already in the range of 50 % of their maximum rating.

- Lower voltage GaN FETs showed a much better reliability due to the reduction of E-Field strength and specific pGaN Gate stack.

- Radiation induced current leakage has been observed, risk can be assessed through degradation modelling.

- Tolerance to short circuit of Power GaN FET is expected as limited. Then not only GaN tolerance to static irradiation, but power cell tolerance to SET propagation and FET activation is to be assessed. Representative Power cell SEE test is considered as a key test for enabling GaN in Space.

- Concerning Total Dose Test, being the GaN Technology sensitive to trapping effect, it needs to be well correlated with the expected mission profile (switching, static regime,...). Separate the reliability mechanisms induced by trapping from TID effects. Risk related to TID is expected as low.

#### methodology for PowerGaN selection for Space Power.

## Conclusion

- GaN-FET: few normally-off GaN FET are already on the market, and less targeting hi-rel

- Disruptive changes in supply chain expected when the major (automotive) players enter the market

- Radiation (SEE) concern, particularly for higher voltages > 200 V

- Long-term reliability to be assessed

- Reliability test methodology and test methods currently being standardized

- European Market development.