# Small form factor Wirefree Die-On-Die WDoD<sup>™</sup> technology used in 3D modules evaluation

Pascal COUDERC

March 10<sup>th</sup>,2021

ESCCON 2021

- 1. Company introduction

- 2. Flow 2 details

- 3. WDoD process description

- 4. WDoD evaluation for space applications

- 5. Conclusion

#### 1. Company introduction

- 2. Flow 2 details

- 3. WDoD process description

- 4. WDoD evaluation for space applications

- 5. Conclusion

### **Corporate information**

Space electronics solutions provider

- French Company founded in 1995

- Locations:

- Buc, (Paris Area) France,

- People: 270 employees

Headquarters

Paris area. France

- Manufacturer of electronic products and System-in-Package for high reliability and high performance applications

- Production: 800 pcs / Week, delivery of 31 000 products in 2019

- More than 160 000 modules in space mid of 2019

- Business Regions: 35% Europe, 40% Asia, 25% North America.

- ESA and CNES approved manufacturing line for Space Applications

- **ITAR Free products.**

- Lines of space products: MEMORIES, INTERFACES, POINT OF LOAD, PROTECTION DEVICES, IP CORES, FPGA MODULE BASED ON NG-MEDIUM, MICRO-CAMERAS

- 1. Company introduction

- 2. Flow 2 details

- 3. WDoD process description

- 4. WDoD evaluation for space applications

- 5. Conclusion

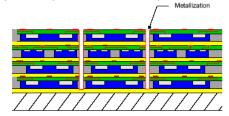

### **3D PLUS technologies overview**

Flow 1: TSOP → Memory

« SPACE QUALIFIED »

Ex 1: Computer core for THALES -July 2013 – Military applications

Ex 2: Leadless pacemaker for a European Customer - April 2013

« NON SPACE QUALIFIED »

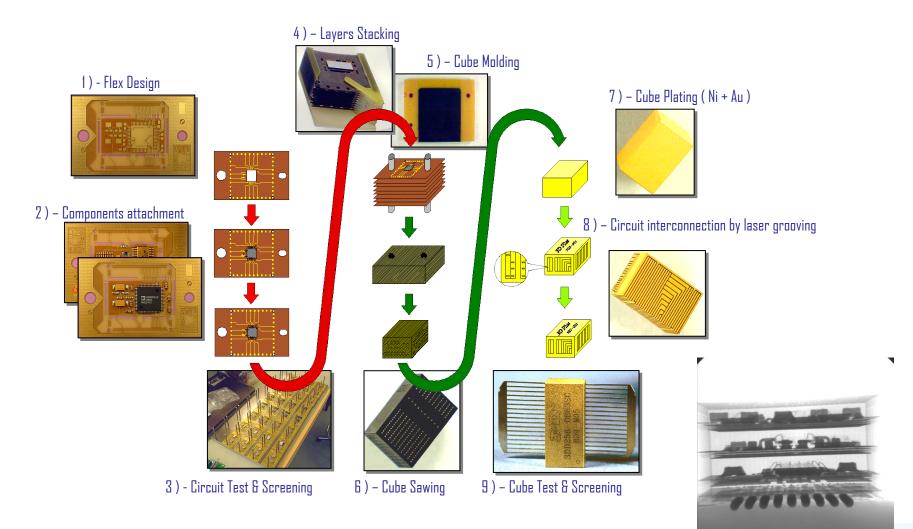

## Flow 2 Process

- 1. Company introduction

- 2. Flow 2 details

- 3. WDoD process description

- 4. WDoD evaluation for space applications

- 5. Conclusion

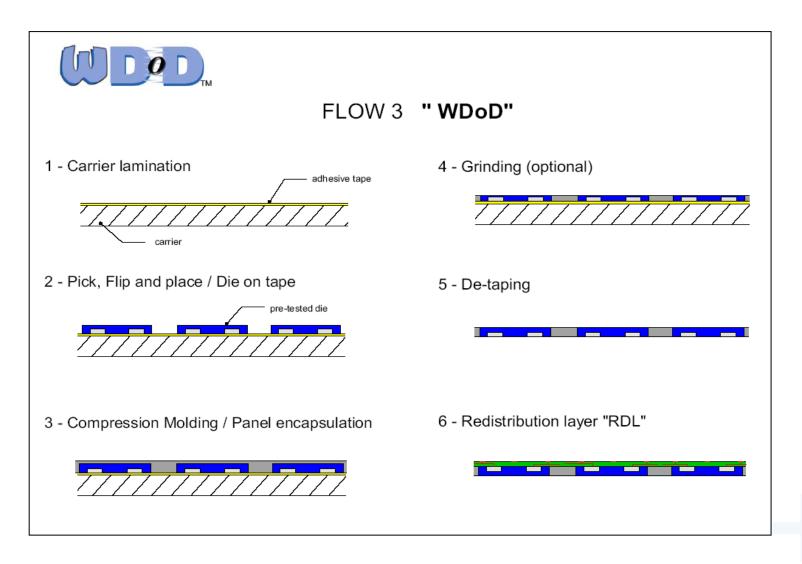

#### WDoD ™(1) initial criteria

- Use of multi sourcing wafers

- Stacking of 5 to 10 levels per mm

- Size: 200µm around the larger Die

- Stacking of Known Good Rebuilt Wafer (KGRW)

- Possibility of several dice of different dimensions of the same level

- Parallel processing/Panelization from A to Z

- Possibility to stack PCB levels (flow 2) and rebuilt wafers in order to optimize performances and costs

(1) Wirefree Die on Die – Trade Mark from 3D PLUS

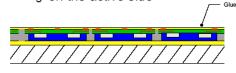

7 - Gluing on the active side

8 - Stacking of the "Known Good Rebuilt Wafer"

9 - Dicing of the rebuilt and stacked wafers

10 - Dicing street edges plating parallel process (electroless Ni + Au)

#### Laser patterning

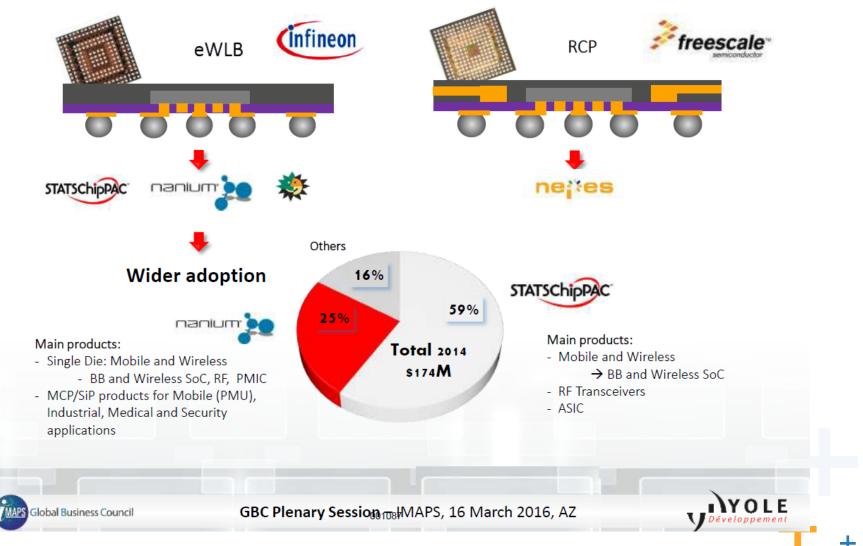

#### Fan-Out main technologies and actors

# First Fan-out WLP Technologies

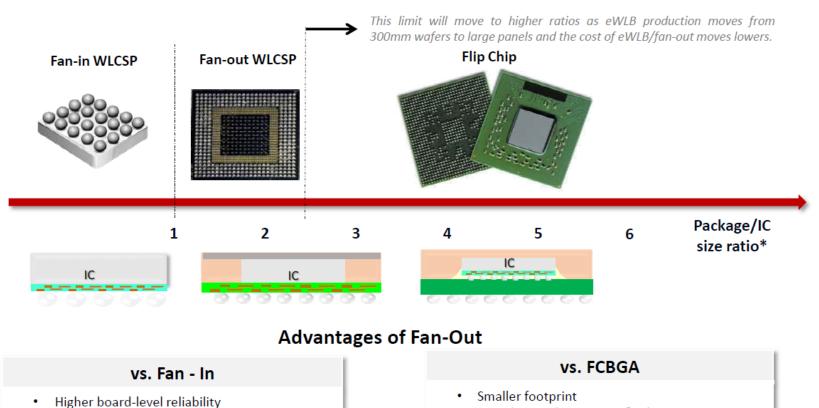

## Fan-Out position/Fan-In and Flip-Chip Fan-Out vs. Fan-In and Fight Conference and Extension Provide Provide

- Bumping is not limited to the die size, fan-out

- area beyond chip area limitation

- Built-in back-side protection (protection available for WLCSP as an option only)

- Lower thermal resistance

- Higher potential for SiP integration

#### Global Business Council

#### GBC Plenary Session makMAPS, 16 March 2016, AZ

No substrate/interposer

Shorter

Higher electrical performance

Higher potential for SiP and 3D integration

NYULE

Développement

interconnections

lower cost

Lower thermal resistance

thinner package

All Rights Reserved © 3D PLUS 2021 Confidential

Similar technology than standard 3D PLUS technology

Huge shrinkage allowing small form factor components

#### **PoP and WDoD package relative sizes**

- 1. Company introduction

- 2. Flow 2 details

- 3. WDoD process description

- 4. WDoD evaluation for space applications

- 5. Conclusion

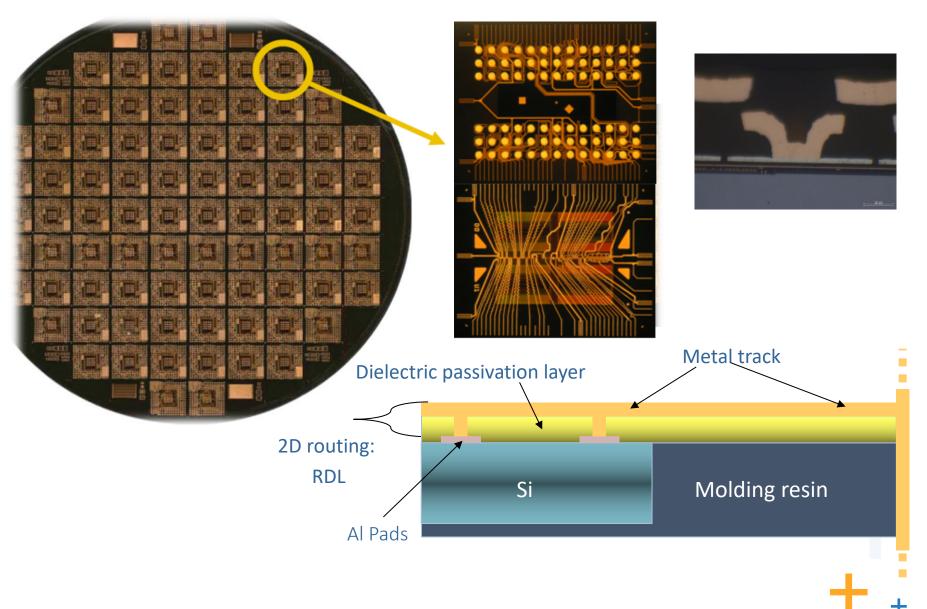

Ojectives

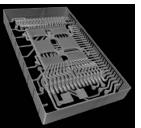

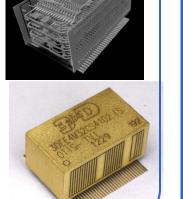

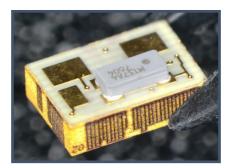

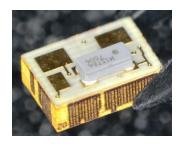

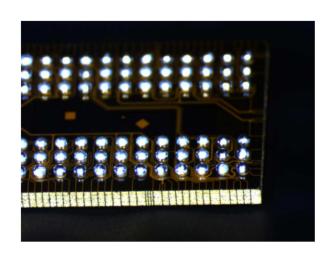

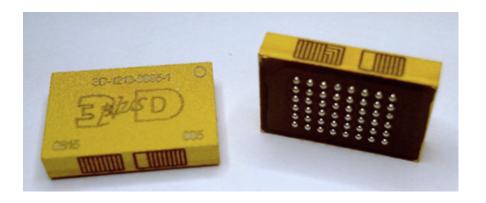

3D PLUS has developed and patented for several years the WDoD<sup>™</sup> process (Wire-Free Die on Die) for industrial applications (Quad-die DDR3 modules or modules including an FPGA, 2 mDDR). The photos below are examples :

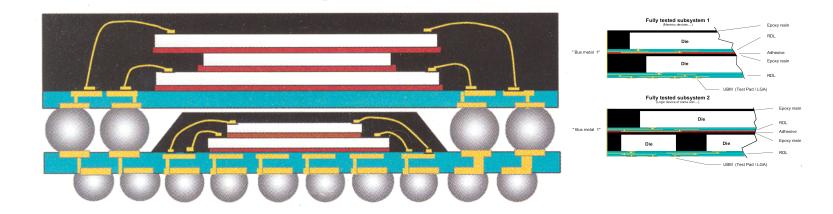

Until now this technology has not been evaluated and qualified for a space application. 3D PLUS, with the support of CNES (French government space agency), evaluated following the ESCC2566001 specification this process in order, among other things, to identify design rules and reliability.

-plus a HEICO company

- This 3D technology allows a form-factor reduction which can be of high interest for space applications

- Main interest is the reduction of each level thickness :

- -from 1-1.2 mm ( with die on PCB ) versus 0.2 -0.3 mm ( WDoD™ )

- Others advantages are:

**Benefit**

- the connexion lengths reduction and a good alternative to flying leads PCBs.

- No lead free packages inside the module

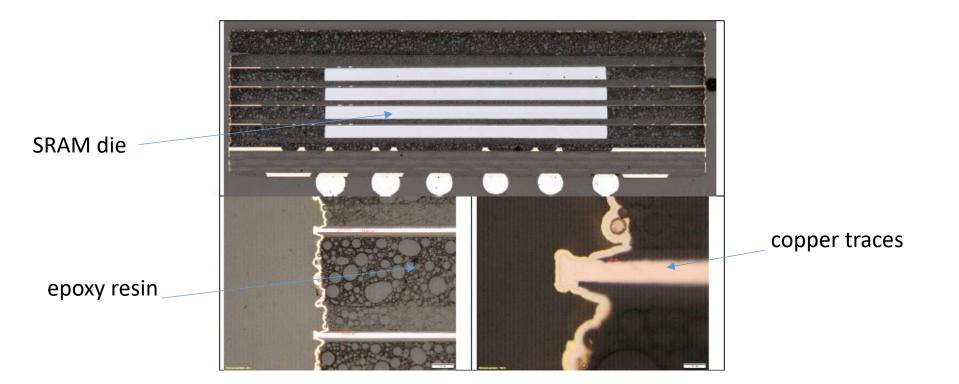

Test Vehicles : SRAM Module

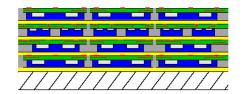

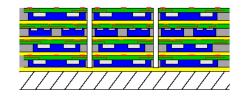

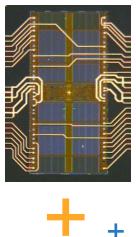

A demonstrator of 4 levels of SRAM dies has be designed and manufactured for this evaluation **MODULE**

- The SRAM module containing four chips stacked is manufactured using WDoD technology.

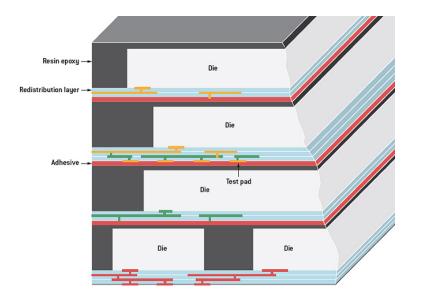

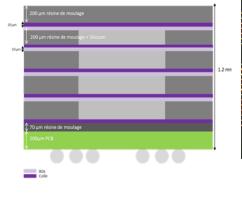

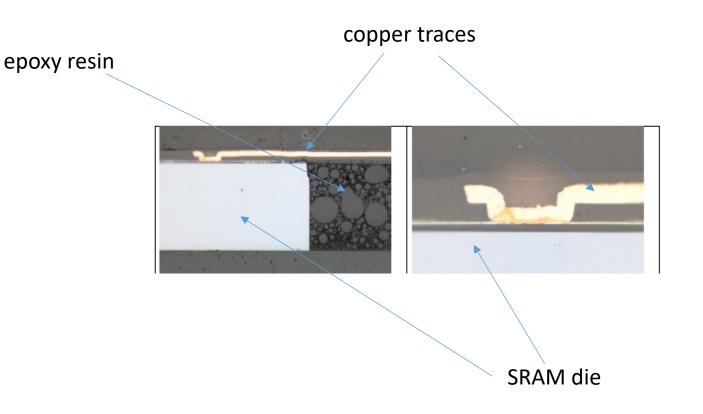

- There is a 200µm thick resin cover, a 200µm connection level (PCB) as well as 4 levels "reconstituted wafer" with RDL. The RDL level is common to each of the 4 levels.

- 2 providers have been tested

- Module dimensions are 6,5 x 9,5 x 1,7 mm

- Module bus metal laser pitch is 250 µm

#### STEPS

- 1 level and module demonstrators manufacturing and electrical continuity tests

- Pré -evaluation tests with failure analysis

- MSL 5

- Thermal cycling TCT 1500 cycles (-55;+125°C)

- High Temperature Storage HTS 2000Hrs @125°C

- THB 1000 hrs 85°C;85 %HR

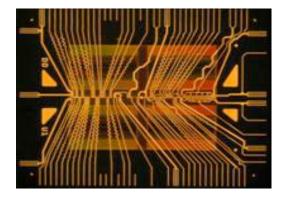

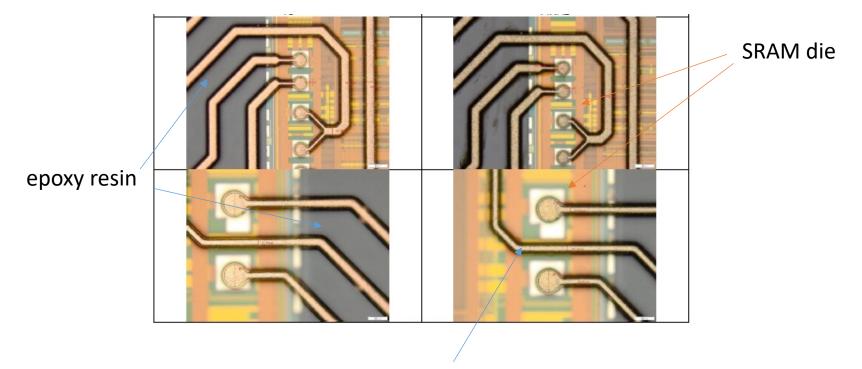

Component level Tests : 1 level 2D panel with RDL

#### 2D panels evaluation was successfull

2D level top view

copper traces

2D level cross section

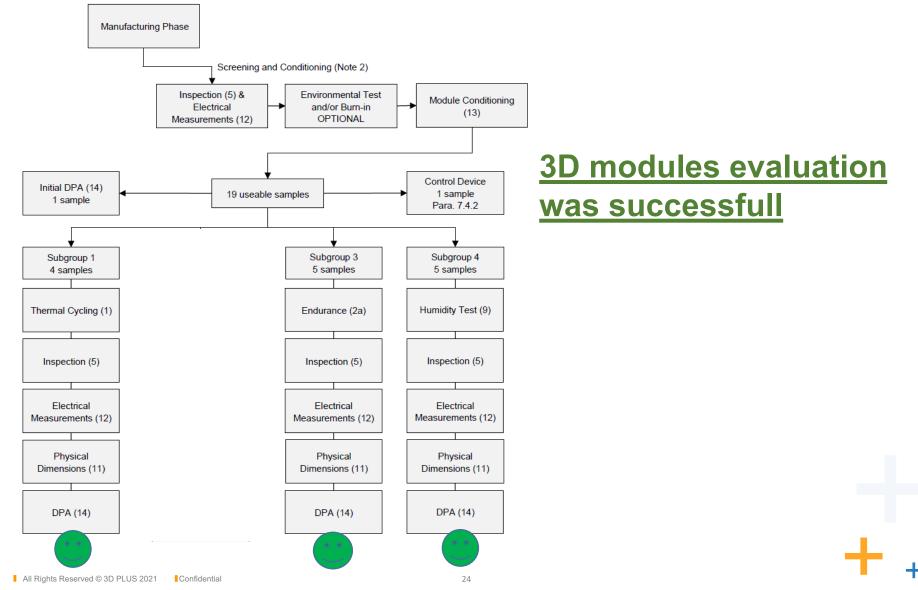

Module level Tests

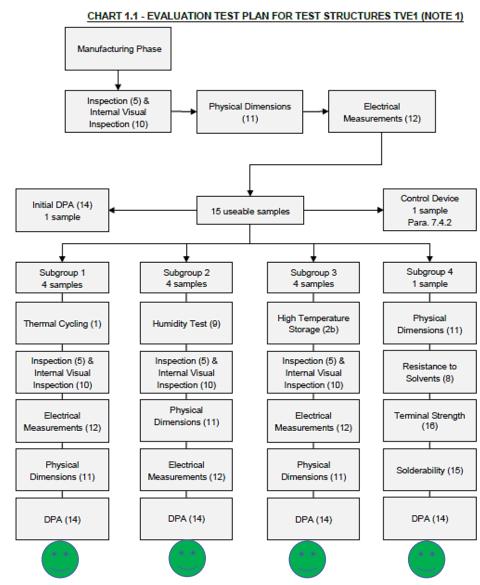

#### CHART 1.2 - EVALUATION TEST PLAN FOR TEST STRUCTURES TVE2

3D module cross section

- 1. Company introduction

- 2. Flow 2 details

- 3. WDoD process description

- 4. WDoD evaluation for space applications

- 5. Conclusion

#### **Conclusion- Next steps**

- A 3D demonstrator consisting of 4 levels of SRAM dies was designed. Two sub-contractors in charge of manufacturing the RDL (Redistribution Layer) have been selected.

- A batch of demonstrators was manufactured and submitted with success to evaluation testing plans based on the ESCC 2566001 specification

- Next steps scheduled through a new RT funded by CNES :

- Process and materials modification for more heterogeneous module including Fan-Out levels with 2 copper layers and PCB levels

- 3D PLUS acknowledges CNES for his support in this RT