March, 9<sup>th</sup>, 2023

Confidential Information

# AGENDA

MNEMOSYNE: Magnetic non-volatile Random Access Memory for space with serial interface

### INTRODUCTION

- $_{\odot}$  What is MNEMOSYNE project ?

- $\circ$  Project pillars

- Advantages forseen

### **FIRST DESIGN**

- $_{\odot}$  The test vehicle (TV)

- Rad-hard design techniques

- $_{\odot}$  Tests and results

### PRODUCTS

- $\circ$  Prototype

- $\circ$  Architecture

- $\circ$  Presentation

- $\circ$  Positioning

- CONCLUSION

# INTRODUCTION

MNEMOSYNE: Magnetic non-volatile Random Access Memory for space with serial interface

Context: Enhance EU independence on the space market

Funded by EU Horizon 2020 research and innovation program

Goal: Design and prototype the new generation of rad-hard high density NVM with serial interface based on most-advance and matured technology

Applications:

- $\circ$  **Boot code storage** for microcontrollers and microprocessors

- o FPGA configuration bitstream storage

Consortium members:

3

# **MNEMOSYNE** project

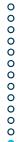

Project pillars

000000

0000

I Confidential

# INTRODUCTION

Advantages forseen

- STT-MRAM technology provides SEU immunity to memory cell.

- FD-SOI (Fully-Depleted Silicon-On-Insulator) process brings SEL immunity.

- 22nm FD-SOI provides: up to 40% die scaling, and nearly 70% power saving relative to the standard

28nm node, or similar power efficiency to FinFET technology.

- 3D PLUS technology is used to increase the device density.

# FIRST DESIGN

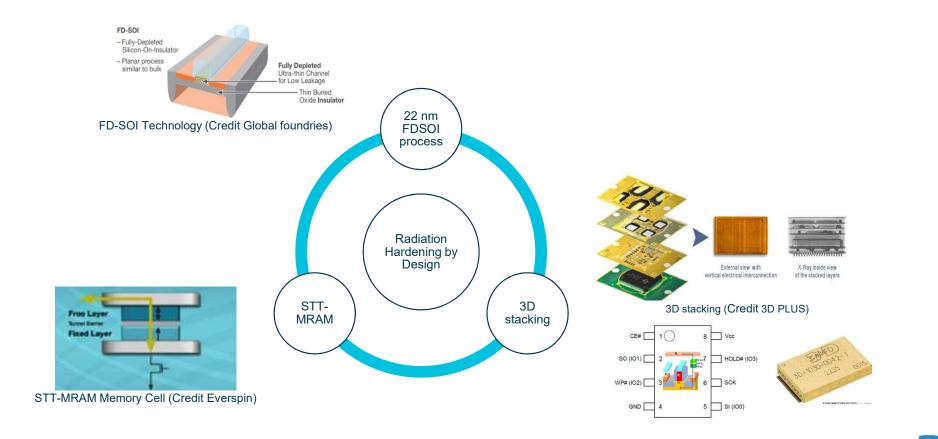

Test vehicle

- A 64 Mb test vehicle was manufactured and tested during 2022 Summer.

- $_{\odot}\,\text{STT-MRAM}$  memory arrays with embedded ECC

- o A memory controller

- $_{\odot}\,A$  fuse-based read-only configuration memory

- A Power Management Unit (PMU)

- $_{\odot}$  Two SPI interfaces (1.8 V and 3.3 V).

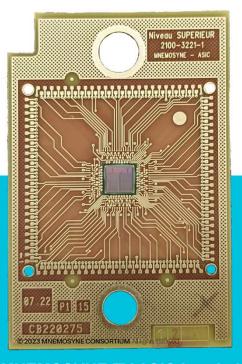

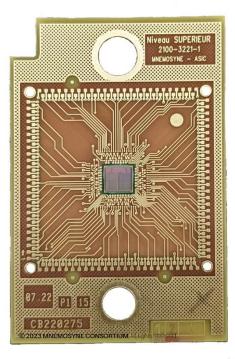

Test vehicle module

## **FIRST DESIGN**

Test vehicle: Rad-hard design techniques

- Rad hard design techniques on control logic and interfaces

- Redundancy, restricted cell sets on SEU critical parts.

- $_{\odot}\,\text{SET}$  immune on clock and reset trees

- $\circ$  Glitch filters on strategic nodes

- $_{\odot}$  Derating accounting for device aging and TID.

7

$\circ$  Leakage reduction (body bias, process)

## **FIRST DESIGN**

**Results summary**

TID > 100 krad(Si) SEL/SEU LETh > 60 MeV.cm<sup>2</sup>/mg 1000h Life test passed with 30 measurements QSPI/SPI interface validated

MNEMOSYNE TV ASIC bonded

# PROUCTS 128 Mbit Prototype

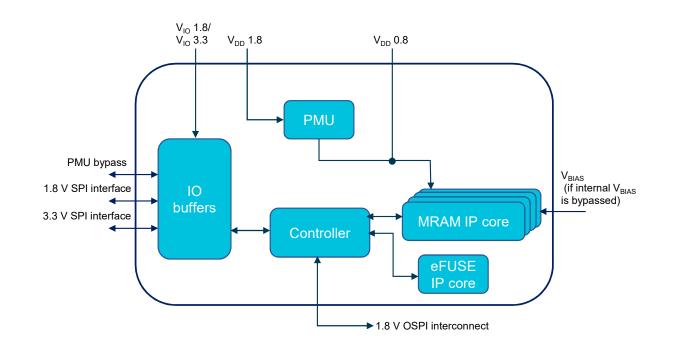

Design update

- Goals:

- Density increase

- $\circ$  TV errors correction

- EEPROM interface

- Manufacturing in progress

- Available by Q2'23

128 Mbit prototype architecture

000

# PRODUCTS

Architecture

000

Ó

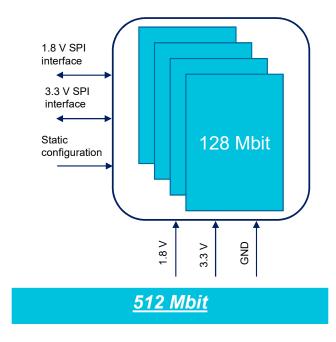

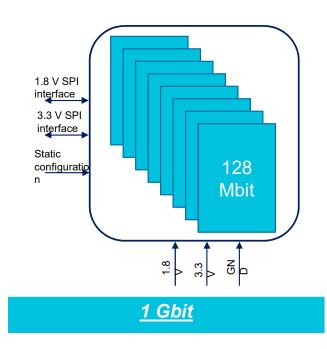

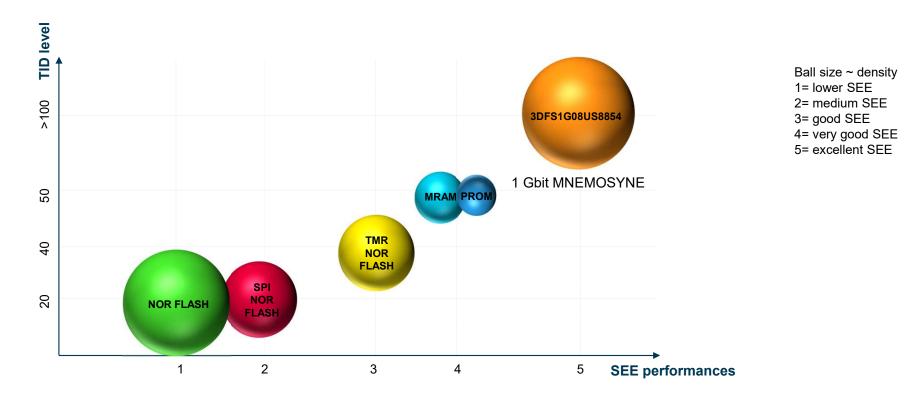

# **PRODUCTS** Up to 1 Gbit rad-hard NVM with serial interface

### **KEY FEATURES**

- $_{\odot}\,$  512 Mb, 1 Gb density

- $_{\odot}\,\text{Up}$  to 100 MHz

- $\circ \text{Embedded ECC}$

- $\circ$  Power management embedded

- o 1.8 V SPI interface (3.3 V optional)

- SPI, QSPI, DSPI, OSPI modes supported

- $\circ$  100 k P/E cycles

- $\circ\,\text{20}$  years data retention

### RADIATION PERFORMANCES

TID > 100 krad(Si)

SEL > 60 MeV.cm²/mg

SEU > 60 MeV.cm²/mg

SET > 60 MeV.cm²/mg

SEFI > 60 MeV.cm²/mg

The SEE LET threshold would be tested in other facilities with 80 MeV.cm<sup>2</sup>/mg target

# **CONFIGURATION MEMORIES**

### 3D PLUS portfolio update

# CONCLUSION

- The Next Generation Radiation Hardened space serial Non Volatile Memory up to 1Gb density with proven TID >100Krad(si) and SEL/SEU LET threshold > 60MeV.cm<sup>2</sup>/mg.

- This product while enhancing EU independence on the space market will be the best in class of program/configuration memory combining that level of reliability with such density.

- 512 Mbit/ 1 Gbit density modules available by Q4 '23

- Authors would like to thank the European Commission and all the members of the consortium that are driving this project.

- MNEMOSYNE project used the results of another Horizon 2020 project named EFESOS.

# www.3d-plus.com

408 rue Hélène Boucher 78530 Buc - **FRANCE** +33 130 832 650

151 Callan Ave, Suite 310 San Leandro CA 94577 - **USA** (415) 316 0981

### OUR MISSION IS THAT YOU ACHIEVE YOURS