# Radiation Test-Bed for High Capacity Memory Components

# Final Presentation of ESTEC Contract No. 11356/95/NL/FM, CCN-7

**TU Braunschweig**

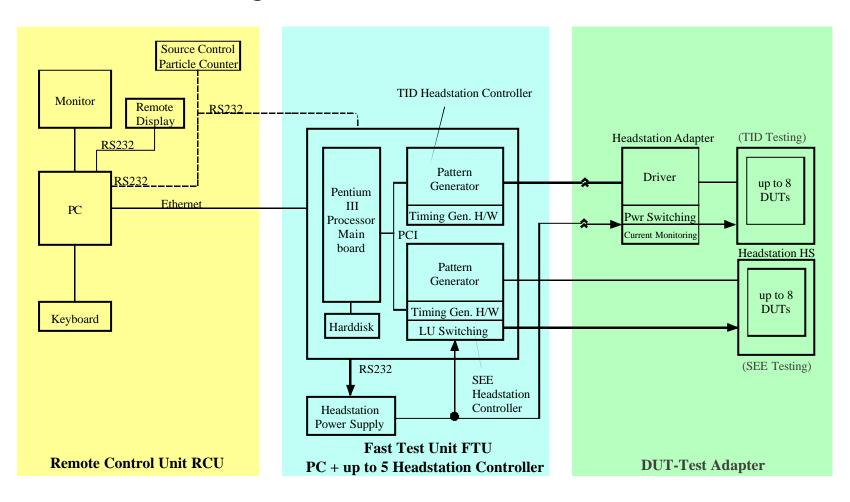

Test-Bed Design Approach

Test-Bed design mainly driven by three requirements:

- in situ testing

- mandatory to detect and isolate special functional errors of state of the art devices, e.g. Flash Memories, FIFO's etc

- real time event detection and recording

- supports isolation of special failure types, e.g. cluster errors (simultaneous multibit errors) or partial SEL

- supports complete testing of large capacity devices within reasonable test time

- flexible and easily adaptable platform

- more and more sophisticated "memory systems on a chip" are available and a test bed needs to be adaptable to these devices with special functions in a short time frame

**Derived Design Characteristics**

- PC based System with special Plug-In Cards to implement real time functions (Fast Test Unit)

- TID and SEE Test capabilities and requirements achievable with the same basic equipment

- Adaptable Device Control and Test Patterns implemented in Firmware within configurable high performance FPGA's

- Remote control of in-situ tests supported via network

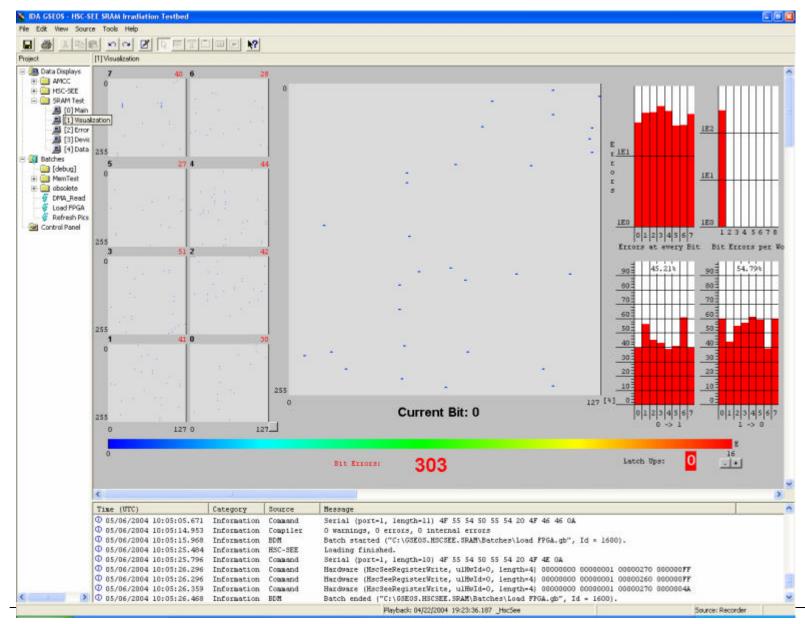

- Quick-Look data analysis to support in-situ tests

#### Block Diagram of In Situ Radiation Test Bed

## Fast Test Unit

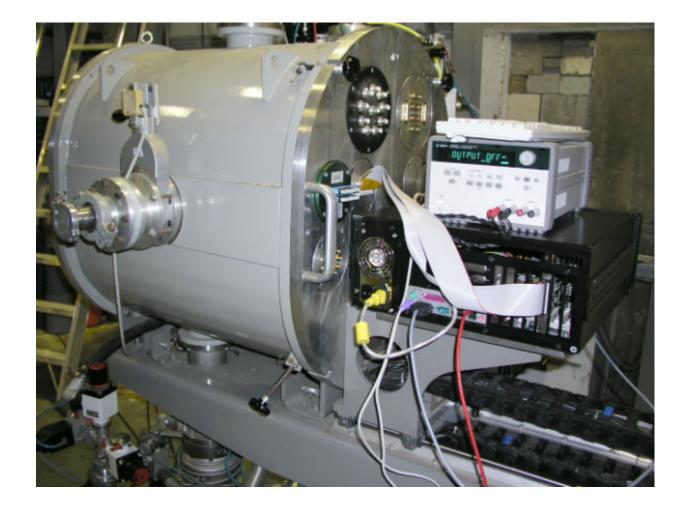

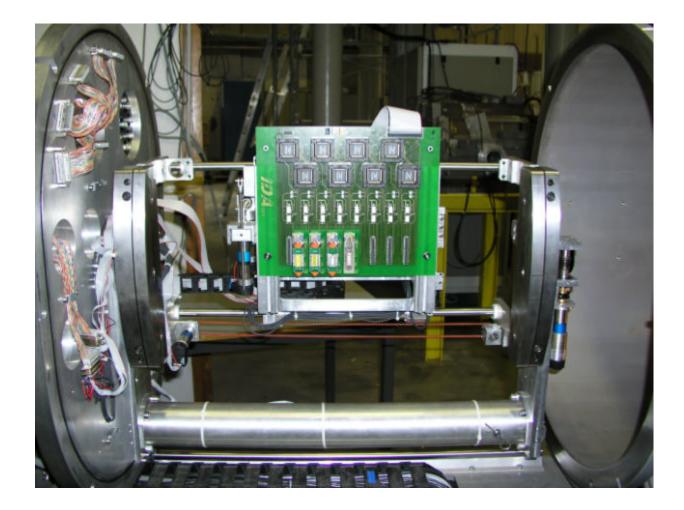

#### SEE Headstation with 4 DUT's

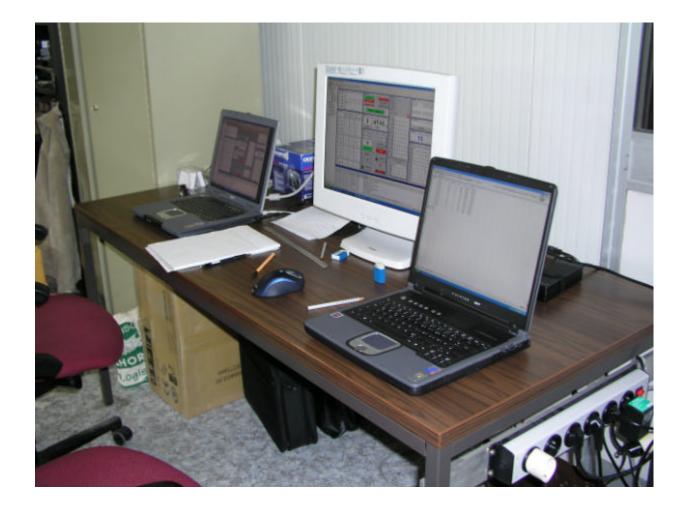

## Remote Control Unit

#### **Performance Characteristics**

| Address Pattern      | Read Background, Write Background, Chessboard, Marching, MOVI, |

|----------------------|----------------------------------------------------------------|

| Data Pattern         | Constant (128 bit), Counting (64 bit), Pseudo-Random(64 bit),  |

| Error Buffer         | 128k Error Records                                             |

| Error Record Storage | limited to harddisk capacity                                   |

| LU Detection         | for both SEE-Test and TID-Tests, threshold adjustable          |

| Current Measurement  | 1 mA resolution for SEE-Tests, 10µA resolution for TID-Tests   |

| Devices              | all kind of memory devices                                     |

| Data Width           | up to 16 Bit                                                   |

| Address Width        | 28 Bit static, 20 Bit (row) + 20 Bit (column) dynamic          |

| Supply Voltage       | 2 – 6 Volts                                                    |

| Current              | up to 200mA per device                                         |

| Min. Cycle Time      | currently 20 ns, 10ns in update version                        |

| Device Count         | 8 per Headstation, up to 4 Headstations connectable            |

|                      |                                                                |

Distance Tester – Headstation1,5m (SEE-Tests), 5m (TID-Tests)Distance Tester – Operating PCup to 100m (standard ethernet)

**Test-Bed Verification**

- Pre-Verification on System Level

- a) with Laser Beam Test Set up (at IDA)

- b) with Flash Memory Devices (at UCL)

- SEE-Test Verification on System Level

SEE Testing of SRAM devices (at UCL)

- TID-Test Verification

- TID Testing of SRAM devices (to be performed at ESTEC)

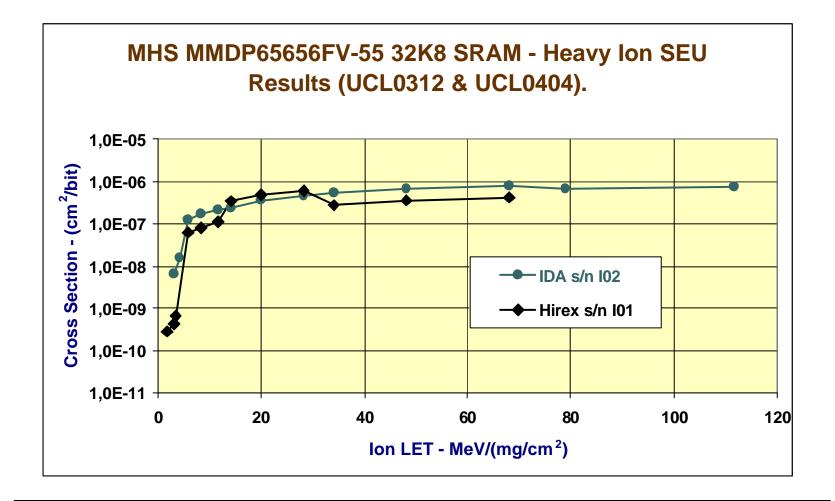

# SEE Test Results

-11-

#### Summary

- Test Bed provides in-situ and real time SEE and TID Test capabilities for

- Flash, SRAM (already implemented)

- SDRAM, DDRAM (to be implemented soon)

- Special devices (FIFO's, DPRAM's already implemented, others TBD)