### EWP-1649

# A STUDY OF DIGITAL-TO-ANALOG CONVERTERS FOR SPACE APPLICATIONS

Young Graduate Trainee Report

February 1992

Christoph T. Panhuber (QCA)

Approved by: Bengt Johlander (QCA)

### NOTE

ESTEC Working Papers are non-official documents intended for the presentation of material for discussion purposes only. The contents of this document do **NOT** represent approved ESA procedures, practices, or standards. This document, or any part of it, may not be issued in any form other than the present without the approval of the European Space Agency.

### **Foreword**

The study described in this report was performed in the Young Graduate Trainee scheme in ESTEC during march -91 to february -92 within the Radiation Effects and Analysis Techniques Unit.

The topic for the study was derived from fruitful discussions with Scientific Institutes and their contractors, designing and building scientific instruments for ESA space projects as well as several semiconductor manufacturers.

It is hoped that this report will become useful for both parts selection purposes as well as for semiconductor manufacturers who assessing the potential of the space market.

Bengt Johlander Radiation Effects and Analysis Techniques Unit, Components Division ESA/ESTEC.

### **Abstract**

A brief market survey of commercially available low-power Digital-to-Analog Converters is presented. Several interesting products were selected to be subjected to radiation testing. Total dose tests were performed using the ESTEC <sup>60</sup>Co-source; depending on device performance devices were irradiated to total doses of up to 100 krad.

Test strategies to verify the static and dynamic performance after irradiation were developed; test results are discussed and interpretations as to the possible mechanisms that lead to degradation and finally to device failure are given.

It was found that parts from different manufacturers show widely varying radiation tolerances. In most parts threshold voltage shifts of the n-MOSFETs were found (charge trapping in the gate oxide); increased leakage due to poor field oxide quality was another common failure mechanism. Best results with virtually no degradation in performance up to a total dose of 70 krad was found for the Sipex 7541A and the Sipex 7584 current output DACs.

# **INDEX**

| 1. Introduction                                                                                                                                 |                   | 1   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|

| 2. Basic working principles of Digital-to-                                                                                                      | Analog Converters | 1   |

| 3. Market survey                                                                                                                                |                   | 3   |

| 3.1 General                                                                                                                                     | 3 .               |     |

| 3.2 Recent trends                                                                                                                               |                   |     |

| 3.3 Brief overview                                                                                                                              | 4                 |     |

| 4. Choice of devices                                                                                                                            |                   | 11  |

| 5. Test setup and strategy                                                                                                                      |                   | 13  |

| 5.1 Static Tests                                                                                                                                | 14                |     |

|                                                                                                                                                 | 17                |     |

| 5.3 Dynamic Testing                                                                                                                             | 17                |     |

| 3.1 General 3.2 Recent trends 3.3 Brief overview  4. Choice of devices  5. Test setup and strategy  5.1 Static Tests 5.2 Parametric Testing  17 |                   | 20  |

| 7. Test results                                                                                                                                 |                   | 22  |

| 7.1 Burr Brown 7802                                                                                                                             | 22                |     |

| 7.2 Sipex 7584C                                                                                                                                 | 43                |     |

| <u> </u>                                                                                                                                        | 58                |     |

|                                                                                                                                                 | 69                |     |

| 7.5 Burr Brown 7541A                                                                                                                            | 76                |     |

| 7.6 PMI 7541A                                                                                                                                   | 81                |     |

|                                                                                                                                                 | 83                |     |

|                                                                                                                                                 | 88                |     |

| 7.9 Sipex 7541A                                                                                                                                 | 96                |     |

| Acknowledgements                                                                                                                                |                   | 103 |

| Bibliography                                                                                                                                    |                   | 104 |

### 1. Introduction

As DACs become more and more important in many electronic applications, there are a lot of different companies producing them and competing for their share of the market.

High-precision, high-resolution DACs (16 - 20 bits) for audio purposes (CD-players) and ultra-high speed DACs (settling times below 25ns) for video applications have been the latest big successes for that kind of device.

But with the variety and flexibility of available DACs increasing, the number of possible applications is steadily on the rise. DACs are used e.g. in the design of microprocessor-controlled filters, programmable gain or attenuator circuits, voice synthesizers, process control actuators and arbitrary signal generators.

Due to rapid progress in applying power-efficient CMOS technology for DACs and the successful combination of bipolar and CMOS elements on a monolithic chip, further use of these devices for an increasing number of space applications seems to become more and more interesting as well.

The scope of this work was to give a brief market survey of available D/A Converters and then apply space-related selection rules to choose a number of devices that were subsequently subjected to total dose radiation testing using the ESTEC <sup>60</sup>Co radiation source.

It is also intended to stress the importance of radiation effects when electronic components are used for space applications. Sometimes considerations of these effects are implemented into a project design at a rather late stage. Keeping in mind that space is a very hostile environment ([1],[2]) and defining the mission radiation profile as early as possible (with appropriate consequences for device selection and/or shielding requirements) may save a lot of unnecessary work.

# 2. Basic working principles of Digital-to-Analog Converters

The general purpose of a DAC is to convert a quantity specified as a binary number to a current or voltage proportional to the value of this number. There are several popular methods:

- 1) Connecting scaled resistors to the summing junction of an OP-AMP. Disadvantages: Requires a number of high precision resistors of widely different values, which is almost impossible to achieve for a larger number of bits (for a 12 bit DAC one needs a range of resistor values having a ratio of 2000:1)

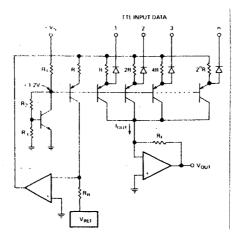

- 2) Scaled current sources: The currents can be generated by an array of transistor current sources with scaled emitter resistors (see figure 2.1) In cases where a current output is sufficient this approach has the advangtage of being very fast; bipolar circuits are rather power-hungry, though.

Figure 2.1: Weighted current source D/A Converter

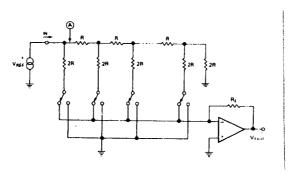

3) R-2R resistor ladder network: Working very similar to the method of scaled current sources, it is the most elegant, most widely used technique. The working principle can be seen in figure 2.2.

Figure 2.2: R-2R ladder D/A Converter. Very often the OP-AMP has to be added externally; the feedback resistor is always included in a commercially available DAC to guarantee identical temperature coefficients of all resistors.

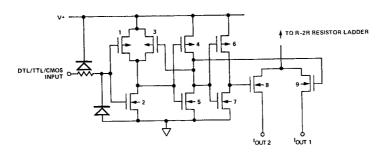

Only two different resistor values are needed, from which the R-2R network generates binary scaled currents if the network is connected to a voltage reference. These currents are constantely flowing and they are switched either to ground or the "virtual ground" point of an OP-AMP by CMOS switches at the end of each leg of the resistor ladder (12 legs for a 12-bit DAC). The use of CMOS switches means that this method is very power-efficient. A possible configuration for the switches is shown in figure 2.3:

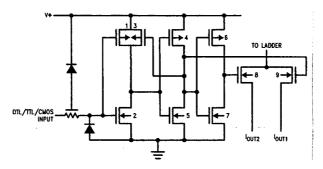

Figure 2.3: CMOS current switches with input voltage level shifters

It allows for DTL/TTL/CMOS digital input levels by using internal voltage level shifters; n-MOS transistors 8 and 9 are connected to the end of a leg of the resistor ladder in such a way that one of them is always in its conducting, the other one in its nonconducting state. The designer has to take care to include the "ON"-resistance of the n-MOS transistors in the total resistance value of the respective R-2R ladder leg in order to preserve accuracy.

In fact, the overwhelming majority of commercially available DACs uses the concept of the R-2R ladder. The most simple DACs like the 7541 type consist of an R-2R ladder network and unbuffered digital inputs driving the CMOS switches at the end of the ladder legs. A precision voltage reference has to be added externally, just as the OP-AMP converting the output current into a voltage (two OP-AMPs are necessary for bipolar voltage output). What is included in even the most simple current output DACs is an internal feedback resistor to be used with the OP-AMP. This is very important because it is matching the resistors of the R-2R ladder in value and in temperature coefficient; the use of external trimpots to adjust gain and offset therefore usually increase the gain temperature coefficient and should be avoided if possible.

Current output DACs normally have a settling time below 2us; for video applications settling times of about 20ns are achieved. If, however, the current has to be converted to a voltage the settling time will increase considerably even if a fast OP-AMP is used.

# 3. Market survey

### 3.1 General

The market for DACs with more than 12 bit resolution is clearly dominated by the major US semiconductor manufacturers (Analog Devices, Burr Brown, Harris, Siliconix, Sipex, Maxim) which all claim to do their own fabrication. European manufacturers are almost nonexistent (some Philips and SGS Thomson parts available) and Japanese companies also play only a minor role.

The situation is different for DACs with less than 12 bits and Video DACs which have very short settling times and resolutions up to 8 bits (some parts having a resolution of 10 and even 12 bits were introduced recently): here Japanese (Fujitsu, Sony, NEC, Hitachi) and other European companies (notably GEC Plessey) can offer a broad range of products as well [D1]

### 3.2 Recent trends in DAC products

Bipolar devices, which have been the early DACs, are more and more being replaced by CMOS DACs, i.e. the current switches implemented in the most popular designs are CMOS switches. One obvious advantage is lower power consumption and high speed; as the physical dimensions of CMOS transistors are becoming smaller and smaller, it is also possible to include an ever increasing number of logic and buffer elements on one chip, increasing the flexibility and making it easy to create interfaces to other logic chips. A major effort of all the companies involved on the market has been to make DACs compatible to a wide range of microprocessors and Digital-Signal-Processing (DSP) devices. This required to incorporate various types of latches in different architectures (12-bit single, 8+4-bit, 4+4+4-bit) and the necessary control logic into their design.

Finally some companies developed production processes which made it possible to combine analog and digital circuitry on the same chip. In this way the OP-AMPs used to convert a

current to a voltage can be included in the device. Some companies, however, switched to hybrid devices to achieve this.

Some examples of the ever increasing complexity of devices will be given in the chapters dealing with the individual manufacturers.

Another goal that is pursued by most manufacturers is the trend to reduce the power supply voltage from +15V (or +/-15V for bipolar output devices) to +5V (+/-5V). In fact, most of the devices that have only recently been introduced to the market operate on 5V supplies. This might have some influence on radiation tolerance as lower voltages allow for the use of thinner gate oxides to be used.

Collecting information as to the exact nature of the manufacturing process, planned changes of processes now in use etc. turned out to be a rather tedious task as many companies are rather uncooperative when asked about these details. In a complementary study of Analog-to-Digital converters (ADCs), another author nevertheless made great efforts to extract exactly that kind of information from major companies. As his questions were mostly directed at successive-approximation ADCs, which have a built-in DAC as one of their major building blocks, the information he got is most likely also the current state of DAC technology. For that kind of information the reader is referred to this report [3].

A final fact to keep in mind is that new devices are being developed in rapid succession these days and appear on the commercial market almost every month. A close observation of these developments is therefore absolutely necessary.

# 3.3 Brief overview of the product line of major companies

### ANALOG DEVICES

This company seems to offer the largest variety of DACs. In fact, in the 1990 databook already 87 different types of devices are offered. They range in resolution from 4 to 18 bits, have settling times from 5ns (4-bit video DAC) to 40us (high-precision 18-bit DAC) with widely varying degrees of functional completeness and interfacing compatibilities.

Analog's so called "LC<sup>2</sup>MOS process" (Linear Compatible CMOS) allows for the combination of precision bipolar circuits and low-power CMOS logic on the same monolithic chip. As a consequence, more recent products include even a couple of OP-AMPs in addition to already rather complex logic circuits.

To give an impression of what Analog Devices can offer, the block diagrams of a few products are presented.

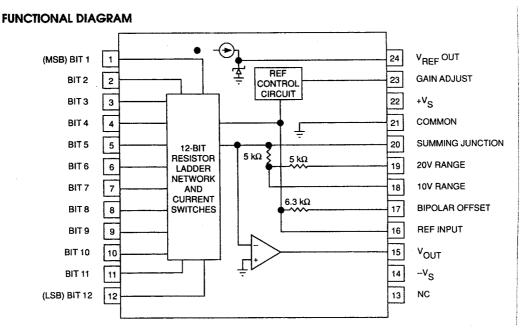

### **AD7541A**

This is an example of the simplest form of a current output DAC. It is also an industry standard, with many other manufacturers second-sourcing Analog Devices on this device. As can be seen in the circuit schematics below, it only consists of an R-2R resistor ladder and CMOS current steering switches with level shifters so that the inputs are DTL/TTL/CMOS compatible. No input or output buffering is available, and a precision voltage reference and an OP-AMP (for current-voltage conversion) have to be provided externally. The OP-AMP feedback resistor is included, however.

This configuration will be referred to as a "basic DAC".

#

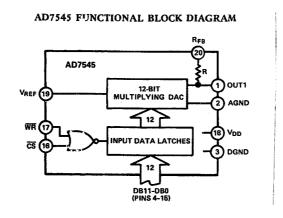

### AD7545

A "basic DAC" with buffered digital inputs and the accompanying, simple control logic.

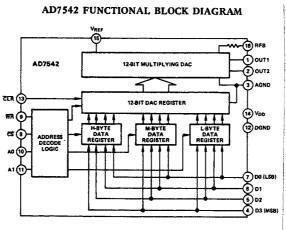

### **AD7542**

A "basic DAC" having two stages of input buffers to allow for easy microprocessor interfacing.

### AD7548

A "basic DAC" with double-buffered inputs and the necessary control logic. It also includes a voltage reference and an output OP-AMP (voltage output).

# AD7548 FUNCTIONAL BLOCK DIAGRAM VREF 19 R-2R LADDER DATA OVERRIDE DAC REGISTER DAC REGISTER DAC SEGISTER DATA STEERING LOGIC DATA OVERRIDE DATA OV

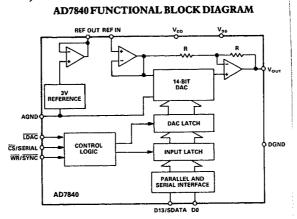

### AD7840 (14-bit DAC)

It provides double-buffered inputs wherein data can be loaded serial or parallel, determined by the setting of the control logic. Also included are a buffered 3V-reference and two output OP-AMPs for bipolar output when using +5V and -5V supplies (also operates from a single +5V supply in unipolar mode)

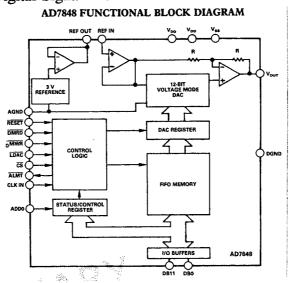

### **AD7848**

basically like the AS7840, but also including a FIFO (first-in, first-out) memory for easy interfacing to high-speed Digital Signal Processors.

### **BURR BROWN**

Another important manufacturer, although the range of available products is smaller. The main strength seems to lie in Audio, Communication and DSP DACs. Again the trend to include precision analog circuitry monolithically on one chip can be seen: quite recently a number of rather fast voltage output DACs appeared on the market, including voltage reference, latches and OP-AMPs (e.g. DAC813). Unfortunately their power dissipation is rather high.

Recent developments are devices with a single +5V power supply sometimes including more than one DAC on a single chip. A good example for the latter is the

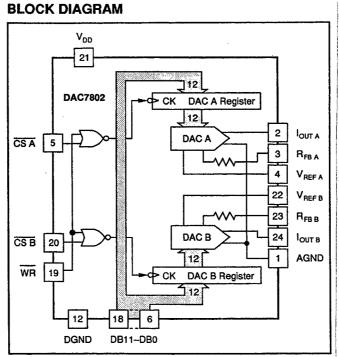

### **DAC7802**

It features two basic DACs whose individual latches share one set of input pins. The necessary write control logic enables the user to address the latches either individually or simultaneously.

Burr Brown is also second-sourcing the AD7541A, which was chosen as a test object for irradiation testing.

### **Harris**

It seems as if Harris does not play a major role in the market for DAC products. They offer a rather limited choice of DACs which are older types that have been on the market for some time. No recent developments have been released to the author's knowledge.

Harris, however, is an important manufacturer of rad-hard analog and digital devices and therefore is of potential interest. Their version of the AD7541 was included in the tests.

### **Sipex**

Although Sipex is also second-sourcing the popular 7541A monolithic current-output DAC, it pursues a rather independent policy with a product range that is rather unique. Their focus is mainly on complete, high-end products, combining many building blocks into one chip, offering resolution up to 18 bits. Most of their DACs feature voltage output.

However, instead of using monolithic designs, a large part of the available devices is made up of hybrids (note that Sipex acquired Hybrid Systems, another manufacturer specialising in hybrid designs, a few years ago). Therefore their power consumption is rather high (approx. 300mW for a simple voltage output DAC). Their recent new developments seem to indicate that also Sipex recognizes the trend towards monolithic devices: a good example is the new SP DAC87, a complete monolithic DAC with voltage reference and OP-AMP, but no input latches.

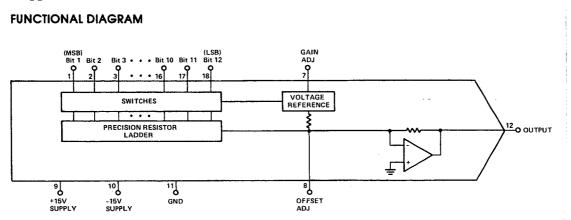

### SP DAC87

Despite its slow settling time of 50us for a full scale step, the Sipex DAC356-12 was chosen to be tested because the manufacturer claimed that its power consumption was only 70mW. (for all test devices it turned out to be about twice as much, however).

It is a hybrid voltage output DAC including Voltage reference and an OP-AMP operating on +/-15V supplies.

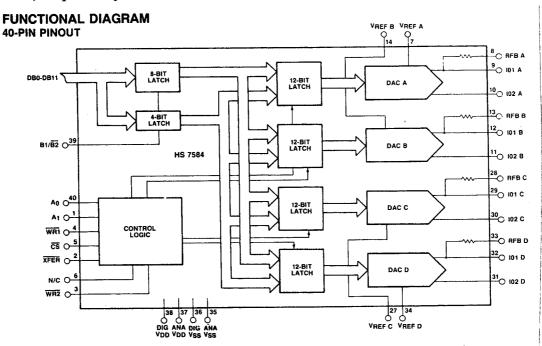

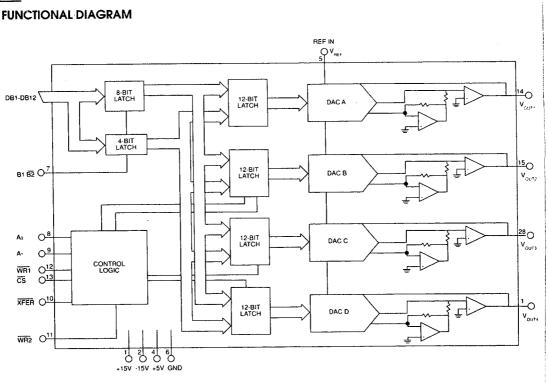

### HS7584

Another test candidate was the monolithic HS7584 Quad current output DAC. It works on a single +5V power supply, needs an external voltage reference, but includes two stages of input latches and dissipates a mere 25mW, about 7mW per DAC if digital levels are 0.8V and 2.4V, respectively! (even less for digital input voltages of 0V and  $V_{dd}$ ).

### SP9344

This voltage-output Quad-DAC is an extension of the HS7584 where OP-AMPs have been added to enable voltage output. It was still in the preparatory phase and about to be released,

but according to preliminary information it works on +/-15V and +5V supplies which makes it more complicated to operate and consumes about 600mW, i.e. 150mW per individual DAC, excluding external voltage reference.

Although it might be useful for applications that require more DACs and where board space is limited, the need for 3 different supply voltages is a drawback. It is supposed that it also will be a hybrid device.

### **Maxim**

Maxim seems to compete mostly in the range of low-end products. They are mostly second-sourcing Analog Devices products (like the popular and simple 75XX series of DACs) with few recent developments of their own.

### **PMI**

This company has been acquired by Analog Devices, but it seem as if they keep their own fabrication lines and only the marketing has been taken over. Its main product line in the 12-bit segment are CMOS current output DACs.

It is also noted here that a product of possible interest was announced in the Sept. 1989 databook: a GaAs-based 12-bit voltage output DAC with 3ns settling time. The power dissipation of 450mW is extremely low for a product of that speed. Due to the material used it might also show considerable radiation tolerance. This was preliminary data, however, and as the power requirements were too high for the present tests, no information as to the present status of this product has been gathered.

The PMI 7541A was subjected to radiation testing.

# 4. Choice of devices

To limit the number of devices to be tested, the DACs had to meet certain criteria to be of potential interest in space applications. Basically the search was limited to converters giving 12-bit resolution as most DACs currently used in space are 8-bit devices. Apart from that, the most stringent restriction was POWER CONSUMPTION: being of great importance in space applications, only low-power devices were sought, the maximum being in the order of 150 mW. This meant that virtually all high-speed devices were excluded as these usually require some 500 mW to a few watts to achieve settling times below 100ns for current output DACs (e.g. Analog Devices AD568 or HDM-1210) and below 3us for voltage output DACs (e.g. Analog Devices AD767, Sipex HS3860 or DAC338). Most bipolar devices have a rather high power consumption,too; as they have been on the market for quite some time, even radiation test reports for some of them are already available (for example the AD565A had to be radiation tested for use in the ISO project [4]). Sipex as a manufacturer performed some irradiation tests under a radiation hardening program currently under way. For some of their DACs data on total dose and neutron testing is available.

<u>Table 4.1:</u> Radiation data available from Sipex on some of their products. Data on voltage references was also included as this is a vital external part for many multiplying DACs.

The numbers give the upper radiation limit where the devices were still within specification limits.

| Туре                             | Remark  | total dose [krad] | Neutrons [n/cm <sup>2</sup> ] |

|----------------------------------|---------|-------------------|-------------------------------|

| HS 2700 family voltage reference | bipolar | 3000              | 5.1012                        |

| HS 3860 12 bit DAC               | bipolar | 300               | $3.10^{12}$                   |

| DAC 370 18 bit D/A               | CMOS    | 5                 | n.a.                          |

Further selection requirements were SPEED (settling time should be no more than 10us for voltage output DACs and no more than 3us for current output DACs) and the BINARY DATA CODING (meaning that the digital input code had to be either "offset binary" or "2s complement"). Finally, care was taken to select only devices requiring "standard" input voltages, i.e. either +/-15V, +15V or +5V.

Although these restrictions excluded a large percentage of devices from being selected, quite a lot of commercially available DACs fulfilling the above-mentioned requirements was still left. At this stage it became clear, however, that only CMOS devices could meet the requested power consumption limits. A closer examination reveales that most manufacturers produce a variety of DACs which are very similar to each other with regard to their "central" part, while the "periphery" was slightly different to meet the various demands of the customers.

A good example is the 7521/7531/7541/7541A/7542/7543/7545 family of CMOS-DACs where the same core building blocks (resistor ladder and CMOS switches) can be seen on each chip, while a varying amount of additional features is included in different chips (different kinds of latches in different arrangements, two stages of latches, control circuitry, provisions for serial or parallel data input). This principle (identical "core" DAC, different logic interfaces and peripheries) can be verified for example by comparing the physical chip topographies for different DACs as they are shown in the MAXIM 1989 databook [D2].

Another example is the Burr Brown DAC7800/7801/7802 series, wherein the digital interface is the only difference between the devices.

As the investigation was also intended to find the weak points and to identify with a high degree of certainty the parts which degrade under irradiation, the "simplest" version of these DACs (i.e. having the fewest functional blocks) was usually chosen. Obviously it is much more difficult to determine the location of failure and the failure mechanism in a highly complex device (comprising for example one or two sets of latches with the according control logic, an internal voltage reference and internal OP-AMP in addition to the central resistor ladder and CMOS switches) than in a rather simple one. While for the first group only the observation of degradation of the performance is possible (with many possible reasons for it), a much more detailed analysis can be performed for the second group by comparison of various input and output parameters at different stages of the irradiation program.

Therefore, in general "simple" devices were chosen to be tested. On the other hand, it is clear that for applications a high degree of functional integration is desirable. But as requirements for different missions might differ considerably (microprocessor interface compatibility yes/no, serial/parallel data input, settling time crucial yes/no...) it is sure that further testing has to be done anyway which might build on the results gained in the course of this evaluation.

In some cases it might even be worth to use a rather primitive current output DAC because this provides some additional flexibility: the OP-AMPs necessary to convert the output current to a voltage can be chosen to be rather slow, low-power devices or fast types with increased power consumption, tailored to the application's needs. A reference voltage, needed for most of the simple DACs, might already be necessary for some other purpose and be available on the board anyway.

### Final choice of test devices

In the end, after a first and second pre-selection, the final candidates were chosen. A natural choice seemed to be to include the AD7541A (and compatible):

- \* it is a simple device (resistor ladder and current switches

- \* it seems to be form a "industry standard" and therefore is produced by a lot of manufacturers, which allows a direct comparison of the quality of the manufacturing process used by them.

The other test candidates were not so obviously found; finally a choice had to be made among a number of different devices which according to the data sheets had about the same performances.

It was therefore decided to vary the power supply voltages, including devices working from a single +5V supply which seem to become more and more popular among manufacturers as well as "standard" DACs working on +15V. The trend to include more than one DAC in one chip was also taken into respect, although it is then necessary to buffer the inputs and provide control circuitry.

Finally a DAC with built-in OP-AMP and a complete bipolar voltage output DAC were also included.

It should be noted that all these DACs used the principle of the R-2R resistor ladder in combination with current switches.

### List of test devices:

- 1) Analog Devices 7541A

- 2) Burr Brown 7541A

- 3) Harris 7541

- 4) PMI 7541A

- 5) Sipex 7541A

These devices were multiplying CMOS current output Digital-to-Analog converters requiring an external precision voltage reference and one (for bipolar output: two) external OP-AMPS.

### 6) Burr Brown 7802

This was a dual multiplying CMOS current output DAC working on a single +5V power supply with buffered inputs.

### 7) Sipex 7584

A CMOS multiplying current output device including 4 DACs in a single package. Supply voltage was +5V, and power consumption was claimed to be a mere 5mW.

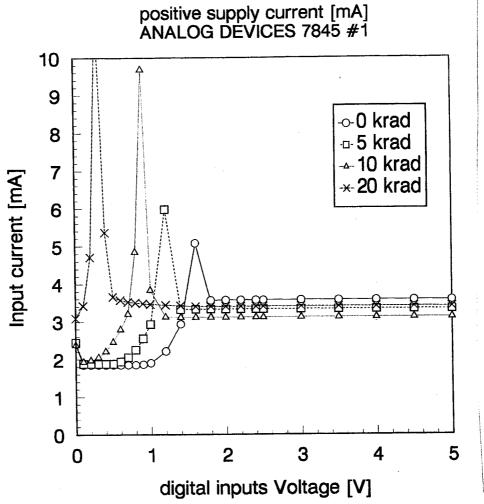

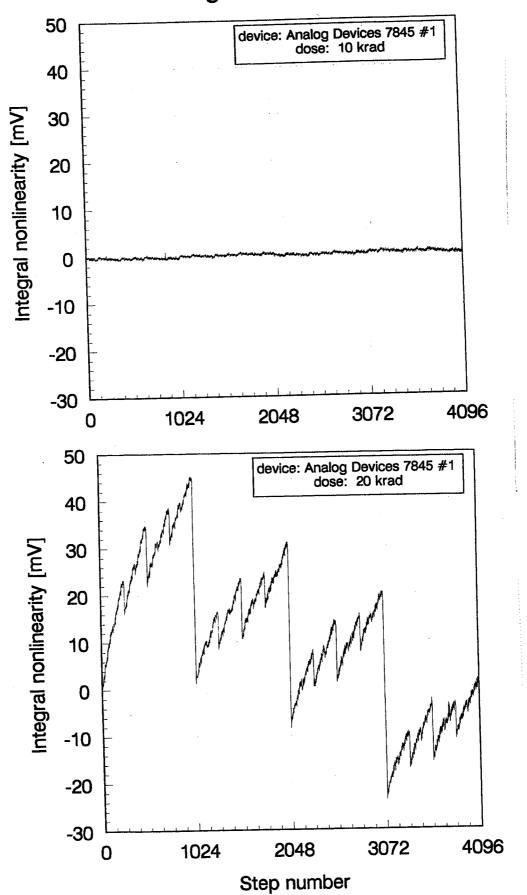

### 8) Analog Devices 7845

A multiplying CMOS DAC, including an OP-AMP monolithically integrated on the chip and produced with Analog Devices' LC<sup>2</sup>MOS process. Power requirements were some 150mW typ., 200mW max., though. Latches were also included, they could be operated in a "transparent" mode.

### 9) Sipex DAC356

This was the only complete voltage output device, operating from +15V and -15V power supplies, including a voltage reference, but without latches. According to the data sheet its settling time was slower than required but it was included as it was supposed to dissipate only 70mW of power; however, it was found that all the available devices consumed more than 150mW! By opening a device it turned out that it was not monolithic, but a hybrid device.

# 5. Test setup and strategy

To convert the current output of DACs to a voltage output, a circuit as shown schematically in Fig. 5.1 was used. This circuit theoretically produces an analog output voltage of -10V for a digital input code of 00..00 and of +9.995V (=10V - 1 LSB) for an input of 11..11. The resolution of 12 bits therefore resulted in a voltage resolution of 4.88mV.

The OP-AMPs used were PMI OP-42 with a pretty high slew rate of 50V/us, which in theory translates into a settling time of approximately 500ns for a 10V step [D3]. However, as indicated in the schematic of the circuitry, a feedback capacitor had to be used to dampen the "ringing" that otherwise would have occurred. This slowed down the settling time a bit; it still did not exceed 1.5us for current output DACs, though.

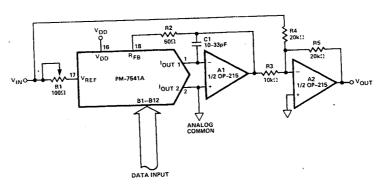

Figure 5.1: External circuitry that was used for current output DACs to convert the current into a voltage. For most DACs that were tested an external voltage reference as indicated in the picture was also necessary. Note the feedback capacitor which is necessary for very fast OP-AMPs to prevent them from oscillating.

In order not to introduce more potential error sources than necessary, no external trimpots for offset and gain adjustments were used (External trimming also causes increased drift with temperature; as all measurements were performed at a constant temperature of 20°C this would not have had any influence).

As the fixed resistors were accurate to 0.1% of their nominal value, the gain error could not be determined more precisely than that. However, as the same circuit was used for all DACs of the same type, the relative change of that parameter in response to radiation could be determined very accurately.

### **5.1 STATIC TESTING**

The main parameters that were determined were

- 1) Differential Nonlinearity (DNL): defined as the largest deviation of any analog voltage output step from the ideal step size of 1 LSB when the digital input code is increased by 1. DACs with DNL greater than +/- 1 LSB may be nonmonotonic.

- 2) Integral Nonlinearity (INL): defined as the maximum deviation of the plotted analog output characteristics from a straight line drawn between the end points.

- 3) Standard Deviation: calculated according to its definition, it gives an estimate of the "mean" deviation of the analog output from a straight line drawn between the end points.

- 4) Gain Error: the difference between the actual and the ideal output range when using only the internal feedback resistor. As pointed out above, it could not be determined more accurately than to 0.1%. Comparison between similar devices at various stages of the irradiation process can nevertheless provide interesting results as the relative accuracy is much better than the absolute one.

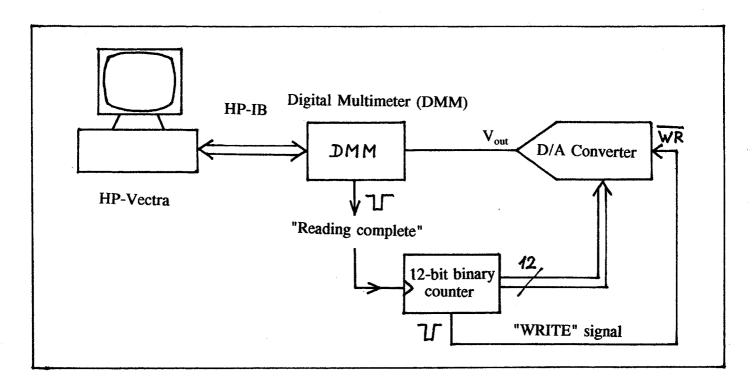

To measure the value of these parameters, a digital ramp was fed into the device under test (DUT). The ramp was generated by TTL counters (74LS393), which were triggered by a TTL-level input signal. A few microseconds after the digital input code for the DAC was set up, a "WRITE" signal (active low) was available to latch the data word into those DACs whose latches could not be operated in a "transparent" mode. The measurement itself was computer-controlled, using a Keithley model 195 Digital Multimeter (DMM) having a resolution of 0.1mV to measure the voltage output for all 4096 different input codes. The DMM, in turn, provided a "reading complete" TTL output signal that was used to trigger the counter, thereby increasing the binary count by 1.

The HP-Vectra acting as a controller and the DMM were interconnected via their HP-IB interfaces, and a software program written in HP-Basic took care of all timing and data transfer considerations. The measurement data was stored and finally processed by another HP-Basic program which calculated Differtial and Integral Nonlinearity, gain error, standard deviation and the output value of each individual bit of the DUT.

Figure 5.2: Schematic measurement set-up used for quasi-static testing D/A converters (top) and the timing diagram for that measurement (bottom). The HP-Vectra acting as controller triggered each measurement via the HP-IB bus; after reading in the result from the DMM on the same way the next measurement was started.

### 5.2 PARAMETRIC TESTING

The HP 4145 parameter analyzer turned out to be a valuable tool in assessing the radiation damage after an irradiation step in a very quick way. It allowed for the determination of such basic parameters as input current and output leakage current and it was possible to use the test results to interpret what was happening inside the device, i.e. which physical processes lead to degradation of device performance.

The general approach to parametric testing was as follows:

- \* all necessary power supplies for a device were provided (+5V, +15V or +/-15V)

- \* for multiplying DACs: a +10V reference voltage was provided

- \* all digital inputs were shorted and connected to a variable voltage source

- \* for DACs where input data had to be latched in: a "WRITE" pulse was applied to the appropriate pin(s) after the desired input code had been set up

- \* for voltage output DACs: the output voltage was measured

- \* for current output DACs: the output current pins were connected to very sensitive current sensors which could detect currents as low as 1pA

The actual measurement consisted of sweeping the input voltage applied to the digital inputs from 0V to 5V while all the other voltages were kept constant.

### Measured parameters were:

- 1) Positive power supply current

- 2) Negative power supply current (where applicable)

- 3) Reference voltage input current (where applicable)

- 4) Combined input current of all 12 digital inputs

- 5) Output current (for current output DACs)

- 6) Output voltage (for voltage output DACs)

All these parameters were determined as a function of digital input voltage. The change of some parameters in response to irradiation made it possible to roughly estimate the radiation sensitivity of a device and to predict the total radiation dose at which the device would probably fail even at a time when the output characteristics were still rather normal.

The measurement was computer-controlled by a simple HP-Basic program, and the measurement data was printed out in tabular form.

# 5.3 DYNAMIC TESTING

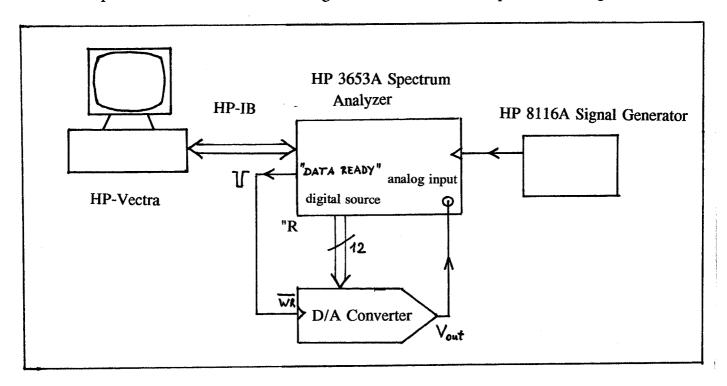

A very powerful tool for dynamic testing seemed to be available with the HP 3653A spectrum analyzer. It offered extremely fast FFT routines, 13-bit resolution and it could operate up to a speed of 256kHz, i.e. taking one measurement every 4us, which seemed just about right to test the performance of the DACs at their upper limit.

Considerable effort was therefore made to design and produce a printed circuit board that did not sacrifice settling speed by keeping the important tracks as short as possible and minimizing the use of sockets by directly soldering most components very close to each other.

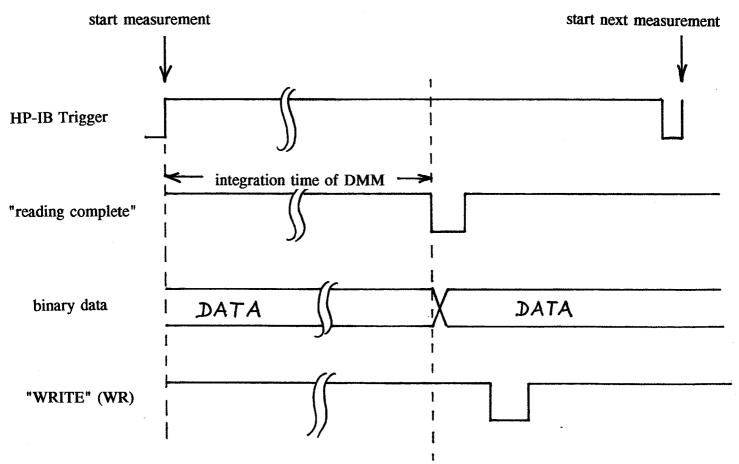

The measurement principle was rather simple: the HP 3653A was programmed to output a 12-bit digital sinewave, which was applied to the inputs of the DUTs. Data was updated at a rate of 250kHz and just before a new 12-bit word was set up, the analog output of the DAC (which had settled to its final value by then) was read back into the spectrum analyzer. In this way a corresponding analog output from the DUT was sampled by the spectrum analyzer for every digital data point of the sinewave. The complete time-domain signal was subjected to a Fast Fourier Transform (FFT) to determine the dynamic parameters Total Harmonic Distortion (THD) and Signal to Noise Ratio (SNR). The idea was to detect any possible degradations in dynamic behaviour that might be apparent at an irradiation stage when the quasi static results are still unchanged. In other words, the reason was to see if radiation damage could initially lead to slower device operation while the static accuracy was still within specifications. A schematic drawing of the measurement set-up is shown in figure 5.3:

Figure 5.3: Measurement setup used for dynamic testing of D/A converters

The setup of the spectrum analyzer and the measurement sequence was controlled by an HP-Vectra computer running under HP-Basic, which also took care of data output and data storage. The HP8116A programmable signal generator served as the main system clock by supplying a TTL squarewave signal of 250kHz. It determined the digital update rate as well as the analog input sample rate. For some DACs the frequency was lowered to 150kHz (in one case even to 20 kHz) as their specified settling time was greater than 4us.

While above-mentioned data update frequency remained constant for any individual kind of DAC, the frequency of the digital sinewave fed into the DUTs was varied. As increasing that frequency means that successive digital codes have to differ in value more and more, it also means that the analog output steps of a DAC become bigger. Another way to look at this is that a full period of the digital sinewave is made up of less and less points, so they have to be spaced further apart. In this way it should have been possible to detect any influence of the stepheight on the settling time, which is usually the case.

However, it turned out that the spectrum analyzer was not as ideal an instrument for that kind of test as originally thought. The reason for it was rather simple, but nontheless crucial: The analog input path of the spectrum analyzer contained a high-order lowpass filter with a cutoff frequency of 100kHz. This filter prevents aliasing by simply filtering out frequencies that are higher than the spectrum analyzer is supposed to sample. This filter, however, heavily distorted the analog signal from the DACs as their output is a step signal when the digital input code is changed. Theoretically a step signal consists of a superposition of sinewaves whose frequencies are not limited. So even as the DAC output steps are not infinitely steep, they are steep enough to contain frequencies that are much higher than the 100kHz cutoff frequency of the filter. If an analog step is applied, the filter responds by oscillating around the new final value and it takes about 50-100us to settle completely. If the data update rate is 4us, then the next input step arrives when the filter has not yet settled but is still heavily oscillating. As a consequence the measurement is not reliable.

The amplitude of the oscillations is proportional to the stepheight of the input signal, so a lower sinewave frequency should yield rather accurate numerical results (e.g. for a 100Hz sinewave a full period consists of 2500 datapoints; if the amplitude of the analog sinewave is 20V full scale as it was for the DACs used, then the maximum possible stepheight is 25mV. The amplitude of oscillation was observed to be about 10-20% of the stepheight, which means that the measurement error should not exceed 5mV in that case).

Test results obtained at higher frequencies however can only give a rough impression of changes in the DAC when comparing the data at different stages of the radiation tests. Their absolute values are meaningless.

As a complementary measurement and in order to "see" possible changes in the output signal shape a hardcopy of the output signal of the DACs as it appeared on the screen of an LeCroy 9410 digital oscilloscope was also recorded. The basic settings for all DACs were kept the same, so without any changes due to radiation damage no change in the signal shape would be detected. This additional test provided some valuable insight into the switching behaviour of devices coming from different manufacturers.

### **Definitions:**

Total Harmonic Distortion: is the ratio of the rms sum of the harmonics of the DAC output to the fundamental value when the DAC is driven by the digitized representation of a sinewave.

$$THD = 20.\log \frac{V_1}{\sqrt{(V_2^2 + V_3^3 + ...)}}$$

$V_1$  is the rms amplitude of the fundamental and  $V_2, \ V_3...$  are the rms amplitudes of the individual harmonics.

Usually the only the first 10 harmonics were included in the calculation.

Signal-to-Noise Ratio: is the measured signal to noise at the output of a converter. The signal is the rms magnitude of the fundamental. Noise is the rms sum of all the nonfundamental signals (including harmonics) up to half the sampling frequency. The theoretical SNR for a sinewave is given by:

SNR = (6.02N + 1.76) dB where N is the number of bits.

# 6. Irradiation facilities and device setup

Irradiations were carried out using the ESTEC <sup>60</sup>Co radiation source, which had an activity of about 1.4 kCi or 5.2 10<sup>13</sup> Bq at the time of this work. The source produced gamma rays with two discrete energies which are very close; their average energy was 1.25MeV.

Doserates were adjusted simply by varying the distance of the samples from the source. The angle of incidence was kept at  $90^{\circ}$  throughout the tests. All total dose figures that will subsequently be given are in krads( $H_2O$ ); to convert to krads(Si) the numbers have to be multiplied by the conversion factor of 0.91. All doses were measured using an Ionex Dosemaster with a  $0.6 \text{cm}^3$  Ion probe which was calibrated to +/-0.5%.

During irradiation, all devices were biased to their nominal supply voltages with a +10V reference voltage supplied to those devices that did not have an internal one. The digital inputs were either kept static at logic 'HIGH' (+5V) or a digital ramp was fed into the DACs at a frequency of approximately 50 kHz.

Table 6.1 and 6.2 give an overview of irradiation levels and the bias mode used. Doserates varied from 4 rads/minute to 30 rads/minute for Table 6.1 and from 5.7 rads/minute to 26 rads/minute for Table 6.2. This was due to smaller irradiation steps at the beginning of each test run with ever increasing steps in further course.

Table 6.1: Main test parameters for the first group of devices

| device                  |    | digital inputs | Irradiation  |

|-------------------------|----|----------------|--------------|

| Burr Brown 7541A KP     | #1 | dynamic        | 0 - 8 krad   |

| PMI 7541A GP            | #4 | dynamic        | 0 - 8 krad   |

| Analog Devices 7541A BQ | #4 | dynamic        | 0 - 16 krad  |

| Harris 7541 LN          | #4 | dynamic        | 0 - 100 krad |

| Harris 7541 LN          | #5 | static         | 0 - 25 krad  |

| Sipex 7541A BQ          | #2 | dynamic        | 0 - 100 krad |

| Sipex 7541A BQ          | #3 | static         | 0 - 100 krad |

| Sipex DAC356            | #1 | dynamic        | 0 - 100 krad |

| Sipex DAC356            | #3 | static         | 0 - 12 krad  |

Table 6.2: Main test parameters for the second group of devices

| device                 |    | digital inputs | Irradiation  |

|------------------------|----|----------------|--------------|

| Burr Brown 7802 KP     | #1 | dynamic        | 0 - 8 krad   |

| Burr Brown 7802 KP     | #2 | static         | 0 - 8 krad   |

| Analog Devices 7845 BQ | #1 | dynamic        | 0 - 16 krad  |

| Analog Devices 7845 BQ | #2 | static         | 0 - 100 krad |

| Sipex HS7584C          | #1 | dynamic        | 0 - 25 krad  |

| Sipex HS7584C          | #2 | static         | 0 - 100 krad |

### 7. Test results

The results obtained will be presented on a device-by-device basis, beginning with a short description and a list of specifications according to the manufacturer and a brief resume of pre-irradiation characteristics, followed by the results of parametric, quasi static and dynamic testing at different total dose levels. Finally for each device a short interpretation of the results is presented.

Failure of any device to comply with any of the specifications during the tests will be mentioned. No comment on a characteristic therefore means that the device was still within the allowable tolerances.

### 7.1 BURR BROWN 7802 KP

<u>Brief characterisation:</u> dual, current output DAC with input latches and control logic. No internal voltage reference or OP-AMP.

### Specifications (according to datasheet):

| Integral nonlinearity        | max. | +/- 1 LSB     |

|------------------------------|------|---------------|

| Differential nonlinearity    | max. | +/- 1 LSB     |

| Gain error                   | max. | +/- 3 LSB (*) |

| Output leakage current       | max. | 10 nA (**)    |

| Digital input current        | max. | +/- 1uA (**)  |

| Power supply current         | max. | 2mA           |

| output current settling time | max. | 0.8us (***)   |

<sup>(\*)</sup> when using internal feedback resistor

### Pre-irradiation characteristics

As can be seen in table 6.2, two devices (=4 DACs in total) were tested up to 80 krad. 2 DACs were irradiated under "static" input conditions (device #1 DAC A and DAC B), 2 DACs had "dynamic" inputs (device #2, DAC A and DAC B)

All DACs showed similar characteristics well within specifications.

<sup>(\*\*)</sup> at 25 degrees Celsius

<sup>(\*\*\*)</sup> to 0.01% of full scale; load resistor 100.

# Electrical parameters and quasistatic test results

### Input current

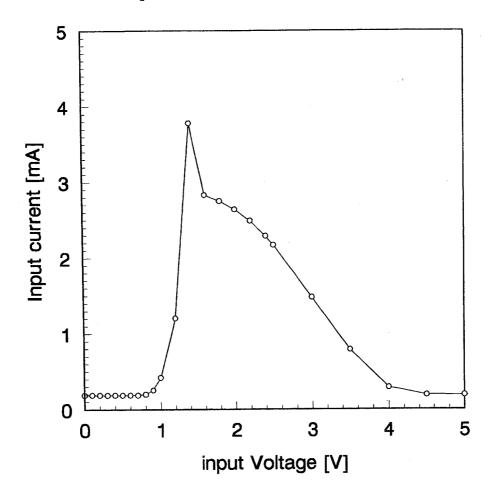

Maybe the best parameter to see what is going on is the evolution of input current vs. input voltage applied to the shorted digital input pins ("digital input voltage") during irradiation. Figure 7.1.1 shows the input current of device #1 before the tests started.

Figure 7.1.12 Input current vs. digital input voltage for Burr Brown 7802 #1 prior to irradiation.

It can be seen that the input current is very small as long as the digital input voltage is within allowed logic levels (i.e. 0V to 0.8V and 2.4V to supply voltage, respectively). Between these levels the MOSFETs of the input buffers and current switches operate in their linear region, corresponding to a sharp surge in input current.

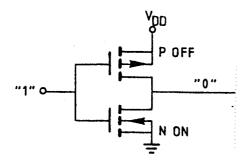

This behaviour can be qualitatively unterstood by examining the current flow in a single CMOS inverter (only a brief overview will be given here; for a complete treatment of radiation effects on CMOS devices see [5] and for an in-depth coverage of radiation effects on MOS structures see [6]).

Figure 7.1.2: CMOS inverter

If the input voltage (=gate voltage of the MOSFETs) is kept to ground, the n-MOS transistor is in its nonconductive state, while the gate-source voltage of the p-MOS transistor is equal to -V<sub>dd</sub>, and consequently its channel is conductive. The current is limited by the leakage current of the n-MOSFET. In case the input voltage is equal to Vdd, the p-MOS transistor is in its nonconductive state and limits the current. Between these input voltages, however a region exists where both transistors are in their transition phase where the current flow increases considerably. At an input voltage of about half the supply voltage the inverter output changes its logic state.

It is well known that the I-V characteristics of p- and n-MOSFETs change under the influence of ionising radiation: Threshold voltages shift towards lower voltages due to a buildup of positive charge in the gate oxide, and the leakage currents increase in magnitude. It is also known that these changes depend on the type of transistor (n-MOSFETs usually show greater shifts than p-MOSFETs) and the bias conditions (the worst case is usually the gate biased positive with respect to the substrate).

Briefly the big problem is the n-MOSFET of the inverter. As the threshold voltage is moving to lower voltages with increasing total dose and finally even crosses 0V, the quiescent current of the device increases sharply. The principle of that mechanism is explained in the text of figure 7.1.3.

Increased leakage can also be found predominatly in n-MOSFETs. The p-MOSFET, on the other hand, poses much less problems because the worst thing that could happen is a threshold voltage shift far enough so that the transistor cannot be turned ON anymore. However, long before that happens the characteristics of the n-MOS transistor have shifted to a point where it is no longer possible to switch that transistor OFF. It is clear that as soon as the threshold voltage of the n-MOSFET shifts into the logic LOW region (0 - 0.8V), reliable operation can not be guaranteed any more. By the time when it crosses 0V changes in logic state become impossible ("logic failure").

One should carefully distinguish between leakage as a result of a threshold voltage shift as described above and leakage caused by poor quality of the field oxide. The latter can also be found in many devices and is caused by trapped charge in the field oxide, especially in those parts adjacent to the gate oxide ("bird's beak"). It causes leakage currents at the periphery of the transistor. Contrary to threshold voltage shift it leads to a general increase in quiescent current, not limited to the region near the current peak. So if an overall current increase in the "flat" part of the current characteristics is observed (e.g. in the region below 0.8V in

Figure 7.1.1) this is almost certainly due to this mechanism.

Before the device fails completely some secondary effects might become apparent like slowing down of switching speed. This is due to interface states created by the irradiation which in turn distort both the I-V ("transconductance") and C-V characteristics, thereby reducing switching speed.

Fig. 7.1.3: Graphical determination of the output voltage and supply current of a CMOS inverter: A few rules are sufficient to calculate this voltage provided the characteristics of the transistors are known.

1) The current through both transistors is the same

The broken lines show the drain current of an unirradiated n-MOSFET as a function of drain-source voltage for a gate voltage of 0.8V and 3.0V, resp. In the linear region the curves almost coincide. The solid curves show the same characteristics for a p-MOSFET. The polarity of all voltages is negative in that case (right end of the figure corresponds to 0V). To determine the output voltage for a given input voltage (e.g. 0.8V) one has to look at the corresponding curve for the n-MOSFET and determine the intersection with the "complementary" curve of the p-MOSFET (i.e. 10V-0.8V=9.2V). This intersection (Point X) is still in the linear part. The x-coordinate yields the output voltage of the inverter, the y-coordinate the current flow. Applying this method to a different input voltage (e.g. 3.0V) shows that now the output voltage is somewhat lower and the current increased considerably (Point Y).

To see the influence of irradiation one has to bear in mind that charge buildup in the oxide acts as if the gate voltage for all I-V curves is lowered by an amount about equal to the shift in threshold voltage. Therefore the curves in the graph now describe the behaviour for gate voltages lower than the original ones. In brackets a shift by 0.8V for both n- and p-MOSFET has been assumed. Now Point X describes the situation for an input voltage of 0V instead for 0.8V. Similarly, the current for an input voltage of 2.2V is already about as high as was previously the case for 3.0V. The current peak, before irradiation located close to 5V, also shifted by the same amount.

<sup>2)</sup> The sum of the gate-source voltages of the p- and the n-MOSFET is equal to the supply voltage (here +5V)

### Discussion

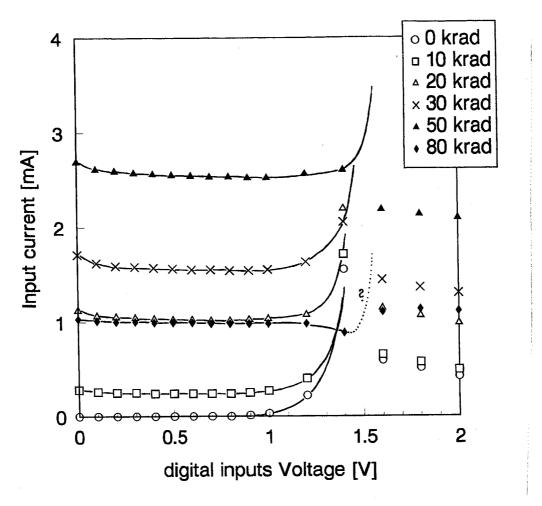

Although the actual DAC is certainly much more complex, the general features described above can be found in the I-V relationship as shown for device #1 in Fig.7.1.4

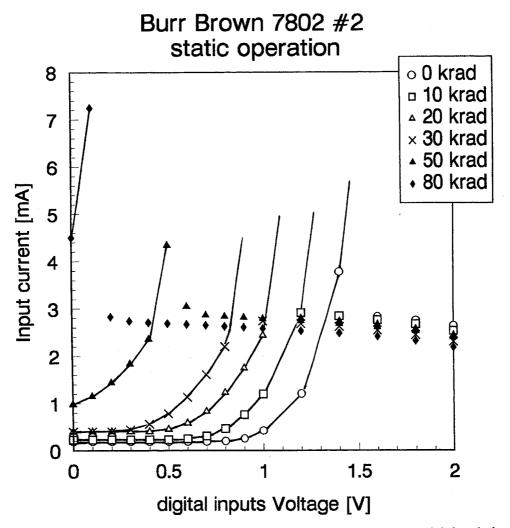

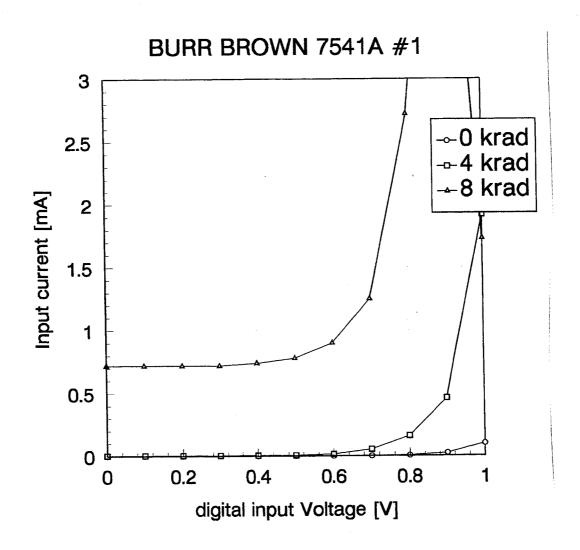

Figure 7.1.4: Input current vs. digital input voltage for several total doses for device #1. For reasons of clarity only the region between 0 and 2V is shown. In the left part of the curve the datapoints have been connected to show the almost linear shift to lower voltages.

### One can see

- a) an increase in leakage current with increasing total dose. This can be seen best by comparing the input current for a digital input voltage of 0V.

- b) that the input current input voltage curve shifts towards lower voltages, reflecting the shift in threshold voltage of the n-MOSFETs. This shift seems to be fairly linear with total dose.

It is interesting to compare this behaviour to the results for device #2 (Fig. 7.1.5)

The difference between them was their bias condition during irradiation: while #1 had the digital inputs continuously changing, device #2 had all the inputs tied to +5V, and consequently one of the n-MOSFETs acting as a current switch at each leg of the R-2R ladder was turned ON all the time, the other transistor was OFF (see Figure 7.1.6). Of course this also meant that all the other MOSFETs in that device did not change their biasing condition, too. One might therefore expect a higher radiation sensitivity for device #2 because 50% of

Figure 7.1.5: Input current vs. digital input voltage for several total doses for device #2. For reasons of clarity only the region between 0 and 2V is shown. In the left part of the curve the datapoints have been connected to show the almost linear shift to lower voltages.

the transistors were constantly biased to "worst case", allowing bigger changes to take place. As the overall behaviour of a complex device is determined by its most affected parts, this means that constant bias leads to greater device degradation.

Figure 7.1.6: Schematic of the current switches at the end of each leg of the R-2R resistor ladder. Driven by different stages in an inverter chain, one n-MOSFET is always switched ON, the other is OFF.

And in fact it turned out that device #2 showed complete functional failure after 80 krad; by then no change in logic states was possible any more. One should recall that the change in logic state of an inverter takes place approximately at the point where the input current reaches its maximum; this point obviously shifted into the region between 0V and 0.8V for higher doses, finally leading to a complete functional failure after 80 krad. The total dose that is necessary to achieve this is dependent on the irradiation bias; obviously static bias is worse than dynamic bias.

### Conclusions

From figures 7.1.4 and 7.1.5 it can be seen that due to the shift of the input current peak the input current specification of max. 2mA is not fulfilled for total doses above 30 krad (taking an input voltage of 0.8V as valid logic LOW). For static operation (device #2) this figure is even lower, close to 25 krad.

It can also be seen that the input current for small voltages, i.e. close to 0V, also increases with total dose. This seems to be mostly a result of growing leakage current of all the transistors (caused by charge trapping in the field oxide) in the DAC because in that region of the curve the effect of the threshold voltage shift is negligible.

### Output leakage current

Output leakage current was measured with nominal supplies and all digital inputs set to LOW. It is basically determined by the deterioration of the n-MOSFET acting as a switch at the end of each leg of the R-2R resistor ladder (see Figure 7.1.6).

These 2 MOSFETs redirect the current between two output pins of the DAC, both of them driven by different outputs of an inverter chain. Several major changes can be caused by irradiation:

- \* The leakage current of the MOSFETs increases

- \* The shift in threshold voltage eventually leads to a noticeable current flow although the driving inverter delivers a proper LOW on the gate (if it is assumed that all n-MOSFETs in an IC are affected equally, then an inverter will still produce a proper LOW level because for this state the n-MOSFET has to be conductive, the p-MOSFET nonconductive. This condition is easily achieved, even if irradiation caused some degradation and even if the prior inverter stage produces a somewhat degraded HIGH output). The quality of the logic HIGH level will deteriorate.

### **Observations**

Table 7.1.1 shows that there is a big difference in the output leakage currents for device #1 and #2; both DACs of each individual device showed a very similar behaviour as expected for identical bias conditions.

A closer examination of the change in analog output between "startpoint" (digital input code 00..00) and "endpoint" (digital input code 11..11) shows that for device #1 these changes are comparable. For device #2 hardly any change in the "endpoint" value was observed, but a

<u>Table 7.1.1:</u> Output leakage current for different total doses. Measurements were taken for a input voltage at the digital inputs of 0.2V.

|               | 0 krad | 10 krad | 20 krad | 30 krad | 50 krad | 80 krad |

|---------------|--------|---------|---------|---------|---------|---------|

| 7802 #1 DAC A | 1.6pA  | 5.3nA   | 230nA   | 205nA   | 1.3uA   | 19uA    |

| 7802 #1 DAC B | 1.3pA  | 2.9nA   | 175nA   | 270nA   | 1.1uA   | 16uA    |

| 7802 #2 DAC A | 1.2pA  | 88nA    | 670nA   | 980nA   | 29uA    | n.f.    |

| 7802 #2 DAC B | 1.5pA  | 94nA    | 600nA   | 1.04uA  | 29uA    | n.f.    |

big change in "startpoint" value took place. This corresponds to a small leakage current for the MOSFET switching to current output #2 and a large leakage current for the second MOSFET, leading to current output #1 (Figure 7.1.6). This implies that a positive bias on the gate of an n-MOSFET during irradiation, as it was the case for the second MOSFET, leads to a quicker degredation compared to almost no bias which was the case for the first one. This is not surprising as a positive gate bias encourages the formation of trapped positive charge close to the interface where it has the greatest effect on threshold voltage; leakage caused by poor field oxide is also enhanced by positive bias.

### **Conclusions**

Device #1 failed to comply with the specification somewhere between 10 and 20 krad, device #2 already failed at about 6 krad.

# Digital input current

The limit given in the specifications is quite high (+/-1uA). For both devices this parameter increased from a few pA to more than 1 uA at 80 krad. The latter value is not negligable as an additional current of that magnitude changes the output voltage by approximately 10-20mV (2-4 LSB). However, compared to the changes that had already taken place at that stage of the irradiation this was of no great importance.

Conclusions: both devices finally failed on that specification, but only after a total dose of 80 krad.

# Gain error, differential and integral nonlinearity (DNL and INL)

The evolution of the "startpoint" and the "endpoint" output voltage as well as the change in gain (difference "endpoint" minus "startpoint") is given in table 7.1.2.

<u>Table 7.1.2:</u> Changes in analog output voltage for binary input codes 00..00 (startpoint) and 11..11 (endpoint) and corresponding change in gain. (n.e.: not evaluated; n.f.: device not functional any longer)

### ALL NUMBERS ARE IN mV

### Burr Brown #1 DAC A

| dosei      | 5 krad | 10 krad | 20 krad | 30 krad 50 krad |       | 80 krad |

|------------|--------|---------|---------|-----------------|-------|---------|

| startpoint | -0.1   | +0.9    | +1.9    | +3.5            | +24.2 | +286.8  |

| endpoint   | -0.3   | +0.6    | +2.4    | +3.2            | -11.8 | -297.0  |

| Gain       | -0.2   | -0.3    | +0.5    | -0.3            | -36.0 | -583.8  |

### Burr Brown #1 DAC B

| dose       | 5 krad | 10 krad | 20 krad | 30 krad | 50 krad | 80 krad |

|------------|--------|---------|---------|---------|---------|---------|

| startpoint | n.e.   | -0.3    | n.e.    | +1.0    | +19.6   | n.e.    |

| endpoint   | n.e.   | +0.1    | n.e.    | +0.9    | -20.8   | n.e.    |

| Gain       | n.e.   | +0.4    | n.e.    | +0.1    | -40.4   | n.e.    |

### Burr Brown #2 DAC A

| dosei      | 5 krad | 5 krad 10 krad |      | 5 krad 10 krad 20 krad 30 krad |      | 50 krad | 80 krad |

|------------|--------|----------------|------|--------------------------------|------|---------|---------|

| startpoint | n.e.   | +1.4           | +8.2 | +22.1                          | +531 | n.f.    |         |

| endpoint   | n.e.   | +2.4           | +5.8 | +8.5                           | +6.9 | n.f.    |         |

| Gain       | n.e.   | +1.0           | -2.4 | -13.6                          | -524 | n.f.    |         |

### Burr Brown #2 DAC B

| dose       | 5 krad | 10 krad | 20 krad | 30 krad | 50 krad | 80 krad |

|------------|--------|---------|---------|---------|---------|---------|

| startpoint | n.e.   | +2.6    | +8.6    | +18.1   | +550    | n.f.    |

| endpoint   | n.e.   | +2.0    | +3.5    | +3.9    | +5.8    | n.f.    |

| Gain       | n.e.   | -0.6    | -5.1    | -14.2   | -544.2  | n.f.    |

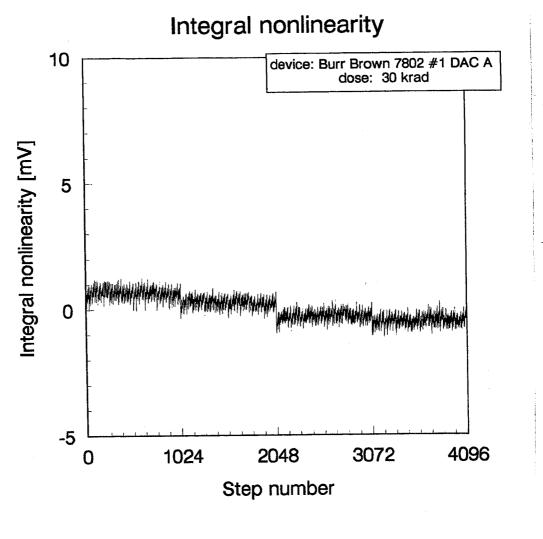

The evolution of INL and DNL can best be seen by a graphics plot of these parameters; numerical values are given in Table 7.1.3.

<u>Table 7.1.3:</u> Numerical values of INL and DNL for Burr Brown 7802 #1 and #2. Values are in mV. (n.e.: not evaluated; n.f.: device not functional any more)

### ALL NUMBERS ARE IN mV

### Differential nonlinearity

|          | 0<br>krad | 5<br>krad | 10<br>krad | 20<br>krad | 30<br>krad | 50<br>krad | 80<br>krad |

|----------|-----------|-----------|------------|------------|------------|------------|------------|

| #1 DAC A | 0.9       | 0.7       | 1.1        | 1.1        | 1.4        | 2.6        | 6.2        |

| #1 DAC B | 0.8       | n.e.      | 0.8        | n.e.       | 1.7        | 2.0        | n.e.       |

| #2 DAC A | 0.9       | n.e.      | 1.2        | 6.2        | 10.9       | 13.9       | n.f.       |

| #2 DAC B | 0.9       | n.e.      | 1.7        | n.e.       | 6.5        | 8.5        | n.f.       |

### Integral nonlinearity

|          | 0<br>krad | 5<br>krad | 10<br>krad | 20<br>krad | 30<br>krad | 50<br>krad | 80<br>krad |

|----------|-----------|-----------|------------|------------|------------|------------|------------|

| #1 DAC A | 1.1       | 1.2       | 1.0        | 1.4        | 1.3        | 2.7        | 5.7        |

| #1 DAC B | 0.9       | n.e.      | 1.0        | n.e.       | 1.8        | 1.9        | n.e.       |

| #2 DAC A | 0.9       | n.e.      | 1.9        | 4.6        | 7.8        | 11.2       | n.f.       |

| #2 DAC B | 1.7       | n.e.      | 1.8        | 2.9        | 6.5        | 10.7       | n.f.       |

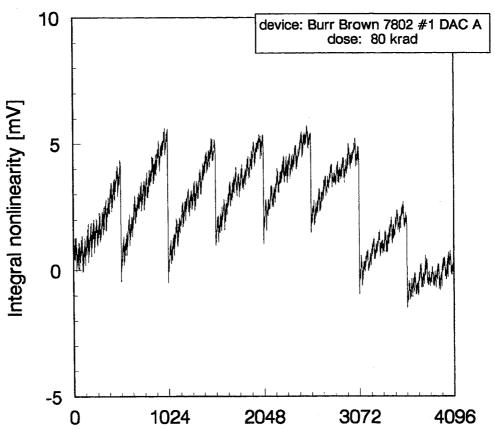

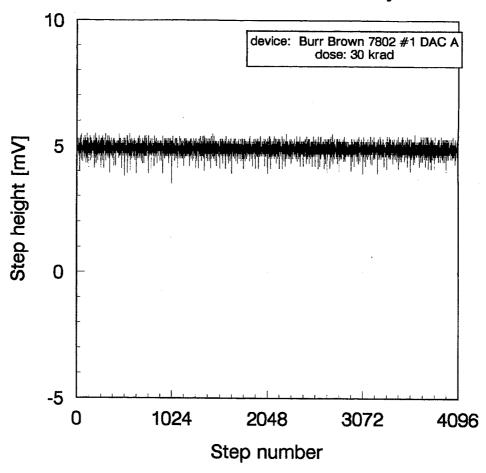

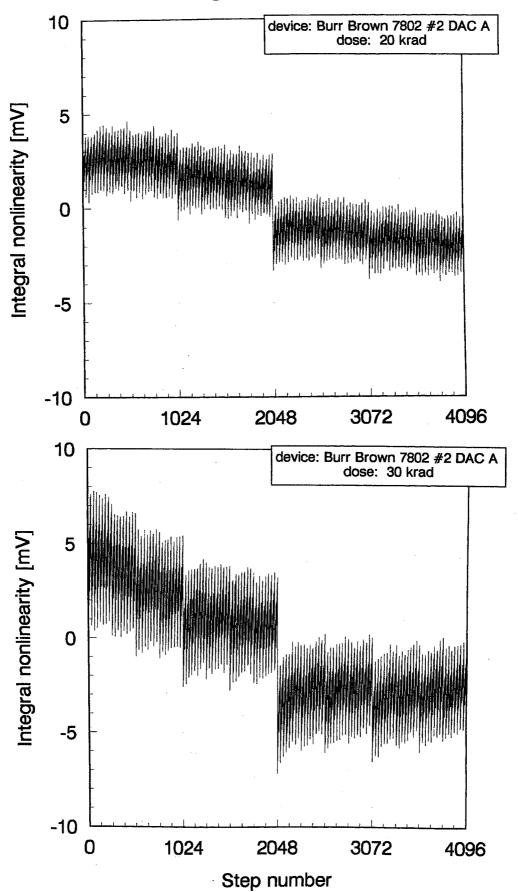

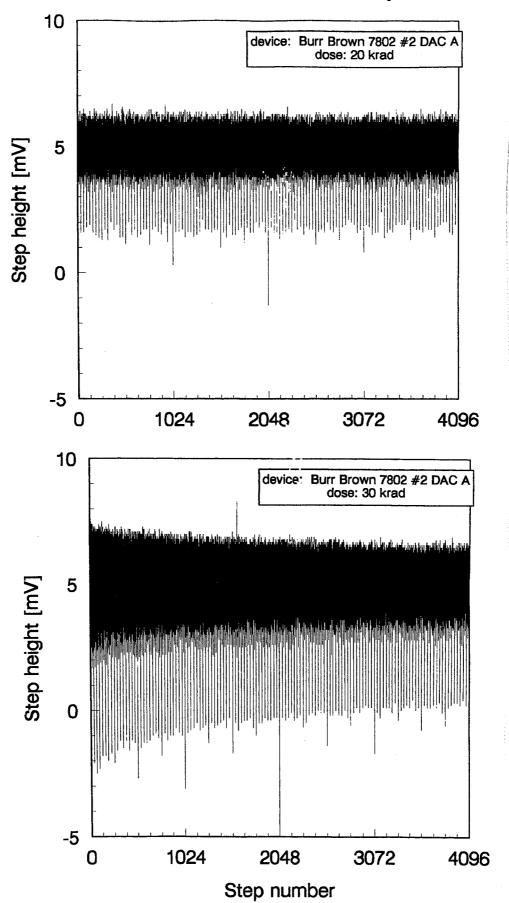

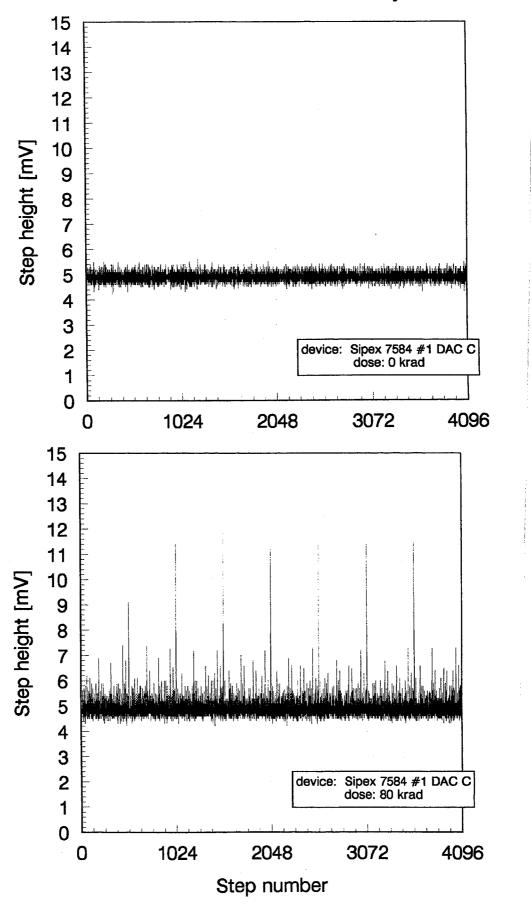

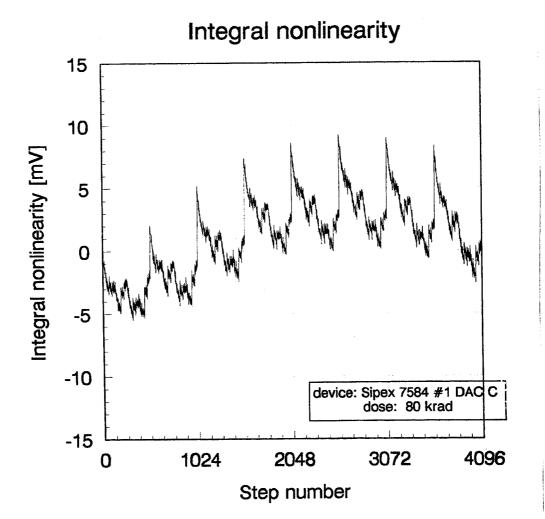

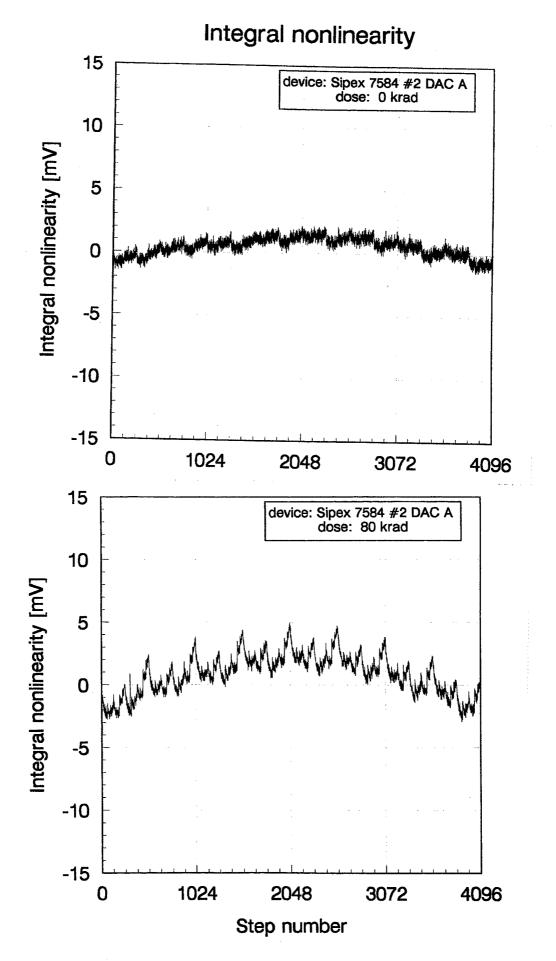

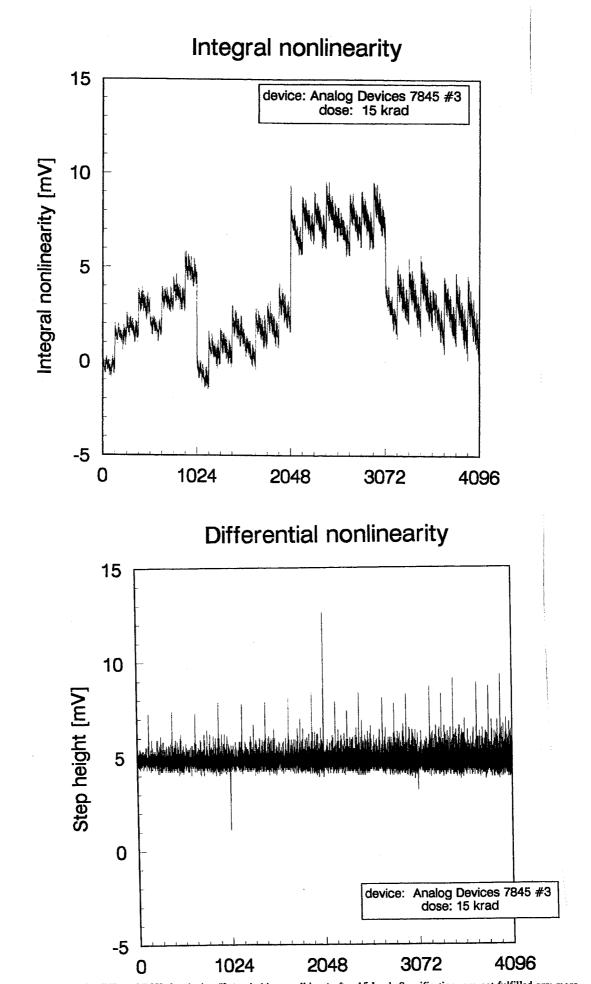

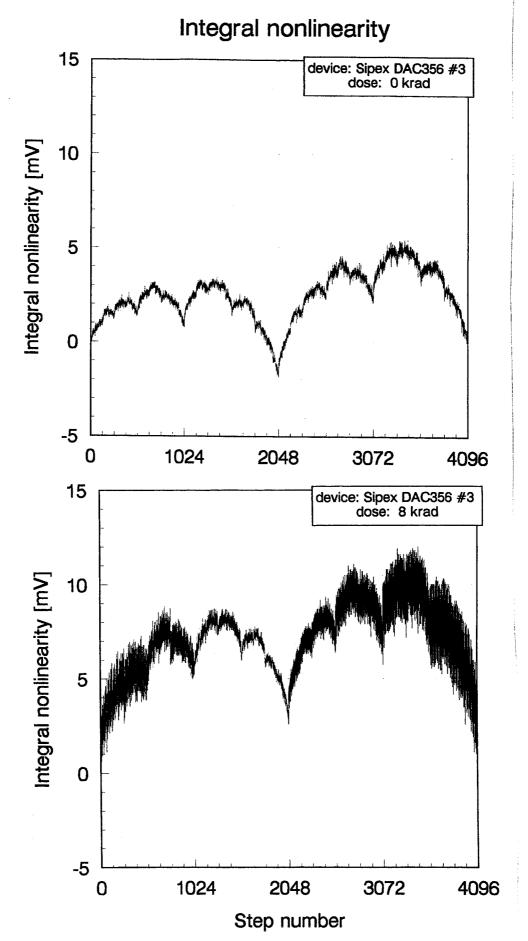

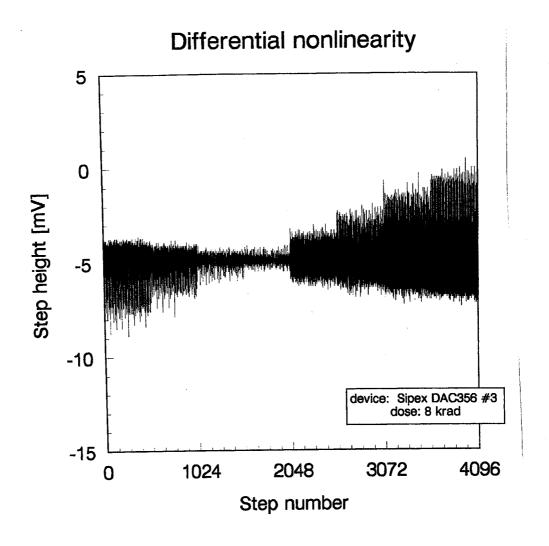

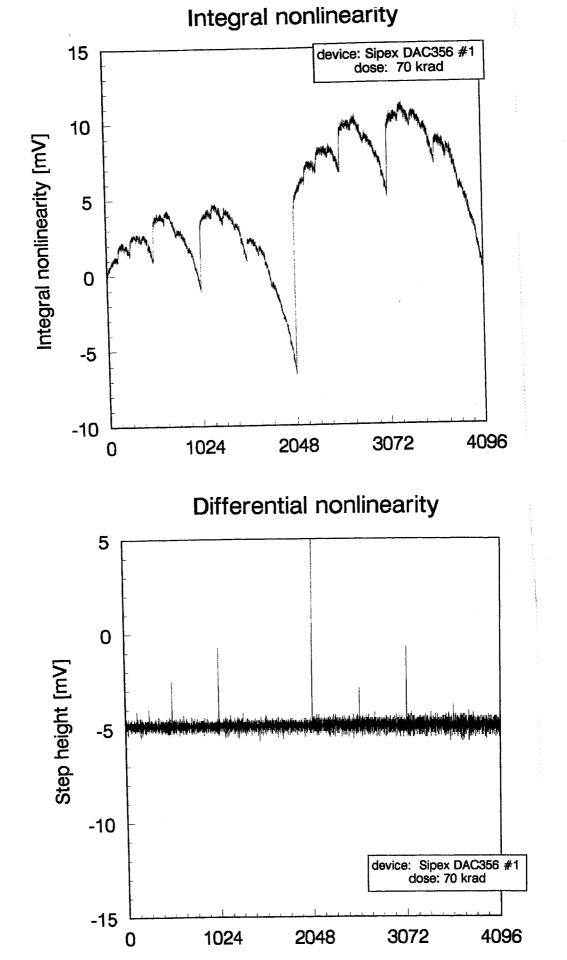

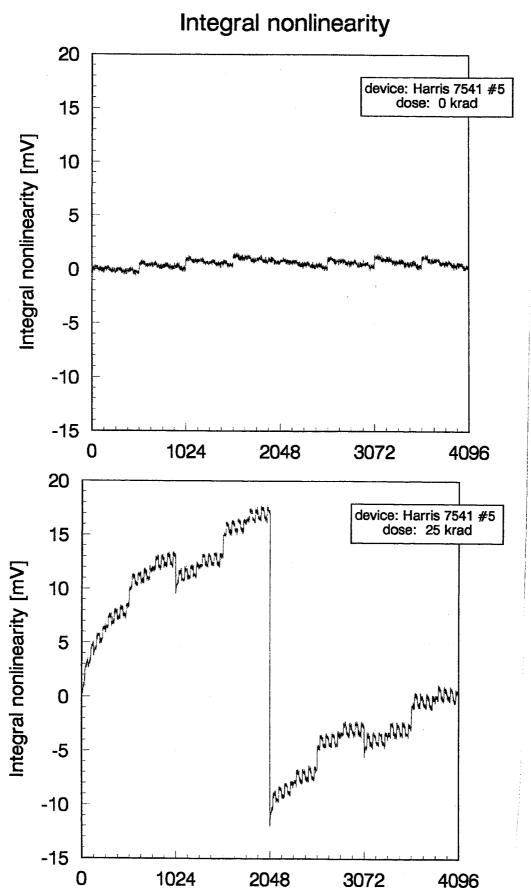

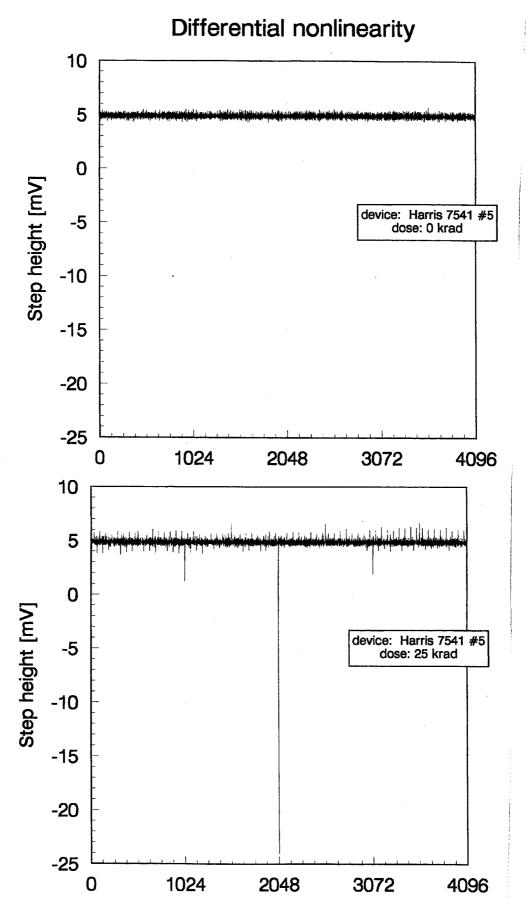

Figure 7.1.7 shows INL and DNL for device #1 prior to irradiation. Both parameters are well within specifications, although small discontinuities are visible for INL at major bit changes. Figure 7.1.8 shows the evolution of INL with increasing total dose. At 30 krad no obvious changes have taken place; after 80 krad, however, the appearance changed significantly. The rather smooth curve developed into a kind of sawtooth-like shape, reflecting the growing mismatch between individual bits.

The evolution of DNL, shown in Figure 7.1.9, can give some additional information. Initially confined to a small band of about 2mV width around the "ideal" value of 4.88mV (=1 LSB), it can be seen that after 80 krad the step size at major bit changes is greatly reduced and even nonmonotonic at steps 1024 and 3072.

# Integral nonlinearity 10 device: Burr Brown 7802 #1 DAC A dose: 0 krad Integral nonlinearity [mV] 5 0 -5 Differential nonlinearity 10 device: Burr Brown 7802 #1 DAC A dose: 0 krad Step height [mV] 5 0 -5 1024 0 2048 3072 4096 Step number

Figure 7.1.7: Quasistatic parameters of device #1 prior to irradiation

Figure 7.1.8: Evolution of integral nonlinearity with increasing total dose for device #1, DAC A. DAC B showed a similar behaviour.

# Differential nonlinearity

Figure 7.1.9: Evolution of differential nonlinearity with increasing total dose for device #1, DAC A. General behaviour of DAC B was similar.

#### **Discussion**

A major bit change is said to take place when the increase of digital input code by 1 causes most (or all) bits to change, e.g. 00111..11 -> 0100..00. The output voltage is determined by the amount of current that is directed to current output pin 1. A smaller than usual increase or even decrease in output voltage necessarily means that this current hardly increased or even decreased. As it can be safely assumed that turning a n-MOSFET OFF is the main problem after a certain amount of irradiation, this means that the current cannot be completely redirected into one of the 2 outputs. So a small portion of it is "leaking" to the wrong output, less current than usually is being converted into a voltage by the external circuitry. An immediate consequence is that the voltage step when turning ON a single bit can only become smaller, but never larger (if the resistor values remain constant). This was observed during the tests: for device #1 the MSB value decreased by 18.5mV, for device #2 by 273mV after 50 krad. The other bits showed similar changes in proportion to their weight. This means for example that the corresponding figures for bit 10 were 9.4mV and 131mV, respectively.

The big difference in the development of gain figures (Table 7.1.2) between device #1 and #2 is a result of different irradiation bias conditions. For DACs with "static" inputs the unbiased switching MOSFETs suffered almost no degradation (=no change in output voltage), while the biased MOSFETs showed a leakage current about twice as large as compared to the equivalent MOSFETs of device #1, resulting in an output voltage shift about twice as large. In device #1, however, both transistors were affected equally because each of them spent the same amount of time in biased and unbiased condition. This result all out confirms the theory of positive gate bias on MOSFETs being worst case.

Close examination of the endpoint values revealed that for device #2 these increased with increasing irradiation. The effect was small (about 5mV after 50 krad), but detectable for both DACs. This can only be explained by two mechanisms: either the resistor values in the R-2R ladder decreased slightly, allowing more current to flow, or the resistor ratio between the ladder resistors and the internal feedback resistor changed. Both effects could lead to the observed results. The main conclusion seems to be that it cannot be taken for granted that resistors are not at all affected at these relatively low total doses.

If for a digital input code of 00..00 the output voltage shifts to higher values this means that a certain amount of current is leaking to the wrong output path. The same holds true for a smaller output voltage after irradiation for a input code of 11..11. The overall effect is a decrease in gain as described above. If all bits were affected equally, then the total gain would be reduced by a certain amount, but the DNL figures would only change very slightly, the INL (according to its definition) would stay the same. Only if some bits show a greater relative leakage than other ones, then this mismatch causes INL and DNL to fluctuate and sharp steps occur in the plots when these most degraded bits change state.

This is the case for device #1, DAC A, where especially bit 9 (representing decimal 512) and bit 10 (decimal 1024) have been affected.

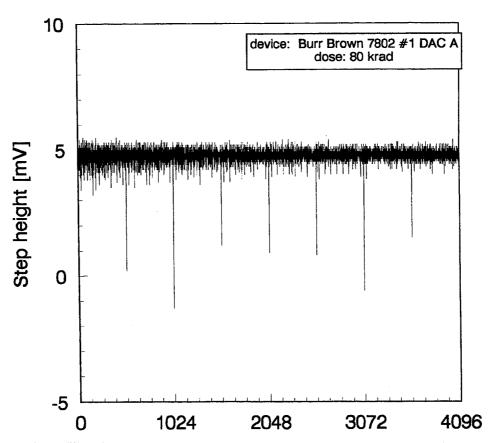

The results for device #2 (Figures 7.1.10 and 7.1.11) were qualitatively similar, but radiation effects were already visible at a much earlier stage. Here bits 10 (decimal 1024) and 11

# Integral nonlinearity

Figure 7.1.10: Evolution of integral nonlinearity with increasing total dose for device #2, DAC A. DAC B showed a similar behaviour.

# Differential nonlinearity

Figure 7.1.11: Evolution of differential nonlinearity with increasing total dose for device #2, DAC A. General behaviour of DAC B was similar.

(decimal 2048) were most affected, but also the lower bits showed larger degradation than those of device #1. As the pre-irradiation curves looked very similar to those of device #1 they were omitted.

It should be kept in mind that the main indicator for a beginning degradation is a shift in the "startpoint" and "endpoint" values.

#### **Conclusions**

Device #1 failed on gain specifications between 30 and 50 krad, probably close to 40 krad. Failure due to degradation in DNL and INL figures was only detected after 80 krad. Device #2 failed on gain specifications at about 25 krad; failure to comply with DNL was already detected after 20krad (nonmonotonicity at step 2048), while INL figures exceeded the allowable limit shortly after 20krad. Somewhere between 50 and 80 krad the device showed complete functional failure.

# **Dynamic parameters**

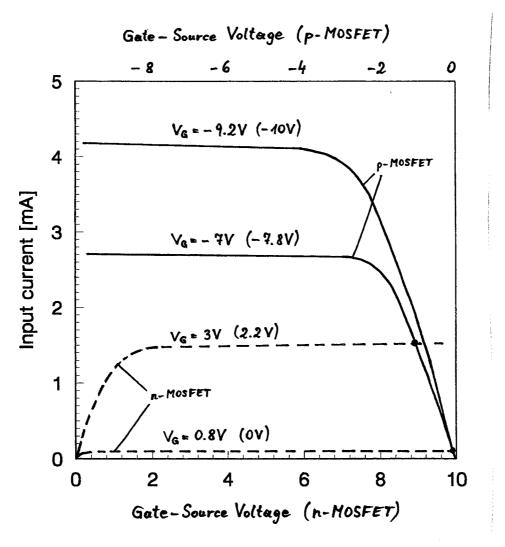

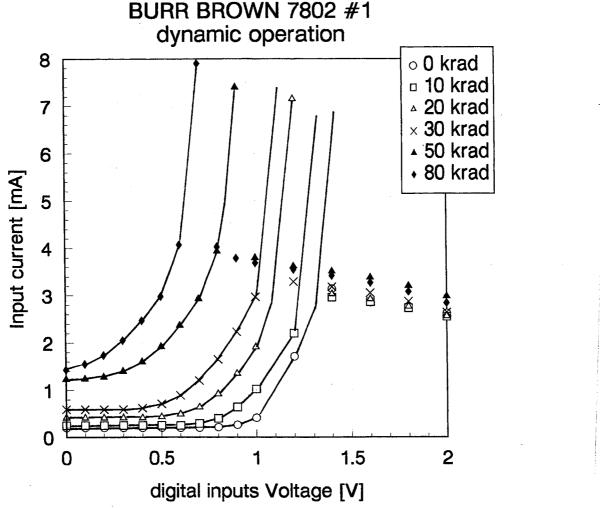

Because of the equipment problems already described earlier (see Section 5.3) the absolute measurement values for the dynamic parameters Signal/Noise Ratio (SNR) and Total Harmonic Distortion (THD) are not reliable. For low digital sinewave frequencies (a full period of the sinewave is represented by many points, so the stepheight from one point to the next is small) the numbers should be quite accurate; for higher frequencies only the relative change of the results for different total doses will give some qualitative information; the numbers itself are meaningless.

The following table shows the results obtained with the HP3653A Spectrum Analyzer; digital data was updated at a rate of 150kHz, and sinewaves of different frequencies were fed into the DAC under test ( $f_{in}$ =125Hz and 9.875kHz). It was avoided to test frequencies that are a multiple of 50Hz because of possible mains noise pickup.

Table 7.1.4: Figures for THD and SNR for two different input frequencies. Numbers are in dB.

#### 50 krad $f_{in} = 125 \text{ Hz}$ 10 krad 20 krad 30 krad 0 krad 5 krad -79.6 -82.3-80.2 7802 #1 DAC A -81.8 -81.6 -80.1 -72.7-81.1 7802 #2 DAC B -81.4 -81.3 -81.3 n.e. $f_{in} = 9.875 \text{ kHz}$ -60.5 7802 #1 DAC A -64.4 -64.1-64.4 -63.8 -63.0 -61.7 -45.7-63.7-63.1 7802 #2 DAC B -60.1n.e.

Total Harmonic Distortion

Signal/Noise Ratio

| $f_{in}$ = 125 Hz            | 0 krad | 5 krad | 10 krad | 20 krad | 30 krad | 50 krad |

|------------------------------|--------|--------|---------|---------|---------|---------|

| 7802 #1 DAC A                | -68.3  | -68.5  | -68.0   | -68.3   | -68.1   | -68.2   |

| 7802 #2 DAC B                | -68.4  | n.e.   | -68.3   | -68.3   | -68.2   | -66.8   |

| $f_{in} = 9.875 \text{ kHz}$ |        | ·      |         |         |         |         |

| 7802 #1 DAC A                | -54.7  | -54.9  | -54.4   | -54.4   | -54.4   | -51.6   |

| 7802 #2 DAC B                | -53.7  | n.e.   | -54.5   | -54.5   | -54.1   | -44.2   |

#### Discussion

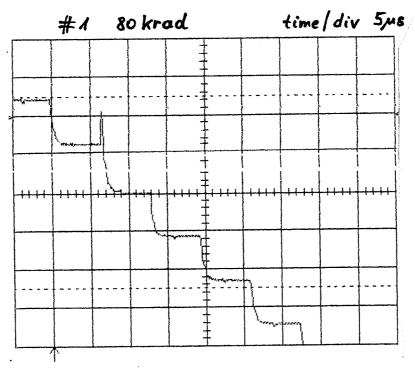

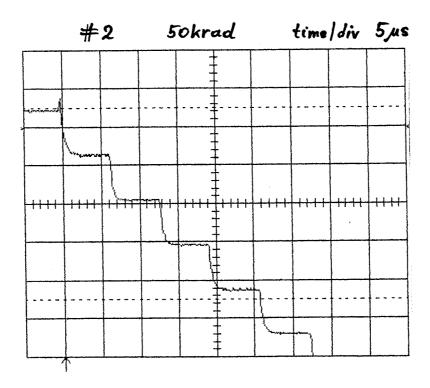

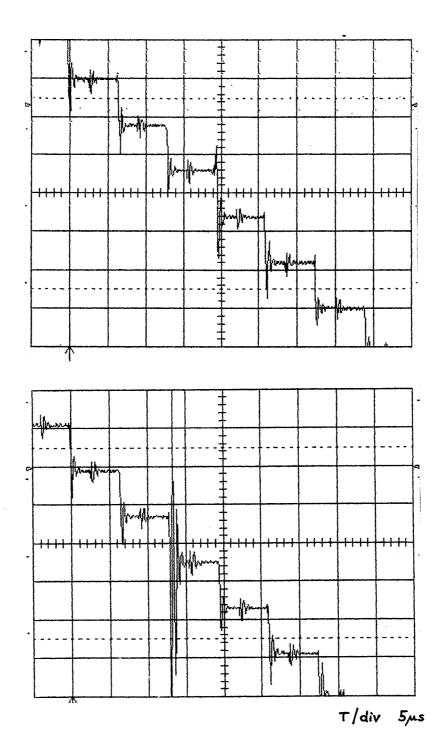

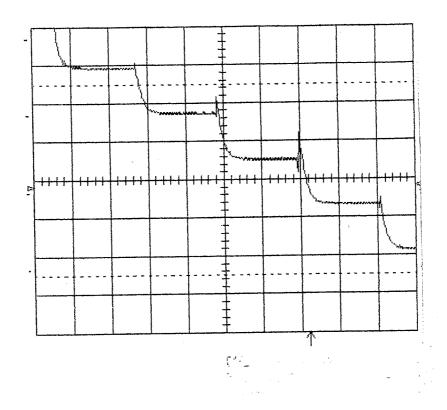

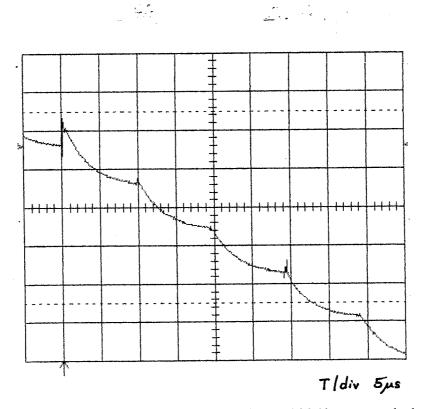

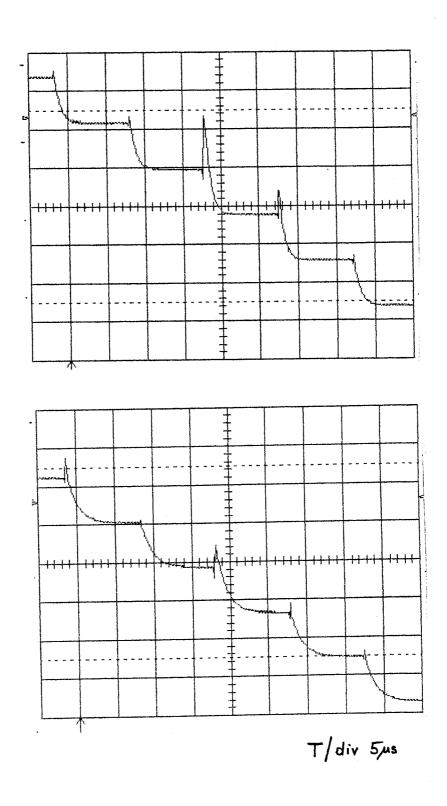

The figures above indicate that for low frequencies like 125Hz the DACs perform close to their theoretical limit of approx. -72.8dB for their SNR. For device #1 the figures hardly change up to 50 krad; after 80 krad a significant deterioriation must have taken place which can be seen in the change in output waveform shown in Figure 7.1.12. Unfortunately no Spectrum Analyzer tests could be performed after 80 krad because of technical problems (HP-Vectra was not available). But as a similar slowing down in settling time was observable for device #2 after 50 krad (Figure 7.1.13), the change in numbers for SNR and THD between 50 krad and 80 krad for device #1 should be similar to the changes for device #2 between 30 krad and 50 krad.

#### Conclusion

No dynamic specifications except the maximum settling time for the output current were given by the manufacturer. The use of OP-AMPs to convert the current into a voltage slows down the settling time, so no direct observation of that figure is possible.

As the external OP-AMPs were not subjected to irradiation, the change in settling time and the degraded figures for SNR and THD after 80 krad for device #1 and after 50 krad for device #2 can undoubtedly be attributed to changes in the DACs. The most likely explanation is slower switching of the current switch MOSFETs.

It seems that these effects are a good indication that complete functional failure is not too far away, meaning that further irradiation will soon destroy the devices.

However, these noticeable changes only took place at doses when some static parameters had already failed to comply with specifications.

THIS PAGE INTENTIONALLY LEFT BLANK

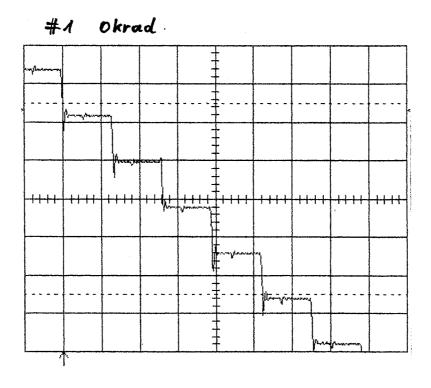

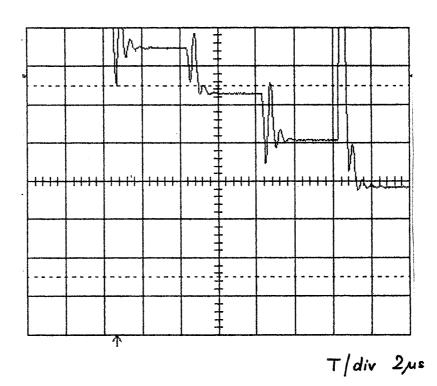

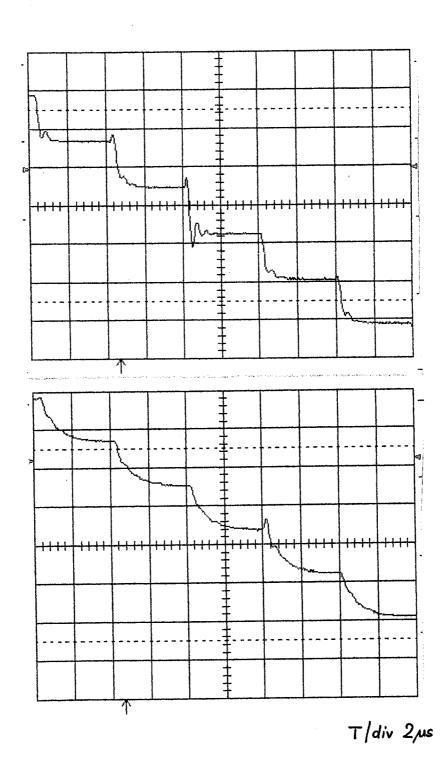

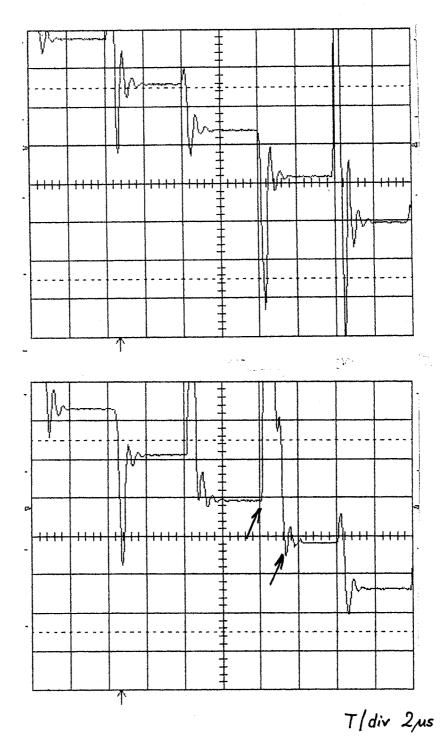

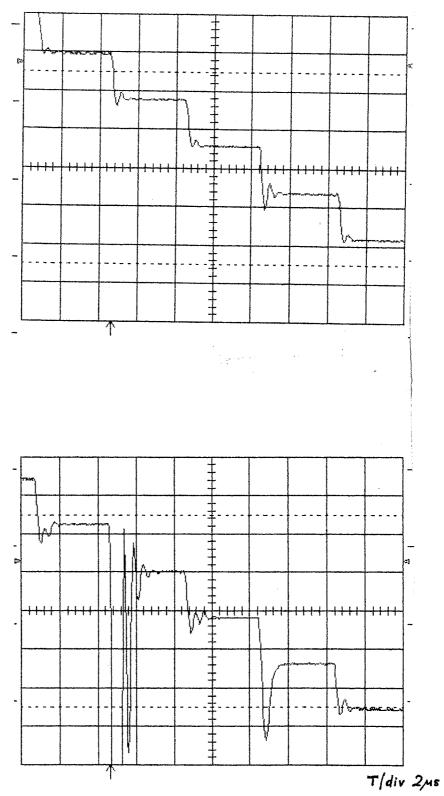

Figure 7.1.12: Hardcopy of the output signal of device #1 as seen on the oscilloscope. Digital inputs were updated at a rate of 150kHz, and the figure shows a detail of a bipolar sinewave around 0V. Stepheight is largest in that part of the curve, and as it crosses 0V most bits of the digital input word change state, among them the MSB. Gain is 200mV per division, with a resolution of 5mV (or 1 LSB). The top picture shows the signal prior to irradiation; settling time is about 1.5us. No change in shape occurred up to 50 krad. After 80 krad, however, a detectable slowing down can be seen (bottom picture). Settling time now was an estimated 3us.

Figure 7.1.13: Same data as in Figure 7.12, for device #2. Here the shape of the initial output signal remained unchanged up to 30 krad After 50 krad the settling time was considerably slower

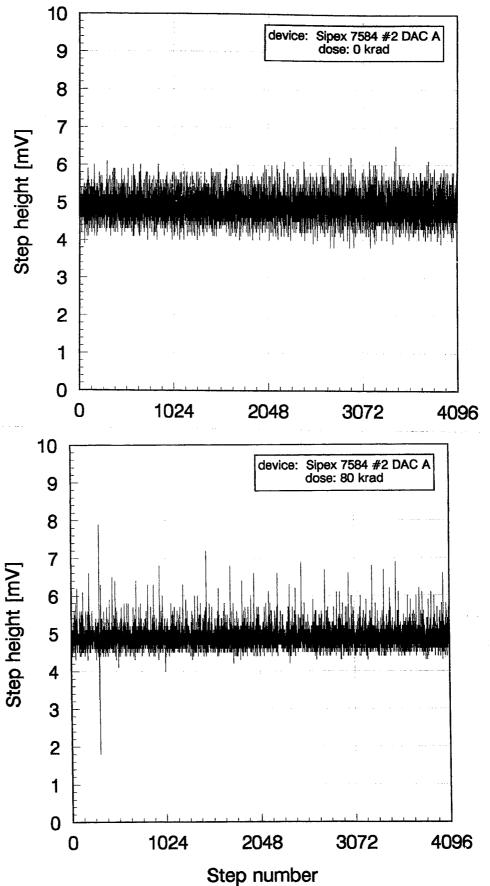

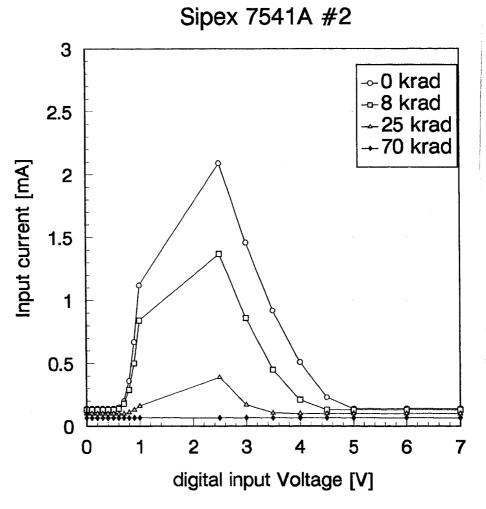

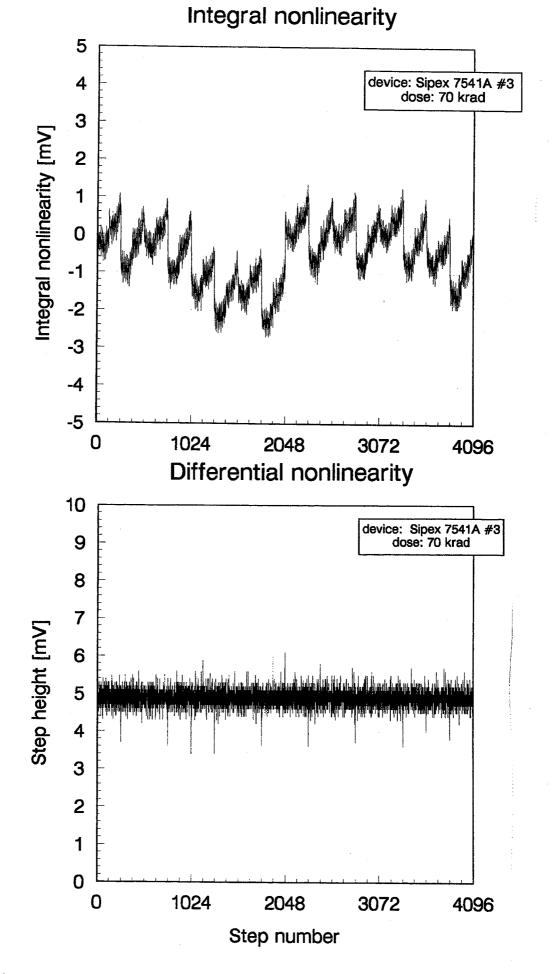

### 7.2 SIPEX 7584C

Brief characterisation: quad current output DAC with input latches and control logic. No internal voltage reference or OP-AMP.

### Specifications (according to datasheet):

| Integral nonlinearity        | max. | +/- 0.5 LSB   |

|------------------------------|------|---------------|

| Differential nonlinearity    | max. | +/- 1 LSB     |

| Gain error                   | max. | +/- 2 LSB (*) |

| Output leakage current       | max. | 10 nA (**)    |

| Digital input current        | max. | +/- 4uA (**)  |

| Power supply current         | max. | 10mA (***)    |

| Output current settling time | max. | 0.8us         |

| Reference input resistance   |      | 5k < R < 15k  |

<sup>(\*)</sup> when using internal feedback resistor

#### General remarks

As can be seen in table 6.2, two devices (=8 DACs in total) were tested up to 80 krad. 4 DACs were irradiated under "static" input conditions (device #1), 4 DACs had "dynamic" inputs (device #2).

#### Pre-irradiation characteristics

Prior to irradiation their characteristics were in accordance with specifications except for INL (0.75 LSB for some of the DACs) and reference input resistor value which was a bit lower than 5k.

# Electrical parameters and quasistatic test results

#### Input current

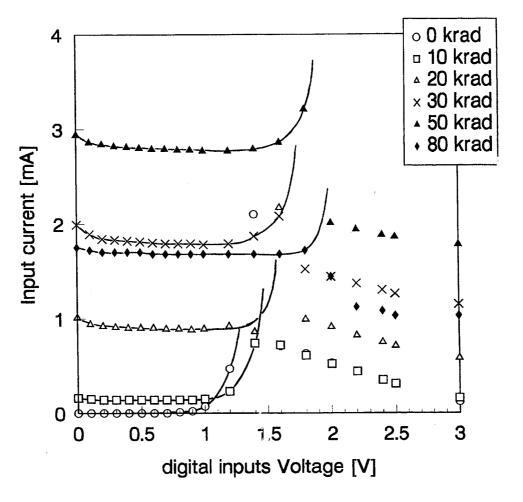

Figure 7.2.1 shows the influence of irradiation on the input current vs. digital input voltage curve for device #1, DAC D, which is representative for the DACs included in that package. (It is worth noting that all four DACs were individually adressable but had only one common power supply pin. The supply current therefore depends on the state of the input latches of

<sup>(\*\*)</sup> at 25 degrees Celsius

<sup>(\*\*\*)</sup>  $V_{in}$ =0.8V or 2.0V. For 0V or 5.0V max. current is 1mA

the 3 DACs that were not adressed; after power-up it might be random. This might lead to a constant offset in input current for different test runs. Therefore only information about changes in the current peak position can be deduced from these plots).