Document No D-P-REP-1083-SE Date Issue Page 23 Aug 2001 1 1/22

+46 13 13 16 28

# ESA RADIATION REPORT ESA\_QCA008901S\_C

Reg. No: 556134-2204

# TITLE Radiation Latch-up Screening of FPGA from Lucent, Lattice and QuickLogic

| EUROPEAN SPACE AGENCY<br>CONTRACT REPORT                 |                             |                                            |                                                                     |             |                                          |           |

|----------------------------------------------------------|-----------------------------|--------------------------------------------|---------------------------------------------------------------------|-------------|------------------------------------------|-----------|

|                                                          |                             | ct. Responsibility f                       | s report was done to<br>or the contents resi<br>ation that prepared | ides in the |                                          |           |

|                                                          | Name                        | ]                                          | Function                                                            | Date        | <u>e S</u>                               | lignature |

| Prepared :                                               | Fredrik Stur<br>Saab Ericss |                                            |                                                                     |             |                                          |           |

| Authorised :                                             | Stanley Ma<br>Saab Ericss   |                                            |                                                                     |             |                                          |           |

|                                                          | Reno Harbo<br>ESA/ESTE      |                                            | ГOS-QCA, Technical Offi                                             | icer        |                                          |           |

| Distribution<br>Complete :<br>Summary :                  |                             |                                            |                                                                     |             |                                          |           |

| Reg. Office:<br>Saab Ericsson<br>S-405 15 Göte<br>Sweden | borg                        | Telephone:<br>+46 31 735 00 00<br>Telefax: | Linköping Of<br>Saab Ericsso<br>S-581 88 Li                         | on Space AB | Telephone:<br>+46 13 18 64 0<br>Telefax: |           |

Sweden

$+46\ 31\ 735\ 40\ 00$

| Document No : D-P-REP-1083-SE | Date : 23 Aug 2001           |                | Issue : 1                             | Page : 2  |

|-------------------------------|------------------------------|----------------|---------------------------------------|-----------|

| Class :<br>Contract No :      | Host System :<br>Host File : | Microsoft Word | 97 for Windows, SE Macro<br>33-SE.doc | o Rev 3.0 |

# SUMMARY

Heavy Ion induced Latch-up tests of Lucent, Lattice and Quicklogic have been performed. All device types indicated Latch-up under heavy ion irradiation.

The Lucent and Quicklogic indicated latch-up at a LET of 14 MeV/cm<sup>2</sup>/mg. The Lucent device showed some kind of permanent damages with increased supply currents, after a few latch-ups.

The Lattice device showed a LET threshold somewhere between 34 and 48  $MeV/cm^2/mg$ . The <sup>252</sup>Cf tests indicated that SEU in control registers of the device might give functionality upsets. No indications of upset in the PROM storage element have been observed.

# **DOCUMENT CHANGE RECORD**

Changes between issues are marked with a left-bar.

| Issue | Date        | Paragraphs affected | Change information |

|-------|-------------|---------------------|--------------------|

| 1     | 23 Aug 2001 | All                 | New document       |

Date : 23 Aug 2001

Issue : 1

### Page : 3

PAGE

# **TABLE OF CONTENTS**

Document No : D-P-REP-1083-SE

| 1.    | ABSTRACT                  |

|-------|---------------------------|

| 2.    | FACILITIES                |

| 2.1   | <sup>252</sup> Cf         |

| 2.2   | Heavy Ion Facility5       |

| 3.    | LATTICE IspLSI5384V(A)6   |

| 3.1   | Test Samples7             |

| 3.2   | Test Techniques9          |

| 3.2.1 | Test Methods9             |

| 3.2.2 | Design of Device          |

| 3.2.3 | Test Flow                 |

| 3.3   | SEL Results 10            |

| 3.3.1 | <sup>252</sup> Cf Results |

| 3.3.2 | Heavy Ion Results         |

| 4.    | LUCENT OR2C06A            |

| 4.1   | Test Object13             |

| 4.2   | Test Samples13            |

| 4.3   | Test Techniques15         |

| 4.3.1 | Test Methods15            |

| 4.3.2 | Design of Device15        |

| 4.3.3 | Test Flow                 |

| 4.4   | SEL Results 16            |

| 4.4.1 | <sup>252</sup> Cf Results |

| 4.4.2 | Heavy Ion Results         |

| 5.    | QUICKLOGIC QL4090 18      |

| 5.1   | Test Object 18            |

| 5.2   | Test Samples18            |

| 5.3   | Test Techniques           |

| 5.3.1 | Test Methods              |

| 5.3.2 | Design of Device          |

| 5.4   | SEL Results               |

| 5.4.1 | Heavy Ion Results         |

| 6.    | CONCLUSION22              |

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

# 1. ABSTRACT

This document presents <sup>252</sup>Cf and heavy ion induced latch-up tests of three FPGA candidates for space application, Lattice, Lucent and Quicklogic. The results indicate that all three device types are susceptible to Latch-up.

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

# 2. FACILITIES

# 2.1 <sup>252</sup>Cf

A dedicated vacuum system for SEL test (and SEU) by  $^{252}$ Cf at Saab Ericsson Space/Components Lab was used for SEL tests. The  $^{252}$ Cf source consist of a thin evaporated layer of Californium on metal backing. The source activity was at time of test 16 kBq. The average nominal stopping power value for the fission fragments is LET=43 MeV/cm<sup>2</sup>/mg. However, due to low penetration depth in Silicon (~13um), metal and polysilicon layers, the real stopping power value would be much lower depending on the technology of the device under test.

# 2.2 Heavy Ion Facility

Latch-up tests have been performed at the Heavy Ion Facility in UCL, Belgium. Ion types and fluence used are reported in the chapter for each device type.

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

Issue : 1

Page : 6

# 3. LATTICE lspLSI5384V(A)

Lattice Semiconductor is a manufacturer that has a non-volatile technology. The ispLSI5000V Family is an In-System Programmable CPLDs. Utilising Lattice's patented  $E^2$ CMOS<sup>®</sup> technology, ispLSI5000V devices provide non-volatile in-system programming specified up to 10,000 program/erase cycles and 20 years data retention. The technology makes it possible for the devices to be programmed and reprogrammed while soldered on-board.

The initial series includes the ispLSI 5256V, 5384V, and 5512V, with logic densities ranging from 256 to 512 macro cells / registers. The I/O pins are compatible with both 3.3- and 2.5V logic levels and with input tolerance of 5V.

|                   | IspLSI 5384VA-70LQ208   | IspLSI 5384V-125LQ208ES |

|-------------------|-------------------------|-------------------------|

| Lattice Family    | IspLSI 5000V            | IspLSI 5000V            |

| Chip revision     | А                       | -                       |

| F <sub>max</sub>  | 70 MHz                  | 125 MHz                 |

| Usable PLD gates: | 18,000                  | 18,000                  |

| Macro cells:      | 384                     | 384                     |

| Registers         | 384                     | 384                     |

| Inputs+I/O        | 144                     | 144                     |

| Vcc               | 3.3V                    | 3.3V                    |

| I/O               | 5 V (input)/3.3V /2.5 V | 5 V (input)/3.3V /2.5 V |

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

# Test Samples

### TEST SAMPLE DETAILS

3.1

| PART TYPE             |   | IspLSI5384VA-70LQ208<br>IspLSI5384V-125LQ208ES |

|-----------------------|---|------------------------------------------------|

| FUNCTIONAL ASSIGNMENT | : | CPLD / FPGA                                    |

| MANUFACTURER          | : | Lattice                                        |

| QUALITY LEVEL         | : | Commercial                                     |

| DATE CODE             | : | IspLSI5384VA 9934                              |

|                       |   | IspLSI5384V 9913                               |

| PACKAGE               | : | PQ208 (Plastic Quad Flat Package)              |

| SPEED GRADE           | : | IspLSI5384VA 70 (Low Power)                    |

|                       |   | IspLSI5384V 125 (Low Power)                    |

| SERIAL NUMBER         | : | IspLSI5384VA #21                               |

|                       |   | IspLSI5384V #1                                 |

IspLSI5384VA is a later chip revision of IspLSI5384V.

|                            | Marking<br><i>Top side</i>               | Marking<br>Bottom Side | Marking<br><i>Chip</i>                                     |

|----------------------------|------------------------------------------|------------------------|------------------------------------------------------------|

| IspLSI5384V<br>Lattice #21 | Lattice Logo<br>IspLSI 5384V<br>125LQ208 | 9913<br>7800104B4      | Chip marking isn't<br>visible behind scraps of<br>plastic. |

|                            | ENG SAMP                                 |                        | plusite.                                                   |

| IspLSI5384VA               | Lattice Logo                             | 9934                   | M-logo 1998                                                |

| Lattice #01                | IspLSI 5384VA<br>70LQ208                 | 7840125A1              | HD5385V-00<br>Lattice                                      |

|                            | B935A04                                  |                        | Lattice-logo                                               |

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

Issue : 1

Page : 8

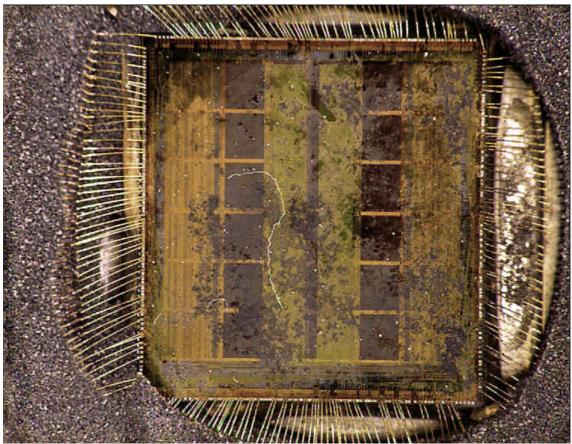

Figure 3.1 Chip photo of Lattice sn#01 after etching of plastic. The size of the chip is 10 x 10 mm.

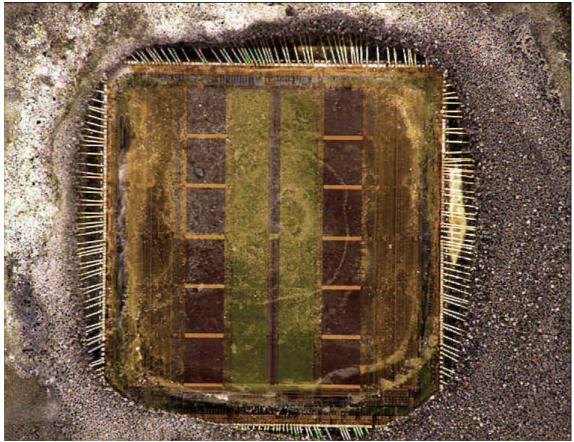

Figure 3.2 Chip photo of Lattice sn#21 after etching of plastic.

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

### 3.2 **Test Techniques**

Single Event Latch-up tests have been performed using a test board connecting power pins and the clock pin of the DUT to external power source and clock generator. Two samples have been delidded and prepared for SEL tests. Functionality test, supply current measurement and program verification by the JTAG interface was performed after delidding, confirming that the devices still were in normal function. The DUT are individually biased and any SEL will result in immediate (within 200 µs) shut down of the power.

### **Test Methods** 3.2.1

| Table 3.1 1 | Electrical Test | <i>Conditions</i> |

|-------------|-----------------|-------------------|

|-------------|-----------------|-------------------|

| TEST PARAMETER                                  | TEST CONDITIONS                           |

|-------------------------------------------------|-------------------------------------------|

| Icc                                             | Vcc = 3.3 V                               |

| Test Mode                                       | Static Mode*                              |

|                                                 |                                           |

| * The <sup>252</sup> Cf-tests were performed in | h a dynamic mode with $f_{CLK} = 25$ MHz. |

### 3.2.2 **Design of Device**

The devices were programmed with a design implementing one shift register utilising 66% of available register cells. With this design functionality of the device could easily be confirmed with a function generator and an oscilloscope.

### 3.2.3 Test Flow

| Step No. | Description                                                |

|----------|------------------------------------------------------------|

| 1        | Programming of Device                                      |

| 2        | JTAG verification of Program                               |

| 3        | Function Test of Device                                    |

| 4        | Irradiation with In Situ Icc measurement and SEL detection |

| 5        | JTAG verification of Program                               |

| 6        | Function Test of Device                                    |

Test Flow for Latch-up tests Table 3.2

The programming and JTAG verification is performed with Lattice's IspDCD software and a download cable connected between a PC and the test board. At UCL we couldn't connect this cable to the test board and only step 1-3 were performed outside the chamber before start of the first test run.

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

### Issue : 1

## 3.3 SEL Results

3.3.1 <sup>252</sup>Cf Results

## **IRRADIATION DETAILS**

| TEST FACILITY      | : Saab Ericsson Space        |

|--------------------|------------------------------|

| IRRADIATION SOURCE | : <sup>252</sup> Cf          |

| BIAS CONDITIONS    | : $Vcc = 3.3V$               |

| TEST TEMPERATURE   | : Room Temperature           |

| TEST MODE          | : $f_{CLK} = 25 \text{ MHz}$ |

The DUT was clocked with 25 MHz during irradiation.

The fluence for the test is calculated from known activity of the source, distance (r) between source and DUT and time of irradiation.

No SEL was detected for any of the tested devices. In Table 3.3 fluence and cross sections for each tests are presented.

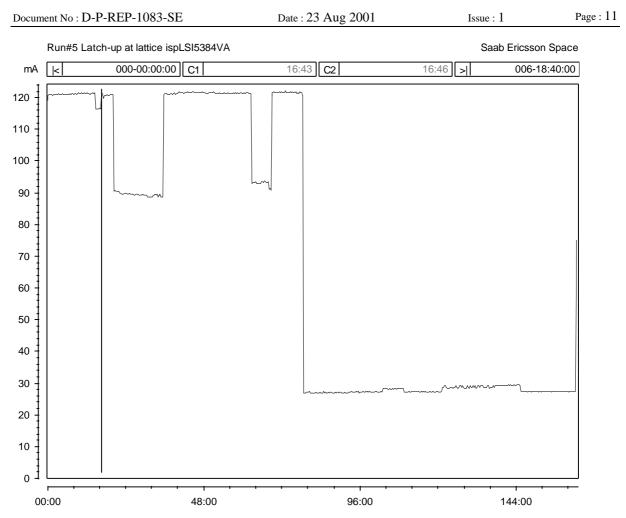

During test run #1 & #2 the standby current was stable through the whole tests at ~120mA. Test run #5, however, the current changed in abrupt steps during irradiation (see Fig. 3.3). Post-irradiation JTAG verification resulted in return to initial current value. This could indicate on SEU in configuration registers used by the JTAG procedure. No errors in program or functionality were detected. However, the function test was performed after the JTAG verification test, and very likely the device was out of function before the JTAG verification. Function test during irradiation at the various current levels has not been performed.

| Tuble                | ible 5.5 Test Result for SEL lesis al Cf source for Lautice IspEst devices. |              |      |                |         |                         |                            |

|----------------------|-----------------------------------------------------------------------------|--------------|------|----------------|---------|-------------------------|----------------------------|

| Run# SN# Device Type |                                                                             | r            | Flux | Runtime        | Fluence | SEL Cross<br>Section    |                            |

|                      |                                                                             |              | [mm] | [ions/(s⋅cm²)] | [hours] | [ions/cm <sup>2</sup> ] | [ cm <sup>2</sup> /device] |

| 1                    | 01                                                                          | IspLSI5384V  | 28   | 8.1            | 234.13  | 6.8 10 <sup>6</sup>     | <1.5 10 <sup>-7</sup>      |

| 2                    | 01                                                                          | lspLSI5384V  | 16   | 20.9           | 185.83  | 1.4 10 <sup>7</sup>     | <7.2 10 <sup>-8</sup>      |

| 5                    | 21                                                                          | IspLSI5384VA | 16.5 | 20.6           | 162.17  | 1.2 10 <sup>7</sup>     | <8.4 10 <sup>-8</sup>      |

Table 3.3 Test Result for SEL tests at <sup>252</sup>Cf source for Lattice IspLSI devices.

Figure 3.3 Icc measurement vs. elapsed time in hours for Run #5. 16:43 hours after test start had the whole test a power-down due to a power failure in the building.

Document No : D-P-REP-1083-SE

## Date : 23 Aug 2001

## 3.3.2 Heavy Ion Results

## **IRRADIATION DETAILS**

|   | UCL                 |

|---|---------------------|

| : | Selected Heavy Ions |

|   | Vcc = 3.3V          |

|   | Static Mode         |

|   |                     |

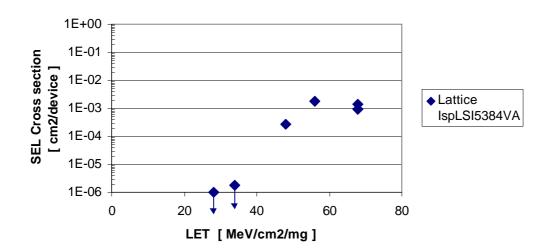

The SEL tests at Heavy Ion Facility were only performed on the IspLSI5384VA (SN#21) device (latest chip revision). The device was static biased during all heavy ion tests.

Figure 3.4 Graph showing Cross Section for Latch-up as a function of LET value for the Lattice IspLSI5384VA device.

| Table 5.45 Heavy fon data form OCL lesis. |     |                         |            |                         |            |                      |     |                         |

|-------------------------------------------|-----|-------------------------|------------|-------------------------|------------|----------------------|-----|-------------------------|

| Run#                                      | lon | LET                     | Tilt       |                         |            | Fluence              |     | SEL Cross<br>Section    |

|                                           |     | MeV/cm <sup>2</sup> /mg |            | MeV/cm <sup>2</sup> /mg | lons/cm²/s | lons/cm <sup>2</sup> | #   | cm <sup>2</sup> /device |

| 45                                        | Ar  | 14,1                    | 60°        | 28,2                    | 2500       | 1,0 10 <sup>6</sup>  | 0   | <1,0 10 <sup>-6</sup>   |

| 46                                        | Xe  | 55,9                    | <b>0</b> ° | 55,9                    | 1500       | 1,1 10 <sup>5</sup>  | 199 | 1,8 10 <sup>-3</sup>    |

| 47                                        | Kr  | 34                      | 60°        | 68                      | 400        | 6,0 10 <sup>4</sup>  | 56  | 9,4 10 <sup>-4</sup>    |

| 48                                        | Kr  | 34                      | 60°        | 68                      | 400        | 3,4 10 <sup>4</sup>  | 48  | 1,4 10 <sup>-3</sup>    |

| 49                                        | Kr  | 34                      | 45°        | 48,08326                | 800        | 2,0 10 <sup>5</sup>  | 52  | 2,6 10 <sup>-4</sup>    |

| 50                                        | Kr  | 34                      | 0°         | 34                      | 1400       | 5,7 10 <sup>5</sup>  | 0   | <1,8 10 <sup>-6</sup>   |

Table 3.43 Heavy Ion data form UCL tests.

Issue:1

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

Issue : 1

# 4. LUCENT OR2C06A

Lucent OR2C06A belongs to the ORCA serie2 of Lucent technologies. It is an SRAM based FPGA. This makes it easy to implement the device for small experimental projects. You only have to have access to a PROM-programmer where the bitstream file is downloaded.

# 4.1 Test Object

The OR2CxxA Family is 5V FPGA manufactured in 0,35  $\mu$ m CMOS technology. The family have devices from 11k to 100k usable gates and up to 480 I/Os. The architecture consists of Lockup tables (LUT), on chip SRAM and flip-flop registers.

|                   | OR2C06A- T 144 |

|-------------------|----------------|

| Usable PLD gates: | 15,900         |

| LUT :             | 576            |

| Registers         | 576            |

| Inputs+I/O        | 114            |

| Vcc               | 5,0V           |

# 4.2 Test Samples

## TEST SAMPLE DETAILS

| PART TYPE<br>FUNCTIONAL ASSIGNMENT<br>MANUFACTURER<br>QUALITY LEVEL<br>DATE CODE<br>PACKAGE | <ul> <li>: LUCENT OR2C06A-2 T 144</li> <li>: CPLD / FPGA</li> <li>: LUCENT</li> <li>: Commercial</li> <li>: 9815S</li> <li>: TQ144 (Plastic Thin Quad Flat Package)</li> </ul> |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Marking                      | Marking                 | Marking                                                                    |

|-------------------------|------------------------------|-------------------------|----------------------------------------------------------------------------|

|                         | <i>Top side</i>              | Bottom Side             | <i>Chip</i>                                                                |

| OR2C06A<br>Sn #01 & #02 | ORCA Logo<br>-<br>-<br>9815S | 37914882<br>2C06A 9810S | M-logo LUCENT<br>Chip marking isn't<br>visible behind scraps of<br>plastic |

$\mathsf{Page}:13$

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

Page : 14

*Figure 4.1 Chip photo of Lucent sn#1 after etching of plastic. The size of the chip is* 6,6 x 6,6 mm.

Figure 4.2 Chip photo of Lucent sn#2 after etching of plastic.

$\mathsf{Document}\ \mathsf{No}: D\text{-}P\text{-}REP\text{-}1083\text{-}SE$

Date : 23 Aug 2001

Issue : 1

### 4.3 **Test Techniques**

Single Event Latch-up tests have been performed using a test board connecting power pins and the input pins of the DUT to external power source and pull-downs. The test board has a PROM with bitstream data for the DUT. The PROM and the DUT use the same power source. This means that each time the power is cycled will the PROM be reset and the DUT will automatically read bitstream into the DUT at start-up. The plastic encapsulation on top of the device has been etched down to the chip on two samples. Functionality test and supply current measurements were performed after etching. The power is connected to a latch-up detection circuit and any SEL will result in immediate (within 200 µs) shut down of the power.

### 4.3.1 Test Methods

| Table 4.1 Electrical Test Conditions |                 |  |  |  |

|--------------------------------------|-----------------|--|--|--|

| TEST PARAMETER                       | TEST CONDITIONS |  |  |  |

| Icc                                  | Vcc = 5,0 V     |  |  |  |

| Test Mode                            | Static Mode     |  |  |  |

#### 1 T 1:4:

### 4.3.2 **Design of Device**

The device was programmed with a design implementing one shift register utilising 20% of available register cells. Also some direct connections between inputs and outputs were implemented. With this design it could easily be confirmed that the device had been correctly initialised.

### 4.3.3 Test Flow

| Table 4.2 | Test Flow for Latch-up tests |  |

|-----------|------------------------------|--|

|-----------|------------------------------|--|

| Step No. | Description                                  |

|----------|----------------------------------------------|

| 1        | Power-up                                     |

| 2        | DUT read bitstream data from external        |

|          | PROM through Master Parallel interface       |

| 3        | Irradiation with In Situ Icc measurement and |

|          | SEL detection                                |

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

## Issue : 1

## 4.4 SEL Results

4.4.1 <sup>252</sup>Cf Results

## **IRRADIATION DETAILS**

| TEST FACILITY      | : Saab Ericsson Space |

|--------------------|-----------------------|

| IRRADIATION SOURCE | : <sup>252</sup> Cf   |

| BIAS CONDITIONS    | : $Vcc = 5,0V$        |

| TEST TEMPERATURE   | : Room Temperature    |

| TEST MODE          | : Static Mode         |

| SAMPLE             | : SN#01               |

Californium tests showed a SEL cross section of  $\sim 3 \cdot 10^{-4}$  cm<sup>2</sup>/device and a few latch-up gave permanently damages. The current didn't return to normal value after the latch-up protection circuit powered down the device.

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

### Issue:1

#### 4.4.2 Heavy Ion Results

## **IRRADIATION DETAILS**

| TEST FACILITY      | : UCL                 |

|--------------------|-----------------------|

| IRRADIATION SOURCE | : Selected Heavy Ions |

| BIAS CONDITIONS    | : $Vcc = 5,0V$        |

| TEST MODE          | : Static Mode         |

| SAMPLE             | : SN#02               |

|                    |                       |

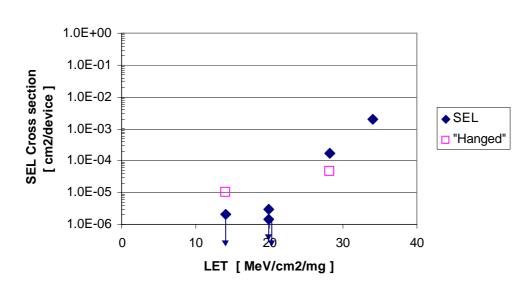

Lucent SEL

Figure 4.3 Graph showing Cross Section for Latch-up as a function of LET value for the Lucent OR2C06A-2 device.

| Table | Table 4.3   Heavy Ion data from UCL Tests |                         |      |                         |                         |                      |     |                         |

|-------|-------------------------------------------|-------------------------|------|-------------------------|-------------------------|----------------------|-----|-------------------------|

| Run#  | lon                                       | LET                     | Tilt |                         | Flux                    | Fluence              | SEL | SEL Cross<br>Section    |

|       |                                           | MeV/cm <sup>2</sup> /mg |      | MeV/cm <sup>2</sup> /mg | lons/cm <sup>2</sup> /s | lons/cm <sup>2</sup> | #   | cm <sup>2</sup> /device |

| 51    | Kr                                        | 34                      | 0°   | 34                      | 800                     | 1,8 10 <sup>4</sup>  | 36  | 2,0 10 <sup>-3</sup>    |

| 13    | Ar                                        | 14,1                    | 0°   | 14,1                    | 700                     | 9,9 10 <sup>4</sup>  | 1*  | 1,0 10 <sup>-5</sup>    |

| 14    | Ar                                        | 14,1                    | 0°   | 14,1                    | 400                     | 5,0 10 <sup>5</sup>  | 0   | <2,0 10 <sup>-6</sup>   |

| 15    | Ar                                        | 14,1                    | 45°  | 19,9                    | 2000                    | 3,4 10 <sup>5</sup>  | 0   | <3,0 10 <sup>-6</sup>   |

| 16    | Ar                                        | 14,1                    | 45°  | 19,9                    | 2000                    | 6,9 10 <sup>5</sup>  | 0   | <1,5 10 <sup>-6</sup>   |

| 17    | Ar                                        | 14,1                    | 60°  | 28,2                    | 1100                    | 2,1 10 <sup>4</sup>  | 1*  | 4,8 10 <sup>-5</sup>    |

| 18    | Ar                                        | 14,1                    | 60°  | 28,2                    | 1100                    | 1,8 10 <sup>5</sup>  | 30  | 1,7 10 <sup>-4</sup>    |

.....

\* The supply current didn't return to normal value ("Hanged") after the latch-up protection circuit powered down the DUT. In Run#13 current increased from 10mA to 30mA and in run#17 to 50mA.

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

Issue : 1

# 5. QUICKLOGIC QL4090

Quicklogic QuickRAM QL4090 is an antifuse FPGA with embedded RAM modules. Quicklogic offer a big military program with many ceramic packages available which makes it to a good candidate for space use.

# 5.1 Test Object

QuickRAM in the QuickLogic's ESP family is an FPGA with embedded dual port SRAM modules. The family includes devices from 9k to 90k PLD gates with 8 to 22 RAM modules of 1,152 bits. The I/O may interface with 3,3 and 5 V devices. QuickRAM is fabricated on a 0.35  $\mu$ m four-layer metal process.

## QuickRAM QL4090 CQ208

|                   | ======================================= |

|-------------------|-----------------------------------------|

| Quicklogic Family | QuickRAM ESP                            |

| Usable PLD gates: | 90,000                                  |

| RAM Modules:      | 22 blocks of 1,152 bits                 |

| Logic Cells:      | 1,584                                   |

| Vcc               | 3.3V / 5,0V                             |

| I/O               | 5 V/3.3V                                |

# 5.2 Test Samples

## TEST SAMPLE DETAILS

|             | Marking  | Marking     | Marking    |  |  |

|-------------|----------|-------------|------------|--|--|

|             | Top side | Bottom Side | Chip       |  |  |

|             |          |             |            |  |  |

| QL4090      |          | 00620A02    | XL36210    |  |  |

| Sn #01 & 02 |          | D31010.00   | QUICKLOGIC |  |  |

|             |          | 0025BJ      | 1998       |  |  |

|             |          |             | QL-logo    |  |  |

|             |          |             | C-logo     |  |  |

|             |          |             | M-logo     |  |  |

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

Issue : 1

Page : 19

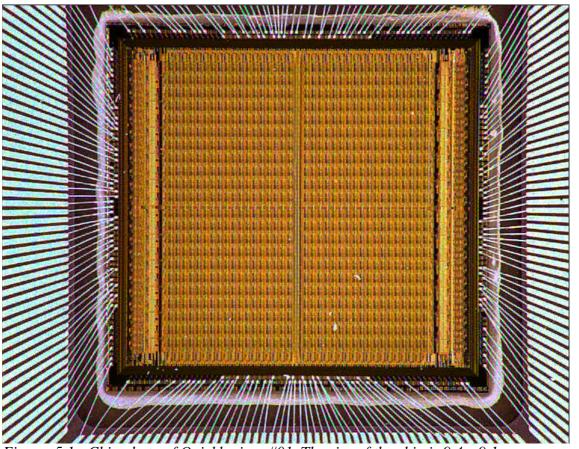

Figure 5.1 Chip photo of Quicklogic sn#01. The size of the chip is 9,4 x 9,1 mm.

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

Issue : 1

# 5.3 Test Techniques

Single Event Latch-up tests have been performed using a test board connecting power pins and the input pins of the DUT to external power source and pull-downs. Two samples were carefully delidded before testing. Functionality test and supply current measurement was performed after delidding, confirming that the devices still were in normal function. The power is connected to a latch-up detection circuit and any SEL will result in immediate (within 200  $\mu$ s) shut down of the power.

# 5.3.1 Test Methods

| Table 5.1 Electrical Test Conditions |                           |  |  |  |  |  |  |

|--------------------------------------|---------------------------|--|--|--|--|--|--|

| TEST PARAMETER                       | TEST CONDITIONS           |  |  |  |  |  |  |

| Icc                                  | $V_{\rm CC} = 3.5  \rm V$ |  |  |  |  |  |  |

|                                      | $V_{CCIO} = 3.5 V$        |  |  |  |  |  |  |

| Test Mode                            | Static Mode               |  |  |  |  |  |  |

|                                      |                           |  |  |  |  |  |  |

Table 5.1Electrical Test Conditions

# 5.3.2 Design of Device

The devices were programmed with a design implementing shift registers utilising more than 90% of available register cells and I/O registers. No of the RAM modules were implemented. The devices were programmed by the manufacturer before delivery to Saab Ericsson Space.

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

# 5.4 SEL Results

# 5.4.1 Heavy Ion Results

## **IRRADIATION DETAILS**

| : UCL                 |

|-----------------------|

| : Selected Heavy Ions |

| : $V_{CC} = 3.5 V$    |

| $V_{CCIO} = 3.5 V$    |

| : Static Mode         |

| : SN#02               |

|                       |

QuckLogic SEL

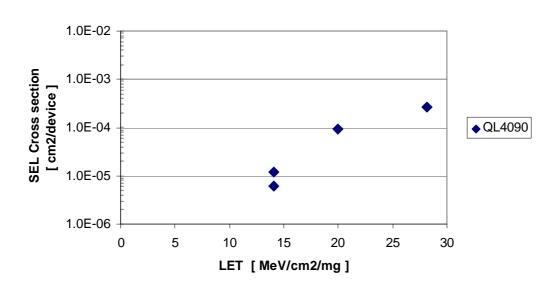

*Figure 5.2 Graph showing Cross Section for Latch-up as a function of LET value for the QuickLogic QL4090 device.*

| Run# | lon | LET                     | Tilt |                         | Flux                    | Fluence              | SEL | SEL Cross               |

|------|-----|-------------------------|------|-------------------------|-------------------------|----------------------|-----|-------------------------|

|      |     |                         |      |                         |                         |                      |     | Section                 |

|      |     | MeV/cm <sup>2</sup> /mg |      | MeV/cm <sup>2</sup> /mg | lons/cm <sup>2</sup> /s | lons/cm <sup>2</sup> | #   | cm <sup>2</sup> /device |

| 41   | Kr  | 14,1                    | 0°   | 34                      | 1000                    | 1,0 10 <sup>6</sup>  | 12  | 1,2 10 <sup>-5</sup>    |

| 42   | Ar  | 14,1                    | 0°   | 14,1                    | 5000                    | 1,0 10 <sup>6</sup>  | 6   | 6,0 10 <sup>-6</sup>    |

| 43   | Ar  | 14,1                    | 45°  | 14,1                    | 3200                    | 5,3 10 <sup>5</sup>  | 49  | 9,3 10 <sup>-5</sup>    |

| 44   | Ar  | 14,1                    | 60°  | 19,9                    | 2000                    | 2,0 10 <sup>5</sup>  | 52  | 2,6 10 <sup>-4</sup>    |

### Page : 21

Document No : D-P-REP-1083-SE

Date : 23 Aug 2001

# 6. CONCLUSION

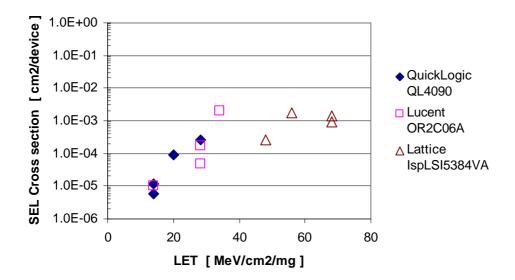

None of the tested devices have survived the Latch-up tests. The Lucent and Quicklogic indicated latch-up at a LET of 14 MeV/cm<sup>2</sup>/mg. The Lucent device showed some kind of permanent damages with increased supply currents, after a few latch-ups.

The Lattice device showed a LET threshold somewhere between 34 and 48  $MeV/cm^2/mg$ . The <sup>252</sup>Cf tests indicated that SEU in control registers of the device might give functionality upsets. No indications of upset in the PROM storage element have been observed.

*Figure 6.1 Graph showing Latch-up Cross sections as function of LET value for all three tested parts performed at the heavy ion facility at UCL, Belgium.*